## Europäisches Patentamt

European Patent Office

## Office européen des brevets

(11)

EP 0 821 460 A2

(12)

## EUROPÄISCHE PATENTANMELDUNG

(43) Veröffentlichungstag:

28.01.1998 Patentblatt 1998/05

(51) Int. Cl.<sup>6</sup>: **H02J 1/04**

(21) Anmeldenummer: 97111124.0

(22) Anmeldedato: 03.07.1997

(84) Benannte Vertragsstaaten:

AT BE CH DE DK ES FI FR GB GR IE IT LI LU MC

NL PT SE

(30) Priorität: 19.07.1996 CH 1811/96

(71) Anmelder:

**Electrowatt Technology Innovation AG**

**6301 Zug (CH)**

(72) Erfinder: Riedel, Friedbert

6300 Zug (CH)

## (54) Stromquelle

(57) Eine Konstantstromquelle (1) weist einen Stromquellentransistor (T1), einen als Folger arbeitenden Kaskodetransistor (T2), einen Verstärkertransistor (T3), eine interne Stromquelle (2) und drei Schalter S1, S2 und S3 auf. Die Transistoren (T1, T2, T3) sind PMOS Transistoren. Im eingeschalteten Zustand der Konstantstromquelle (1) sind die Schalter S1 und S2 geschlossen und der Schalter S3 geöffnet. In diesem Zustand bilden der Verstärkertransistor (T3), der Kaskodetransistor (T2) und die Stromquelle (2) eine Gegenkopplungsschleife, um das Potential am Drain des Stromquellentransistors (T1) auf einen möglichst konstanten Wert zu

regeln. In die Last L wird ein Strom ( $I_p$ ) eingespeist. Im ausgeschalteten Zustand der Konstantstromquelle (1) sind die Schalter S1 und S2 geöffnet und der Schalter S3 geschlossen. In die Last L wird kein Strom eingespeist.

Die Schalter S1 und S3 dienen zum Ein- und Ausschalten der Konstantstromquelle (1), während der Schalter S2 die Einschwingzeit beim Ein- und Ausschalten verkürzt.

Fig. 1

## Beschreibung

Die Erfindung betrifft eine Stromquelle der im Oberbegriff des Anspruchs 1 genannten Art.

Solche Stromquellen eignen sich beispielsweise zur Erzeugung von hochkonstanten Strömen mit weitem Ausgangsaussteuerbereich. Sie werden vorteilhaft in Operationsverstärkern, Steilheitsverstärkern, Switched Current Mode-Techniken für Sigma-Delta-Modulatoren, A/D- Wandlern, usw. eingesetzt.

Eine Stromquelle der im Oberbegriff des Anspruchs 1 genannten Art ist bekannt aus dem Artikel "A High-Swing, High-Impedance MOS Cascode Circuit", IEEE J. Solid-State Circuits, vol. 25, no. 1, pp. 289-297, Feb. 1990 der Autoren E. Säckinger und W. Guggenbühl. Es handelt sich bei dieser Stromquelle um eine geregelte MOS-Kaskode-Konstantstromquelle.

Die Konstantstromquelle speist eine Last. Um ein schnelles Ein- und/oder Ausschalten der Last zu erreichen, kann der von der Konstantstromquelle gelieferte Strom in bekannter Weise mittels eines Umschalters entweder der Last zugeführt oder gegen Masse geschaltet werden (U. Tietze und Ch. Schenk, "Halbleiterschaltungstechnik", Springer Verlag, 10. Auflage, S. 759). Die Konstantstromquelle ist somit immer in Betrieb. Dies führt zu einem kontinuierlichen Verbrauch an Verlustleistung. Beim Schalten wechselt natürlich auch das Potential am Ausgang der Stromquelle von Masse auf einen von der Last abhängigen Wert des Potentials. Dies führt zu unerwünscht grossen Ein- bzw. Ausschaltstromspikes, da beim Potentialwechsel Ladungsverschiebungen parasitärer Kapazitäten auftreten.

Der Erfindung liegt die Aufgabe zugrunde, eine Konstantstromquelle mit sehr guten Schalteigenschaften vorzuschlagen. Eine weitere Aufgabe besteht darin, die Verlustleistung einer für vergleichsweise grosse Ströme ausgelegten Konstantstromquelle möglichst tief zu halten.

Die genannte Aufgabe wird erfindungsgemäss gelöst durch die Merkmale der Ansprüche 1 und 5.

Nachfolgend werden Ausführungsbeispiele der Erfindung anhand der Zeichnung näher erläutert.

Es zeigen:

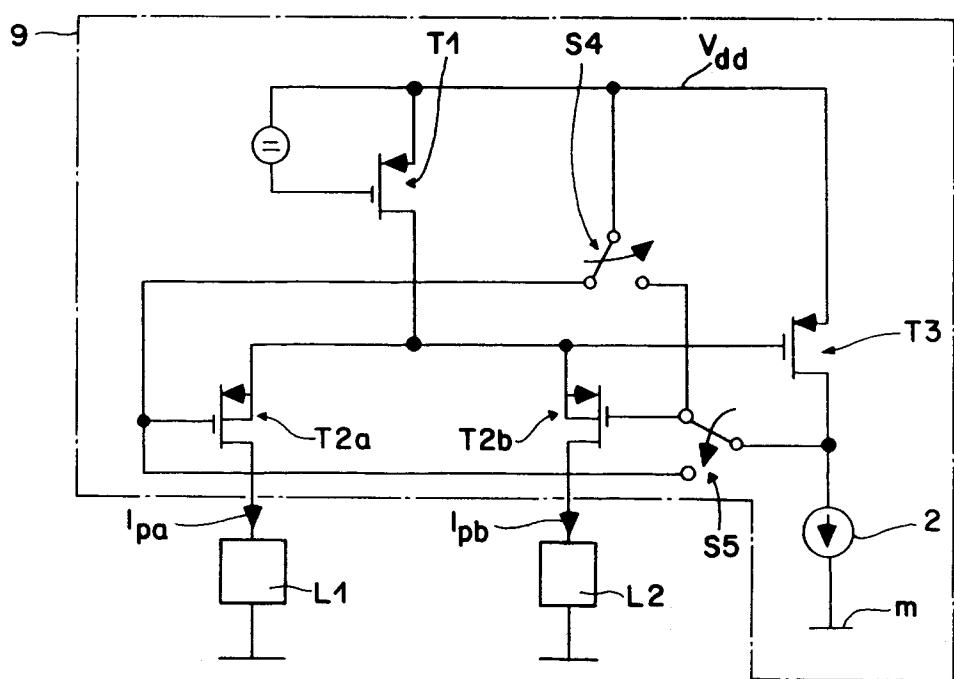

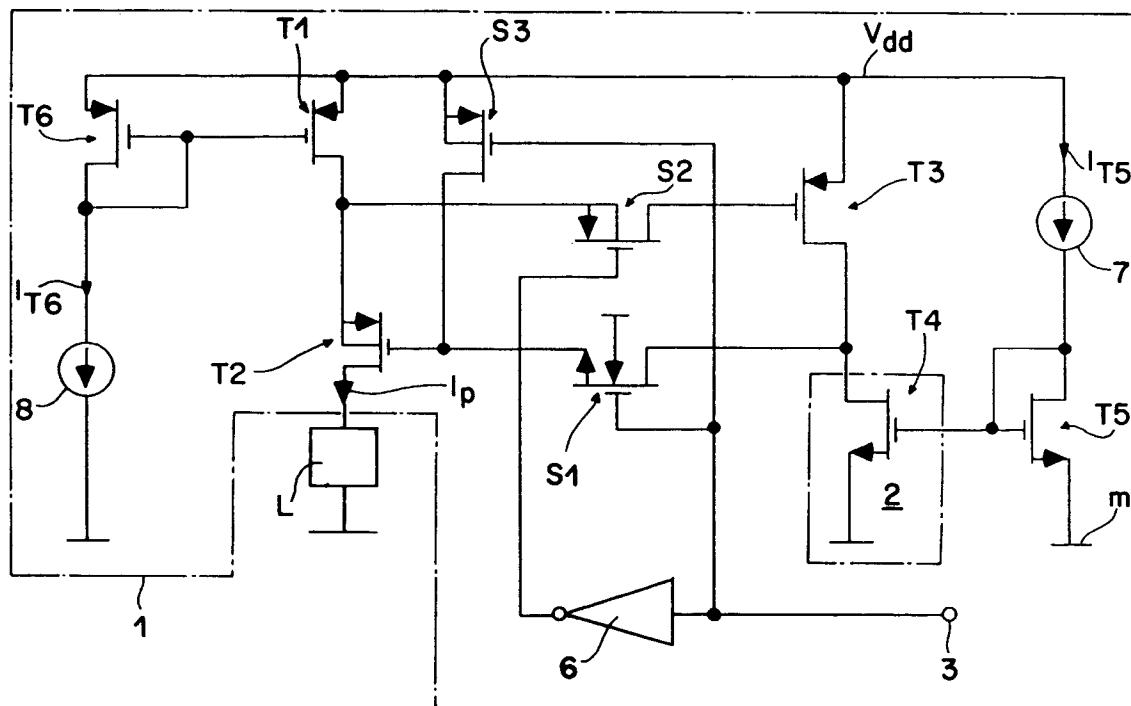

- Fig. 1 eine mit PMOS Transistoren realisierte, ein- und ausschaltbare Konstantstromquelle,

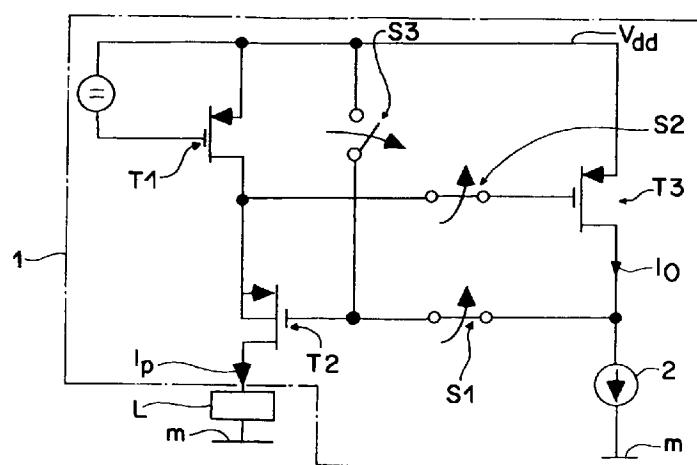

- Fig. 2 ein Zeitdiagramm zur Darstellung des Schaltvorganges,

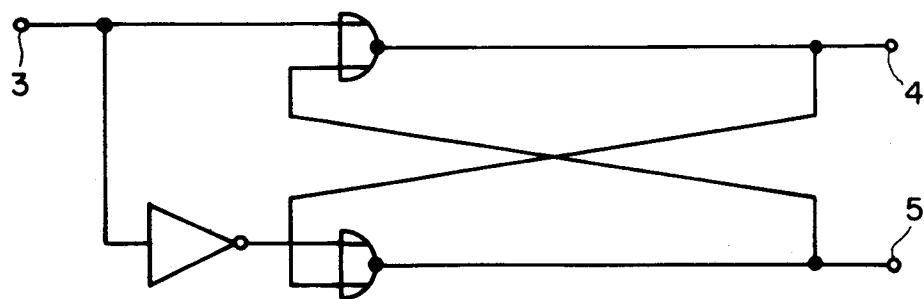

- Fig. 3 eine Schaltungsanordnung zum nichtüberlappenden Schalten von zwei Schaltern,

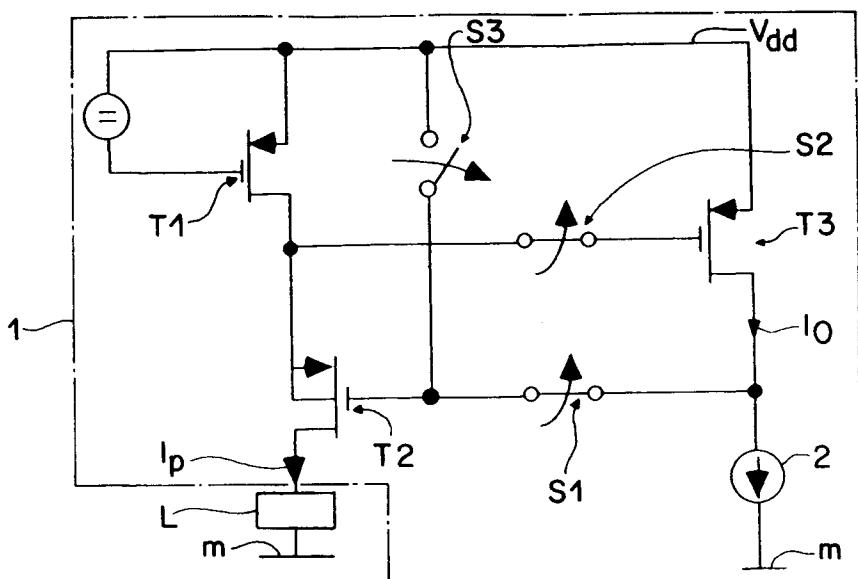

- Fig. 4 die Konstantstromquelle mit als MOS Transistoren ausgebildeten Schaltern und

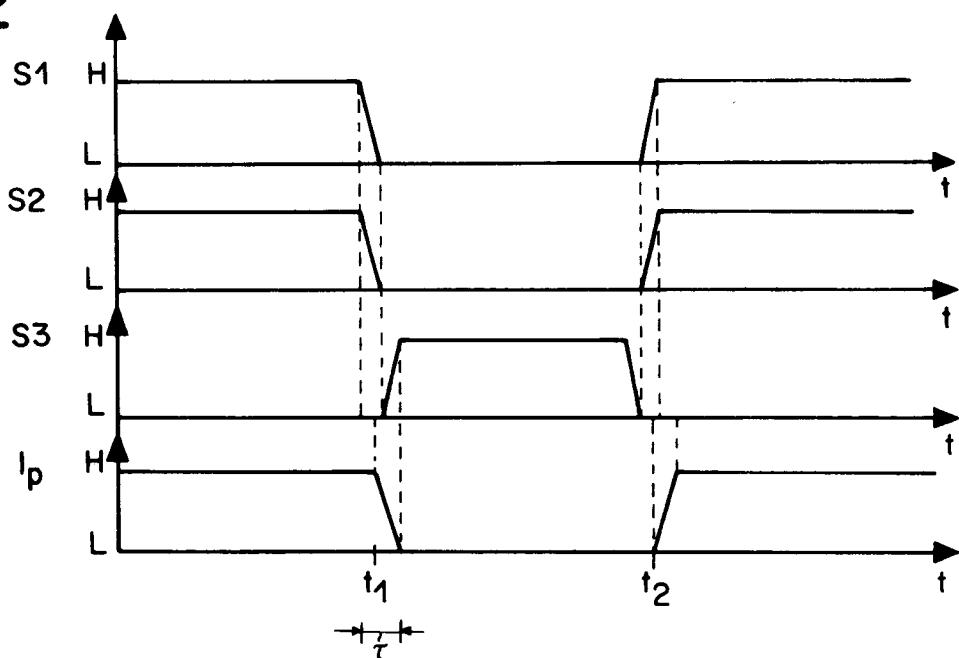

- Fig. 5 eine umschaltbare Konstantstromquelle.

Die Fig. 1 zeigt eine Konstantstromquelle 1, die einen Stromquellentransistor T1, einen als Folger arbeitenden Kaskodetransistor T2, einen Verstärkertransi-

stor T3, eine interne Stromquelle 2 und drei Schalter S1, S2 und S3 aufweist. Die Transistoren T1, T2 und T3 sind PMOS-Transistoren, deren Anschlüsse wie üblich als Gate, Drain bzw. Source bezeichnet sind und die mit den in der Fachliteratur üblichen Symbolen dargestellt sind. Die Konstantstromquelle 1 ist mit der Betriebsspannung  $V_{dd}$  gegenüber der Masse m gespeist.

Die Transistoren T1 und T2 und die zu schaltende Last L sind in Reihe geschaltet: Das Source des Transistors T1 ist mit  $V_{dd}$  verbunden, das Drain des Transistors T1 ist mit dem Source des Transistors T2 verbunden. Die Last L hängt zwischen dem Drain des Transistors T2 und der Masse m. Der Transistor T3 und die Stromquelle 2 sind ebenfalls in Reihe zwischen der Betriebsspannung  $V_{dd}$  und der Masse m geschaltet, wobei das Source des Transistors T3 mit  $V_{dd}$  verbunden ist. An das Gate des Transistors T1 ist eine konstante Spannung angelegt. Das Gate des Transistors T2 ist einerseits über den Schalter S3 an die Spannung  $V_{dd}$  oder andererseits über den Schalter S1 an das Drain des Transistors T3 anschliessbar. Über den Schalter S2 ist das Drain des Transistors T1 mit dem Gate des Transistors T3 verbindbar.

Im eingeschalteten Zustand der Konstantstromquelle 1 sind die Schalter S1 und S2 geschlossen und der Schalter S3 geöffnet. In diesem Zustand bilden der Verstärkertransistor T3, der Kaskodetransistor T2 und die Stromquelle 2 eine Gegenkopplungsschleife, um das Potential am Drain des Stromquellentransistors T1 auf einen möglichst konstanten, vorbestimmten Wert zu regeln. In die Last L wird ein Strom  $I_p$  eingespeist.

Im ausgeschalteten Zustand der Konstantstromquelle 1 sind die Schalter S1 und S2 geöffnet und der Schalter S3 geschlossen. Die Gate-Source Kapazität des Transistors T2 wird beim Schliessen des Schalters S3 sehr schnell entladen, so dass der Transistor T2 sofort sperrt. In die Last L wird kein Strom eingespeist.

Die Schalter S1 und S3 dienen zum Ein- und Ausschalten der Konstantstromquelle 1, während der Schalter S2 die Einschwingzeit beim Ein- und Ausschalten verkürzt.

Um die Konstantstromquelle 1 auszuschalten, werden zuerst die beiden Schalter S1 und S2 geöffnet, wodurch die Gegenkopplungsschleife unterbrochen wird. Etwas verzögert wird dann der Schalter S3 geschlossen. Beim Einschalten der Konstantstromquelle 1 werden in umgekehrter Reihenfolge zuerst der Schalter S3 geöffnet und dann verzögert die Schalter S1 und S2 geschlossen.

Der Transistor T3 leitet auch im ausgeschalteten Zustand der Konstantstromquelle 1, so dass der von der internen Stromquelle 2 gelieferte Strom  $I_0$  weiterhin fliessen kann. Ohne den Schalter S2, d.h. bei einer direkten Verbindung zwischen dem Drain des Transistors T1 und dem Gate des Transistors T3, würde das Gate des Transistors T3 über den Transistor T1 entladen, so dass der Transistor T3 sperrt und der Strom  $I_0$  nicht mehr fliessen könnte. Durch die nichtüberlap-

pende Schaltweise ist sichergestellt, dass das Drain des Transistors T3 nicht kurzzeitig über die Schalter S1 und S3 mit dem Potential  $V_{dd}$  verbunden ist. Da somit der Arbeitspunkt des Transistors T3 beim Schalten nicht wesentlich ändert und der Strom  $I_0$  immer fließt, stabilisiert die Gegenkopplungsschleife das Potential am Drain des Stromquellentransistors T1 beim Einschalten der Konstantstromquelle 1 sehr schnell, so dass die Einschwingzeit und die Schaltspikes beim Einschalten der Konstantstromquelle 1 äußerst kurz bzw. gering werden.

Beim Öffnen des Schalters S2 wird durch Ladungsinjektion seiner Kanalrückwirkungskapazitäten die Gatebeladung des Transistors T3 kurzzeitig erhöht, die sich aber infolge der reaktiven Wirkung der Gate-Drain-Kanalrückwirkungskapazität des Transistors T3 wieder ausgleicht, da immer der Strom  $I_0$  durch den Transistor T3 fließt.

Der Einsatz zusätzlicher kapazitiver Elemente zur Verkleinerung der Ladungsinjektion auf dem Gate des Transistors T3, z.B. in der Form von sogenannten Dummy-Transistoren, brachte keine Verkürzung der Einschwingzeit.

Beim Schließen des Schalters S1 wird durch die Gate-Drain-Kanalrückwirkungskapazität innerhalb einer sehr kurzen Zeit von typisch einer Nanosekunde ein größerer Stromspike in den gemeinsamen Knoten des Drains des Transistors T3 und der Stromquelle 2 injiziert, der aber in dieser Zeitspanne durch die Stromquelle 2 sofort wieder aufgehoben wird. Auch hier lohnt sich der Einsatz von Dummy-Transistoren zur rein kapazitiven Kompensation der Stromspikes nicht, da diese die Reaktionszeiten nicht verkürzen und der Einschwingvorgang bereits ohne Dummy-Transistoren wenig verlangsamt ist.

Die Konstantstromquelle 1 lässt sich in einer Standard CMOS-Bulk Technologie realisieren. In der Fig. 1 ist eine mit PMOS Transistoren realisierte Konstantstromquelle 1 dargestellt. Bevorzugt ist die Verwendung einer n-Wannen Technologie, bei der der Source-Bulk Kurzschluss des Transistors T2 in einer separaten n-Wanne möglich ist, wodurch sich der Aussteuerebereich des Transistors T2 in positiver Richtung vergrößert. Im obengenannten Artikel der Autoren E. Säckinger und W. Guggenbühl ist die Konstantstromquelle 1, jedoch ohne die Schalter S1, S2 und S3, in der Ausführung mit NMOS Transistoren offenbart. Die Schalter S1, S2 und S3 lassen sich in analoger Weise in diese Ausführung mit NMOS Transistoren realisieren.

Eine solche Konstantstromquelle 1 lässt sich auslegen für einen Strom  $I_p$ , der z.B. 10 Mikroampère oder auch ein Milliampère betragen kann. Bei einer für vergleichsweise grosse Ströme ausgelegten Konstantstromquelle 1, bei der der Strom  $I_p$  markant grösser als der Strom  $I_0$  oder andere interne Ströme ist, reduziert sich die Verlustleistung durch das Ausschalten merklich.

Die Fig. 2 zeigt die Stellung der Schalter S1 - S3

und den idealisierten Strom  $I_p$  in Funktion der Zeit  $t$ , wobei die Konstantstromquelle 1 zum Zeitpunkt  $t_1$  ausgeschaltet und zum Zeitpunkt  $t_2$  wieder eingeschaltet wird. Die Schalter S1 bis S3 sind analoge Bauelemente mit einer endlichen Schaltzeit  $\tau$ . Dem Zustand "eingeschaltet" der Schalter S1 bis S3 ist in der Fig. 2 ein Pegel "H", dem Zustand "ausgeschaltet" ein Pegel "L" zugeordnet.

Die Ansteuerung der Schalter S1 bis S3 zum nicht-überlappenden Schalten erfolgt zum Beispiel mit der in der Fig. 3 gezeigten Schaltung. Die Schaltung weist einen Steuereingang 3, einen Ausgang 4 zur Steuerung der Schalter S1 und S2 und einen Ausgang 5 zur Steuerung des Schalters S3 auf. Diese Schaltung mit zwei NOR-Gattern und einem Inverter wird vielfach für Switched Capacitor Schaltungen eingesetzt und ist z.B. aus dem Artikel "Switched Capacitor Circuit Design", R. Gregorian, K.W. Martin and G.C. Temes, Proc. IEEE, vol. 71, pp. 941-966, Aug. 1983 bekannt. Durch zusätzliche Inverter zwischen den Ausgängen der NOR-Gatter und den Ausgängen 4 und 5 lässt sich die Dauer der Nichtüberlappung zwischen dem Schalten verlängern.

Die Fig. 4 zeigt ein spezielles Ausführungsbeispiel der in der Fig. 1 dargestellten Konstantstromquelle 1, bei der als Schalter S1 bis S3 MOS Transistoren verwendet werden. Die Konstantstromquelle 1 weist den Eingang 3 auf, über den die Schalter S1 bis S3 gesteuert werden. Der Schalter S1 ist ein NMOS Transistor mit Bodyeffekt, die Schalter S2 und S3 sind PMOS Schalter ohne Bodyeffekt. Der Schalter S2 weist deshalb eine eigene n-Wanne auf oder ist in die n-Wanne des Transistors T2 integriert. Die Gates der Schalter S1 und S3 sind direkt mit dem Eingang 3 verbunden, das Gate des Schalters S2 ist über einen Inverter 6 mit dem Eingang 3 verbunden. Führt der Eingang 3 ein logisch hohes Potential, z.B. das Potential  $V_{dd}$ , dann ist die Konstantstromquelle 1 eingeschaltet, führt der Eingang 3 ein logisch tiefes Potential, z.B. das Potential der Masse m, dann ist die Konstantstromquelle 1 ausgeschaltet. Am Eingang 3 eintreffende Pulse der richtigen Polarität schalten somit mit ihrer positiven Flanke die Konstantstromquelle 1 ein und mit ihrer negativen Flanke wieder aus.

Beim Einschalten der Konstantstromquelle 1 passiert folgendes: Zu Beginn liegt das Gate des Transistors T2 an  $V_{dd}$ , so dass der als Schalter S1 dienende NMOS Transistor sperrt. Erreicht die Spannung am Eingang 3 die Schwellspannung des Schalters S3, dann sperrt der Schalter S3, so dass die Spannung am Gate des Transistors T2 und an dem Source des Schalters S1 sinkt und schliesslich der Schalter S1 leitend wird, d.h. schliesst. Der Schalter S1 schaltet somit immer erst ein, wenn der Schalter S3 bereits geöffnet ist. Der Schalter S2 schliesst um eine sehr geringe Gatterverzögerung vor dem Schalter S1, da der Schalter S2 ohne Bodyeffekt wirkt. Mit Bodyeffekt des Schalters S2 wäre die Einschwingzeit des Stromes  $I_p$  grösser.

Die Stromquelle 2 besteht aus einem NMOS Tran-

sistor T4, der mit einem weiteren NMOS Transistor T5 einen Stromspiegel bildet. Die konstante Spannung am Gate des Transistors T1 wird mittels eines PMOS Transistors T6 erzeugt. Der Transistor T5 und der Transistor T6 sind ihrerseits aus weiteren Stromquellen 7 bzw. 8 mit Strömen  $I_{T5}$  bzw.  $I_{T6}$  gespeist. Die Stromquelle 7 ist beispielsweise ein PMOS Transistor, dessen Gate mit dem Gate des Transistors T6 verbunden ist. Vor allem der Strom  $I_{T6}$  und in geringerem Mass der Strom  $I_{T5}$  beeinflussen die Einschwingzeit der Konstantstromquelle 1. Sie sind deshalb ausreichend gross zu wählen, um die Einschwingzeit möglichst kurz zu halten.

Die Last L ist beispielsweise ein Kondensator, der geladen wird, solange am Eingang 3 ein Impuls anliegt. Die Impulslängen einer vorgegebenen Anzahl von Impulsen lassen sich auf diese Weise einfach und genau addieren und später mit einer entsprechend erweiterten Schaltungsanordnung auslesen.

Die Fig. 5 zeigt eine weitert Konstantstromquelle 9 mit PMOS Transistoren, bei der der zur Last L fließende Strom  $I_p$  nicht abgeschaltet, sondern umgeleitet wird. Die Konstantstromquelle 9 weist wiederum den Stromquellentransistor T1 und eine Gegenkopplungsschleife auf, die durch den einen von zwei parallel angeordneten Kaskodetransistoren T2a und T2b, den Verstärkertransistor T3 und die Stromquelle 2 gebildet ist. Mittels eines ersten Umschalters S4 ist entweder das Gate des ersten Kaskodetransistors T2a oder das Gate des zweiten Kaskodetransistors T2b mit dem Potential  $V_{dd}$  verbunden. Mittels eines zweiten Umschalters S5 ist das Gate des anderen Kaskodetransistors T2b bzw. T2a mit dem Drain des Transistors T3 verbunden. Die Umschalter S4 und S5 werden gleichzeitig geschaltet. Zwischen dem Drain des ersten Kaskodetransistors T2a und der Masse m ist eine Last L1 geschaltet, zwischen dem Drain des zweiten Kaskodetransistors T2b und der Masse m ist eine zweite Last L2 geschaltet. Das Drain des ersten Kaskodetransistors T2a oder das Drain des zweiten Kaskodetransistors T2b kann aber auch direkt mit der Masse m verbunden sein. Der von der Konstantstromquelle 9 gelieferte Konstantstrom speist somit entweder als Strom  $I_{pa}$  die Last L1 oder als Strom  $I_{pb}$  die Last L2. Das Potential am Drain des Stromquellentransistors T1 ist somit permanent auf einen konstanten Wert geregt.

Während des Umschaltvorganges der beiden Umschalter S4 und S5 kann sich das Potential am Drain des Stromquellentransistors T1 kurzzeitig ändern, da die Verschiedenartigkeit der Lasten L1 und L2 in der Regel unterschiedliche Spannungen an den Drains der Kaskodetransistoren T2a und T2b bedingt, was wiederum die Drain-Bulk Kapazität des Stromquellentransistors T1 umlädt. Die Ströme  $I_{pa}$  und  $I_{pb}$  weisen deshalb Ein- und Ausschaltspikes auf, diese sind jedoch geringer als bei der konventionellen Art der Umschaltung, wo anstelle der Transistoren T2a und T2b nur der Transistor T2 vorhanden ist und wo ein Umschalter das Drain des Transistors T2 entweder mit der Last L1 oder mit der

Last L2 verbindet. Die Einschwingzeit der Ströme  $I_{pa}$  und  $I_{pb}$  sind etwa vergleichbar mit der Einschwingzeit des Stromes  $I_p$  der Konstantstromquelle 1 (Fig. 1). Die Konstantstromquelle 9 lässt sich in analoger Weise auch mit NMOS Transistoren realisieren.

Mit den Konstantstromquellen 1 und 9 sind bei Realisierung in einer 2µm CMOS-Bulk Technologie Einschwingzeiten von ungefähr 50 Nanosekunden erreichbar. Dabei weisen die geschalteten Ströme  $I_p$  bzw.  $I_{pa}$  und  $I_{pb}$  Stromspikes beim Ein- und Ausschalten auf, die in der Größenordnung des Nennwertes der Ströme liegen.

## Patentansprüche

1. Konstantstromquelle (1) zur Speisung einer Last (L) mit einem Strom ( $I_p$ ), wobei die Konstantstromquelle (1) einen Stromquellentransistor (T1), einen als Folger arbeitenden Kaskodetransistor (T2), einen Verstärkertransistor (T3) und eine interne Stromquelle (2) aufweist, wobei der Stromquellentransistor (T1), der Kaskodetransistor (T2) und der Verstärkertransistor (T3) entweder PMOS oder NMOS Transistoren mit einem Gate, einem Drain und einem Source sind, wobei der Stromquellentransistor (T1) und der Kaskodetransistor (T2) in Reihe geschaltet sind, wobei der Verstärkertransistor (T3) und die interne Stromquelle (2) in Reihe geschaltet sind, wobei die Konstantstromquelle (1) mit einer Betriebsspannung ( $V_{dd}$ ) gegenüber Masse (m) gespeist ist und wobei die Last (L) im Falle von PMOS Transistoren zwischen dem Drain des Kaskodetransistors (T2) und der Masse (m), im Falle von NMOS Transistoren zwischen dem Drain des Kaskodetransistors (T2) und der Betriebsspannung ( $V_{dd}$ ) angeordnet ist, **dadurch gekennzeichnet, dass das Gate des Kaskodetransistors (T2) mittels eines ersten Schalters (S1) mit dem Drain des Verstärkertransistors (T3) verbindbar ist, dass das Gate des Verstärkertransistors (T3) mittels eines zweiten Schalters (S2) mit dem Drain des Stromquellentransistors (T1) verbindbar ist, dass das Gate des Kaskodetransistors (T2) mittels eines dritten Schalters (S3) im Falle von PMOS Transistoren mit der Betriebsspannung ( $V_{dd}$ ) bzw. im Falle von NMOS Transistoren mit der Masse (m) verbindbar ist, dass im eingeschalteten Zustand der Konstantstromquelle (1) der erste und der zweite Schalter (S1; S2) geschlossen und der dritte Schalter (S3) geöffnet ist und dass im ausgeschalteten Zustand der erste und der zweite Schalter (S1; S2) geöffnet und der dritte Schalter (S3) geschlossen ist.**

2. Konstantstromquelle (1) nach Anspruch 1, **dadurch gekennzeichnet, dass** beim Einschalten zuerst der dritte Schalter (S3) geöffnet und anschliessend der erste und der zweite Schalter

- (S1; S2) geschlossen werden und dass beim Ausschalten zuerst der dritte Schalter (S3) geschlossen und anschliessend der erste und der zweite Schalter (S1; S2) geöffnet werden.

- 5

3. Konstantstromquelle (1) nach Anspruch 1 oder 2, **dadurch gekennzeichnet, dass** ein Eingang (3) zur Steuerung der Schalter (S1; S2; S3) vorgesehen ist, dass der erste Schalter (S1) ein NMOS Transistor ist und der zweite und der dritte Schalter (S2; S3) PMOS Schalter sind, sofern die Transistoren (T1; T2; T3) PMOS Transistoren sind, bzw. dass der erste Schalter (S1) ein PMOS Transistor ist, der zweite und der dritte Schalter (S2; S3) NMOS Schalter sind, sofern die Transistoren (T1; T2; T3) NMOS Transistoren sind, dass die Gates des ersten und des dritten Schalters (S1; S3) direkt mit dem Eingang (3) verbunden sind und dass das Gate des zweiten Schalters (S2) über einen Inverter (6) mit dem Eingang (3) verbunden ist.

- 10

4. Konstantstromquelle (1) nach einem der Ansprüche 1 bis 3, **dadurch gekennzeichnet, dass** der erste Schalter (S1) ein Transistor mit Bodyeffekt und dass der zweite und der dritte Schalter (S2; S3) Transistoren ohne Bodyeffekt sind.

- 15

5. Konstantstromquelle (9) zur Speisung einer Last (L1) mit einem Strom ( $I_{pa}$ ), wobei die Konstantstromquelle (9) einen Stromquellentransistor (T1), einen als Folger arbeitenden ersten Kaskodetransistor (T2a), einen Verstärkertransistor (T3) und eine interne Stromquelle (2) aufweist, wobei der Stromquellentransistor (T1), der Kaskodetransistor (T2a) und der Verstärkertransistor (T3) entweder PMOS oder NMOS Transistoren mit einem Gate, einem Drain und einem Source sind, wobei der Stromquellentransistor (T1) und der Kaskodetransistor (T2a) in Reihe geschaltet sind, wobei der Verstärkertransistor (T3) und die interne Stromquelle (2) in Reihe geschaltet sind, wobei die Konstantstromquelle (1) mit einer Betriebsspannung ( $V_{dd}$ ) gegenüber Masse (m) gespeist ist und wobei die Last (L1) im Falle von PMOS Transistoren zwischen dem Drain des Kaskodetransistors (T2a) und der Masse (m), im Falle von NMOS Transistoren zwischen dem Drain des Kaskodetransistors (T2a) und der Betriebsspannung ( $V_{dd}$ ) angeordnet ist, **dadurch gekennzeichnet, dass** parallel zum ersten Kaskodetransistor (T2a) ein zweiter Kaskodetransistor (T2b) geschaltet ist, dessen Drain eine zweite Last (L2) speist, dass mittels eines ersten Umschalters (S4) entweder das Gate des einen Kaskodetransistors (T2a; T2b) mit der Betriebsspannung ( $V_{dd}$ ) im Falle von PMOS Transistoren bzw. mit der Masse (m) im Falle von NMOS Transistoren verbunden ist und dass mittels eines zweiten Umschalters (S5) das Gate des anderen Kaskodetransistors (T2b;

- 20

- 25

- 30

- 35

- 40

- 45

- 50

- 55

- T2a) mit dem Drain des Verstärkertransistors (T3) verbunden ist.

6. Konstantstromquelle (9) nach Anspruch 5, **dadurch gekennzeichnet, dass** die zweite Last (L2) ein Kurzschluss ist.

Fig. 1

Fig. 2

Fig. 3

Fig. 4

Fig. 5