(12)

**Europäisches Patentamt European Patent Office**

Office européen des brevets

EP 0 858 178 A1 (11)

**EUROPÄISCHE PATENTANMELDUNG**

(43) Veröffentlichungstag: 12.08.1998 Patentblatt 1998/33 (51) Int. Cl.6: H04H 7/00

(21) Anmeldenummer: 98100793.3

(22) Anmeldetag: 19.01.1998

(84) Benannte Vertragsstaaten:

AT BE CH DE DK ES FI FR GB GR IE IT LI LU MC **NL PT SE**

Benannte Erstreckungsstaaten:

**AL LT LV MK RO SI**

(30) Priorität: 06.02.1997 CH 262/97

(71) Anmelder:

**STUDER Professional Audio AG** CH-8105 Regensdorf ZH (CH)

(72) Erfinder:

- Von Ow, Andreas 8340 Hinwil (CH)

- · Gehri, Silvio 8604 Volketswil (CH)

- · Huber, Robert 8103 Unterengstringen (CH)

## (54)Verfahren und Vorrichtung zum Mischen von digitalen Audio-Signalen

(57)Die Erfindung betrifft ein Verfahren und eine Vorrichtung zum Mischen von digitalen Audio-Signalen aus einer ersten Anzahl Eingängen (1 bis m) in eine zweite Anzahl Ausgänge (21 bis n). Um ein Verfahren und eine Vorrichtung zu schaffen die wesentlich einfacher und billiger sind, sollen Datenworte der eingehenden Audio-Signale so zueinander geführt werden, dass die Datenbit in aufsteigender Reihenfolge mit dem niedrigstwertigen Bit voraus, in parallelen Datenströmen wort- und bitweise synchronisiert auftreten und bitweise summiert werden können.

## **Beschreibung**

Die Erfindung betrifft ein Verfahren und eine Vorrichtung zum Mischen von digitalen Audio-Signalen aus einer ersten Anzahl Eingängen in eine zweite Anzahl Ausgänge.

Solche Verfahren und Vorrichtungen sind bereits bekannt und werden in sogenannten digitalen oder digital arbeitenden Audio-Mischpulten angewendet. Digital arbeitende Mischpulte ermöglichen es, in mehreren verschiedenen Kanälen eintreffende Tonsignale einzeln oder gesammelt beliebigen Ausgängen zuzuleiten. Dabei können die einzelnen Tonsignale verändert und mit anderen Tonsignalen vereinigt werden. Das bedeutet, dass die Möglichkeit bestehen soll, jedes Signal üblicherweise mit einem Faktor zu multiplizieren und mit anderen Signalen zu addieren und eventuell auch die Tonsignale zu verzögern.

Bekannte digitale Mischpulte haben deshalb Vorrichtungen, bei denen die Eingänge paar- oder gruppenweise mit digitalen Signalprozessoren (DSP's) verbunden sind, die problemlos in der Lage sind, solche Operationen wie Addition, Multiplikation und Speicherung von Tonsignalen vorzunehmen. Allerdings stösst man auf Grenzen, wenn man versucht möglichst viele Eingänge auf einen Signalprozessor zu leiten, denn diese sind nicht mit geeigneten Schnittstellen versehen und können die verlangte Rechenleistung für viele Kanäle nicht mehr erbringen. Dies weil Tonsignale in gegebenen Zeitabschnitten relativ grosse Datenmengen enthalten.

Diese durch die grosse Datenmenge verursachten Probleme werden üblicherweise dadurch entschärft, dass eben einem Signalprozessor nur eine geringe Anzahl Eingänge zugeordnet wird, was bedeutet, dass bei einer gegebenen Anzahl Ein- und Ausgänge mehrere Signalprozessoren vorgesehen werden, die zu Kaskaden geschaltet werden müssen. Das grösste Problem ist dabei die Summierung der Tonsignale aus einer grossen Anzahl Eingänge oder eben aus mehreren solchen Signalprozessoren in einem sogenannten Summenbus.

Als Summenbus sind deshalb bereits Lösungen mit sogenannten TDM-Bussen oder Systeme mit gemeinsamen Speichern, sog. "shared memory"-Systeme bekannt geworden. Ein TDM-Bus ist ein Parallelbus der für die Daten aus jedem Eingangskanal ein Zeitfenster bereithält, so dass die Signale im Bus seriell hintereinander geschaltet auftreten. Ebenso ist es denkbar dafür DPRAM-Speicher einzusetzen und die Prozessoren wie eine sogenannte "daisy-chain" untereinander zu verbinden. Allerdings sind alle diese Lösungen technisch aufwendig und teuer.

Die Erfindung wie sie in den Ansprüchen gekennzeichnet ist, löst deshalb die Aufgabe ein Verfahren und eine Vorrichtung zum Mischen von digitalen Audio-Signalen zu schaffen, die wesentlich einfacher und billiger sind.

Die Lösung dieser Aufgabe gelingt insbesondere dadurch, dass für die Summierung der Tonsignale aus den einzelnen Eingängen oder Kanälen einfache Schaltungen oder programmierbare Bausteine wie programmierbare Logikbausteine, PLD's oder kundenspezifische integrierte Schatungen ASICS verwendet werden, die zur bitweisen Summierung der wort- und bitweise synchronisierten Datenströme der Tonsignale ausgebildet sind und verwendet werden. Dazu müssen aber die Datenworte mit dem niedrigstwertigen Bit voraus übertragen werden, was eine entsprechende Formatierung der Datenströme voraussetzt. Für eventuelle zusätzliche Verarbeitungen der Signale vor der Summierung, ist eine bitweise Multiplikation des betreffenden Datenstromes vorgesehen, wobei der Datenstrom mehrfach einem Summierer zugeführt wird, dabei aber die mehrfach zugeführten Datenströme jeweils um ein Bit versetzt oder verzögert werden. Somit werden die Datenworte der eingehenden Audio-Signale so zueinander geführt, dass die Datenbit in aufsteigender Reihenfolge mit dem niedrigstwertigen Bit voraus, in parallelen Datenströmen wort- und bitweise synchronisiert auftreten und bitweise summiert werden. Dazu ist jedem Ausgang ein Summierer vorgeschaltet, der mit mindestens einem Teil der Eingänge über die Verarbeitungselemente verbunden ist.

Die durch die Erfindung erreichten Vorteile sind insbesondere darin zu sehen, dass die Vorrichtung sehr preisgünstig realisierbar ist. Ein Grund dafür ist darin zu sehen, dass die vorgeschlagene Summierung der Datenströme sehr wenig Speicher benötigt. Ein weiterer Grund liegt darin, dass für die Formatierung und für eventuelle weitere Verarbeitungen der

Daten aus den einzelnen Eingängen oder Kanälen nun relativ einfache und preisgünstige digitale Signalprozessoren (DSP's) verwendet werden können, wobei ein Signalprozessor, sofern er mehrere Eingänge aufweist auch mehrere Kanäle bedienen kann, da er nur noch relativ einfache Aufgaben erfüllen muss. Dies ist eben darum möglich, weil eine aufwendige Aufgabe, nämlich die Summierung der Datenströme nicht mehr durch die Signalprozessoren erfüllt werden muss. Es kann aber auch vorgesehen werden, dass ein Signalprozessor soweit wie möglich Datenströme addiert, so dass dem Summierer bereits Teilsummen zugeführt werden. Dies soll aber nur soweit geschehen, wie dies in einem einzigen Signalprozessor durchgeführt werden kann

Im folgenden wird die Erfindung anhand von lediglich einen Ausführungsweg darstellenden Zeichnungen näher erläutert. Es zeigt

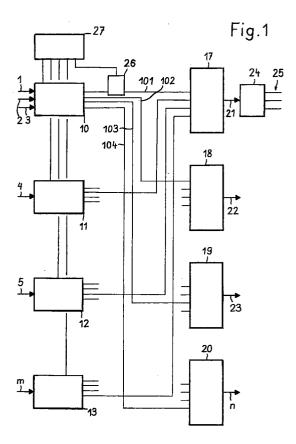

Fig. 1 ein Blockschema einer erfindungsgemässen Vorrichtung,

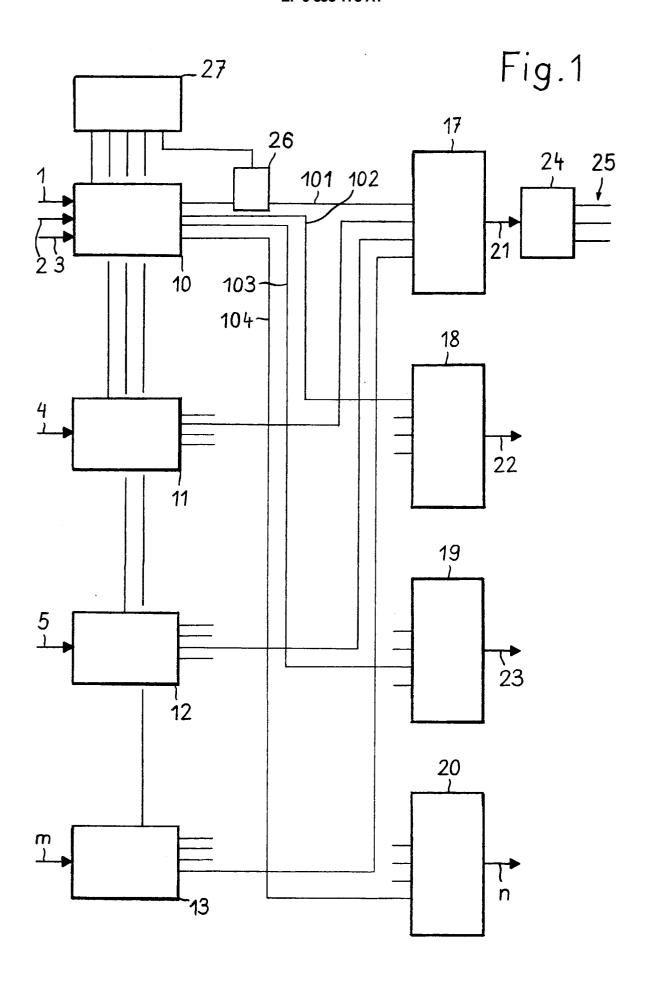

Fig. 2 eine schematische aber detailliertere Darstellung eines Teils der Vorrichtung gemäss Fig. 1,

25

35

40

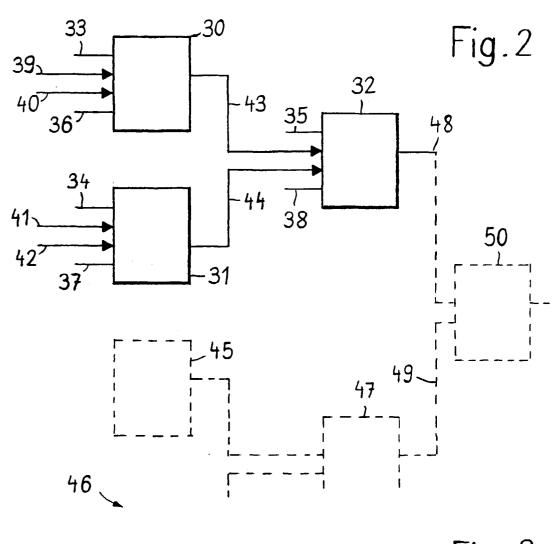

Fig. 3 eine schematische Darstellung eines weiteren Teils der Vorrichtung gemäss Fig. 1 und

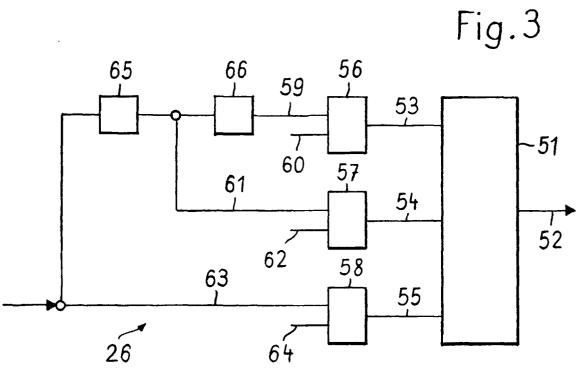

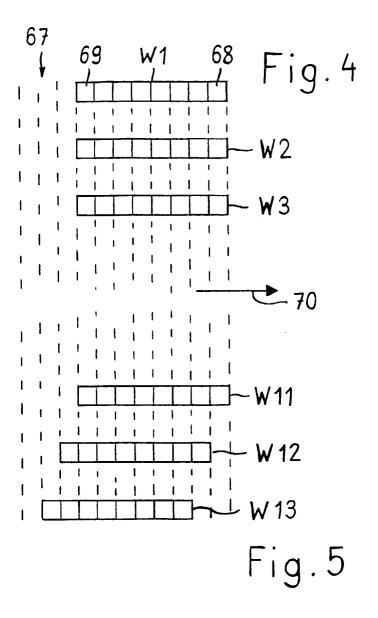

Fig. 4 und 5 je eine schematische Dartellung eines Verfahrensschrittes.

Fig. 1 zeigt eine Vorrichtung zum Mischen digitaler Audio-Signale mit mehreren Eingängen 1, 2, 3, 4, 5 und m, womit angedeutet ist, dass eine Anzahl m Eingänge möglich ist, wobei heute bis zu m = 64 Kanälen üblich sind. Die Eingänge 1 bis m münden in je eine Verarbeitungseinheit 10, 11, 12, 13, die entweder als digital arbeitender Signalprozessor DSP oder sonstwie als Einheit zur digitalen Signalverarbeitung aufgebaut sein kann. Eine Verarbeitungseinheit kann auch an mehrere Eingänge angeschlossen sein, wie dies für die Verarbeitungseinheit 10 mit den Eingängen 1, 2 und 3 angedeutet ist. Die Vorrichtung weist Ausgänge 21, 22, 23 und n auf, wobei heute bis zu n = 32 Ausgängen nicht ungewöhlich sind. Jedem Ausgang 21 bis n ist ein Summierer 17, 18, 19, 20 vorgeschaltet. Jede

Verarbeitungseinheit 10, 11, 12, 13 und damit jeder Eingang 1 bis m ist über Verbindungen mit mehreren oder idealerweise allen Ausgängen 21 bis n verbunden. Dies geschieht für die Verarbeitungseinheit 10 hier über Leitungen 101, 102, 103, 104 die von entsprechenden Ausgängen an den Verarbeitungseinheiten 10 bis 13 zu Eingängen an den Summierern 17 bis 20 führen. In Fig. 1 sind solche Ein- und Ausgänge und ein Teil der notwendigen Verbindungen eingezeichnet. Auf die Darstellung aller Verbindungen wurde verzichtet um die Klarheit der Darstellung zu gewährleisten. Wahlweise können die Ausgänge, wie hier Ausgang 21, auch in einen Formatkonverter 24 münden, der wiederum mehrere parallele Ausgänge 25 aufweisen kann. Dies insbesondere dann, wenn über einen Eingang Audiosignale aus mehreren Kanälen seriell zugeführt werden. Diese Audiosignale können dann parallel ausgegeben werden. Weiter kann in die Leitungen 101, 102, usw. ein weiteres Verarbeitungselement 26 eingefügt sein, das das Signal abschwächen oder verstärken kann. Ein solches weiteres Verarbeitungselement 26 ist zusammen mit den anderen Verarbeitungselementen 10 bis 13 über Steuerleitungen 28 mit einer Bedienungseinheit 27 verbunden, welche diejenigen Bedienungselemente aufweist, die üblicherweise auf der Bedieneroberfläche eines Mischpultes vorhanden sind. Der Formatkonverter 24 kann ebenfalls ein digital arbeitender Signalprozessor (DSP) oder sonst ein signalverarbeitendes Element sein. Vorzugsweise bilden die Summierer 17 bis 20 einen Summenbus in einem digital arbeitenden Audio-Mischpult.

Fig. 2 zeigt eine Ausführung eines Summierers 17 bis 20. Ein solcher besteht aus mindestens drei Zweibitaddierern 30, 31 und 32, die je einen Eingang 33, 34 und 35 für ein erstes Taktsignal, je einen Eingang 36, 37 und 38 für ein weiteres Taktsignal und je zwei Eingänge 39 und 40, 41 und 42 sowie 43 und 44 für digitalisierte

Audiosignale aufweisen. Dabei sind die beiden Zweibitaddierer 30 und 31 parallel geschaltet und deren Ausgänge sind an die Eingänge 43, 44 des dritten Zweibitaddierers 32 angeschlossen. Sind Audiosignale aus mehr als vier Eingängen 39, 40, 41, 42 zu verarbeiten wird die Struktur durch drei weitere Zweibitaddierer 45, 46, 47 ergänzt. Die Ausgänge 48, 49 der Zweibitaddierer 32 und 47 münden aber in einen zusätzlichen Zweibitaddierer 50. So lässt sich die Struktur für mehrere Eingänge kaskadenartig erweitern. Der Summierer kann aber im gleichen Sinne auch aus Zwei-oder Mehrbitaddierern aufgebaut sein. Werden beispielsweise Dreibitaddierer verwendet, so hat jeder Dreibitaddierer drei Eingänge für Audiosignale und drei Dreibitaddierer sind mit einem weiteren Dreibitaddierer parallel verbunden.

Fig. 3 zeigt eine spezielle Ausführung eines Verarbeitungselementes 26 wie es aus der Fig. 1 bekannt ist. Dieses besteht wiederum aus einem Summierer 51 mit einem Ausgang 52 und beispielsweise drei Eingängen 53, 54, 55. Diesen vorgeschaltet sind Multiplizierer 56, 57, 58 mit je zwei Eingängen 59 und 60, 61 und 62, 63 und 64. Dabei ist der Eingang 63 direkt für den unveränderten Datenstrom vorgesehen. Die Eingänge 61 und 59 erhalten den Datenstrom verzögert aus Verzögerungseinheiten 65 oder 66.

Fig. 4 zeigt beispielsweise drei Datenworte W1, W2, W3 die bitweise synchronisiert parallel auftreten. Linien 67 geben erste Taktsignale an, die die Vorgänge im Bitraster steuern. Die Datenworte werden in Richtung eines Pfeiles 70 bewegt. Dabei ist jedes Datenwort W in einer solchen Reihenfolge formatiert, dass zuerst das niedrigstwertige Bit 68 und zuletzt das höchstwertige Bit 69 auftritt.

Fig. 5 zeigt eine Darstellung von Datenworten entsprechend Fig. 4 wobei zwischen Datenworten W11, W12 und W13 eine zeitliche Verzögerung entsprechend der einem bzw. zwei oder mehr Bit zugeordneten Zeitdauer vorgesehen ist, was bewirkt, dass die Datenworte W11, W12 und W13 um ein bzw. zwei oder mehr Bit örtlich oder zeitlich versetzt dargestellt sind.

Die Wirkungsweise der Vorrichtung ist demnach wie folgt:

Digitalisierte Tonsignal triffen über die Eingänge 1 bis n ein und werden in den Verarbeitungseinheiten 10 bis 13 in an sich bekannter Weise so formatiert, dass das niedrigstwertige Bit zuerst und das höchstwertige Bit zuletzt ausgegeben wird. Dies ist durch eine entsprechende Auslesevorschrift aus einem Zwischenspeicher zu erreichen. Alle von den Verarbeitungseinheiten 10 bis 13 ausgegebenen oder eventuall auch alle eingegebenen Audiosignale werden mit dem ersten Taktsignal 67 synchronisiert, so dass jedes Bit in der Vorrichtung synchron behandelt wird, wie dies in den Fig. 4 und 5 dargestellt ist. Zudem erfolgt das Auslesen der Datenworte aus den Verarbeitungseinheiten 10 bis 13 wortsynchron, wie dies die Fig. 4 zeigt. Über die Bedienungseinheit 27 und die Steuerleitungen 28 wer-

15

25

den die einzelnen Ausgänge der Verarbeitungseinheiten 10 bis 13 angesteuert. Damit wird für jeden Ausgang einer Verarbeitungseinheit vorgegeben ob dort ein Audiosignal abgegeben wird und in welcher Stärke.

Damit empfängt nun jeder Summierer 17 bis 20 aus den Leitungen 101 bis 104 usw. Audiosignale die er summieren und anschliessend an seinen Ausgang 21 bis n abgeben muss. Dabei kann es auch sein, dass über einen Eingang mehrere Audiosignal in Serie geschaltet eintreffen. Solche Signale werden gleich behandelt wie ein einziges Signal. Nach dem Ausgang können sie aber parallel weitergegeben werden, wie dies für den Ausgang 21 und die parallelen Ausgänge 25 angedeutet ist.

Die Summierung der bitweise synchronisierten Audiosignale in den Summierern 17 bis 20 kann mit Hilfe der Fig. 2 erklärt werden. Je zwei Signale a und b liegen an den Eingängen 39 und 40, weitere zwei Signale b und c an den Eingängen 41 und 42. An den Eingängen 33, 34 und 35 liegt ein erstes Taktsignal für die bitweise Synchronisierung und an den Eingängen 36, 37 und 38 liegt ein weiteres Taktsignal an, das den Anfanng (oder das Ende) eines Datenwortes angibt und damit die Wortsynchronisation bewirkt. Das weitere Taktsignal ist dabei vom ersten Taktsignal abgeleitet. Dabei werden die Signale a und b im Zweibitaddierer 30 nach folgender Formel oder Instruktion summiert: (!a UND !b UND cy) ODER (!a UND b UND !cy) ODER (a UND b UND cy)

Dabei wird der Übertrag cy nach folgender Regel behandelt:

(a UND b UND !pr) ODER (a UND cy UND !pr) ODER (b UND cy UND !pr),

wobei pr ein angelegtes weiteres Taktsignal für das Wortende und !pr Fehlen eines solchen Signales bedeutet (!steht allg. für Fehlen des entspr. Signales). Die anderen Zweibitaddierer arbeiten nach dem gleichen Prinzip und ergeben immer aus zwei Eingangssignalen ein Ausgangssignal. So kann mit der gezeigten Struktur eine beliebige Anzahl Eingangssignale summiert werden. Diese Verarbeitung entspricht der Addition von mehrstelligen Zahlen wie sie im Kopf des Menschen oder bei grösseren Zahlen mit Hilfe einer Rechenmethode durchgeführt und in der Schule gelehrt wird. Das bedeutet, dass zuerst alle niedrigstwertigen Bit 68 addiert werden, wobei ein Übertrag gespeichert wird, so dass er bei der Addition der nächsthöheren Bit zugerechnet werden kann. Zuletzt werden die höchstwertigen Bit 69 untereinander addiert und, sofern vorhanden, der letzte Übertrag berücksichtigt. Die so summierten Datenströme verlassen den Summierer über den Ausgang 21. Dann können sie im Formatkonverter 24 beispielsweise so formatiert werden, dass nun das höchstwertige Bit im Datenwort vorausgeht. Oder der Datenstrom kann aufgeteilt werden und über mehrere Leitungen 25 parallel ausgegeben werden.

Die Eingangssignale können dabei in ihrem Wert

in den Verarbeitungseinheiten 10 bis 13 vor der Summierung verändert oder gewichtet werden. Dies kann aber auch in einem Verarbeitungselement 26 geschehen.

Ist das Verarbeitungselement 26 als Vorrichtung gemäss Fig. 3 ausgebildet, so wird ein Tonsignal über den Eingang 63 einerseits dem Multiplizierer 58 und andererseits der Verzögerungseinheit 65 zugeführt. Aus der Verzögerungseinheit 65 wird das Ausgangssignal sowohl dem Multiplizierer 57 als auch der weiteren Verzögerungseinheit 66 zugeführt. So sind die Signale, die an den Multiplizierern 56, 57 und 58 anlegen jeweils um ein Bit zueinander versetzt, was durch die Verzögerungseinheiten 65, 66 bewirkt wird. Parallel dazu liegen an den Multiplizierern 56, 57, 58 über die Eingänge 60, 62 und 64 auch je ein Bit eines Multiplikators oder Faktors an, mit dem das Signal im Eingang 63 multipliziert werden soll. So wird ein über den Eingang 63 eintreffendes Datenwort im Multiplizierer 58 mit dem ersten Bit des Faktors, im Addierer 57 mit dem zweiten Bit und im Addierer 56 mit dem dritten Bit des Faktors bitweise multipliziert. So entstehen drei zueinander um ein Bit versetzte Datenwörter, die im Summierer 40 summiert werden. Mit anderen Worten entsteht eine Situation, wie sie Fig. 5 zeigt, so dass die drei Datenworte W11, W12 und W13 nur noch bitweise summiert werden müssen. So soll ein Audiosignal 63 in mehrere gleiche parallele Signale 63, 61, 59 aufgeteilt und mit aufsteigender Verzögerung um je ein Bit verzögert werden. Dann soll das ursprüngliche Signal und die verzögerten Signale mit je einem Bit eines in einem digitalen Wert ausgedrückten Faktor addiert und anschliessend die resultierenden Signale bitweise zu einem veränderten Signal summmiert werden.

## Patentansprüche

- 1. Verfahren zum Mischen von digitalen Audio-Signalen aus einer ersten Anzahl Eingängen (1 bis m) in eine zweite Anzahl (21 bis n) Ausgänge, dadurch gekennzeichnet, dass die Datenworte der eingehenden Audio-Signale so zueinander geführt werden, dass die Datenbit in aufsteigender Reihenfolge mit dem niedrigstwertigen Bit voraus, in parallelen Datenströmen wort- und bitweise synchronisiert auftreten und bitweise summiert werden.

- 2. Verfahren nach Anspruch 1, dadurch gekennzeichnet, dass ein Audiosignal (63) in mehrere gleiche parallele Signale (63, 61, 59) aufgeteilt und mit aufsteigender Verzögerung um je ein Bit verzögert wird und dass das Signal (63) und die verzögerten Signale (61, 59) mit je einem Bit eines in einem digitalen Wert ausgedrückten Faktor addiert und anschliessend die resultierenden Signale (53; 54, 55) bitweise zu einem veränderten Signal summmiert werden (52).

- 3. Vorrichtung zum Mischen digitaler Audio-Signale mit einer ersten Anzahl m Eingängen (1, 2, 3, 4, 5, m) und einer zweiten Anzahl n Ausgängen (21, 22, 23, n), wobei mindestens ein Teil der Eingänge über je ein Verarbeitungselement (10 bis 13) mit mindestens einem Teil der n Ausgänge verbunden ist, dadurch gekennzeichnet, dass einem Ausgang ein Summierer (17, 18, 19, 20) vorgeschaltet ist, der mit mindestens einem Teil seiner Eingänge mit den Verarbeitungselementen (10 bis 13) verbunden ist.

- **4.** Vorrichtung nach Anspruch 3, dadurch gekennzeichnet, dass der Summierer zum bitweisen Summieren beginnend mit dem niedrigstwertigen Bit 15 ausgebildet ist.

- Vorrichtung nach Anspruch 3, dadurch gekennzeichnet, dass der Summierer aus mindestens einem Zwei- oder Mehrbitaddierer (32) aufgebaut 20 ist.

- 6. Vorrichtung nach Anspruch 3, dadurch gekennzeichnet, dass der Summierer aus mindestens drei Zwei-oder Mehrbitaddierern (30, 31, 32) aufgebaut 25 ist, die in Kaskade geschaltet sind.

- Vorrichtung nach Anspruch 3, dadurch gekennzeichnet, dass ein Verarbeitungselement (10 bis 13) aus einem digital arbeitenden Signalprozessor besteht.

- 8. Vorrichtung nach Anspruch 3, dadurch gekennzeichnet, dass ein Verarbeitungselement aus einem Summierer (51), mindestens einem Multiplizierer (56, 57, 58) und mindestens einer Verzögerungseinheit (65, 66) aufgebaut ist.

- Vorrichtung nach Anspruch 8, dadurch gekennzeichnet, dass die Verzögerungseinheit (65, 66), der Multiplizierer (56, 57) und der Summierer (51) für mindestens einen Eingang (53, 54) des Summierers in Serie geschaltet sind.

- Vorrichtung nach Anspruch 3, dadurch gekennzeichnet, dass ein oder mehrere Summierer (17, 18, 19, 20) einen Summenbus für ein digital arbeitendes Audio-Mischpult bilden.

55

## EUROPÄISCHER RECHERCHENBERICHT

Nummer der Anmeldung EP 98 10 0793

| EINSCHLÄGIGE DOKUMENTE                                   |                                                                                                                                                                                                                        |                                                                        |                                                                                                                       |                                                                                       |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Kategorie                                                | Kennzeichnung des Doku<br>der maßgeblic                                                                                                                                                                                | ments mit Angabe, soweit erforderlichen Teile                          | ch, Betrifft<br>Anspruch                                                                                              | KLASSIFIKATION DER<br>ANMELDUNG (Int.Cl.6)                                            |

| Α                                                        | FR 2 552 958 A (MO<br>* Seite 1, Zeile 1<br>Ansprüche 1,2 *                                                                                                                                                            | JLIN) 5.April 1985<br>- Seite 2, Zeile 24;                             | 1,3                                                                                                                   | H04H7/00                                                                              |

| А                                                        | EP 0 342 530 A (SIEMENS A.G. ÖSTERREICH) 23.November 1989 * Spalte 1, Zeile 1 - Spalte 4, Zeile 25; Anspruch 1; Abbildung 1 *                                                                                          |                                                                        | ,                                                                                                                     |                                                                                       |

| A                                                        | AT 389 784 B (SIEMENS AKTIENGESELLSCHAFT<br>ÖSTERREICH) 25.Januar 1990<br>* das ganze Dokument *                                                                                                                       |                                                                        | 1,3                                                                                                                   |                                                                                       |

| Α                                                        | EP 0 462 799 A (MATSUSHITA ELECTRIC INDUSTRIAL CO., LTD.) 27.Dezember 1991 * Seite 3, Zeile 1 - Zeile 47; Ansprüche 1,4,7; Abbildungen 2,3 *                                                                           |                                                                        | 1,3                                                                                                                   |                                                                                       |

| A                                                        |                                                                                                                                                                                                                        | ESSIONAL MIXING NEEDS"<br>CTRONIC ENGINEERING,<br>191,<br>1230856      | 1,3                                                                                                                   | RECHERCHIERTE SACHGEBIETE (Int.CI.6)                                                  |

| Der voi                                                  | rliegende Recherchenbericht wu                                                                                                                                                                                         | rde für alle Patentansprüche erstellt                                  |                                                                                                                       |                                                                                       |

|                                                          | Recherchenort                                                                                                                                                                                                          | Abschlußdatum der Recherche                                            |                                                                                                                       | Prüfer                                                                                |

|                                                          | DEN HAAG                                                                                                                                                                                                               | 11.Juni 1998                                                           | Del                                                                                                                   | Haan, A.J.                                                                            |

| X : von t<br>Y : von t<br>ande<br>A : techt<br>O : nicht | ATEGORIE DER GENANNTEN DOK<br>Desonderer Bedeutung allein betrach<br>Desonderer Bedeutung in Verbindung<br>ren Veröffentlichung derselben Kate<br>nologischer Hintergrund<br>schriftliche Offenbarung<br>chenliteratur | tet E : älteres Pate g mit einer D : in der Anme gorie L : aus anderen | g zugrunde liegende 7<br>ntdokument, das jedor<br>nmeldedatum veröffen<br>ldung angeführtes Do<br>Gründen angeführtes | heorien oder Grundsätze<br>ch erst am oder<br>tlicht worden ist<br>kument<br>Dokument |