(11) **EP 0 936 553 A3**

(12)

## **EUROPEAN PATENT APPLICATION**

(88) Date of publication A3: **22.09.1999 Bulletin 1999/38**

(51) Int Cl.6: G06F 12/08

(43) Date of publication A2: 18.08.1999 Bulletin 1999/33

(21) Application number: 99301052.9

(22) Date of filing: 15.02.1999

(84) Designated Contracting States:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE

**Designated Extension States:**

AL LT LV MK RO SI

(30) Priority: 17.02.1998 US 24394

(71) Applicant: International Business Machines

Corporation

Armonk, N.Y. 10504 (US)

(72) Inventors:

- Arimilli, Ravi Kumar Austin, Texas 78759 (US)

- Dodson, John Steven Pflugerville, Texas 78660 (US)

- Lewis, Jerry Don Round Rock, Texas 78681 (US)

- (74) Representative: Burt, Roger James, Dr. et al IBM United Kingdom Limited Intellectual Property Department Hursley Park Winchester Hampshire SO21 2JN (GB)

## (54) Cache coherency protocol with tagged state and historical information

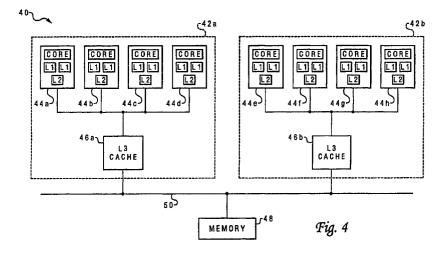

(57) A cache coherency protocol uses a "Tagged" coherency state to track responsibility for writing a modified value back to system memory, allowing intervention of the value without immediately writing it back to system memory, thus increasing memory bandwidth. The Tagged state can migrate across the caches (horizontally) when assigned to a cache line that has most recently loaded the modified value. Historical states relating to the Tagged state may further be used. The invention may also be applied to a multi-processor computer system having clustered processing units, such that the

Tagged state can be applied to one of the cache lines in each group of caches that support separate processing unit clusters. Priorities are assigned to different cache states, including the Tagged state, for responding to a request to access a corresponding memory block. Any tagged intervention response can be forwarded only to selected caches that could be affected by the intervention response, using cross-bars. The Tagged protocol can be combined with existing and new cache coherency protocols. The invention further contemplates independent optimization of cache operations using the Tagged state.

## **EUROPEAN SEARCH REPORT**

Application Number EP 99 30 1052

| Category                                | Citation of document with indication of relevant passages                                                                                                                                                                                             | n, where appropriate,                                                                                                     | Relevant<br>to claim                                            | CLASSIFICATION OF THE APPLICATION (Int.CI.6) |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------|

| X                                       | BORRILL P: "FUTUREBUS FOR CACHE DATA CONSISTENT" COMPUTER TECHNOLOGY REVIOUS Page 36, 38 XP000054499 ISSN: 0278-9647 * the whole document *                                                                                                           |                                                                                                                           | 1-7,9,10                                                        | G06F12/08                                    |

| X                                       | SWEAZY P ET AL: "A CLAS CACHE CONSISTENCY PROTOG SUPPORT BY THE IEEE FUTU PROCEEDINGS OF THE ANNUA SYMPOSIUM ON COMPUTER AN JUNE 2 - 5, 1986, NR. SY 414 - 423, INSTITUTE ON ELECTRONICS ENGINEERS XN * page 33, middle column 34, right-hand column, | COLS AND THEIR JREBUS", AL INTERNATIONAL RCHITECTURE, TOKYO, YMP. 13, PAGE(S) FELECTRICAL AND PO02039991 n, line 9 - page | 1-7,9,10                                                        |                                              |

| X                                       | "CACHING ON FUTUREBUS" ELECTRONIC ENGINEERING, vol. 60, no. 739, 1 July 1988 (1988-07-01 36 XP000046105 ISSN: 0013-4902 * page 416, left-hand color page 420, left-hand color, figure 3 *                                                             | olumn, paragraph 3                                                                                                        | 1-7,9,10                                                        | TECHNICAL FIELDS SEARCHED (Int.Cl.6) G06F    |

|                                         | The present search report has been dr                                                                                                                                                                                                                 | awn up for all claims                                                                                                     |                                                                 |                                              |

| Place of search  THE HAGUE              |                                                                                                                                                                                                                                                       | Date of completion of the search  3 August 1999                                                                           | Examiner  Ledrut, P                                             |                                              |

| X : part<br>Y : part<br>doc<br>A : tech | ATEGORY OF CITED DOCUMENTS  icularly relevant if taken alone icularly relevant if combined with another ument of the same category involgical backgroundwritten disclosure                                                                            | T : theory or principle E : earlier patent doc after the filing dat D : document cited in L : document cited fo           | ument, but publis<br>e<br>n the application<br>or other reasons |                                              |