## Europäisches Patentamt **European Patent Office**

Office européen des brevets

EP 0 936 569 A1 (11)

(12)

### EUROPÄISCHE PATENTANMELDUNG

(43) Veröffentlichungstag: 18.08.1999 Patentblatt 1999/33

(51) Int. Cl.<sup>6</sup>: **G06G 1/00**, G06G 7/20, G06G 7/22

(21) Anmeldenummer: 98102333.6

(22) Anmeldetag: 11.02.1998

(84) Benannte Vertragsstaaten:

AT BE CH DE DK ES FI FR GB GR IE IT LI LU MC **NL PT SE**

Benannte Erstreckungsstaaten:

AL LT LV MK RO SI

(71) Anmelder: Deutsche Telekom AG 53113 Bonn (DE)

(72) Erfinder: Huber, Klaus, Dr.-Ing. 64283 Darmstadt (DE)

#### (54)Verfahren und Schaltungsanordnung zur Frequenzvervielfachung

(57)Es werden ein Verfahren und eine Schaltungsanordnung zur Frequenzvervielfachung mit Hilfe von Tschebyscheffschen Polynomen angegeben. Die Frequenzvervielfacher lassen sich dadurch sehr einfach und in Modulbauweise realisieren, wodurch der Einsatz insbesondere in der Nachrichtechnik sehr preisgünstig wird. Die Tschebyscheffschen Polynome bzw. die zur schaltungstechnischen Implementierung erforderlichen Multiplizierer (7) und Summier- bzw. Subtrahierschaltungen (8) oder dergleichen lassen sich in integrierter Schaltungstechnik realisieren, die dann je nach äußerer Verdrahtung die unterschiedlichsten gewünschten Funktionen ausführen können. Als weitere Funktionen, die mit solch einem Chip leicht realisierbar sind, wird die Synthese beliebiger Funktionsverläufe durch Darstellung der Funktion mittels einer Tschebyscheff-Reihe oder die Verwendung der Funktion T<sub>n</sub>(x) als Verstärker mit dem Verstärkungsfaktor n für kleines x mit  $sin(nx) \approx nx$ , und ungerades n angegeben.

#### **Beschreibung**

[0001] Die Erfindung betrifft ein Verfahren und eine Schaltungsanordnung nach dem Oberbegriff des Patentanspruches 1 bzw. des Patentanspruches 3.

[0002] Verfahren zur analogen Frequenzvervielfachung sind in der Nachrichtentechnik und in der Computertechnik für verschiedene Zwecke bekannt. Außerdem sind für diese verschiedenen Zwecke auch Schaltungsanordnungen bekannt, die die Frequenzen von Sinus- und Cosinusschwingungen vervielfachen. Dabei ist der Schaltungsaufwand insbesondere bei Vielfachen, die nicht eine Zweierpotenz der Ausgangsfrequenz sind, erheblich, da je nach Realisierung noch zusätzliche Divisionsschaltungen benötigt werden. Derartige Schaltungen, die zum Beispiel in PLL-Technik ausgeführt sind, sind zum Beispiel in dem Buch von U. Tietze, Ch. Schenk, Halbleiterschaltungstechnik, Springer Verlag 1980, beschrieben. Die Tschebyscheffschen Polynomen n-ten Grades sind definiert durch die Gleichung  $T_n(\cos(\varphi)) = \cos(n\varphi)$ .

[0003] Die Tschebyscheffschen Polynome sind zum Beispiel beschrieben in I. Schur, "Arithmetisches über die Teschebyscheffschen Polynome", Gesammelte Abhandlungen Vol. III, Seiten 422 bis 453, Springer Verlag 1973.

[0004] Der Erfindung liegt die Aufgabe zugrunde, ein Verfahren und eine Schaltungsanordnung zur analogen Frequenzvervielfachung zu schaffen, die mittels einfacher und leicht kombinierbarer Bausteine die Frequenzvervielfachung erreichen und insbesondere die bisherigen Divisionsschaltungen vermeiden, wenn Vielfache einer Grundfrequenz erzeugt werden sollen, die nicht eine Zweierpotenz davon sind.

**[0005]** Die erfindungsgemäße Lösung für das Verfahren zur analogen Frequenzvervielfachung ist im Kennzeichen des Patentanspruches 1 charakterisiert.

**[0006]** Die erfindungsgemäße Lösung für die Schaltungsanordnung zur Frequenzvervielfachung ist im Kennzeichen des Patentanspruches 3 charakterisiert.

**[0007]** Weitere Merkmale bzw. Ausgestaltungen der Erfindung sind in der Beschreibung, im Patentanspruch 2 für das Verfahren und in den Patentansprüchen 4 bis 10 für die Vorrichtung angegeben.

[0008] Das erfindungsgemäße Verfahren bzw. die erfindungsgemäße Vorrichtung hat den Vorteil, daß durch von Tschebyscheffschen Polynomen abgeleitete Strukturen eine Frequenzvervielfachung erreicht wird, die mittels einfacher und leicht kombinierbarer Bausteine bzw. modularer Schaltungsstrukturen erreicht wird.

**[0009]** Gibt man zum Beispiel eine Cosinusschwingung als Eingangsgröße in  $T_n(X)$ , so erhält man am Ausgang die Cosinusschwingung mit n-facher Frequenz. Information zu Tschebyscheff Polynomen findet man zum Beispiel in Abramowitz, Stegun: Handbook of Mathematical Functions. Die ersten Tschebyscheff Polynome lauten:

$T_o(x) = 1$ ,  $T_1(x) = x$ ,  $T_2(x) = 2x^2 - 1$ , etc. entsprechend  $T_{n+1}(x) = 2xT_n(x) - T_{n-1}(x)$ . Sie lassen sich mit Multiplizierern und Addierern bzw. Subtrahierern realisieren. Für die Realisierung beliebiger n besonders hilfreich sind die beiden folgenden Beziehungen:

$$T_{n-m}(X) = T_n(T_m(X))$$

$$\mathsf{T}_{n+m}(\mathsf{x}) = 2 \cdot \mathsf{T}_m(\mathsf{x}) \cdot \mathsf{T}_n(\mathsf{x}) \cdot \mathsf{T}_{n-m}(\mathsf{x}).$$

[0010] Die Tschebyscheffschen Polynome sowie die zur schaltungstechnischen Implementierung erforderlichen Multiplizierer und Summierer bzw. Addier- bzw. Subtrahierschaltungen lassen sich in integrierter Schaltungstechnik realisieren, die dann je nach äußerer Verdrahtung bzw. Vernetzung die unterschiedlichsten gewünschten Funktionen ausführen können. Als weitere Funktionen, die mit solch einem Chip leicht realisierbar sind, wird an dieser Stelle die Synthese beliebiger Funktionsverläufe durch Darstellung der Funktion mittels einer Tschebyscheff-Reihe oder die Verwendung der Funktion  $T_n(x)$  als Verstärker mit dem Verstärkungsfaktor n für kleine x mit  $sin(nx) \approx nx$ , und ungerades n genannt.

**[0011]** Die Erfindung wird im folgenden anhand von in der Zeichnung dargestellten Ausführungsbeispielen näher beschrieben. In der Beschreibung, in den Patentansprüchen, der Zusammenfassung und in der Zeichnung werden die in der hinten angeführten Liste der Bezugszeichen aufgeführten Begriffe und die zugeordneten Bezugszeichen verwendet.

[0012] In der Zeichnung bedeuten:

35

55

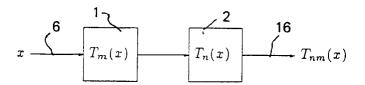

Fig. 1 eine Schaltungsanordnung zur Realisierung von  $T_{nm}(x)$ ;

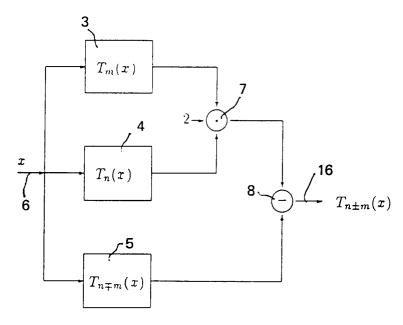

Fig. 2 eine Schaltungsanordnung zur Realisierung von  $T_{n+-m}(x)$ ;

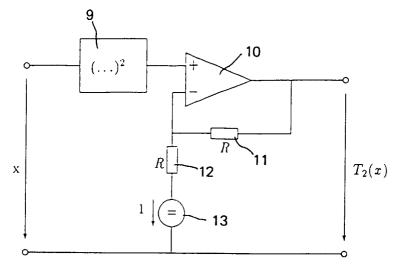

Fig. 3 eine Schaltung zur Realisierung von T<sub>2</sub>(x) und

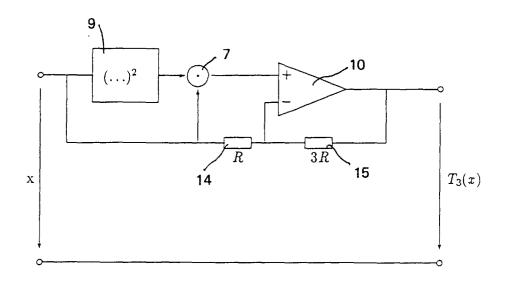

Fig. 4 eine Schaltung zur Realisierung von  $T_3(x)$ .

#### EP 0 936 569 A1

[0013] Zunächst soll die mathematische Grundlage für das Verfahren und die Schaltungsanordnung beschrieben werden. In den vorliegenden Lösungen werden von Tschebyscheff Polynomen abgeleitete Strukturen verwendet, mit denen mittels einfacher und leicht kombinierbarer Schaltungsbausteine eine beliebige Frequenzvervielfachung zu realisieren ist. Die Tschebyscheffschen Polynome n-ten Grades  $T_n(x)$  sind definiert durch die Gleichung

$T_{n}(\cos(\varphi)) = \cos(n\varphi), \tag{1}$

das heißt, gibt man eine Cosinusschwingung als Eingangsgröße in  $T_n(x)$ , so erhält man am Ausgang die Cosinusschwingung mit n-facher Frequenz. Informationen zu Tschebyscheff Polynomen findet man auch in Abramowitz, Stegun: Handbook of Mathematical Functions. Die ersten Tschebyscheff Polynome lauten:

$T_0(x) = 1$ ,  $T_1(x) = x$ ,  $T_2(x) = 2x^2 - 1$ , etc. Sie lassen sich mit Multiplizierern und Addierern bzw. Subtrahierern realisieren. Für die Realisierung beliebiger n besonders hilfreich sind die beiden folgenden Beziehungen

$$T_{n \cdot m}(x) = T_n(T_m(x)) \tag{2}$$

$T_{n+m}(x) = 2 \cdot T_m(x) \cdot T_n(x) - T_{n-m}(x)$  (3)

[0014] Die Schaltungen für die Gleichungen (2) und (3) sind in den Figuren 1 und 2 dargestellt.

[0015] Die auf dieser Basis aufgebaute und realisierte Schaltung für Gleichung (2) gemäß Fig. 1 besteht aus zwei hintereinandergeschalteten Tschebyscheffmodulen 1 und 2, wobei am Eingang des Tschebyscheffmoduls 1 die Eingangsgröße mit der Grundfrequenz liegt und am Ausgang des Tschebyscheffmoduls 2 die Ausgangsgröße mit der um den Faktor  $n \cdot m$  vervielfachten Frequenz. Die Realisierung der Gleichung (3) ist in Fig. 2 dargestellt. Diese Schaltung besteht aus den Tschebyscheffmodulen 3, 4 und 5, deren Eingänge alle die Eingangsgröße mit der Grundfrequenz zugeführt bekommen. Die Ausgänge der Tschebyscheffmodule 3 und 4 sind auf den Eingang eines Multiplizierers 7 geführt, an dessen weiteren Eingang eine 2 zur Multiplikation anliegt. Der Ausgang des Multiplizierers 7 wird mit dem Ausgang des Tschebyscheffmoduls 5 auf einen Subtrahierer 8 geführt, an dessen Ausgang dann die Funktion  $T_{n+m}(x)$  liegt, wenn im Tschebyscheffmodul 5 die Funktion  $T_{n+m}(x)$  realisiert ist und  $T_{n+m}(x)$ , wenn im Tschebyscheffmodul 5 die Funktion  $T_{n+m}(x)$  realisiert ist.

[0016] Zu jedem beliebigen Wert N läßt sich nun das Tschebyscheffmodul T<sub>N</sub>(x) aus den Schaltungen der Figuren 1 und 2 zusammensetzen. Dabei ergeben sich je nach N verschiedene Realisierungsmöglichkeiten. Die jeweilige Realisierung ist abhängig von den Kosten jeweils vom Fachmann auszuwählen. Im folgenden wird der Einfachheit halber eine Realisierung mit Hilfe von Operationsverstärkern angenommen. Die angegebenen Schaltungen sind nicht notwendigerweise für jeden Anwendungsfall gleich gut geeignet. Je nach Kosten der benötigten Bauteile sind gegebenenfalls andere Realisierungen ohne weiters möglich und im gegebenen Fall günstiger. Mit Hilfe der hier angegebenen Gleichungen kann der Entwurf aber leicht modifiziert und auf den entsprechenden Anwendungsfall zurechtgeschnitten werden

**[0017]** Unter Benutzung der in der Schaltungstechnik bekannten Operationsverstärkerschaltungen erhält man für die ersten nicht trivialen Polynome  $T_2(x)$  und  $T_3(x)$  die in den Figuren 3 bzw. 4 dargestellte schaltungsmäßige Realisierung bzw. Implementierung. Bezeichnet man mit  $K_n$  die Kosten der Realisierung der Funktion  $T_n(x)$ , so ist aus Fig. 3 zu ersehen, daß das mit Operationsverstärkern implementierte Polynom  $T_2$  die Kosten von einem Quadrierer 9, einem Operationsverstärker 10, zwei Widerständen 11 und 12 sowie einer Konstantspannungsquelle 13 verursacht. Damit ist gezeigt, daß durch eine derartige Schaltung eine preisgünstige Realisierung von Schaltungen zur Frequenzvervielfachung möglich ist.

[0018] Die Schaltung nach Fig. 4 für die Realisierung der Funktion  $T_3(x)$  besteht wiederum aus einem Quadrierer 9, einem nachgeschalteten Multiplizierer 7 sowie einem Operationsverstärker 10, dessen Ausgangssignal über einen Spannungsteiler, bestehend aus den Widerständen 14 und 15, auf seinen Eingang rückgekoppelt ist. Am Ausgang dieser Schaltung stehen die entsprechenden elektrischen Größen der Funktion  $T_3(x)$  zur Verfügung.

[0019] Die für die Synthese beliebiger  $T_n(x)$  nützlichen Formeln sind die angegebenen Formeln (2) und (3).

[0020] Diese Formeln lassen sich, wie bereits gesagt, schematisch als Schaltungen gemäß Figuren 1 und 2 darstellen. Als Spezialfall von Gleichung (3) erhält man für m=1 die wohlbekannte Formel  $T_{n+1}(x)=2x \cdot T_n(x)-T_{n-1}(x)$  und für m=n die Formel  $T_{2n}(x)=2 \cdot T_n(x)^2-1$ . Durch Umstellen von Gleichung (3) erhält man auch  $T_{n-m}(x)=2 \cdot T_m(x) \cdot T_{n+m}(x)$ , die ebenfalls durch eine Schaltung nach Fig. 2 realisiert werden kann. Wir bezeichnen mit  $K(S_1)$  und  $K(S_2)$  die Kosten für Schaltungen  $S_1$  und  $S_2$  nach Fig. 1 und Fig. 2 ohne die darin enthaltenen Tschebyscheffmodule. Entsprechend der Schaltungen erhält man bei Realisierung mit Operationsverstärkern:

$$K(S_1) = 0$$

K(S<sub>2</sub>) = Kosten für Multiplizierer, 1 OV, 2 Widerstände

35

5

15

55

#### EP 0 936 569 A1

**[0021]** Zu jeder dieser Schaltungen läßt sich nun in einfacher Weise die Kostenrechnung aufstellen. Ein Beispiel zeigt die Vorgehensweise am besten. Um  $T_{17}(x)$  zu bestimmen, kann man setzen:

$$T_{17}(x) = 2 \cdot T_8(x) \cdot T_9 - x = 2 \cdot T_2(T_2(x)) \cdot T_3(T_3(x)) - x$$

und erhält  $K_{17} = 3K_2 + 2K_3 + K(S_2)$ , da die Kosten  $K(S_1)$  zur Realisierung von Gleichung (2) hier gleich Null angesetzt sind.

#### Liste der Bezugszeichen

#### [0022]

5

10

25

30

35

40

45

50

55

|    | 1 bis 5 | Tschebyscheffmodule     |

|----|---------|-------------------------|

|    | 6       | Schaltungseingang       |

| 15 | 7       | Multiplizierer          |

|    | 8       | Subtrahierer            |

|    | 9       | Quadrierer              |

|    | 10      | Operationsverstärker    |

|    | 11,12   | Widerstände             |

| 20 | 13      | Konstantspannungsquelle |

|    | 14,15   | Widerstände             |

|    | 16      | Schaltungsausgang       |

#### Patentansprüche

1. Verfahren zur Frequenzvervielfachung, dadurch gekennzeichnet,

daß Schaltungsmodule Tschebyscheffsche Polynome n-ter Ordnung (T<sub>n</sub>(x)) realisieren,

daß die Tschebyscheffschen Polynome definiert sind durch  $T_n(\cos(\omega t)) = \cos(n\omega t)$ , das heißt  $T_1(x) = 1$ ,  $T_2(x) = 2x^2 - 1$  und  $T_{n+1}(x) = 2xT_n(x) - T_{n-1}(x)$  für n = 1,2,3 ... und welche arithmetische Eigenschaften haben

daß die Schaltungsmodule zu einem modularen Schaltungsverband bzw. zu einer modularen Schaltungsstruktur zusammengeschaltet werden mit Hilfe der Beziehungen  $T_{nm}(x) = T_n(T_m(x))$  und  $T_{n+m}(x) = T_n(x)T_m(x) - T_{n-m}(x)$ , und

daß am Eingang des Tschebyscheffschen Schaltungsmoduls ( $T_n(x)$ ) eine Cosinusschwingung bestimmter Frequenz anliegt, die im Tschebyscheffschen Schaltungsmodul Cosinusschwingungen mit n-facher Frequenz generiert, die am Ausgang des Schaltungsmoduls zur Verfügung stehen.

2. Verfahren nach Patentanspruch 1, dadurch gekennzeichnet,

daß anstatt der Tschebyscheffschen Polynome allgemeiner definierte Funktionen im Schaltungsmodul realisiert werden, die sich durch die Darstellung von  $T_n(x) = (1/2)((x+(x^2-1)^{1/2})^n + (x-(x^2-1)^{1/2})^n)$  ergeben, wobei n eine rationale oder reelle Zahl sein kann.

3. Schaltungsanordnung zur Durchführung des Verfahrens nach Patentanspruch 1 oder 2, dadurch gekennzeichnet,

daß Schaltungsmodule zur Realisierung von Tschebyscheffschen Polynomen der entsprechenden Ordnungen zur Frequenzvervielfachung strukturiert miteinander gekoppelt bzw. zusammengeschaltet sind,

daß an den Eingängen (6) als Eingangsgrößen (x) Sinus-/Cosinusschwingungen anliegen, die in einem Schaltungsmodul oder in einem strukturierten Schaltungsmodulverband entsprechend den realisierten Tschebyscheffschen Polynomen Schwingungen erzeugen, die auf den Ausgangsleitungen (16) zur Verfügung stehen.

4. Schaltungsanordnung nach Patentanspruch 3, dadurch gekennzeichnet,

#### EP 0 936 569 A1

daß die Schaltungsmodule als programmierbare oder fest programmierte Halbleiterchips mit arithmetischen Eigenschaften zur Realisierung der Tschebyscheffschen Polynome ausgeführt sind.

5. Schaltungsanordnung nach einem der Patentansprüche 3 oder 4, dadurch gekennzeichnet,

daß ein Schaltungsmodul zur Realisierung des Tschebyscheffschen Polynoms  $T_m(x)$  (1), an dessen Eingang (6) die Eingangsgröße (x) anliegt, mit einem weiteren Schaltungsmodul zur Realisierung des Tschebyscheffschen Polynoms  $T_n(x)$  (2), an dessen Ausgang (16) die Funktion  $T_{nm}(x)$  steht, zusammengeschaltet ist.

10 6. Schaltungsanordnung nach einem der Patentansprüche 3 oder 4, dadurch gekennzeichnet,

daß zur Realisierung des Tschebyscheffschen Polynoms  $T_{n\pm m}(x)$  drei Tschebyscheffmodule (3 bis 5) über einen gemeinsamen Eingang (6) die Eingangsgröße x zugeführt bekommen,

daß zwei der Schaltungsmodule (3 und 4) ausgangsseitig über einen Multiplizierer (7), an dessen weiteren Eingang eine Zwei anliegt, miteinander gekoppelt sind und

daß der Ausgang des Multiplizierers (7) mit dem Ausgang des dritten Schaltungsmoduls (5) über einen Subtrahierer (8) zum Ausgang 16 miteinander verbunden sind.

7. Schaltungsanordnung nach einem der Patentansprüche 3 bis 6, dadurch gekennzeichnet,

daß zur Realisierung der Funktion  $T_2(x)$  ein Quadrierer (9) mit dem Eingang eines Operationsverstärkers (10) verbunden ist,

daß mit dem zweiten Eingang des Operationsverstärkers (10) über einen Widerstand (12) eine Konstantstromquelle (13) verbunden ist und

daß der Ausgang und der zweite Eingang des Operationsverstärkers (10) über einen weiteren Widerstand (11) miteinander verbunden sind.

8. Schaltungsanordnung nach einem der Patentansprüche 3 bis 6, dadurch gekennzeichnet,

daß zur Realisierung der Tschebyscheffschen Funktion  $T_3(x)$  ein Quadrierer (9) mit dem Eingangssignal (x) beaufschlagt ist,

das außerdem über einen Widerstand (14) mit einem Eingang des Operationsverstärkers (10) und mit einem Eingang eines Multiplizierers (7) verbunden ist, an dessen Eingang das Ausgangssignal des Quadrierers (9) anliegt und dessen Ausgang mit dem zweiten Eingang des Operationsverstärkers (10) verbunden ist und

daß der Ausgang des Operationsverstärkers (10) über einen weiteren Widerstand (15) rückgekoppelt ist.

9. Schaltungsanordnung nach einem der Patentansprüche 3 bis 8, dadurch gekennzeichnet,

daß die Schaltungsmodule als programmierte bzw. programmierbare Halbleiterchips oder dergleichen ausgeführt sind.

10. Schaltungsanordnung nach einem der Patentansprüche 3 bis 7, dadurch gekennzeichnet,

daß die Schaltungsstrukturen aus Schaltungsmodulen (zum Beispiel 3 bis 5), Multiplizierern (7), Subtrahierern (8) und gegebenenfalls Operationsverstärkern (10) sowie erforderliche Strom- bzw. Spannungsquellen und Zu- und Ableitungen als integrierte Ein-/Mehrchipausführung bestehen.

55

5

15

20

25

30

35

40

45

50

FIG. 1

FIG. 2

FIG. 3

FIG. 4

### EUROPÄISCHER RECHERCHENBERICHT

Nummer der Anmeldung EP 98 10 2333

| Kategorie                              | Kennzeichnung des Dokuments m                                                                                                                                                                                                                                                                          |                                                                                                                      | Betrifft                                                                                       | KLASSIFIKATION DER                                                          |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| x                                      | VON HUBER K: "On appli<br>Chebyshev polynomials i<br>FREQUENZ, JANFEB. 199<br>SCHIELE & SCHON, GERMAN<br>Bd. 52, Nr. 1-2, Seite<br>XP002067845<br>ISSN 0016-1136<br>* Seite 11, linke Spalt<br>Seite 12, rechte Spalte<br>Abbildungen 1-4; Tabell<br>* Seite 13, linke Spalt<br>rechte Spalte, letzter | cations of n circuit design" 8, FACHVERLAG Y, n 11-13, e, letzter Absatz - , Absatz 3; e 1 * e, letzter Absatz -     | 1,3-10<br>2                                                                                    | G06G1/00<br>G06G7/20<br>G06G7/22                                            |

| A                                      | GB 2 086 627 A (BEI ELE<br>12. Mai 1982<br>* Zusammenfassung; Abbi                                                                                                                                                                                                                                     | CTRONICS)                                                                                                            | 1,2                                                                                            |                                                                             |

|                                        |                                                                                                                                                                                                                                                                                                        |                                                                                                                      |                                                                                                | RECHERCHIERTE<br>SACHGEBIETE (Int.Cl.6)                                     |

| Der vo                                 |                                                                                                                                                                                                                                                                                                        |                                                                                                                      |                                                                                                |                                                                             |

|                                        | rliegende Recherchenbericht wurde für                                                                                                                                                                                                                                                                  | alle Patentansprüche erstellt                                                                                        |                                                                                                |                                                                             |

|                                        | Recherchenort                                                                                                                                                                                                                                                                                          | Abschlußdatum der Recherche                                                                                          |                                                                                                | Prüfer                                                                      |

|                                        | DEN HAAG                                                                                                                                                                                                                                                                                               | 12. Juni 1998                                                                                                        | Led                                                                                            | rut, P                                                                      |

| X : von<br>Y : von<br>ande<br>A : tech | ATEGORIE DER GENANNTEN DOKUMENTE<br>besonderer Bedeutung allein betrachtet<br>besonderer Bedeutung in Verbindung mit eine<br>ren Veröffentlichung derselben Kategorie<br>nologischer Hintergrund<br>tschriftliche Offenbarung                                                                          | T : der Erfindung zug<br>E : älteres Patentdok<br>nach dem Anmeld<br>er D : in der Anmeldung<br>L : aus anderen Grün | runde liegende l<br>aument, das jedo<br>ledatum veröffen<br>angeführtes Do<br>nden angeführtes | Theorien oder Grundsätze<br>ch erst am oder<br>tlicht worden ist<br>kurnent |

# ANHANG ZUM EUROPÄISCHEN RECHERCHENBERICHT ÜBER DIE EUROPÄISCHE PATENTANMELDUNG NR.

EP 98 10 2333

In diesem Anhang sind die Mitglieder der Patentfamilien der im obengenannten europäischen Recherchenbericht angeführten Patentdokumente angegeben.

Die Angaben über die Familienmitglieder entsprechen dem Stand der Datei des Europäischen Patentamts am

Diese Angaben dienen nur zur Unterrichtung und erfolgen ohne Gewähr.

12-06-1998

| Im Recherchenbericht<br>angeführtes Patentdokument | Datum der<br>Veröffentlichung | Mitglied(er) der<br>Patentfamilie                             | Datum der<br>Veröffentlichung                        |

|----------------------------------------------------|-------------------------------|---------------------------------------------------------------|------------------------------------------------------|

| GB 2086627 A                                       | 12-05-1982                    | US 4359688 A<br>CA 1176713 A<br>DE 3142213 A<br>JP 57104304 A | 16-11-1982<br>23-10-1984<br>09-06-1982<br>29-06-1982 |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

|                                                    |                               |                                                               |                                                      |

Für nähere Einzelheiten zu diesem Anhang : siehe Amtsblatt des Europäischen Patentamts, Nr.12/82