# **Europäisches Patentamt European Patent Office** Office européen des brevets

EP 0 966 039 A2 (11)

(12)

# **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

22.12.1999 Bulletin 1999/51

(51) Int. Cl.6: H01L 23/532

(21) Application number: 99300284.9

(22) Date of filing: 15.01.1999

(84) Designated Contracting States:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE

Designated Extension States:

**AL LT LV MK RO SI**

(30) Priority: 15.06.1998 JP 18337698

(71) Applicants:

· KISHIMOTO SANGYO CO., LTD. Osaka-shi, Osaka (JP)

· Daisankasei Co.,Ltd. Tokyo (JP)

(72) Inventors:

· Kimoto, Hisao, Kishimoto Sangyo Co.Ltd. Osaka-shi, Osaka (JP)

· Mochizuki, Tsutomu Ichihara-shi, Chiba (JP)

(74) Representative:

Wise, Stephen James et al c/o RAWORTH, MOSS & COOK, Raworth House, 36 Sydenham Road Croydon, Surrey CR0 2EF (GB)

#### (54)Insulating film for semiconductor device and semiconductor device

(57)To provide an insulating film having a low dielectric constant and performance sufficient as an interlayer insulating film of a semiconductor device, and a semiconductor device using the insulating film.

An insulating film for a semiconductor device used as an interlayer insulating film of a semiconductor device, the insulating film consisting essentially of poly- $\alpha$ , $\alpha$ -difluoroparaxylylene and having a relative dielectric constant of from 2.1 to 2.7. An insulating film for a semiconductor device used as an interlayer insulating film of a semiconductor device, the insulating film consisting essentially of poly- $\alpha$ ,  $\alpha$ -difluoroparaxylylene and exhibiting a step coverage of from 0.4 to 0.9. An insulating film for a semiconductor device capable of being filled in a gap, the insulating film consisting essentially of poly- $\alpha, \alpha$ -difluoroparaxylylene, having a ratio (D/L) of a depth (D) and an opening width (L) of 1 or more.

EP 0 966 039 A2

# Description

15

20

35

40

45

50

55

**[0001]** The present invention relates to an interlayer insulating film formed on a production process of a semiconductor device, and a semiconductor device using the interlayer insulating film.

**[0002]** Miniaturization of circuit patterns, low power consumption and high-speed operation of semiconductor devices proceed, and therefore low capacitance and low resistance of the circuit patterns are spread. As one means of ensuring high-speed and normal operation of the circuit, there has been considered to lower a dielectric constant of an interlayer insulating film.

[0003] An insulating film containing a carbon atom, such as an amorphous carbon film, an organic compound insulating film containing a fluorine atom, and an inorganic insulating film have drawn attention as an insulating film having a low dielectric constant. However, must satisfy the following requirements to become a substitute of a silicon oxide insulating film, which is most frequently employed at the present. That is, they must have:

1) Low dielectric constant,

and also the following characteristics, which are basically required for a semiconductor insulating film:

- 2) Good adhesion,

- 3) Good workability,

- 4) Good in step coverage

- 5) Good in gap fill property,

- 6) Low water absorption

- 7) Capability of coping with a damascene process (embedded wiring).

However, no material has been known that has a low dielectric constant and satisfies all the characteristics required for an interlayer insulating film of a semiconductor device.

**[0004]** An object of the invention is to provide an insulating film having a low dielectric constant and exhibiting performance that is sufficient as an interlayer insulating film of a semiconductor device, and also provide a semiconductor device using the insulating film.

- 30 [0005] The object of the invention can be accomplished by the following constitutions of the invention.

- (1) An insulating film for a semiconductor device used as an interlayer insulating film of a semiconductor device, the insulating film consisting essentially of poly- $\alpha$ ,  $\alpha$ -difluoroparaxylylene and having a relative dielectric constant of from 2.1 to 2.7.

- (2) An insulating film for a semiconductor device used as an interlayer insulating film of a semiconductor device, the insulating film consisting essentially of poly- $\alpha$ ,  $\alpha$ -difluoroparaxylylene and exhibiting a step coverage of from 0.4 to 0.9

- (3) An insulating film for a semiconductor device capable of being filled in a gap, the insulating film consisting essentially of poly- $\alpha$ ,  $\alpha$ -difluoroparaxylylene, having a ratio (D/L) of a depth (D) and an opening width (L) of 1 or more.

- (4) An insulating film for a semiconductor device as in one of the constitutions (1) to (3), wherein a shape of the insulating film is capable of being patterned by irradiation of oxygen plasma.

- (5) A semiconductor device comprising a semiconductor substrate having thereon at least two conductive layers through an interlayer insulating film, the interlayer insulating film is an insulating film as in one of the constitutions (1) to (4).

[0006] In the accompanying drawings:-

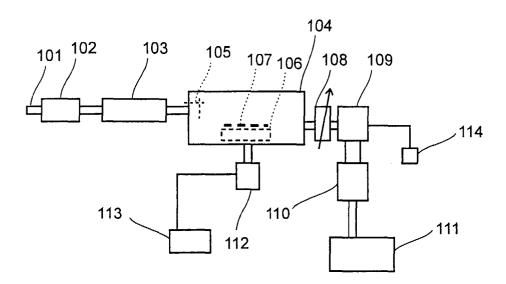

Figure 1 is a diagrammatic front view of a constitutional example of a LPCVD (Low Pressure Chemical Vapor Deposition) apparatus used for formation of an insulating film of the invention.

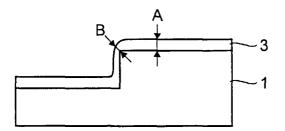

Figure 2 is an explanatory diagram of calculation of a step coverage.

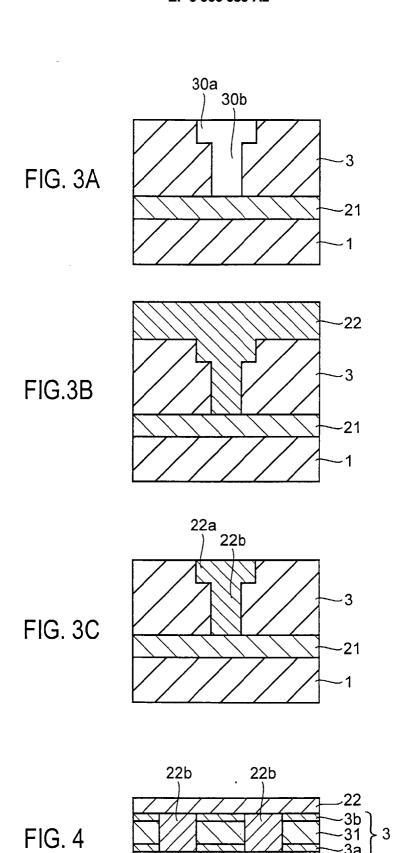

Figures 3A to 3C are cross sectional views showing a damascene process.

Figure 4 is a cross sectional view showing an embodiment in which an insulating film of the invention is used as an interlayer insulating film of a semiconductor device.

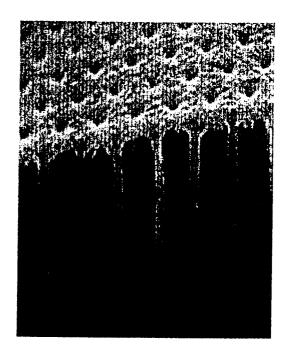

Figure 5 is a scanning electron micrograph showing a cross section of a substrate having an insulating film of the invention formed thereon.

Figure 6 is a scanning electron micrograph showing a cross section of a substrate having an insulating film of the invention formed thereon.

2

Figure 7 is a scanning electron micrograph showing a cross section of a substrate having an insulating film of the invention formed thereon.

Figure 8 is a scanning electron micrograph showing a cross section of a substrate having an insulating film of the invention formed thereon.

Figure 9 is a graph showing an infrared spectrum of an insulating film of the invention for determining water absorption.

Figure 10 is a scanning electron micrograph showing a cross section of a substrate having an insulating film of the invention formed thereon.

10 **[0007]** The insulating film of the invention consists essentially of poly- $\alpha$ , $\alpha$ ,-difluoroparaxylylene represented by the following structural formula (I):

$$+CH_2$$

$CF_2$   $n$

20

25

30

35

15

5

**[0008]** In the structural formula (I), n represents a polymerization degree. The polymerization degree n of the poly- $\alpha$ ,  $\alpha$ -difluoroparaxylylene used in the invention is generally 1,000 or more, and particularly 5,000 or more.

[0009] The poly- $\alpha$ , $\alpha$ -difluoroparaxylylene can be formed by the CVD (chemical vapor deposition) process using tetrafluoro-[2,2]-paracyclophane represented by the following structural formula (II) as a raw material:

$$CF_2$$

$CH_2$

$CH_2$

$CF_2$

**4**0

[0010] The synthesis of poly- $\alpha$ , $\alpha$ -difluoroparaxylylene represented by the structural formula (I) by the CVD (chemical vapor deposition) process using tetrafluoro-[2,2]-paracyclophane represented by the following structural formula (II) as a raw material has been known as disclosed in Unexamined Published Japanese Patent Application No. 9-25252. However, the publication only discloses the effect in that a coating film can be formed that is excellent in heat resistance and is expected to have good balance in all the physical properties. In the invention, on the other hand, a poly- $\alpha$ , $\alpha$ -difluoroparaxylylene film is produced under various conditions and examined for properties and characteristics, and thus it has been found that the film is suitable as an interlayer insulating film for a semiconductor device.

o m is be th ge

[0011] A constitutional example of a LPCVD apparatus used for formation of an insulating film of the invention is shown in Figure 1. On producing the insulating film, tetrafluoro-[2,2]-paracyclophane in the form of a dimer as a raw material is put in an evaporation chamber 102 through an inlet 101. In the evaporation chamber 102, the raw material is evaporated to be a dimer gas. The evaporation chamber 102, and a decomposition chamber 103 and a sample chamber 104 connected thereto have different vacuum degrees by a turbo molecular pump 110 and a rotary pump 111, and therefore the dimer gas is introduced into the decomposition chamber 103 and heated by a heater to be a monomer gas, which is then introduced into the sample chamber 104. In the sample chamber 104, a polymerization reaction occurs on the surface of a sample 107 placed on a susceptor 106, and a polymer is accumulated to form an insulating film. The susceptor 106 can be rotated by a motor 112, and its temperature can be controlled by a cooler 113. The sample 107 is generally a semiconductor wafer. The monomer gas that does not contribute to the polymerization and accumulation is introduced to a cooling trap 109 through a vacuum conductance valve 108. The cooling trap 109 is cooled

by a cooler 114, and the monomer gas is solidified therein and recovered.

**[0012]** In LPCVD apparatus having such a constitution, the characteristics and the formation rate of the insulating film can be controlled by adjusting the opening ratio of a shutter 105 for exhaust adjustment provided between the sample chamber 104 and the decomposition chamber 103, the opening ratio of the vacuum conductance valve 108, and the rotation number and the temperature of the susceptor 106.

[0013] In the invention, the conditions for accumulation of the insulating film are preferably controlled to the following ranges:

| _ | - |  |

|---|---|--|

| 7 | L |  |

| • | _ |  |

15

| Heating temperature in the evaporation chamber 102:                        | 80 to 180°C                                                      |

|----------------------------------------------------------------------------|------------------------------------------------------------------|

| Heating temperature in the decomposition chamber 103:                      | 600 to 750°C                                                     |

| Pressure on accumulation of the insulating film in the sample chamber 104: | 1 to 10 Pa, preferably 3 to 6 Pa                                 |

| Rotation number of the susceptor 106:                                      | 0 to 10 rpm                                                      |

| Temperature of the susceptor 106:                                          | -60 to 60°C, preferably -60 to 0°C, more preferably -60 to -20°C |

20

[0014] When the temperature of the susceptor 106 (temperature of the substrate) is low, it is preferred since the growing rate of the film is high, the film is liable to be dense, and the yield is improved. The pressure on accumulation of the insulating film in the sample chamber 104 is important for forming a dense insulating film. When the pressure is too high, it is difficult to form a dense insulating film. On the other hand, when it is too low, the growing rate of the film becomes low, and the productivity is deteriorated.

**[0015]** By controlling the accumulation conditions to the above-described ranges, characteristics suitable as an interlayer insulating film for a semiconductor device as shown in the following (1) to (7) can be obtained:

- (1) The dielectric constant can be in the range of from 2.1 to 2.7. The dielectric constant of a silicon oxide insulating film is generally 3.9, and the dielectric constant of a silicon oxide insulating film containing fluorine is generally from 3.3 to 3.6.

- (2) A strong adhesive power to a metallic conductive layer, an inorganic insulating layer and a semiconductor substrate can be realized.

- (3) The shape of the insulating film can be worked by ashing by oxygen plasma irradiation.

- (4) The step coverage can be in the range of from 0.4 to 0.9.

- (5) Good gap fill property can be obtained.

- (6) Water absorption can be lowered.

- (7) A damascene process on the production of a semiconductor device can be applied.

40

30

35

[0016] The above-described characteristics are described in more detail.

[0017] As described in item (1), the dielectric constant of the insulating film of the invention can be low. Thus, when it is applied for an interlayer insulating film of a semiconductor device having a fine circuit pattern, the capacitance is lowered, and high-speed and normal operation can be ensured. Specifically, it is suitable as an interlayer insulating film in a device of a wiring design rule of a minimum line width of 1  $\mu$ m or less.

**[0018]** As described in item (3), the insulating film of the invention can be removed by ashing by oxygen plasma irradiation. Specifically, because sufficient selectivity can be ensured between a resist mask and a hard mask on the oxygen plasma ashing, the insulating film can be easily patterned by ashing.

[0019] The calculation method of the step coverage in item (4) is explained with reference to Figure 2. Figure 2 shows a state in that an insulating film 3 is accumulated on a substrate 1 having a step structure. The step coverage is expressed by B/A, where A represents the thickness of the insulating film 3 at the upper surface of the step, and B represents the minimum thickness of the insulating film 3 at the edge part of the step.

[0020] The gap fill property shown in item (5) shows the capability of filling in a gap, such as a groove and a hole present between electrode layers. When the aspect ratio of the gap becomes high, it is generally difficult to fill the insulating film in the gap without forming any defect such as voids or pinholes. Therefore, the insulating film that can be filled in a gap having a high aspect ratio is excellent in gap fill property. The aspect ratio is expressed by D/L, where D represents the depth of the gap, and L represents the opening width of the gap. When the gap is in the form of a hole, the opening width L means its via-hole diameter (short diameter). The insulating film of the invention has high gap fill prop-

erty due to high flowability on film formation, and can be filled with substantially no defect, for example, in a gap having a D/L of 1 or more. Furthermore, it can be easily filled in a gap having a high aspect ratio of from 3 to 10. It can be applied to a fine wiring pattern where L is  $0.25 \, \mu m$  or less, and also can be applied to an extremely fine wiring pattern where L is from  $0.1 \, to \, 0.18 \, \mu m$ .

[0021] Since the insulating film of the invention is excellent in step coverage and gap fill property, an insulating film having a uniform thickness with no voids can be formed even in a step part and an uneven part having a narrow opening and a high aspect ratio. The insulating film excellent in gap fill property is advantageous on embedding of a capacitance between capacitor electrodes and flattening of various steps in a semiconductor device.

[0022] Because the insulating film of the invention has an extremely low water absorption as shown in item (6), it substantially does not adsorb water when it is allowed to stand in the air after formation. Since the insulating film immediately after forming by the CVD process is soft, it is generally hardened by annealing, and water absorption after annealing is also extremely low. Accordingly, the water absorption does not change by heat history. The annealing is generally conducted by heating at a temperature range of from 300 to 500°C for from 5 to 60 minutes.

[0023] The process of the damascene process shown in item (7) is explained with reference to Figures 3A, 3B and 3C. As shown in Figure 3A, a conductive layer (first wiring layer) 21 is formed on a substrate 1, and an insulating film 3 as an interlayer insulating film is formed. The insulating film 3 is etched by the photolithographic process to form a groove 30a in which a second wiring layer is filled, and a via hole 30b in which a conductive material connecting the first wiring layer and the second wiring layer is filled. As shown in Figure 3B, a conductive layer 22 is formed on the insulating film 3 by sputtering or electrolytic plating. At this time, the conductive material is filled in the groove 31a and the via hole 30b. As shown in Figure 3C, the conductive layer 22 is etched by chemical mechanical polishing or reverse sputtering to remove the part present on the insulating film 3, so as to obtain the state where a second wiring layer 22a and a via conductive material 22b are embedded in the insulating film 3. Thus, the damascene process can be applied to the insulating film of the invention. This means that a metallic wiring can be embedded by a photolythographic process, and the insulating film 3 functions as a stopper when the conductive layer 22 is etched by chemical mechanical polishing or reverse sputtering.

[0024] A constitutional example of an embodiment in which the insulating film of the invention is used as an interlayer insulating film of a semiconductor device is shown in Figure 4. In Figure 4, a conductive layer (first wiring layer) 21, an insulating film 3 and a conductive layer (second wiring layer) 22 are formed on a substrate 1 in this order, and the conductive layer 21 and the conductive layer 22 are electrically connected by a via conductive material 22b filled in a contact hole piercing the insulating film 3. The insulating film 3 is an interlayer insulating film, and, in the embodiment shown in Figure 4, has a constitution in that inorganic insulating films 3a and 3b are accumulated as sandwiching an insulating film 31 of the invention. The inorganic insulating films 3a and 3b also has functions as a mask for pattern forming, a reinforcing layer for adhesiveness and an anti-hygroscopic film, and generally comprise silicon oxide or silicon nitride. The conductive layer 21 in contact with the substrate 1 generally comprises AI, and the conductive layer 22 not in contact with the substrate 1 generally comprises Cu, Al-Cu or Al-Si-Cu. The via conductive material 22b generally comprises W or Cu since it must have gap fill property. The thickness of the conductive layers 21 and 22 is about from 50 to 500 nm, that of the inorganic insulating films 3a and 3b is about from 50 to 200 nm, and that of the insulating film 31 of the invention is about from 200 to 500 nm. The diameter of the via conductive material 22b is generally from 100 to 500 nm.

[0025] In an interlayer insulating film using SOG (spin on glass), a laminated structure where an SOG film is sand-wiched by inorganic insulating films has been known. However, since the SOG film absorbs moisture in the SOG laminated structure, moisture is released from the SOG film when wiring (via conductive material) is formed in the adjacent via hole. Due to such moisture release, W absorbs moisture, and conductive failure sometimes occurs. On the other hand, because the insulating film of the invention is extremely low in water absorption, such conductive failure is difficult to occur.

**[0026]** In the constitutional example shown in Figure 4, while the conductive layers (wiring layers) has a 2-layer structure, the insulating film of the invention can be applied to a constitution having 3 or more conductive layers. The inorganic insulating films 3a and 3b are not necessary and can be provided depending on necessity.

[0027] The production process of tetrafluoro-[2,2]-paracyclophane represented by the structural formula (II) used on forming the insulating film of the invention by the CVD process is not particularly limited, and it can be synthesized according to the following route as shown in Unexamined Published Japanese Patent Application No. 9-25252.

[0028] [2,2]-Paracyclophane represented by the structural formula (III) used as a starting raw material in this synthesis route is available from Daisan Kasei Co., Ltd. The starting raw material is reacted with N-bromosuccinic imide in an inert solvent in the presence of a peroxide catalyst, under irradiation of an ultraviolet ray, or under the combination use of a peroxide catalyst and ultraviolet ray irradiation, to obtain tetrabromo-[2,2]-paracyclophane represented by the structural formula (IV). Diketone-[2,2]-paracyclophane represented by the structural formula (V) is obtained by reacting tetrabromo-[2,2]-paracyclophane represented by the structural formula (IV) with sodium acetate or silver acetate in an acetic acid solvent. By reacting diketone-[2,2]-paracyclophane represented by the structural formula (V) with a fluorination agent such as tetrafluoro sulfur and diethylaminosulfur trifluoride (DAST), tetrafluoro-[2,2]-paracyclophane represented by the structural formula (III) as the objective compound can be obtained.

On the reaction obtaining tetrabromo-[2,2]-paracyclophane represented by the structural formula (IV) from [2,2]-paracyclophane represented by the structural formula (IV) is also formed according to the following scheme:

CBr<sub>2</sub>

$$CH_2$$

$CH_2$   $CH_2$

35

The brominated compound represented by the structural formula (VI) can be separated by utilizing difference in solu-

bility in the solvent.

[0029] Embodiments of the present invetion will now be described in the following examples.

# **EXAMPLE 1**

[0030] The insulating film of the invention was produced and its dielectric constant was measured.

**[0031]** Tetrafluoro-[2,2]-paracyclophane represented by the structural formula (II) used as a raw material of the CVD process was produced according to the method described in Unexamined Published Japanese Patent Application No. 9-25252.

[0032] Poly- $\alpha$ , $\alpha$  -difluoroparaxylylene represented by the structural formula (I) was accumulated on a substrate having a flat surface by using a vacuum CVD apparatus having a constitution shown in Figure 1. The conditions of accumulation were as follows:

15

20

30

35

5

| Heating temperature in the evaporation chamber 102:                        |  |

|----------------------------------------------------------------------------|--|

| Heating temperature in the decomposition chamber 103:                      |  |

| Pressure on accumulation of the insulating film in the sample chamber 104: |  |

| Temperature of the susceptor:                                              |  |

[0033] The accumulation time was 30 minutes. After accumulation, annealing was conducted at 350°C for 30 minutes. As a substrate, a copper substrate and a p-type semiconductor Si wafer were used. After forming an insulating film having a thickness of 1  $\mu$ m on the substrates, an Al electrode was continuously formed by sputtering, to obtain samples for measurement.

[0034] The samples for measurement were subjected to measurement of capacitance between the Al electrode and the copper substrate or between the Al electrode and the p-type semiconductor Si wafer with a 1-MHz C-V plotter. As a result, the dielectric constant of the insulating film was in the range of from 2.1 to 2.7.

# **EXAMPLE 2**

[0035] The adhesive power of the insulating film was measured. By using an Si wafer as a substrate, an insulating film (thickness: 220 nm) of the invention was formed and annealed under the same conditions as in Example 1. An adhesive tape was adhered on the insulating film and then peeled off, but the insulating film was not peeled.

# **EXAMPLE 3**

[0036] The oxygen plasma ashing was conducted on the insulating film.

[0037] An insulating film (thickness: 560 nm) of the invention was formed on an Si wafer under the same conditions as in Example 1, and after accumulation, annealing was conducted at 350°C for 75 minutes. After a mask was formed by photoresist, it was placed on a substrate stage of a plasma asher, and oxygen plasma ashing was conducted under the following conditions:

45

50

| Oxygen gas flow amount: | 90 SCCM                              |

|-------------------------|--------------------------------------|

| Vacuum degree:          | 8 Pa                                 |

| RF power:               | 4.1 Watt/cm <sup>2</sup> (13.56 MHz) |

| Ashing rate:            | 113.3 nm/min                         |

[0

[0038] After ashing, the insulating film was removed according to the mask pattern, and burning flaw was not observed on the insulating film after ashing.

# **EXAMPLE 4**

[0039] The step coverage and the gap fill property of the insulating film were measured.

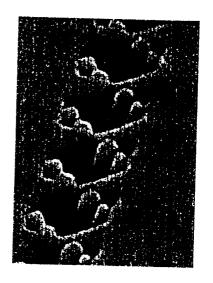

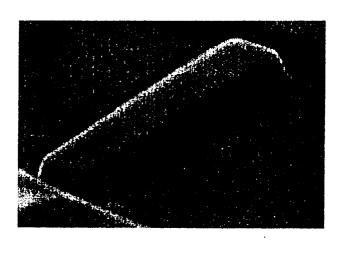

[0040] An insulating film (thickness: 250 nm) of the invention was formed on an Si wafer having a via hole having an opening diameter of 0.18 µm and an aspect ratio of 8, to fill the insulating film in the via hole. The conditions for accumulation of the insulating film were the same as in Example 1. After forming the insulating film, the substrate was cut at a face perpendicular to the main plane of the substrate. Al was deposited on the cut surface, which was then observed by a scanning electron microscope. A scanning electron micrograph thus obtained is shown in Figure 5, and an enlarged view thereof is shown in Figure 6. In Figures 5 and 6, a part having a high brightness is the insulating film. It is understood from these figures that the insulating film of the invention is filled in the via hole having a small opening diameter and a large aspect ratio without voids.

**[0041]** The insulating film of the invention was formed on a substrate having a surface of a step structure containing complicated unevenness. The conditions for accumulation of the insulating film were the same as in Example 1. Scanning electron micrographs after the formation of the insulating film are shown in Figures 7 and 8. It is understood from these figures that in the insulating film, a bridge connecting protrusions of the unevenness is not observed, and the formation of voids is not observed.

# **EXAMPLE 5**

[0042] Water absorption of the insulating film was measured.

[0043] The insulating film (thickness: 220 nm) of the invention was formed on an Si substrate under the same conditions as in Example 1. The resulting samples for measurement were allowed to stand in the air (23°C, 65%RH) for 48 hours. They were then annealed in an electric furnace in a nitrogen atmosphere for 30 minutes. The annealing temperature was 300°C, 350°C or 400°C. They were then further allowed to stand in the air for 48 hours. A part of samples was not subjected to the annealing but continuously allowed to stand in the air for 96 hours.

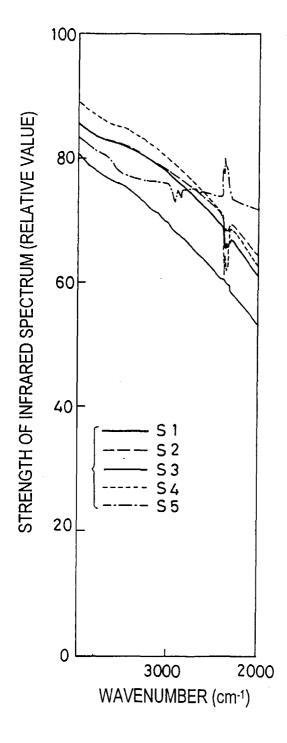

**[0044]** The insulating film of the samples was measured for infrared spectrum to determine the change in water absorption. The results are shown in Figure 9. The heat history corresponding to the spectra S1 to S4 is as follows:

S1: Continuously allowed to stand in the air

30 S2: Annealing temperature of 300°C

S3: Annealing temperature of 350°C

S4: Annealing temperature of 400°C

The spectrum S5 is for an aluminum base of an infrared spectroscope.

[0045] It is understood from Figure 9 that change in wave shape of an OH group (appearing near 3,300 cm<sup>-1</sup>) due to water absorption is not observed in all the insulating films having any heat history. Accordingly, the insulating film of the invention exhibits substantially no water absorption immediately after the film formation and after suffering heat history by annealing.

# 40 EXAMPLE 6

[0046] The insulating film of the invention was applied to the damascene process.

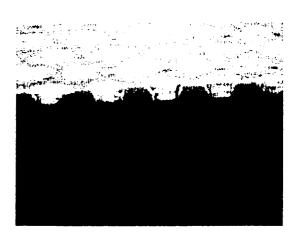

[0047] An insulating film (thickness: 350 nm) of the invention was formed on an Si wafer under the same conditions as in Example 1, and subjected to annealing under the same conditions as in Example 1. After forming a via hole in the insulating film, a Cu conductive layer was formed on the insulating film by sputtering. The diameter of the via hole was 0.25  $\mu$ m. The Cu conductive layer was then etched by chemical mechanical polishing. As a result, the polishing was stopped at the surface of the insulating film, and a state, in which a copper plug having a flat surface was filled in the via hole of the insulating film, was obtained. The scanning electron micrograph after polishing is shown in Figure 10.

[0048] In the present invention, poly-α,α-difluoroparaxylylene is applied to an interlayer insulating film of a semiconductor device. Accordingly, the capacitance coupling is lowered, and high-speed and normal operation can be ensured in a semiconductor device having a fine circuit pattern.

# **Claims**

An insulating film for a semiconductor device used as an interlayer insulating film of a semiconductor device, said insulating film consisting essentially of poly-α, α-difluoroparaxylylene and having a relative dielectric constant of from 2.1 to 2.7.

EP 0 966 039 A2 2. An insulating film for a semiconductor device used as an interlayer insulating film of a semiconductor device, said insulating film consisting essentially of poly- $\alpha$ ,  $\alpha$ -difluoroparaxylylene and exhibiting a step coverage of from 0.4 to 0.9. 3. An insulating film for a semiconductor device capable of being filled in a gap, said insulating film consisting essentially of poly- $\alpha$ ,  $\alpha$ -difluoroparaxylylene, having a ratio (D/L) of a depth (D) and an opening width (L) of 1 or more. 4. An insulating film for a semiconductor device as claimed in one of claims 1 to 3, wherein a shape of said insulating film is capable of being patterned by irradiation of oxygen plasma. 5. A semiconductor device comprising a semiconductor substrate having thereon at least two conductive layers through an interlayer insulating film, said interlayer insulating film is an insulating film as claimed in one of claims 1

5

10

15

20

25

30

35

40

45

50

55

FIG. 1

FIG. 2

FIG. 5

400 nm

FIG. 6

200 nm

FIG. 7

$1^{-}\mu$  m

FIG. 8

$1 \mu \text{ m}$

FIG. 9

FIG. 10

200 nm