# Europäisches Patentamt European Patent Office Office européen des brevets

(11) **EP 1 021 045 A1**

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

19.07.2000 Bulletin 2000/29

(21) Application number: 99250009.0

(22) Date of filing: 12.01.1999

(51) Int. Cl.<sup>7</sup>: **H04N 7/52**, H04B 1/66

(84) Designated Contracting States:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE

**Designated Extension States:**

AL LT LV MK RO SI

(71) Applicant:

DEUTSCHE THOMSON-BRANDT GMBH 78048 Villingen-Schwenningen (DE)

(72) Inventor: Schreiber, Ulrich 30827 Garbsen (DE)

(74) Representative:

Hartnack, Wolfgang, Dipl.-Ing.

Deutsche Thomson-Brandt GmbH

European Patent Operations

Karl-Wiechert-Allee 74

30625 Hannover (DE)

# (54) Method for processing and apparatus for encoding audio or video frame data

(57) For broadcasting purposes a multi-channel audio encoder board has been designed. Input time stamps (ITS) are generated which become linked at least in one input processing stage with frames of said audio data to be encoded, wherein the input time stamps or time stamps derived from the input time stamps remain linked with the correspondingly processed frame data (COE) in the different processing stages in the processing, but are at least in the last processing stage replaced by output time stamps. In each of theses stages the corresponding time stamp information linked with current frame data to be processed is regarded in order to control the overall delay of the processing.

Fig.2

#### Description

[0001] The invention relates to a method for processing and to an apparatus for encoding audio or video frame data.

**Background**

5

15

25

30

45

[0002] For broadcasting purposes a 4-stereo-channel real time MPEG audio encoder board has been designed. Such encoders can be realised using DSPs (Digital Signal Processor) wherein the processing as well as input and output interfaces is distributed over several DSPs. The processing is block oriented. For every new block of e.g. 1152 samples the related bitstream part is generated. As processing time for the processing blocks is not constant, and because several processing blocks on each DSP might compete for execution at any time instant, the total processing delay can vary significantly.

A requirement may be that the encoder is able to operate with different encoding parameters because MPEG, allows e.g. various sample frequencies and overall data rates.

Invention

- **[0003]** The total burden of the real time processing is distributed by means of multi-threading to each DSP and to the software equivalent of FIFO buffers carrying one or more frames or blocks of data, i.e. the encoder in principle consists of a chain of software FIFOs alternating with processing blocks (denoted threads) between the encoder input and output. The following problems need to be solved for a real time processing system:

- a) The total input to output delay should either be constant or better be definable (within the given memory constraints) for both, external and internal requirements. Enforcing a minimum delay will assure that enough processing time even for the worst case (an input data sequence resulting in maximum processing time) is available without temporary underflow of the output buffer (consider start with low delay time and afterwards increased processing time).

- b) A sufficiently simple and reliable way for controlling this delay is required for serviceability.

**[0004]** It is one object of the invention to disclose a method for processing audio or video frame data in which processing the delay between different processing stages as well as the overall delay can be adapted, particularly when a presentation of audio data together with the related video is required. This object is achieved by the method disclosed in claim 1.

35 **[0005]** It is a further object of the invention to disclose an apparatus for encoding audio data which utilises the inventive method. This object is achieved by the apparatus disclosed in claim 5.

**[0006]** Normally the audio or video frames are processed in an encoder in subsequent different stages, for example conversion to frequency coefficients in a first stage and bit allocation and quantisation in a further stage. In a path in parallel to the first stage the (psychoacoustic) masking is calculated.

In the invention the overall input to output delay is controlled by applying a time stamp based mechanism related to a system time base. Upon entering into the system, input data, e.g. per frame or block of data, are stamped with the present system time, i.e. an input time stamp ITS. This time stamp is then passed along together with the main data through the processing stages, e.g. in the format of a linked data field. Somewhere during the processing the intended output time for an output frame or block of data is calculated, using in principle the calculation

OTS = ITS + DELAY,

wherein OTS is an output time stamp. OTS is then used by the output stage to control that the output data are output at the intended time.

[0007] Additionally, encoding parameters required for a specific processing path can be added to the input streams for the audio channels by linking them with the associated audio data and by storage in the various buffers together with its audio data, i.e. the corresponding encoding parameters are kept linked with the audio data to be encoded throughout the encoding processing in the different data streams and data paths. Preferably the original encoding parameters assigned to the processing paths become converted to a different format in order to minimise the required word length and/or to facilitate easy evaluation in the related processing stages. Thereby each data stream can be processed with the correct parameter set without waiting for finishing encoding of the old data stream and for reset and loading of new parameters before starting encoding of a new data stream with new parameters.

[0008] The invention can also be used for audio or video decoding with a corresponding inverse order of processing

stages.

10

15

25

30

35

[0009] In principle, the inventive method is suited for processing audio or video frame data which are processed in succeeding different processing stages wherein input time stamps are generated which become linked at least in one input processing stage with frames of said audio or video data to be encoded, and wherein said input time stamps or time stamps derived from said input time stamps remain linked with the correspondingly processed frame data in said different processing stages in the processing but are at least in the last processing stage replaced by output time stamps denoting the presentation time, and wherein in each of theses stages the corresponding time stamp information linked with current frame data to be processed is regarded in order to control the overall delay of the processing.

[0010] Advantageous additional embodiments of the inventive method are disclosed in the respective dependent claims.

**[0011]** In principle the inventive apparatus is suited for encoding audio frame data which are processed in succeeding different processing stages, and includes:

- means for generating time stamp information including input time stamps and output time stamps;

- means for linking time stamp information with frames of said audio data or processed audio data, respectively;

- means for converting time domain samples into frequency domain coefficients, to the input of which means buffer means are assigned;

- means for calculating masking properties from said time domain samples, to the input of which means buffer means are assigned;

- means for performing bit allocation and quantisation of the coefficients under the control of the output of said masking calculating means, to the input of which bit allocation and quantisation means buffer means are assigned;

- means (AES-EBU\_A) for controlling presentation of the final output data at or at about a time corresponding to said output time stamps,

- wherein said input time stamps become linked at least for one input processing stage with frames of said audio data to be encoded and said input time stamps or time stamps derived from said input time stamps remain linked with the correspondingly processed frame data in said conversion means, in said masking calculating means and in said bit allocation and quantisation means, but at least in the last processing stage in the encoding processing are replaced by output time stamps, and wherein in each of theses stages the corresponding time stamp information linked with current frame data to be processed is regarded in order to control the overall delay of the encoding processing.

Advantageous additional embodiments of the inventive apparatus are disclosed in the respective dependent claims.

#### **Drawings**

[0012] Embodiments of the invention are described with reference to the accompanying drawings, which show in:

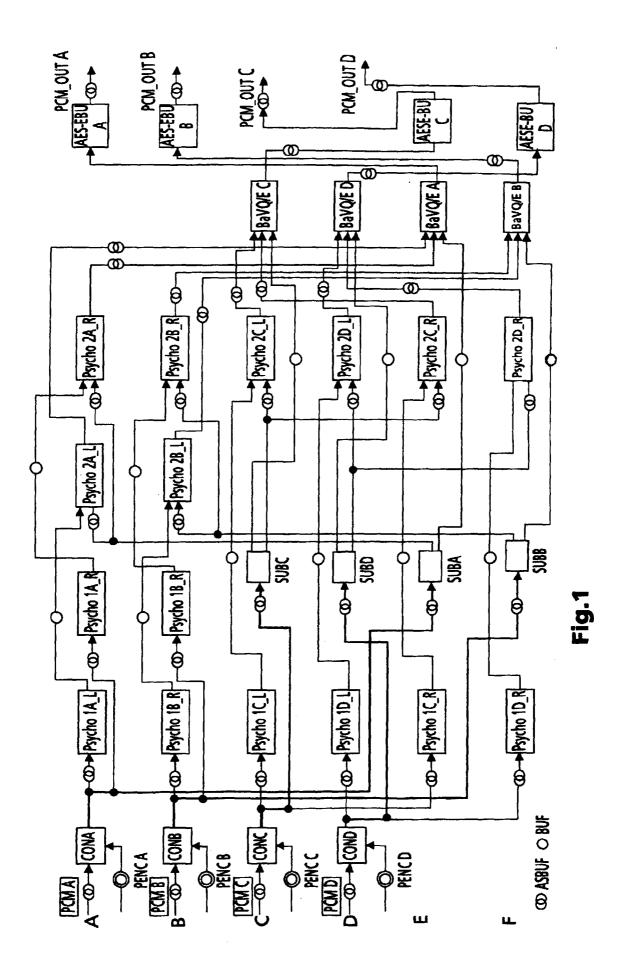

- Fig. 1 functional block diagram of a 4-channel audio encoder;

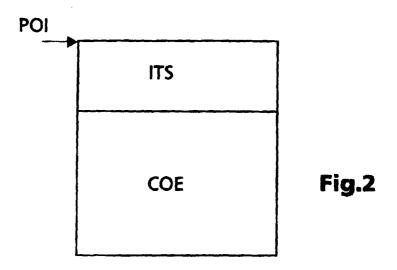

- Fig. 2 linked data field including audio data to be encoded and associated input time stamp data;

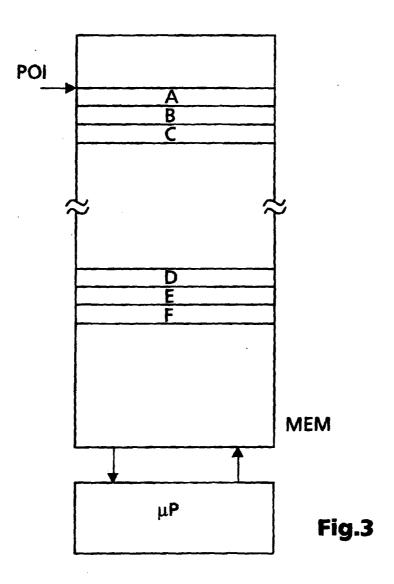

- 40 Fig. 3 microprocessor with memory including linked data fields.

#### **Exemplary embodiments**

- [0013] The audio encoder in Fig. 1 receives four stereo PCM input signals PCMA, PCMB, PCMC and PCMD. E.g. MPEG audio data are frame based, each frame containing 1152 mono or stereo samples. The encoder operating system of Fig. 1 may include six DSPs (not depicted) for the encoding of the four MPEG channels. These DSPs form a software encoder which includes the technical functions depicted in Fig. 1. A suitable type of DSP is for example ADSP 21060 or 21061 or 21062 of Analog Devices. As an alternative, the technical functions depicted in Fig. 1 can be realised in hardware.

- 50 Synchronisation of the software running on the six DSPs, or on corresponding hardware, is achieved using FIFO buffers wherein each buffer is assigned to one or some specific frames. This means that at a certain time instant a current frame as well as previous frames, the number of which depends from the quantity of available buffers, are present in the processing stages.

- Between some of the stages asynchronous buffers ASBUF are inserted which allow asynchronous write and read operations. Between other stages synchronous buffers BUF are sufficient. The PCM input signals PCMA, PCMB, PCMC and PCMD each pass via an asynchronous buffer to a respective converter CONA, CONB, CONC and COND. In such converter an integer-to-floating representation conversion of the audio samples to be encoded may take place. It is also possible that the encoder processes integer representation audio samples. In such converter also one or more kinds of

energy levels in a frame may be calculated, e.g. energy of all samples of the frame or average energy of the samples of a frame. These energy values may be used in the subsequent psychoacoustic processing.

In addition, in such converter the possibly adapted encoding parameters can become linked with the frame audio data. In respective parameter encoders PENCA, PENCB, PENCC and PENCD the original encoding parameters may be converted as described above and then fed to CONA, CONB, CONC and COND, respectively.

[0014] Via asynchronous buffers the output data of CONA, CONB, CONC and COND are fed in parallel to subband filters SUBA, SUBB, SUBC and SUBD and to first left and right channel psychoacoustic calculators Psycho1A\_L, Psycho1A\_R, Psycho1B\_L, Psycho1B\_R, Psycho1C\_L, Psycho1C\_R, Psycho1D\_L and Psycho1D\_R, respectively. The subband filters divide the total audio spectrum into frequency bands, possibly using FFT, and may calculate the maximum or scale factor of the coefficients in a frequency band or subband. Within the frequency bands a normalisation may be carried out. The subband filters take into account the above time stamp information and possibly the relevant encoding parameters read from the corresponding upstream asynchronous buffer.

The first psychoacoustic calculators perform an FFT having a length of e.g. 1024 samples and determine the current masking information. Each first psychoacoustic calculator can be followed by a second psychoacoustic calculator Psycho2A\_L, Psycho2A\_R, Psycho2B\_L, Psycho2B\_R, Psycho2C\_L, Psycho2C\_R, Psycho2D\_L and Psycho2D\_R, respectively, which evaluates the maximum or scale factor values previously calculated in the subband filters. The first and second psychoacoustic calculators take into account the above time stamp information and possibly relevant encoding parameters read from the corresponding upstream asynchronous buffers.

The output signals of Psycho2A\_L, Psycho2A\_R, Psycho2B\_L, Psycho2B\_R, Psycho2C\_L, Psycho2C\_R, Psycho2D\_L and Psycho2D\_ R are used in bit allocators and quantisers Bal/Q/E\_A, Bal/Q/E\_B, Bal/Q/E\_C and Bal/Q/E\_D, respectively, for determining the number of bits allocated and the quantisation the audio data coefficients coming from the associated subband filter via a buffer. It is also possible to calculate in the second psychoacoustic calculators in addition what is being calculated in the first psychoacoustic calculators and thereby to omit the first psychoacoustic calculators. Finally, the outputs of Bal/Q/E\_A, Bal/Q/E\_B, Bal/Q/E\_C and Bal/Q/E\_D pass through an asynchronous buffers and output interfaces AES-EBU\_A, AES-EBU\_B, AES-EBU\_C, ABS-EBU\_D, respectively, which deliver the encoder stereo output signals PCM\_Out\_A, PCM\_Out\_B, PCM\_Out\_C, PCM\_Out\_D, respectively. The output interfaces may correspond to IEC 958.

**[0015]** A video encoder includes the following stages: block difference stage, DCT (discrete cosine transform), quantisation and in the feedback loop inverse quantisation, inverse DCT, motion compensated interpolation the output of which is input to the block difference stage, wherein the output of the quantisation is possibly VLC (variable length coding) encoded and buffered before final output and the buffer filling level is used to control the quantisation in such a way that encoding artefacts are masked as far as possible.

**[0016]** In the invention the following elements are required:

- a system time base supplying a system time, that delivers unique values for all comprised input and output stages;

- hardware and/or software mechanisms that relates system time base and input data to obtain sufficiently precise input time stamps (ITS);

- hardware and/or software mechanisms that relates the system time base with the data output to obtain sufficiently precise output according to the output time stamps (OTS).

**[0017]** These elements are used in the following way:

35

40

45

50

55

- a) Per input interface of the system, input data are related to the system timer, i.e. an input time stamp ITS along with the incoming data is obtained and assigned to the data frames. For example, the system time of the sampling moment of the first sample of a sampled audio data block or frame is used therefore.

- b) In the case of multiple inputs, the input data blocks can be realigned across the channels by the time information given by the input time stamps.

- Example 1: multichannel audio inputs distributed over several two-channel interfaces.

- Example 2: bitstream outputs of multiple stereo encoders shall be multiplexed into an MPEG TS (transport stream) with a well-defined time relation across the channels, i.e. equal delay possibility.

- c) From input time stamps ITS and the intended overall delay DELAY output time stamps OTS for the output data are calculated.

- In the easiest processing case where one output data block per input data block is calculated by the system, the intended output time of each output block is given by OTS(n) = ITS(n) + DELAY, n = 0,1,2... denoting the data block number

In the case where per input data block several output data blocks or even a non-integer number of output blocks is

to be generated, the OTS for each of the output blocks can be interpolated according to the corresponding time ratios. An example is the MPEG encoder 1152 samples input, or an MPEG PES packet with one or more ESPs (elementary stream packets), and the MPEG TS transport stream wherein the packets have a length of 188 Bytes, i.e. for each sample frame 3 to 7 TS packets are required for transmission.

d) Each output interface examines the output data blocks, as supplied to the output buffer by the processing stages, for their related OTS in relation to the present system time. If OTS is indicating a time instant that has already passed the output data block can be discarded or can be output immediately, depending on the application. If the OTS is pointing to a future time instant the output stage will wait until that time instant has come and during the wait time can either output nothing or a defined filling pattern.

5

10

15

30

**[0018]** A couple of related mechanisms are available which can be used in different combinations as required for the I/O process to be implemented.

In an example minimum hardware scenario the system makes use of a single hardware timer, which is typically already part of each DSP, in combination with some kind of regular or controlled output driver software activation. The rest of the delay control is then executed by the DSP. In principle two timer functions are required:

- A 'getTime()' function, that allows the software to ask for the actual system time. Upon reception (DMA or INT based) of the beginning or the end of each input data block the getTime() function can be used to obtain the ITS for that block.

- The output function may need a certain delay before sending an output block for which the corresponding processing has finished. This can either be done in a polling manner, i.e. by cyclic control of the actual system time vs. OTS if some kind of cyclic activation is available, or by a specific timer-based delay function that issues an interrupt after a definable delay 'interruptAfter(DELAY)' or 'threadActivityAfter (DELAY)' function.

- The single hardware timer, operating as a backward counter with interrupt at zero, and the input and output DMA block-complete interrupts which are build-in functions of the DSPs, are used.

- The single hardware timer can provide the functions 'interruptAfter(DELAY)' and 'getTime()', wherein for the latter function the subsequent delay times loaded to the timer are summed up to obtain a continuos system time and wherein several 'interruptAfter(DELAY)' functions can run in parallel.

- [0019] In the case of a multi-DSP system with each DSP implementing it's own timer, but distributing inputs and outputs with delay requirements between them across different DSPs, there is a problem of timer synchronicity. This problem can be solved by a special cyclic interrupt signal (e.g. of 10ms length) that is applied to all DSPs in the system and that is used to resynchronise the system times. The counter output word may have the format iiii.ffff, wherein iiii is interpreted as integer part and ffff is interpreted as fractional part. Every 10ms iiii is incremented by '1'. This event is transmitted to the DSPs and is counted therein. The maximum manageable value for DELAY depends on the word length of iiii. Thereby the interrupt indicates the moment of resynchronisation and during the interrupt period a master value iiii for the time is transmitted from one master DSP to all other DSPs. At this time instant ffff is set to zero.

- [0020] While the delay control described in above example scenario requires minimum hardware only and thus leaves most of the job to (cheaper and more flexible) software, the disadvantage is that the delay time accuracy is limited by e.g. interrupt latency times, maximum interrupt disable times and, in case of a multi-DSP system, bus arbitration delays. If the achieved accuracy is not sufficient, hardware enhancements can be used that make the process of obtaining ITS relative to system time and output at OTS relative to system time more accurate. A combined solution with software determining the rough point in time and special hardware establishing the exact point in time will achieve a compromise between required DSP reaction time (tends to be slow compared to hardware) and hardware complexity (tends to be more complex the longer the time periods are).

- **[0021]** A theoretical overflow beginning at the buffers related to the last processing stages and proceeding to the buffers related to the front processing stages is prevented by handshake between the DSPs.

- **[0022]** Fig. 2 shows a data field including audio samples or audio coefficients COE for a frame or block. To these samples or coefficients an input time stamp information ITS is linked or assigned. An address pointer POI indicates the begin of the input time stamp information ITS. Beginning at the second processing stage ITS can be replaced by (ITS + DELAY) and PCR (MPEG program clock reference) wherein DELAY is the user-defined delay. At the last processing stages ITS or (ITS + DELAY) can be replaced by OTS.

- The MPEG program clock reference PCR is a 33bit word clock representing a 90kHz clock frequency.

- Additionally, encoding or decoding parameters including for instance mode information (mono, stereo, dual, joint stereo), sample rate and data rate information, length of the data field and/or type of MPEG layer can be linked to COE. **[0023]** In Fig. 3 a microprocessor or DSP μP is shown together with its memory MEM. In the memory some data fields A to F are depicted which correspond to data fields as shown in Fig. 2. E.g. data fields A, B and C may correspond to data fields of three succeeding audio frames in one of the data paths of Fig. 1. Data field A may include other ITS,

(ITS+DELAY) or OTS information or encoding parameters than data fields B and C. The address of the begin of data field B can be calculated by adding the length of data field A to POI.

The software running on  $\mu P$  can use the following example commands in C-language for constructing the data fields according to Fig. 2:

```

typedef struct {

10

int bitrate index

int sampling frequency

15

} layer;

20

"struct" may also contain time stamp information.

25

#define FRAMESIZE 1152

/*1152 is a decimal number*/

30

typedef struct {

35

layer info

40

float PCMBuf[FRAMESIZE]

} FloatBuffer L Type

```

**[0024]** The inventive delay control can also be applied for single DSP systems and for any other kind of real time processing.

[0025] In simplified applications, e.g. in an AC-3 decoder, computing a single data frame after reception with the real time constraint that the processing time for each block must be shorter than the frame period is an often used approach. This approach can be extended to a solution with more distributed processing including splitting into several subsequent processing stages, eventually distributed over several DSPs. In this case each processing stage can be forced into a well defined 'time slot', where for each processing stage the processing time must be shorter than the time slot length. In contrast to the solution described first, instead of a single time constraint there would be one time constraint per time slot/processing stage.

**[0026]** The invention has the following advantages:

5

45

55

· freely choosable delay, including implementation of user selectable delay. The delay may vary between a two-frame

- period (48ms) and e.g. 1.5sec;

- software dominated implementations as well as hardware enhanced implementations for improved delay time precision or reduced jitter are possible;

- single (minimum) delay time parameter constraining the real time processing in contrast to one maximum execution time per processing stage;

- easy implementation of systems where an input data frame processing time is temporarily larger (but not in the average) than the data frame period.

[0027] The invention can be used e.g. for MPEG 1, 2 and 4 Audio encoding and decoding for MPEG layers 1, 2 or 3, Digital Video Broadcast DVB, for AC-3, MD and AAC processing, for DVD processing and Internet applications concerning audio data encoding and decoding.

#### **Claims**

5

40

45

- 15 1. Method for processing audio or video frame data (PCMA, COE) which are processed in succeeding different processing stages (CONA, SUBA, BAL/Q/E\_A), characterised in that input time stamps (ITS) are generated which become linked at least in one input processing stage (CONA) with frames of said audio or video data to be encoded, wherein said input time stamps or time stamps derived from said input time stamps remain linked with the correspondingly processed frame data in said different processing stages (SUBA, BAL/Q/E\_A) in the processing, but are at least in the last processing stage (AES-EBU\_A) replaced by output time stamps (OTS) denoting the presentation time, and wherein in each of theses stages the corresponding time stamp information (ITS, OTS) linked with current frame data to be processed is regarded in order to control the overall delay of the processing.

- 2. Method according to claim 1, wherein to each stage a buffer is assigned at its input and wherein the buffers contain data fields including audio frame data (COE) and the associated time stamp information.

- 3. Method according to claim 2, wherein said buffers are controlled like FIFOs and the total processing delay is distributed over the chain of FIFOs.

- 4. Method according to any of claims 1 to 3, wherein the processing is carried out using multiple DSPs and the internal DSP timers are synchronised using a slow periodic interrupt signal in order to achieve a unique system time across all DSPs.

- **5.** Apparatus for encoding audio frame data (PCMA, COE) which are processed in succeeding different processing stages (CONA, SUBA, BAL/Q/E\_A), and including:

- means for generating time stamp information including input time stamps (ITS) and output time stamps (OTS);

- means for linking (CONA, CONB, CONC, COND) time stamp information with frames of said audio data or processed audio data, respectively;

- means (SUBA, SUBB, SUBC, SUBD) for converting time domain samples into frequency domain coefficients, to the input of which means buffer means are assigned;

- means (Psycho1A\_L, Psycho1A\_R, Psycho1B\_L, Psycho1B\_R, Psycho1C\_L, Psycho1C\_R, Psycho1D\_L, Psycho1D\_R, Psycho2A\_L, Psycho2A\_R, Psycho2B\_L, Psycho2B\_R, Psycho2C\_L, Psycho2C\_R, Psycho2D\_L, Psycho2D\_R) for calculating masking properties from said time domain samples, to the input of which means buffer means are assigned;

- means (Bal/Q/E\_A, Bal/Q/E\_B, Bal/Q/E\_C, Bal/Q/E\_D) for performing bit allocation and quantisation of the

coefficients under the control of the output of said masking calculating means, to the input of which bit allocation and quantisation means buffer means are assigned;

- means (AES-EBU\_A) for controlling presentation of the final output data at or at about a time corresponding to said output time stamps,

wherein said input time stamps (ITS) become linked at least for one input processing stage (CONA) with frames of said audio data to be encoded and said input time stamps or time stamps derived from said input time stamps remain linked with the correspondingly processed frame data in said conversion means, in said masking calculating means and in said bit allocation and quantisation means, but at least in the last processing stage (AES-EBU\_A) in the encoding processing are replaced by output time stamps (OTS), and wherein in each of theses stages the corresponding time stamp information (ITS, OTS) linked with current frame data to be processed is regarded in order to control the overall delay of the encoding processing.

|    | 6. | Apparatus according to claim 5, wherein said buffer means contain data fields including audio frame data (COE) and the associated time stamp information (ITS, OTS). |  |  |  |  |  |  |  |

|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 5  | 7. | Apparatus according to claim 6, wherein said buffer means are controlled like FIFOs and the total processing delay is distributed over the chain of FIFOs.           |  |  |  |  |  |  |  |

| 10 |    |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 15 |    |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 20 |    |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 25 |    |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 30 |    |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 35 |    |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 40 |    |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 45 |    |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 50 |    |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 55 |    |                                                                                                                                                                      |  |  |  |  |  |  |  |

# **EUROPEAN SEARCH REPORT**

Application Number EP 99 25 0009

|                                                  | DOCUMENTS CONSID                                                                                                                                                                                          | ERED TO BE REL                                             | EVANT                                                                                                                                                      |                                         | 7                                                               |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------|

| Category                                         | Citation of document with ir<br>of relevant pass                                                                                                                                                          |                                                            |                                                                                                                                                            | Relevant<br>to claim                    | CLASSIFICATION OF THE APPLICATION (Int.Cl.6)                    |

| Y<br>A                                           | WO 98 45959 A (OPTI<br>DAVID (IL); ELMALIA<br>15 October 1998<br>* abstract *<br>* page 7, line 20 -<br>* page 8, line 22 -<br>* page 12, line 25<br>* page 16, line 17<br>* claims 1-4 *<br>* figure 5 * | CH YEHUDA (IL))  line 23 * line 25 * - line 28 *           |                                                                                                                                                            | .5                                      | H04N7/52<br>H04B1/66                                            |

| Y                                                | "OPTIMIZED DATA TI<br>AUDIO AMD VIDEO ON<br>IBM TECHNICAL DISCL<br>vol. 36, no. 9A, 1<br>183 XP000395356<br>* the whole documen                                                                           | A STOCHASTIC NE<br>OSURE BULLETIN,<br>September 1993,      | TWORK"                                                                                                                                                     | , 5                                     |                                                                 |

| Α                                                | KIM S -Y ET AL: "A<br>IMPLEMENTATION OF T<br>ENCODER"<br>IEEE TRANSACTIONS O<br>vol. 43, no. 3, 1 A<br>593-597, XP00074253<br>* the whole documen                                                         | HE MPEG-2 AUDIO<br>N CONSUMER ELEC<br>ugust 1997, pag<br>6 | TRONICS,                                                                                                                                                   | -7                                      | TECHNICAL FIELDS<br>SEARCHED (Int.CI.6)<br>H04N<br>H04B<br>H03M |

| A                                                | US 4 845 752 A (BLA<br>4 July 1989<br>* abstract *<br>* figures 1,3 *                                                                                                                                     | NC ALAIN ET AL                                             | ) 1-                                                                                                                                                       | -7                                      | G11B                                                            |

| Α                                                | EP 0 701 374 A (THO<br>ELECTRONICS) 13 Mar<br>* abstract *<br>* column 4, line 37                                                                                                                         | ch 1996                                                    |                                                                                                                                                            | -7                                      |                                                                 |

|                                                  | The present search report has                                                                                                                                                                             | been drawn up for all clair                                | ns                                                                                                                                                         |                                         |                                                                 |

|                                                  | Place of search                                                                                                                                                                                           | Date of completion                                         | of the search                                                                                                                                              | 1                                       | Examiner                                                        |

|                                                  | THE HAGUE                                                                                                                                                                                                 | 11 June                                                    | 1999                                                                                                                                                       | Ber                                     | bain, F                                                         |

| X : par<br>Y : par<br>doc<br>A : tecl<br>O : nor | CATEGORY OF CITED DOCUMENTS ticularly relevant if taken alone ticularly relevant if combined with anoument of the same category hnological background n-written disclosure ermediate document             | E:c<br>a<br>ther D:c<br>L:c<br><br>&:r                     | heory or principle un<br>earlier patent docum<br>ifter the filing date<br>document cited in the<br>locument cited for of<br>member of the same<br>locument | ent, but puble application ther reasons | ished on, or                                                    |

### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 99 25 0009

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

11-06-1999

| Patent document<br>cited in search repo |       | Publication date | Patent family member(s) |                                     | Publication date                    |

|-----------------------------------------|-------|------------------|-------------------------|-------------------------------------|-------------------------------------|

| WO 9845959                              | Α     | 15-10-1998       | AU                      | 6850498 A                           | 30-10-199                           |

| US 4845752                              | Α     | 04-07-1989       | EP<br>JP<br>JP          | 0224626 A<br>1600802 C<br>2025320 B | 10-06-198<br>31-01-199<br>01-06-199 |

| <br>EP 0701374                          | <br>A | 13-03-1996       | JP<br><br>US            | 62107598 A<br>5568403 A             | 18-05-198<br><br>22-10-199          |

| LI 0/013/4                              | N     | 13 03 1990       | AU<br>AU                | 698661 B<br>3011595 A               | 05-11-199<br>29-02-199              |

|                                         |       |                  | CA<br>CN<br>JP          | 2154800 A<br>1122990 A<br>8079705 A | 20-02-199<br>22-05-199<br>22-03-199 |

|                                         |       |                  | SG<br>US                | 43666 A<br>5841987 A                | 14-11-199<br>24-11-199              |

FORM P0459

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82