(19)

## Europäisches Patentamt

European Patent Office

Office européen des brevets

(11)

EP 1 026 569 A1

(12)

## EUROPÄISCHE PATENTANMELDUNG

(43) Veröffentlichungstag:

**09.08.2000 Patentblatt 2000/32**

(51) Int Cl.<sup>7</sup>: **G05F 1/575**

(21) Anmeldenummer: **00101965.2**

(22) Anmeldetag: 01.02.2000

(84) Benannte Vertragsstaaten:

**AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU

MC NL PT SE**

Benannte Erstreckungsstaaten:

**AL LT LV MK RO SI**

(30) Priorität: **03.02.1999 DE 19904344**

(71) Anmelder: **SIEMENS AKTIENGESELLSCHAFT**

**80333 München (DE)**

(72) Erfinder: **Taghizadeh-Kaschani, Karim-Thomas, Dr.**

**82008 Unterhaching (DE)**

(74) Vertreter: **Zedlitz, Peter, Dipl.-Inf. et al**

**Patentanwalt,**

**Postfach 22 13 17**

**80503 München (DE)**

## (54) Spannungsregler

(57) Es wird ein Spannungsregler vorgeschlagen, dessen Eingang mit einer ersten Versorgungsspannung verbunden ist und dessen Ausgangsspannung am einen Ausgang im Normalbetrieb über eine Rückkoppelleitung einem Eingang einer integrierten Schaltung mit einer Ansteuerung zugeführt wird zur Überwachung und Regelung der Ausgangsspannung auf einem vorgegebenen Wert.

benen ersten Spannungswert durch die Ansteuerung wobei eine Schaltungsanordnung zum Detektieren einer Unterbrechung der Rückkoppelleitung vorgesehen ist und wobei am Ausgang bei einer Unterbrechung von dem vorgegebenen ersten Spannungswert auf einen vorgegebenen zweiten Spannungswert umgeschaltet wird.

FIG 2

## Beschreibung

**[0001]** Die Erfindung betrifft einen Spannungsregler, dessen Eingang mit einer ersten Versorgungsspannung verbunden ist und dessen Ausgangsspannung an einem Ausgang im Normalbetrieb über eine Rückkoppelleitung einem Eingang einer integrierten Schaltung mit einem Schaltungsblock zur Ansteuerung des Stellgliedes zugeführt wird, um so die Überwachung und Regelung der Ausgangsspannung auf einen vorgegebenen ersten Spannungswert zu gewährleisten.

**[0002]** Sowohl bei getakteten als auch bei linearen Spannungsreglern ist es erforderlich, daß die geregelte Ausgangsspannung ständig von einem Regler überwacht wird, um bei einer Abweichung von einem Sollwert sofort korrigierend eingreifen zu können. Somit kann die Ausgangsspannung konstant gehalten werden. Lineare Spannungsregler sind zum Beispiel aus Tietze, Schenk; Halbleiterschaltungstechnik, 10. Auflage, Springer-Verlag, 1993, Seiten 542 bis 555 bekannt. Getaktete Spannungsregler zum Beispiel in Form eines Aufwärts- oder eines Abwärtswandlers sind an der gleichen Literaturstelle auf den Seiten 563 bis 571 beschrieben.

**[0003]** Sinkt bei einem getakteten Spannungsregler die Ausgangsspannung unter einen vorgegebenen Wert ab, so wird das Einschaltverhältnis ("duty cycle") des Schalters durch eine Ansteuerung erhöht, so daß sich die Ausgangsspannung dem vorgegebenen Sollwert wiederum annähert. Das Erzeugen einer konstanten Ausgangsspannung auf einen vorgegebenen Sollwert basiert somit auf einem ständig arbeitenden Regelkreis. Ein Problem tritt dann auf, wenn die Leitung, mit welcher der Spannungsregler die Ausgangsspannung überwacht, unterbrochen ist. In der Regel ist der Eingangsknoten der Ansteuerschaltung intern ohmsch mit Masse verbunden, so daß die Spannung am Eingangsknoten im Fall einer Leitungsunterbrechung auf Null absinkt. Der Spannungsregler muß dann davon ausgehen, daß seine Ausgangsspannung zu klein ist. Er versucht deshalb, ohne Rücksicht auf etwaige angeschlossene Verbraucher, die Ausgangsspannung auch über den Sollwert hinaus zu erhöhen. Dies führt jedoch unweigerlich zu einer Schädigung der angeschlossenen Verbraucher, sofern nicht zusätzliche externe Schutzmaßnahmen an den Verbrauchern vorgesehen sind.

**[0004]** Die Aufgabe der vorliegenden Erfindung besteht deshalb darin, einen Spannungsregler der ein- gangs beschriebenen Art vorzusehen, der einen vom Normalbetrieb abweichenden Zustand, insbesondere eine Unterbrechung der Rückkoppelleitung vom Ausgang zu einer Ansteuerung erkennt und die mit dem Ausgang des Spannungsreglers verbundene Verbraucher sicher vor Fehlfunktion oder Zerstörung schützt.

**[0005]** Erfindungsgemäß ist in dem Spannungsregler eine Schaltungsanordnung zum Detektieren einer Unterbrechung der Rückkoppelleitung vorgesehen, wobei am Ausgang des Spannungsreglers bei einer Unterbre-

chung der Rückkoppelleitung von einem vorgegebenen ersten Spannungswert auf einen vorgegebenen zweiten Spannungswert umgeschaltet wird. Vorteilhafterweise ist der Ausgang des Spannungsreglers mit einem

5 massebezogenen Ladungsspeicher verbunden, der in einer ersten Zeitspanne eine erste Ladungsquantität speichern kann, wobei die an dem Ladungsspeicher abfallende Spannung der Ansteuerung und im Normalbetrieb der Schaltungsanordnung zum Detektieren einer

10 Unterbrechung der Rückkoppelleitung zugeführt wird. Die Schaltungsanordnung zum Detektieren einer Unterbrechung der Rückkoppelleitung ist dabei vorteilhafterweise mit ihrem Ausgang mit der Ansteuerung verbunden. Hierdurch wird erzielt, daß im Falle einer Unterbrechung der Rückkoppelleitung das Hochregeln der Spannung am Ausgang der Spannungsreglers verhindert werden kann, so daß eine Fehlfunktion oder Zerstörung der angeschlossenen Verbraucher nicht auftreten kann. Die Schaltungsanordnung zum Detektieren

15 einer Unterbrechung der Rückkoppelleitung ist sowohl in einem linearen als auch in einem getakteten Spannungsregler einsetzbar.

**[0006]** Vorteilhafte Ausgestaltungen der Erfindung sind in den Unteransprüchen angegeben.

**[0007]** Die Schaltungsanordnung zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes in dem erfindungsgemäßen Spannungsregler ist derart, daß im Falle einer Unterbrechung am Eingang der Schaltungsanordnung innerhalb einer

20 zweiten Zeitspanne ein zweiter kleinerer, vorgegebener Spannungswert als die im Normalbetrieb an dem Ladungsspeicher abfallende Spannung anliegt, der mit einem innerhalb einer dritten Zeitspanne ab dem Eintreten der Unterbrechung erzeugten Referenzspannungswert jeweils einem Eingang einer Auswertung zugeführt wird, die ein Signal am Ausgang der Schaltungsanordnung erzeugt, das der Ansteuerung zugeführt wird. Der Vorteil der erfindungsgemäßen Schaltungsanordnung besteht darin, daß die eigentliche Funktion der Rückkoppelleitung nicht beeinträchtigt wird, nämlich die am Ausgang anliegende Spannung einer Ansteuerung zu zuführen, die die Ausgangsspannung auf einem konstanten, vorgegebenen ersten Spannungswert hält.

**[0008]** Zur Erzeugung des zweiten Spannungswertes

25 ist vorteilhafterweise eine Serienschaltung aus einer Stromquelle, einer Schaltvorrichtung und einem Widerstand zwischen Versorgungspotentialanschlüssen vorgesehen, wobei der Verbindungspunkt zwischen dem Widerstand und der Schaltvorrichtung einerseits mit dem Eingang der Schaltungsanordnung und andererseits mit dem ersten Eingang der Auswertung verschalten ist. Zur Erzeugung des Referenzspannungswertes ist vorteilhafterweise eine Serienschaltung einer zweiten Stromquelle, einer zweiten Schaltungsvorrichtung

30 und einem Ladungsspeicher zwischen den Versorgungspotentialanschlüssen vorgesehen, wobei der Verbindungspunkt zwischen dem zweiten Ladungsspeicher und der zweiten Schaltungsvorrichtung mit dem zweiten

35

Eingang der Auswertung verschalten ist und wobei dem Ladungsspeicher zumindest ein Halbleiterschalter mit seiner Laststrecke parallel geschalten ist.

**[0009]** Durch das Einprägen eines definierten, internen Stromes in den Eingangsknoten der Schaltungsanordnung und dem Vergleich des resultierenden Spannungsabfalles an dem Widerstand mit der Spannung, die durch das Einprägen eines Referenzstromes über dem zweiten Ladungsspeicher entsteht, kann festgestellt werden, ob eine Unterbrechung in der Rückkoppelleitung vorliegt oder nicht. Der erste und der zweite Ladungsspeicher sind derart dimensioniert, daß im Normalbetrieb die Spannung am Eingang der Schaltungsanordnung deutlich langsamer ansteigt als die Spannung über dem zweiten Ladungsspeicher. Bei einer Unterbrechung der Rückkoppelleitung bestimmt nicht der erste Ladungsspeicher die Spannung am Eingang der Schaltungsanordnung, sondern die über dem Widerstand sofort abfallende Spannung, die wesentlich kleiner als die an dem ersten Ladungsspeicher abfallende Soll-Spannung ist.

**[0010]** Die Auswertung der Schaltungsanordnung zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes in dem erfindungsgemäßen Spannungsregler ist derart, daß sie einem ersten und einen zweiten Differenzverstärker aufweist, deren positive Eingänge miteinander und mit dem Eingang der Schaltungsanordnung verbunden sind und den ersten Eingang der Auswertung bilden. Der negative Eingang des ersten Differenzverstärkers ist mit einer zwischen zwei Spannungswerten schaltbaren Vorrichtung verbunden. Der negative Eingang des zweiten Differenzverstärkers ist dem Verbindungspunkt zwischen dem zweiten Ladungsspeicher und der zweiten Schaltvorrichtung verbunden. Der Ausgang des ersten Differenzverstärkers steuert einerseits die erste und die zweite Schaltvorrichtung im Fehlerfall leitend, andererseits den dem zweiten Ladungsspeicher parallel geschalteten Halbleiterschalter im Fehlerfall sperrend und ist weiterhin mit einem ersten Eingang eines logischen Verknüpfungselementes verbunden. Der Ausgang des zweiten Differenzverstärkers ist mit einem zweiten Eingang des logischen Verknüpfungsgliedes verbunden und der Ausgang des logischen Verknüpfungsgliedes mit dem Ausgang der Schaltungsanordnung zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes. Beim Auftreten eines Fehlerfalles schaltet der Ausgang des logischen Verknüpfungsgliedes die zweite Schaltvorrichtung sperrend. Die zweite Schaltvorrichtung weist vorteilhafterweise zwei mit ihrer Laststrecke seriell verschaltete Halbleiterschalter auf. Das logische Verknüpfungsglied ist vorteilhafterweise ein UND-Gatter, wobei der erste Eingang invertierend ausgeführt ist. Der erste und der zweite Ladungsspeicher sind vorteilhafterweise Kondensatoren, wobei das Speichervermögen des ersten Ladungsspeicher sehr viel größer als das Speichervermögen des zweiten Ladungsspeichers ist. Vorteilhafterweise ist zwischen dem

negativen Eingang des zweiten Differenzverstärkers und dem zweiten Ladungsspeicher eine Spannungsquelle geschalten.

**[0011]** Die Schaltungsanordnung in dem erfindungsgemäßen Spannungsregler weist die vorteilhafte Eigenschaft auf, daß ein Fehler in der Rückkoppelleitung von einem Hochlauf des Spannungsreglers unterschieden werden kann. Unter einem Hochlauf des Spannungsreglers ist hierbei zu verstehen, daß am Eingang des Spannungsreglers erstmalig eine von Null unterschiedliche Spannung angelegt wird, so daß der Spannungsregler am Ausgang die vorgegebene Sollwertspannung zu erreichen versucht. Ein undefiniertes Statusausgang ist somit unterbunden, das heißt es ist zweifelsfrei feststellbar, ob ein Fehler vorliegt oder nicht. Ansonsten weist der Statusausgang der Schaltungsanordnung ein Signal auf, welches der Ansteuerung oder aber auch über eine Signalvorrichtung die korrekte Funktionsweise des Spannungsreglers anzeigen. Durch die besondere Ausgestaltung der Schaltungsanordnung wird weiterhin erzielt, daß diese im Normalbetrieb einen nur geringen Stromverbrauch aufweist, da die Stromquellen durch die besondere Arbeitsweise der Auswertung abgeschaltet werden. Diese erzeugen folglich nur dann Strom, welcher sich in einem Spannungsabfall an dem Widerstand beziehungsweise dem zweiten Ladungsspeicher bemerkbar macht, wenn die Schaltungsanordnung überprüft, ob ein Fehlerfall vorliegen könnte. Weiterhin ist eine monolithische Integration der Schaltungsanordnung zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes zusammen mit der Ansteuerung möglich.

**[0012]** Die Erfindung wird anhand der nachfolgenden Figuren weiter erläutert.

**[0013]** Es zeigen:

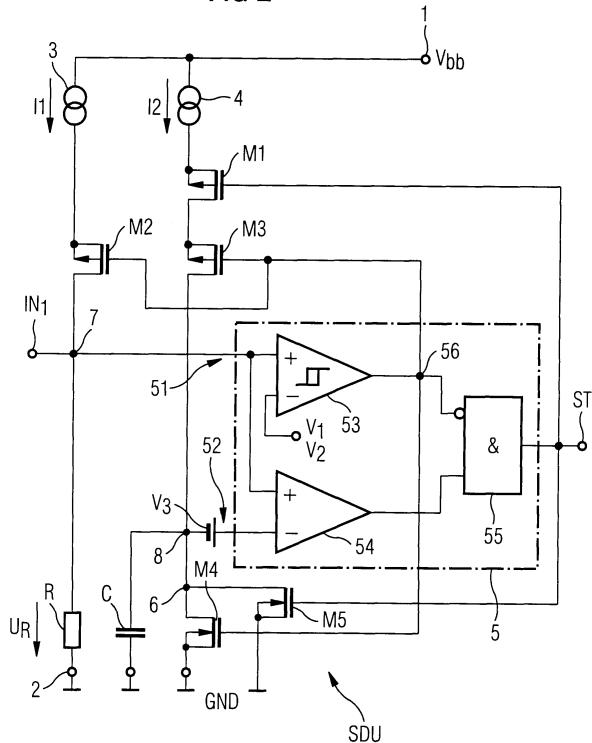

Figur 1 ein erfindungsgemäßer getakteter Spannungsregler in Form eines Abwärtswandlers,

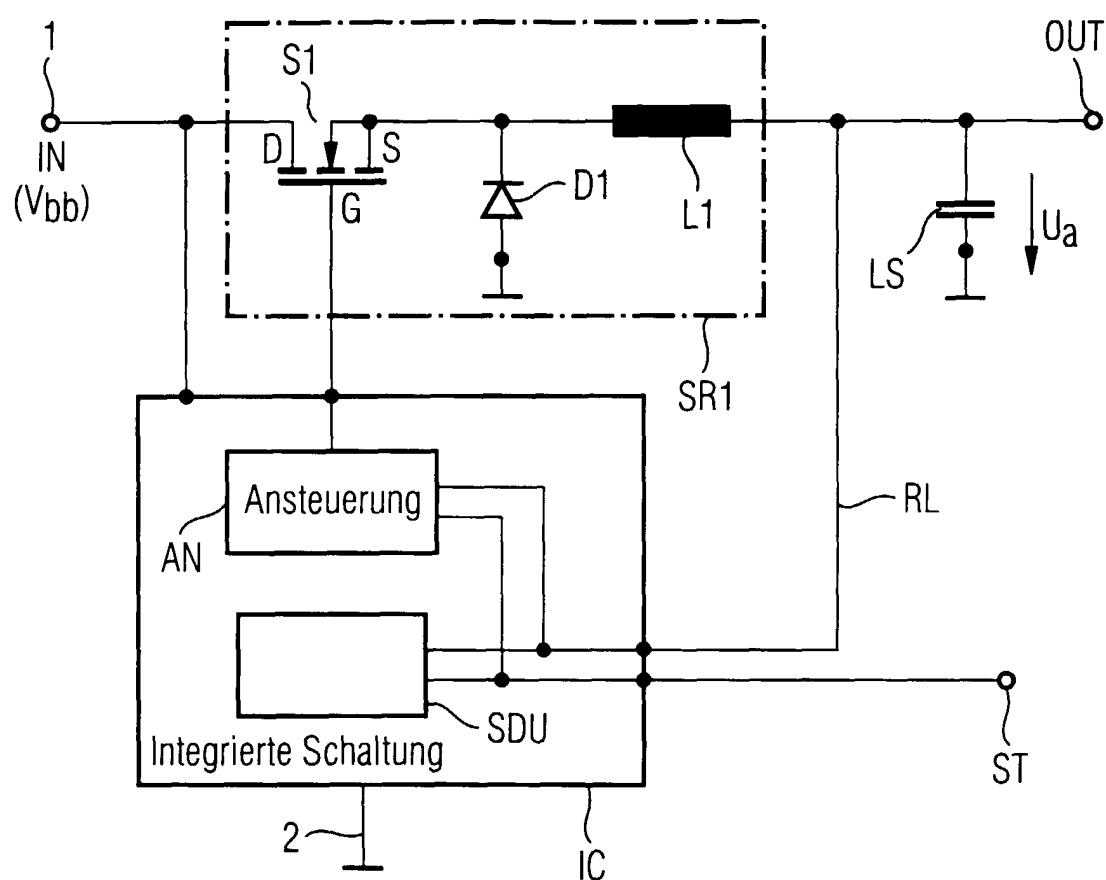

Figur 2 die erfindungsgemäße Schaltungsanordnung zum Detektieren einer Unterbrechung der Rückkoppelleitung,

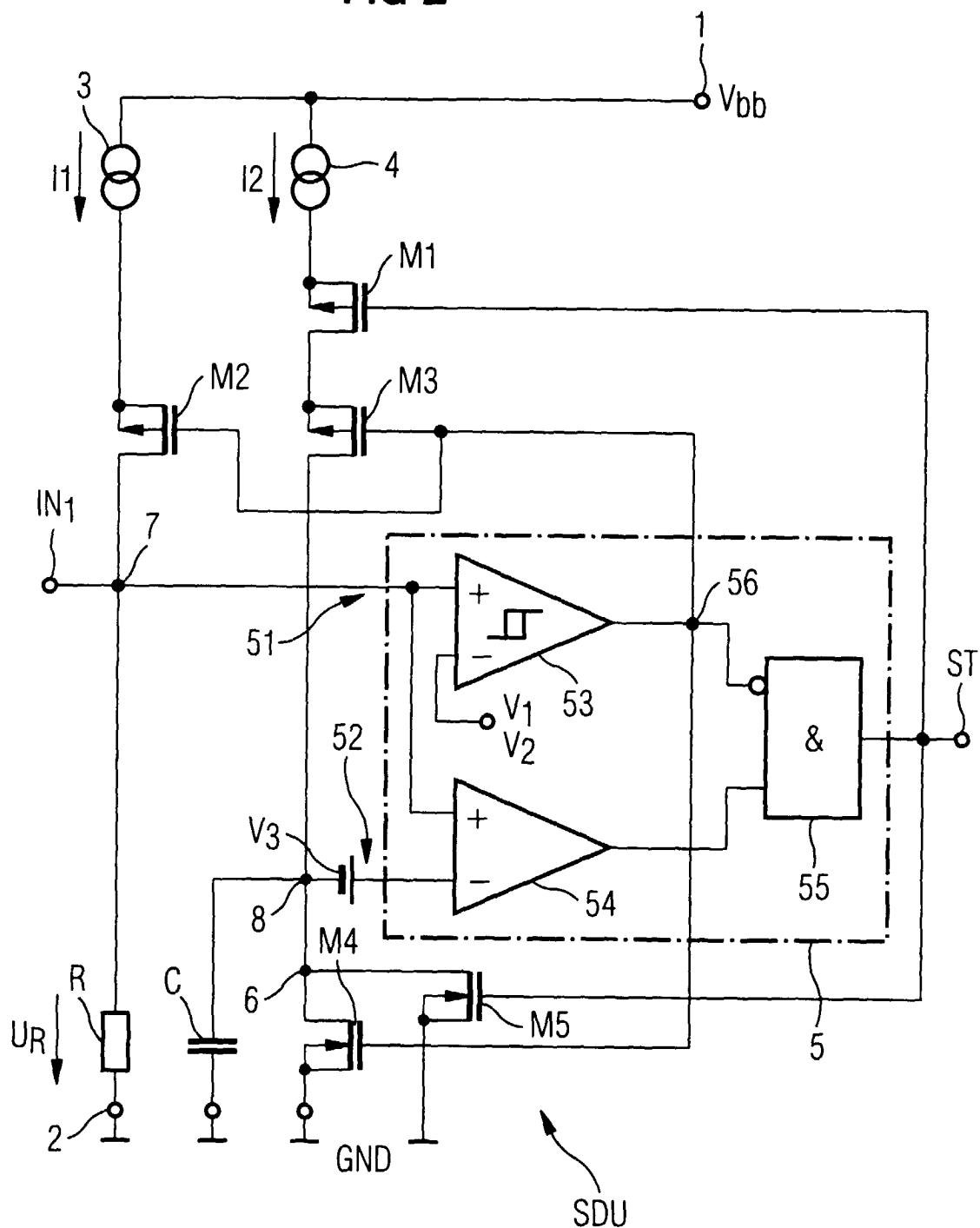

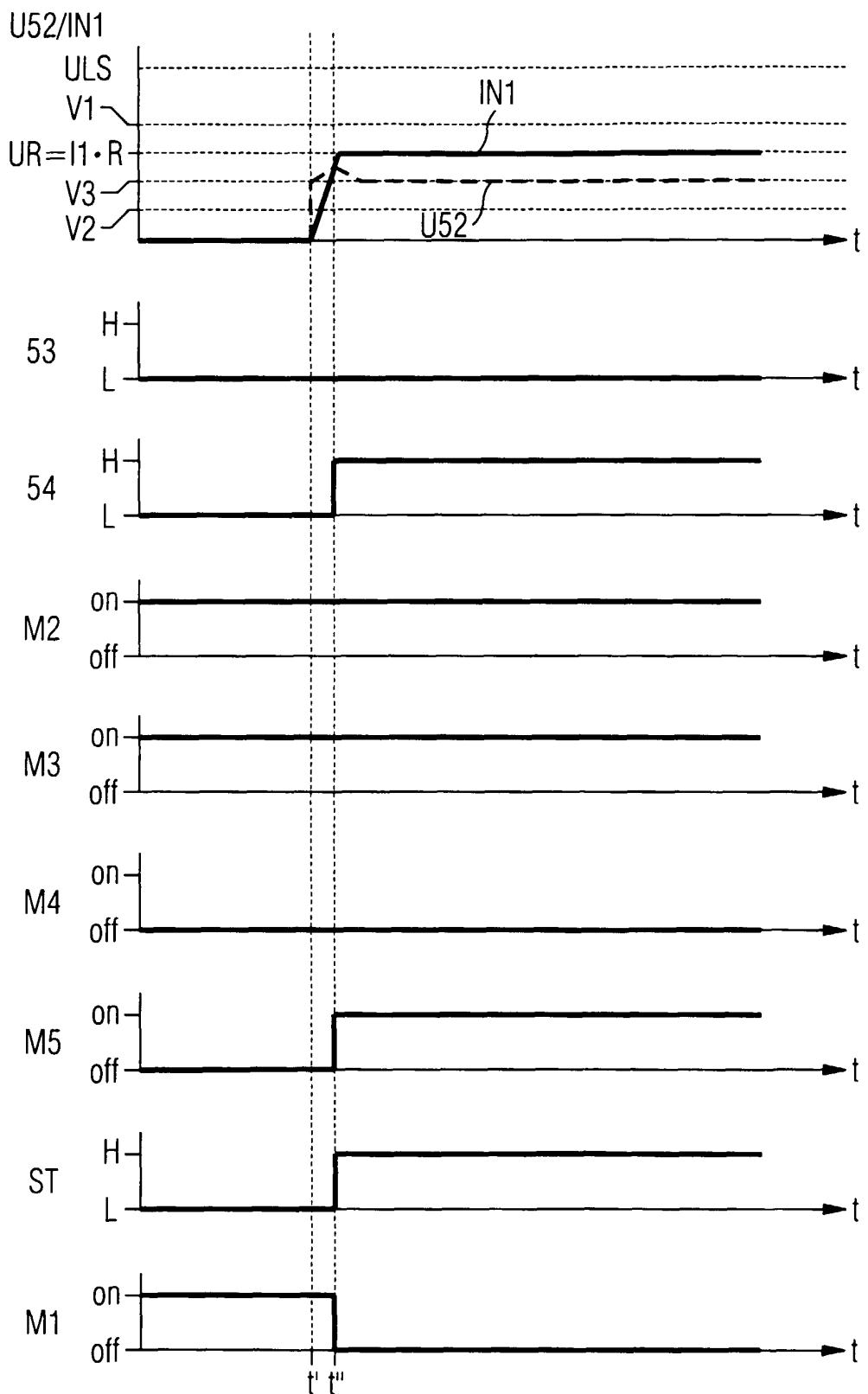

Figur 3a die Arbeitsweise der Schaltungsanordnung beim Hochlaufen des Spannungsreglers sowie während eines Betriebes des Spannungsreglers im Normalbetrieb,

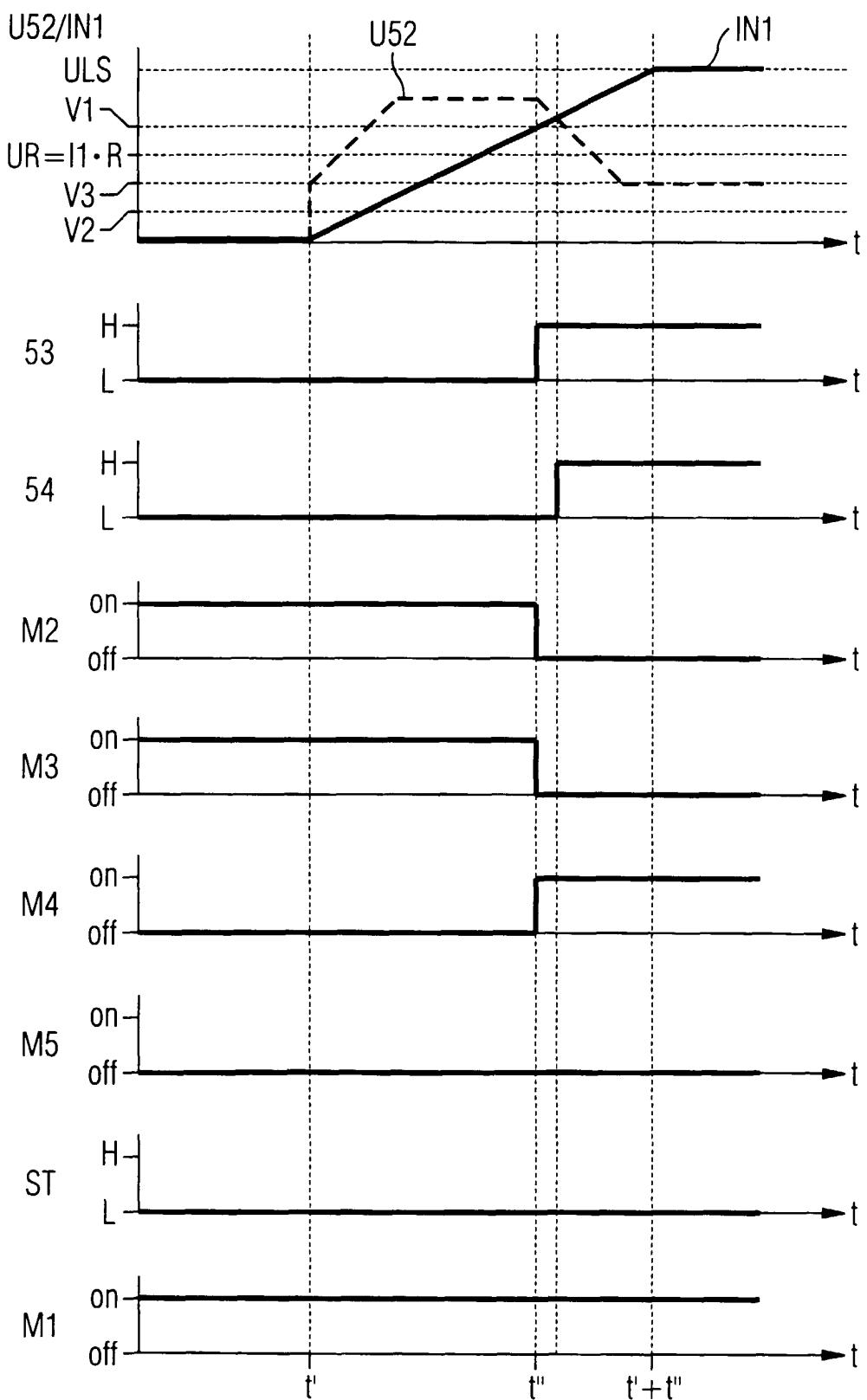

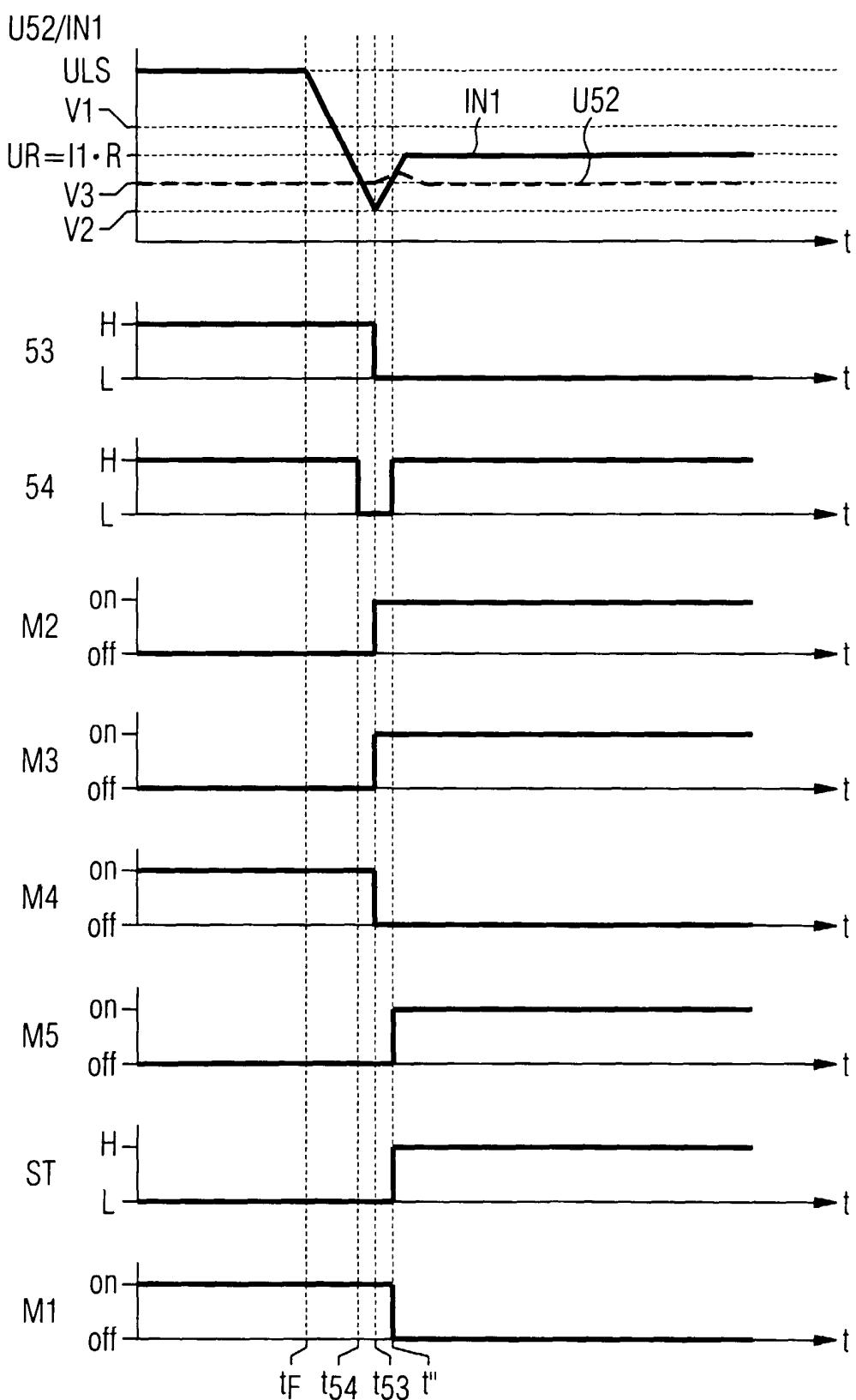

Figur 3b die Arbeitsweise der Schaltungsanordnung des Spannungsreglers, wenn beim Hochlauf ein Fehler auftritt und

Figur 3c die Arbeitsweise der Schaltungsanordnung des Spannungsreglers beim Auftreten eines Fehlers während des Betriebes des Spannungsreglers.

**[0014]** Figur 1 zeigt den prinzipiellen Aufbau eines erfundungsgemäßen getakteten Spannungsreglers, wobei der Spannungsregler SR1 in Form eines Abwärtswandlers ausgeführt ist. Der Spannungsregler wird an seinem Eingang IN, welcher gleichzeitig einen ersten Versorgungspotentialanschluß 1 darstellt, mit einer in der Regel positiven Versorgungsspannung Vbb versorgt. Der Spannungsregler SR1 beinhaltet einen Halbleiterschalter S1, der beispielsweise als MOSFET ausgeführt sein kann. Es ist jedoch auch jeder andere steuerbare Schalter denkbar. Der Halbleiterschalter S1 ist mit seinem Drain mit dem Eingang IN verbunden, während sein Sourceanschluß S mit dem Kathodenanschluß einer gegen Bezugspotential verschalteten Diode D1 verbunden ist. Das Bezugspotential GND stellt gleichzeitig einen zweiten Versorgungspotentialanschluß 2 dar. Weiterhin ist mit dem Sourceanschluß S des Halbleiterschalters S1 ein Anschluß einer Induktivität verbunden, deren anderer Anschluß mit dem Ausgang OUT in Verbindung steht und mit einem Ladungsspeicher LS verbunden ist, der gegen Bezugspotential verschalten ist. Der Ladungsspeicher LS ist als Kondensator ausgeführt, der eine Kapazität C1 besitzt. Um eine geregelte Spannung am Ausgang OUT zu erhalten, weist der Spannungsregler eine Rückkoppelleitung RL auf, die einerseits mit dem Ausgang OUT und andererseits mit dem Eingang IN1 einer integrierten Schaltung IC verbunden ist. Die integrierte Schaltung IC weist eine Ansteuerung AN auf, die abhängig von der Ausgangsspannung Ua die Taktfrequenz des Gates G des Halbleiterschalters S1 steuert. Die integrierte Schaltung ist weiterhin mit dem Eingang IN sowie dem Bezugspotential GND verbunden. Die integrierte Schaltung IC weist weiterhin eine Schaltungsanordnung SDU zum Detektieren einer Unterbrechung der Rückkoppelleitung RL auf. Die Schaltungsanordnung SDU ist deshalb ebenfalls über den Eingang IN1 mit der Rückkoppelleitung RL verbunden. Sie weist weiterhin einen Ausgang ST auf, der einerseits mit der Ansteuerung AN verbunden ist, um bei einem auftretenden Defekt den Spannungsregler abschalten zu können. Andererseits ist der Ausgang ST der Schaltungsanordnung SDU aus der integrierten Schaltung IC herausgeführt.

**[0015]** Der getaktete Spannungsregler SR1 könnte auch als Aufwärtswandler oder aber als linearer Spannungsregler ausgeführt sein.

**[0016]** Figur 2 zeigt das wesentliche Element des erfundungsgemäßen Spannungsreglers, nämlich die Schaltungsanordnung SDU zum Detektieren einer Unterbrechung der Rückkoppelleitung. Die Schaltungsanordnung SDU kann zusammen mit der Ansteuerung des Schalters S1 monolithisch integriert auf der integrierten Schaltung IC vorliegen. Die Schaltungsanordnung SDU weist einen Eingang IN1 auf, an dem im Normalbetrieb die Ausgangsspannung Ua über die Rückkoppelleitung RL anliegt. Der Eingang IN1 der Schaltungsanordnung SDU ist mit einem ersten Eingang 51 einer Auswertung 5 verbunden. Weiterhin ist eine Serienschaltung aus ei-

ner ersten Stromquelle 3, einem Halbleiterschalter M2 sowie einem Widerstand R vorgesehen, die mit einem ersten Versorgungspotentialanschluß 1, an welchem üblicherweise die Versorgungsspannung Vbb oder eine 5 daraus abgeleitete Spannung anliegt, und einem zweiten Versorgungspotentialanschluß 2, welches das Bezugspotential darstellt, verbunden ist. Der Halbleiterschalter M2 ist im vorliegenden Beispiel als p-Kanal-Enhancement-MOSFET ausgeführt, es könnte jedoch beispielsweise auch ein Bipolartransistor oder ein beliebiger steuerbarer Schalter eingesetzt werden. Der Verbindungspunkt 7 zwischen dem Widerstand R und dem Drainanschluß des Halbleiterschalters M2 ist mit dem Eingang IN1 der Schaltungsanordnung SDU verbunden. Die Schaltungsanordnung SDU weist eine weitere Reihenschaltung aus einer zweiten Stromquelle 4, zwei Halbleiterschaltern M1 und M3 deren Laststrecken in Serie miteinander verschalten sind, sowie einen Kondensator C auf. Diese Serienschaltung ist wiederum zwischen dem ersten 1 und dem zweiten Versorgungspotentialanschluß 2 gelegen. Der erste Versorgungspotentialanschluß 1 steht dabei jeweils mit der ersten beziehungsweise mit der zweiten Stromquelle 4 in Verbindung. Dem Ladungsspeicher C sind zwei weitere Halbleiterschalter M4 und M5 mit ihrer Laststrecke parallel geschaltet. Die Halbleiterschalter M1 und M3 sind als p-Kanal-Enhancement-MOSFETs ausgeführt, während der Halbleiterschalter M4 und M5 n-Kanal-Enhancement-MOSFETs sind. Auch an die Stelle der Halbleiterschalter M1, M3, M4 und M5 könnten beliebige steuerbare Schalter treten. Der Verbindungspunkt 8 zwischen dem Kondensator C und dem Drainanschluß des Halbleiterschalters M3 ist über eine Spannungsquelle 6, die die voreingestellte Spannung V3 liefert, mit einem zweiten Eingang 52 der Auswertung 5 verbunden.

**[0017]** Die Auswertung 5 umfaßt einen ersten 53 und einen zweiten Differenzverstärker 54, wobei deren positive Eingänge miteinander verbunden sind. Diese stehen wiederum mit dem ersten Eingang 51 und somit mit 40 dem Eingang IN1 der Schaltungsanordnung SDU in Verbindung. Der erste Differenzverstärker 53 ist vorteilhafterweise mit Eingangshysterese ausgeführt, das heißt an seinem negativen Eingang werden zwei verschiedene große, positive Spannungen V1 beziehungsweise V2 angelegt. Hierzu können beispielsweise zwei separate Spannungsquellen V1 beziehungsweise V2 zur Erzeugung vorgesehen sein. Der zweite Eingang 52 der Auswertung 5 steht in direkter Verbindung zum negativem Eingang des zweiten Differenzverstärkers 54. 45 Die Auswertung 5 weist weiterhin ein logisches Verknüpfungselement 55 auf, welches als UND-Gatter ausgeführt ist. Dieses weist einen invertierenden Eingang auf, welcher mit dem Ausgang des ersten Differenzverstärkers 53 verbunden ist. Der nichtinvertierende, zweite Eingang steht mit dem Ausgang des zweiten Differenzverstärkers 54 in Verbindung. Der Ausgang ST des logischen Verknüpfungselementes 55 stellt gleichzeitig 55 den Ausgang ST der Schaltungsanordnung SDU dar.

Der Ausgang des ersten Differenzverstärkers 53 ist weiterhin mit den Gateanschlüssen der Halbleiterschalter M2, M3 sowie M4 verbunden. Der Ausgang ST des logischen Verknüpfungselementes 55, das im Normalfall einen logischen Low-Pegel annimmt oder aber im Fehlerfall einen logischen High-Pegel annimmt, steuert das Gate der Halbleiterschalter M1 und M5.

**[0018]** Die Stromquellen 3 und 4, der Kondensator C sowie die Spannungsquellen V1, V2 und V3 sind so dimensioniert, daß die Spannung am Eingangsknoten IN1 im Normalfall, das heißt bei einem korrekt geschlossenen externen Kondensator LS, deutlich langsamer ansteigt als die Spannung über dem Kondensator C. Hierzu ist folgende Dimensionierung vorgesehen:

$$V2 < V3 < I1 * R < V1 < V_{IN1, Soll}.$$

**[0019]** Diese Dimensionierung hat zur Folge, daß der Ausgang des zweiten Differenzverstärkers 54 im Normalfall am Ausgang ein logisches L liefert und somit auch der Ausgang ST mit einem logischen L die korrekte Funktionsweise Spannungsreglers signalisiert. Die Diagnose, ob eine Unterbrechung der Rückkoppelleitung RL vorliegt, wird im Normalfall abgebrochen, sobald die Spannung am Eingang IN1 über die Referenzspannung V1 angestiegen ist. In diesem Fall wechselt der erste Differenzverstärker 53 von einem logischen L auf ein logisches H, so daß die Stromquellen 3 und 4 mit Hilfe der Halbleiterschalter M2 und M3 abgeschaltet werden. Die im Kondensator C enthaltene Ladung wird durch das Schließen des Halbleiterschalters M4 entladen.

**[0020]** Durch das Abschalten der Stromquellen 3 und 4 ist ein geringer Stromverbrauch des Spannungsreglers im Normalbetrieb sichergestellt.

**[0021]** Beim Auftreten eines Fehlers wechselt die Spannung am Eingang IN1 mangels des externen Ladungsspeichers LS sofort auf einen Spannungswert UR, der sich aus dem Produkt des Stromes I1 und des Widerstandes R ergibt. Dies hat zur Folge, daß der zweite Differenzverstärker 54 an seinem Ausgang von einem logischen L auf ein logisches H wechselt, während der Zustand des ersten Differenzverstärkers 53 unverändert auf einem logischen L verharrt. Dies hat nun zur Folge, daß auch der Ausgang ST von einem logischen L auf ein logisches H wechselt, so daß ein Fehler signalisiert wird. Ist die Schaltungsanordnung SDU mit der Ansteuerung AN verbunden, so kann der Spannungsregler z. B. sofort abgeschaltet werden. Hat der Ausgang ST von einem logischen L auf ein logisches H gewechselt, so wird der Ladevorgang des Ladungsspeichers C durch das Öffnen des Leistungsschalters M1 unterbrochen und eine eventuell vorhandene Ladung durch Schließen von M5 wieder entfernt. Dieser Zustand bleibt solange erhalten, bis die Unterbrechung in der Rückkoppelleitung behoben ist. Der erste Differenzverstärker 53, der vorteilhafterweise als Schmitt-Trigger ausgeführt ist, ist zur Unterdrückung transienter

Störsignale mit einer großen Hysterese auszuführen, das heißt:

$$V1 - V2 > I1 * R.$$

**[0022]** Die Arbeitsweise und die Vorteile des erfindungsgemäß Spannungsreglers werden anhand drei verschiedener Betriebszustände genauer erklärt. Die 10 Figuren 3a bis 3c zeigen hierzu die am Eingang IN1 anliegenden Spannungswerte sowie die logischen Signalfälle der zwei Differenzverstärker 53 und 54 sowie die Schaltzustände der Halbleiterschalter M1 bis M5.

**[0023]** Figur 3a veranschaulicht die Arbeitsweise der 15 Schaltungsanordnung SDU beim Hochlaufen des Spannungsreglers sowie während eines Betriebes des Spannungsreglers im Normalbetrieb. Der Spannungsregler wird zum Zeitpunkt  $t'$  eingeschaltet. Vor dem Erreichen des Zeitpunktes  $t'$  weisen beide Differenzverstärker 20 53 und 54 ein logisches L am Ausgang auf. Hierdurch bedingt sind die Halbleiterschalter M1 und M3 leitend geschalten, während die Halbleiterschalter M4 und M5 sperren. Das logische L des ersten Differenzverstärkers 25 53 wird invertiert, so daß am Ausgang ST des logischen Verknüpfungselementes ein logisches L anliegt. Dieses hat wiederum zu Folge, daß der Halbleiterschalter M1 eingeschaltet ist.

**[0024]** Zum Zeitpunkt  $t'$  wird an den ersten Versorgungspotentialanschluß 1 die Versorgungsspannung 30 Vbb angelegt. Der Hochlauf des Spannungsreglers beginnt, das heißt die Spannung am Eingang IN1, welcher über die Rückkoppelleitung RL mit dem Ausgang OUT des Spannungsreglers verbunden ist beginnt kontinuierlich bis auf einen Wert ULS zu steigen. Der Spannungswert ULS ist durch den Regelkreis vorgegeben. Bis zum Zeitpunkt  $t''$  verändern sich die Zustände der einzelnen Bauelemente nicht. Nach dem Erreichen des Zeitpunktes  $t''$  übersteigt die am Eingang IN1 anliegende Spannung den Spannungswert V1. Dies hat zur Folge, daß der Ausgang des ersten Differenzverstärkers 40 53 von einem logischen L auf ein logisches H wechselt. Die Halbleiterschalter M2 und M3 werden hierdurch sperrend geschaltet, das heißt der weitere Stromfluß durch den Widerstand R beziehungsweise ein weiteres 45 Ansteigen der Spannung am Verbindungspunkt 8 wird unterbunden. Gleichzeitig wird der Halbleiterschalter M4 leitend geschalten, so daß die in dem Ladungsspeicher C gespeicherte Ladung abfließen kann und sich am Verbindungspunkt 8 einen Spannung von 0 V einstellt. M5 bleibt unverändert im gesperrten Zustand.

**[0025]** Bedingt durch die Schaltverzögerung von M4, wechselt der Ausgang des zweiten Differenzverstärkers 54 erst kurz nach dem Zeitpunkt  $t''$  von einem logischen L auf ein logisches H. Dies ist durch den Spannungsverlauf (U52) am zweiten Eingang 52 der Auswertung 5 bedingt. Zur Erklärung ist der Spannungsverlauf U52 mit eingezeichnet. Zum Zeitpunkt  $t'$  beginnt sich der Kondensator C aufzuladen. Durch das Öffnen des Halb-

leiterschalters M4 sinkt U52 auf den konstanten Spannungswert V3 ab. Beim Schnittpunkt der Spannungsverläufe von U52 und IN1 wechselt der Ausgang des zweiten Differenzverstärkers dann seinen wert. Dieses Verhalten hat jedoch keine Folge auf das am Ausgang ST anliegende Signal, welches weiterhin auf einem logischen L verbleibt. Dieses signalisiert eine korrekte Funktionsfähigkeit des Spannungsreglers. Die am Eingang IN1 anliegende Spannung steigt bis zum Zeitpunkt  $t_1 + t'$  auf den Wert ULS. Der Ladungsspeicher LS hat seine vollständige Ladung aufgenommen und am Ausgang OUT liegt die vorgegebene Sollspannung an.

**[0026]** Figur 3b zeigt die Arbeitsweise des erfindungsgemäßen Spannungsreglers bei einem Hochlauf, wenn die Rückkoppelleitung unterbrochen ist. Der Hochlauf beginnt zum Zeitpunkt  $t'$ . Bis zum Zeitpunkt  $t'$  weisen die Differenzverstärker 53 und 54 an ihren Ausgängen ein logisches L auf. Die Halbleiterschalter M2 und M3 sind leitend geschalten während die Halbleiterschalter M4 und M5 sperren. Der Statusausgang ST weist bis zum Zeitpunkt  $t'$  ebenfalls ein logisches L auf. Der Halbleiterschalter M1 ist deshalb leitend geschalten.

**[0027]** Ab dem Zeitpunkt  $t'$  liegt am ersten Versorgungspotentialanschluß 1 die positive Versorgungsspannung Vbb an, das heißt der Hochlauf beginnt. Da der externe Ladungsspeicher LS aufgrund der Unterbrechung der Rückkoppelleitung RL nicht mit den Eingang IN1 verbunden ist wird durch die Stromquelle 3 über den geschlossenen Schalter M2 im Widerstand R eine Spannung UR eingeprägt, die am Eingang IN1 und somit am ersten Eingang 51 der Auswertung anliegt. Diese Spannung steht sofort zur Verfügung. Die am Widerstand abfallende Spannung UR ist betragsmäßig größer als die Spannungen V2, die am negativen Eingang des ersten Differenzverstärkers 53 anliegt und größer als V3, die am negativen Eingang des zweiten Differenzverstärkers 54 anliegt. Überschreitet die am Eingang IN1 anliegende Spannung den Wert U52 zum Zeitpunkt  $t''$ , so wechselt der zweite Differenzverstärker 54 am Ausgang sein Signal von L auf ein logisches H. Der Ausgang des ersten Differenzverstärkers 53 verbleibt unverändert auf einem logischen L. Da dieses durch den invertierenden Eingang im logischen Verknüpfungselement 55 zu einem logischen H wird, wechselt am Ausgang ST das Signal von einem logischen L auf ein logisches H und signalisiert einen Fehler. Dies hat zur Folge, daß der Halbleiterschalter M1 ausgeschaltet und M5 eingeschaltet wird und somit eine Entladung des Ladungsspeichers C durchgeführt wird. Die Halbleiterschalter M2 und M3 verbleiben leitend, während der Halbleiterschalter M4 weiterhin im ausgeschalteten Zustand verbleibt. Das Durchschalten von M5 hat weiterhin den Vorteil, daß der Verbindungspunkt 8 definiert auf Bezugspotential liegt. Ein Spannungsanstieg am Verbindungspunkt 8 durch Leckströme durch M1 ist somit verhindert.

**[0028]** Aus der Beschreibung wird ersichtlich, daß ein Vorteil der erfindungsgemäßen Schaltungsanordnung

SDU darin besteht, daß ein Fehler in der Rückkoppelleitung RL von einem Hochlauf des Spannungsreglers unterschieden werden kann.

**[0029]** In Figur 3c wird die Arbeitsweise der Schaltungsanordnung des erfindungsgemäßen Spannungsreglers beim Auftreten eines Fehlers während des Betriebes erläutert. Der Fehler tritt zum Zeitpunkt  $t_F$  auf. Bis zu diesem Zeitpunkt liegt am Eingang IN1 die Spannung ULS an. Die beiden Differenzverstärker 53 und 54 erzeugen an ihren Ausgängen ein logisches H. Die Halbleiterschalter M2 und M3 sind ausgeschaltet, während der Halbleiterschalter M4 leitend geschalten ist. Aufgrund der an den Ausgängen der beiden Differenzverstärker 53 und 54 anliegenden logischen H weist der Ausgang ST ein logisches L auf. Dies hat zur Folge, daß der Halbleiterschalter M1 eingeschalten ist und M5 ausgeschaltet.

**[0030]** Zum Zeitpunkt  $t_F$  findet eine Unterbrechung in der Rückkoppelleitung RL statt. Dies hat zur Folge, daß die Spannung am Eingang IN1 von ULS auf den Wert 0 abzusinken beginnt. Sinkt die Spannung am Eingang IN1 unter den Wert V3 zum Zeitpunkt  $t_{54}$  ab, so ändert sich am Ausgang des zweiten Differenzverstärkers 54 das logische H zu einem logischen L. Die Spannung am Eingang IN1 sinkt bis zum Zeitpunkt  $t_{53}$  auf den Wert V2 ab, bei welchem sich das Signal am Ausgang des ersten Differenzverstärkers 53 auf ein logisches L verändert. Zu diesem Zeitpunkt  $t_{53}$  werden die Halbleiterschalter M2 und M3 leitend geschalten, so daß ein Strom  $I_1$  durch den Widerstand R fließen kann, welcher am Eingang IN1 eine Spannung UR erzeugt. Die Spannung am Eingang IN1 beginnt folglich von einem Wert V2 auf einen Wert UR anzusteigen. Dies hat in der Praxis einen sehr steilen Gratienten zur Folge. Dies ist in der Zeichnung der übersichtlichkeithalber jedoch mit einer leichten Rampe dargestellt. Gleichzeitig kann nun auch ein Strom  $I_2$  durch M1 und M3 fließen und den Kondensator C laden. Der damit an 8 verbundene Spannungsanstieg erfolgt jedoch deutlich langsamer als der an 7, so daß die Spannung an IN1 sehr schnell die Spannung U52 übersteigt. Übersteigt die am Eingang IN1 anliegende Spannung den Spannungswert V3, so ändert sich das am Ausgang des zweiten Differenzverstärkers anliegende Signal wiederum auf ein logisches H. Das Signal am Ausgang ST des logischen Verknüpfungselement 55 ändert sich demzufolge von einem logischen L auf ein logisches H und signalisiert einen Fehler. Gleichzeitig wird der Stromfluß im Referenzspannungszweig durch das Öffnen des Halbleiterschalters M1 unterbunden und C durch Einschalten von M5 entladen. Erst nachdem die Unterbrechung in der Rückkoppelleitung behoben ist, ändert sich das am Ausgang ST anliegende Signal wieder auf ein logisches L.

## Bezugszeichenliste

## [0031]

|     |                                                                                  |    |

|-----|----------------------------------------------------------------------------------|----|

| IN  | Eingang Spannungsregler                                                          | 5  |

| OUT | Ausgang Spannungsregler                                                          |    |

| LS  | Ladungsspeicher                                                                  |    |

| ULS | Ausgangsspannung                                                                 |    |

| tl  | Zeitspanne                                                                       |    |

| RL  | Rückkoppelleitung                                                                | 10 |

| IC  | integrierte Schaltung                                                            |    |

| IN1 | Eingang integrierte Schaltung                                                    |    |

| AN  | Ansteuerung                                                                      |    |

| SDU | Schaltungsanordnung zum Detektieren einer Unterbrechung in der Rückkoppelleitung | 15 |

| Vbb | positives Versorgungspotential                                                   |    |

| GND | Bezugspotential/Masse                                                            |    |

| SR1 | Spannungsregler                                                                  |    |

| S1  | Halbleiterschalter (MOSFET)                                                      |    |

| D1  | Diode                                                                            | 20 |

| L1  | Induktivität                                                                     |    |

| 1   | erster Versorgungspotentialanschluß                                              |    |

| 2   | zweiter Versorgungspotentialanschluß                                             |    |

| 3   | erste Stromquelle                                                                | 25 |

| 4   | zweite Stromquelle                                                               |    |

| 5   | Auswertung                                                                       |    |

| 6   | Spannungsquelle                                                                  |    |

| 7   | Verbindungspunkt                                                                 |    |

| 8   | Verbindungspunkt                                                                 |    |

| 51  | erster Eingang                                                                   | 30 |

| 52  | zweiter Eingang                                                                  |    |

| 53  | erster Differenzverstärker                                                       |    |

| 54  | zweiter Differenzverstärker                                                      |    |

| 55  | logisches Verknüpfungselement                                                    |    |

| 56  | Verbindungspunkt                                                                 | 35 |

| M1  | Halbleiterschalter (zweite Schaltvorrichtung)                                    |    |

| M3  | Halbleiterschalter (zweite Schaltvorrichtung)                                    |    |

| M2  | Halbleiterschalter (erste Schaltvorrichtung)                                     |    |

| M4  | Halbleiterschalter (erste Schaltvorrichtung)                                     |    |

| M5  | Halbleiterschalter                                                               | 40 |

| R   | Widerstand                                                                       |    |

| UR  | Spannung (an R)                                                                  |    |

| ST  | Ausgang von SDU                                                                  |    |

| C   | Ladungsspeicher                                                                  | 45 |

## Patentansprüche

- Spannungsregler (SR1), dessen Eingang (IN) mit einer ersten Versorgungsspannung (Vbb) verbunden ist und dessen Ausgangsspannung (Ua) an einem Ausgang (OUT) im Normalbetrieb über eine Rückkoppelleitung (RL) einem Eingang (IN1) einer integrierten Schaltung (IC) mit einer Ansteuerung (AN) zugeführt wird zur Überwachung und Regelung der Ausgangsspannung (Ua) auf einen vorgegebenen ersten Spannungswert durch die Ansteuerung (AN),

- dadurch gekennzeichnet,

daß eine Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung der Rückkoppelleitung (RL) vorgesehen ist und, daß am Ausgang (OUT) bei einer Unterbrechung von dem vorgegebenen ersten Spannungswert auf einen vorgegebenen zweiten Spannungswert umgeschaltet wird.

- Spannungsregler nach Patentanspruch 1, **dadurch gekennzeichnet**,

daß der Ausgang (OUT) mit einem massebezogenen, ersten Ladungsspeicher (LS) verbunden ist, wobei die an dem Ladungsspeicher (LS) abfallende Spannung (ULS) im Normalbetrieb der Ansteuerung und der Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung der Rückkoppelleitung (RL) zugeführt wird.

- Spannungsregler nach Patentanspruch 1 oder 2, **dadurch gekennzeichnet**,

daß die Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung der Rückkoppelleitung (RL) mit ihrem Ausgang (ST) mit der Ansteuerung (AN) verbunden ist.

- Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes nach einem der Patentansprüche 1 bis 3, **dadurch gekennzeichnet**,

daß im Falle einer Unterbrechung am Eingang (IN1) innerhalb einer zweiten Zeitspanne (t2) ein zweiter kleinerer, vorgegebener Spannungswert (UR) als die im Normalbetrieb abfallende Spannung (ULS) anliegt, der mit einem innerhalb einer dritten Zeitspanne (t3) ab dem Eintreten der Unterbrechung erzeugten Referenzspannungswert (Uref) jeweils einem Eingang (51,52) einer Auswertung (5) zugeführt wird, die ein Signal am Ausgang (ST) erzeugt, das der Auswertung (AN) zugeführt wird.

- Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes nach Patentanspruch 4, **dadurch gekennzeichnet**,

daß zur Erzeugung des zweiten Spannungswertes (UR) zwischen Versorgungspotentialanschlüssen (Vbb, GND) eine Serienschaltung aus einer ersten Stromquelle (3), einer ersten Schaltvorrichtung (M2) und einem Widerstand (R) vorgesehen ist, wobei der Verbindungspunkt (7) zwischen dem Widerstand (R) und der ersten Schaltungsvorrichtung (M2) einerseits mit dem Eingang (IN1) und andererseits mit dem ersten Eingang (51) der Auswertung (5) verschalten ist.

- Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten

- Spannungswertes nach einem der Patentansprüche 4 oder 5,

**dadurch gekennzeichnet**,

daß zur Erzeugung des Referenzspannungswertes (Uref) eine Serienschaltung aus einer zweiten Stromquelle (4), einer zweiten Schaltvorrichtung (M1, M3) und einem zweiten Ladungsspeicher (C) zwischen den Versorgungspotentialanschlüssen (Vbb, GND) vorgesehen ist, wobei der Verbindungspunkt zwischen dem zweiten Ladungsspeicher (C) und der zweiten Schaltvorrichtung (M1, M3) mit dem zweiten Eingang (52) der Auswertung (5) verschalten ist und wobei dem Ladungsspeicher (C) zumindest ein Halbleiterschalter (M4, M5) mit seiner Laststrecke parallel geschalten ist.

7. Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes Patentanspruch 6,

**dadurch gekennzeichnet**,

daß die zweite Schaltvorrichtung (M1, M3) zwei mit ihrer Laststrecke seriell verschaltete Halbleiterschalter aufweist.

8. Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes nach einem der Patentansprüche 4 bis 7,

**dadurch gekennzeichnet**,

daß die Auswertung einen ersten (53) und einen zweiten Differenzverstärker (54) aufweist, deren positive Eingänge miteinander und mit dem Eingang (IN1) verbunden sind und den ersten Eingang der Auswertung bilden,

daß der negative Eingang des ersten Differenzverstärkers (53) mit einer zwei Spannungswerten (V1, V2) bereitstellende Vorrichtung verbunden ist und

daß der negative Eingang des zweiten Differenzverstärkers (54) mit dem Verbindungspunkt zwischen dem zweiten Ladungsspeicher (C) und der zweiten Schaltvorrichtung (M1, M3) verbunden ist,

wobei der Ausgang des ersten Differenzverstärkers (53) einerseits die erste (M2) und die zweite Schaltvorrichtung (M3) im Fehlerfall leitend steuert, andererseits den Halbleiterschalter (M4) im Fehlerfall sperrend schaltet und weiterhin mit einem ersten Eingang eines logischen Verknüpfungsgliedes verbunden ist

und wobei der Ausgang des zweiten Differenzverstärkers (54) mit einem zweiten Eingang des logischen Verknüpfungsgliedes (55) verbunden ist und der Ausgang des logischen Verknüpfungsgliedes (55) mit dem Ausgang (ST) in Verbindung ist.

9. Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes nach Patentanspruch 8,

**dadurch gekennzeichnet**,

daß der Ausgang (ST) des logischen Verknüpfungsgliedes (55) im Fehlerfall die zweite Schaltvorrichtung (M1) sperrend und den Halbleiterschalter (M5) leitend schaltet.

10. Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes nach einem der Patentansprüche 8 oder 9,

**dadurch gekennzeichnet**,

daß der erste Eingang des logischen Verknüpfungsgliedes (55) invertierend ist und das logische Verknüpfungsglied (55) ansonsten ein UND-Gatter ist.

11. Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes nach einem der Patentansprüche 6 bis 10,

**dadurch gekennzeichnet**,

daß der erste Ladungsspeicher (LS) und der zweite Ladungsspeicher (C) Kondensatoren sind, wobei die Kapazität (C1) des ersten Ladungsspeichers (LS) größer als Kapazität (C2) des zweiten Ladungsspeichers (C) ist.

12. Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes nach einem der Patentansprüche 8 bis 11,

**dadurch gekennzeichnet**,

daß zwischen den negativen Eingang des zweiten Differenzverstärkers (54) und den Ladungsspeicher (C) eine Spannungsquelle (6) geschalten ist.

13. Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes nach einem der Patentansprüche 8 bis 12,

**dadurch gekennzeichnet**,

daß über ein externes Signal ( ) die Schaltungsanordnung in den Stand-by-Betrieb geschalten werden kann.

14. Schaltungsanordnung (SDU) zum Detektieren einer Unterbrechung eines vorgegebenen ersten Spannungswertes nach einem der Patentansprüche 8 bis 13,

**dadurch gekennzeichnet**,

daß der erste Differenzverstärker (53) als Schmitt-Trigger ausgeführt ist.

FIG 1

FIG 2

FIG 3A

FIG 3B

FIG 3C

Europäisches

Patentamt

## EUROPÄISCHER RECHERCHENBERICHT

Nummer der Anmeldung

EP 00 10 1965

| EINSCHLÄGIGE DOKUMENTE                                                                                                                                                                                                                               |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                         |                                         |                                      |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------|------|

| Kategorie                                                                                                                                                                                                                                            | Kennzeichnung des Dokuments mit Angabe, soweit erforderlich, der maßgeblichen Teile                                  | Betritt Anspruch                                                                                                                                                                                                                                                                                                                                        | KLASSIFIKATION DER ANMELDUNG (Int.Cl.7) |                                      |      |

| A                                                                                                                                                                                                                                                    | DE 42 24 243 C (SIEMENS AG)<br>5. Januar 1994 (1994-01-05)<br>* das ganze Dokument *<br>---                          | 1-14                                                                                                                                                                                                                                                                                                                                                    | G05F1/575                               |                                      |      |

| A                                                                                                                                                                                                                                                    | EP 0 883 051 A (SGS THOMSON<br>MICROELECTRONICS)<br>9. Dezember 1998 (1998-12-09)<br>* das ganze Dokument *<br>----- | 1-14                                                                                                                                                                                                                                                                                                                                                    |                                         |                                      |      |

| <table border="1"> <tr> <td>RECHERCHIERTE SACHGEBiete (Int.Cl.7)</td> </tr> <tr> <td>G05F</td> </tr> </table>                                                                                                                                        |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                         |                                         | RECHERCHIERTE SACHGEBiete (Int.Cl.7) | G05F |

| RECHERCHIERTE SACHGEBiete (Int.Cl.7)                                                                                                                                                                                                                 |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                         |                                         |                                      |      |

| G05F                                                                                                                                                                                                                                                 |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                         |                                         |                                      |      |

| <p>Der vorliegende Recherchenbericht wurde für alle Patentansprüche erstellt</p>                                                                                                                                                                     |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                         |                                         |                                      |      |

| Recherchenort                                                                                                                                                                                                                                        | Abschlußdatum der Recherche                                                                                          | Prüfer                                                                                                                                                                                                                                                                                                                                                  |                                         |                                      |      |

| DEN HAAG                                                                                                                                                                                                                                             | 19. Mai 2000                                                                                                         | Schobert, D                                                                                                                                                                                                                                                                                                                                             |                                         |                                      |      |

| KATEGORIE DER GENANNTEN DOKUMENTE                                                                                                                                                                                                                    |                                                                                                                      | T : der Erfindung zugrunde liegende Theorien oder Grundsätze<br>E : älteres Patentdokument, das jedoch erst am oder<br>nach dem Anmelde datum veröffentlicht worden ist<br>D : in der Anmeldung angeführtes Dokument<br>L : aus anderen Gründen angeführtes Dokument<br>-----<br>& : Mitglied der gleichen Patentfamilie, übereinstimmendes<br>Dokument |                                         |                                      |      |

| X : von besonderer Bedeutung allein betrachtet<br>Y : von besonderer Bedeutung in Verbindung mit einer anderen Veröffentlichung derselben Kategorie<br>A : technologischer Hintergrund<br>O : nichtschriftliche Offenbarung<br>P : Zwischenliteratur |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                         |                                         |                                      |      |

**ANHANG ZUM EUROPÄISCHEN RECHERCHENBERICHT

ÜBER DIE EUROPÄISCHE PATENTANMELDUNG NR.**

EP 00 10 1965

In diesem Anhang sind die Mitglieder der Patentfamilien der im obengenannten europäischen Recherchenbericht angeführten Patentdokumente angegeben.

Die Angaben über die Familienmitglieder entsprechen dem Stand der Datei des Europäischen Patentamts am

Diese Angaben dienen nur zur Unterrichtung und erfolgen ohne Gewähr.

19-05-2000

| Im Recherchenbericht<br>angeführtes Patentdokument |   | Datum der<br>Veröffentlichung | Mitglied(er) der<br>Patentfamilie | Datum der<br>Veröffentlichung |

|----------------------------------------------------|---|-------------------------------|-----------------------------------|-------------------------------|

| DE 4224243                                         | C | 05-01-1994                    | KEINE                             |                               |

| EP 0883051                                         | A | 09-12-1998                    | FR 2764450 A                      | 11-12-1998                    |

EPO FORM P0461

Für nähere Einzelheiten zu diesem Anhang : siehe Amtsblatt des Europäischen Patentamts, Nr.12/82