| (19) | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets                                                                    | (11) EP 1 069 768 A2                                                                                                                                                                                         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (12) | EUROPEAN PATENT APPLICATION                                                                                                                        |                                                                                                                                                                                                              |

| (43) | Date of publication:<br>17.01.2001 Bulletin 2001/03                                                                                                | (51) Int. CI. <sup>7</sup> : <b>H04N 5/44</b>                                                                                                                                                                |

| (21) | Application number: 00114589.5                                                                                                                     |                                                                                                                                                                                                              |

| (22) | Date of filing: 07.07.2000                                                                                                                         |                                                                                                                                                                                                              |

| (84) | Designated Contracting States:<br>AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU<br>MC NL PT SE<br>Designated Extension States:<br>AL LT LV MK RO SI | <ul> <li>Crabb, Michael Evan<br/>Carmel, IN 46033 (US)</li> <li>Flickner, Andrew Kent<br/>Carmel, IN 46032 (US)</li> <li>Li, Wenhua<br/>Brownsville, IN 46112 (US)</li> </ul>                                |

| (30) | Priority: 15.07.1999 US 144152                                                                                                                     |                                                                                                                                                                                                              |

| (72) | Applicant:<br>Thomson Licensing S.A.<br>92648 Boulogne Cedex (FR)<br>Inventors:<br>Worrell, Charles William<br>Carmel, IN 46032 (US)               | <ul> <li>(74) Representative:</li> <li>Hartnack, Wolfgang, DiplIng. et al<br/>Deutsche Thomson-Brandt GmbH<br/>European Patent Operations<br/>Karl-Wiechert-Allee 74</li> <li>30625 Hannover (DE)</li> </ul> |

|      | Carmel, IN 46032 (US)                                                                                                                              |                                                                                                                                                                                                              |

## (54) Processing of progressive video signals in digital TV receivers

(57) A memory management process (32) for buffering progressive, interlaced, CCIR 601/656 compliant, and MPEG compliant video signals in a video memory that is partitioned into first and second buffers. The process includes identifying the format (36,44) of a received video signal, buffering the received video signal in the video memory in accordance with a standard buffering mode if the video signal is in an interlaced, CCIR 601/656 compliant, or MPEG compliant format, and buffering the received video signal in the video memory in accordance with an override buffering mode (40, 46) if the video signal is in a progressive format such as a 240p signal generated by a game console, VCR, cable text generator, and the like.

10

15

20

25

35

40

45

## Description

**[0001]** The present invention relates to processing progressive video signals in digital TV receivers.

1

**[0002]** A standard Digital TV receiver architecture reuses MPEG digital video processing circuitry for the processing of digitized analog signals. Although this approach works well for processing digitized analog interlaced signals (e.g., NTSC and PAL signals having 480i or 1080i vertical formats), standard Digital TV receivers have difficulty processing the progressively scanned signals that are often produced by VCRs, video game consoles, and cable system text generators (e.g., progressively scanned signals having 240p vertical formats). The present invention is directed to overcoming this difficulty.

**[0003]** A memory management process for buffering digital video data of various formats (i.e., progressive, interlaced, CCIR 601/656 compliant, and MPEG compliant formats) in a video memory that is partitioned into first and second buffers.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0004] In the Drawings:

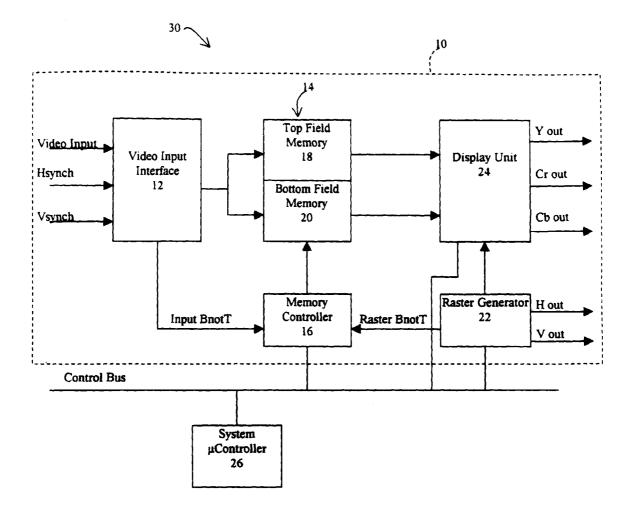

FIG. 1 is a logical system block diagram of video processing circuitry of a standard Digital TV receiver;

FIG. 2 is a timing diagram of the standard receiver *30* processing an interlaced input signal;

FIG. 3 is a timing diagram of the standard receiver processing a progressively scanned input signal;

FIG. 4 is a logical system block diagram of video processing circuitry in accordance with the present invention;

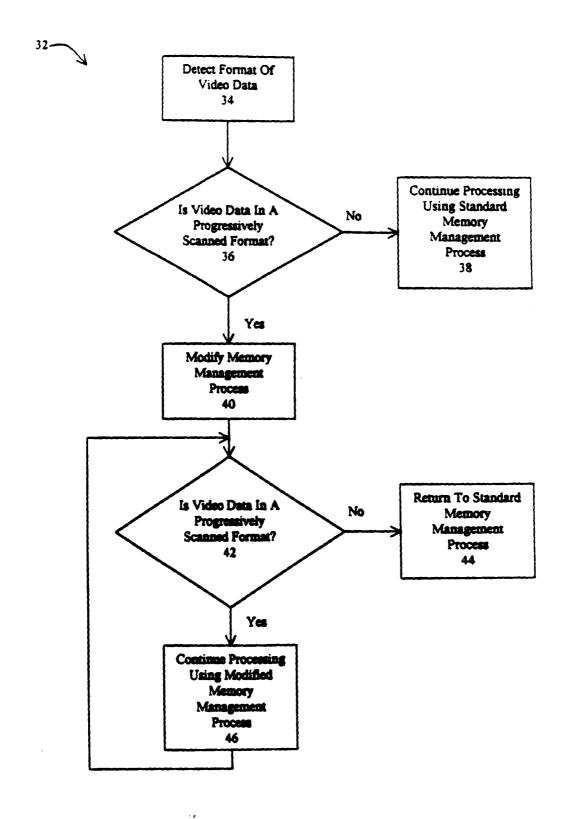

FIG. 5 is a flow chart illustrating a method of processing a progressively scanned video signal in accordance with the present invention;

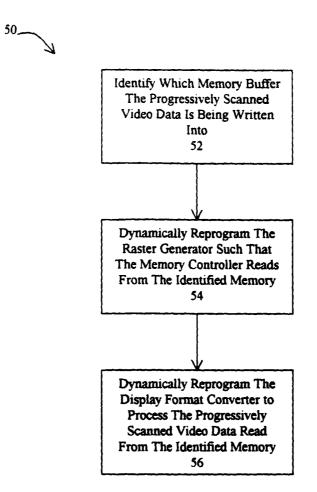

FIG. 6 is a flow chart illustrating a video memory management method in accordance with the present invention;

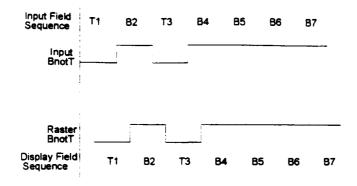

FIG. 7 is a timing diagram of an improved system processing a progressively scanned input signal in accordance with the video memory management method of FIG. 4;

FIG. 8 is a flow chart illustrating an alternative memory management method in accordance with the present invention;

FIG. 9 is a block diagram of field type detector cir- 50 cuitry of the video interface of FIG. 4; and

FIG. 10 is a timing diagram for the field type detector circuitry of FIG. 9;

FIG. 11 is a timing diagram of an improved system processing a progressively scanned input signal in *55* accordance with the alternative memory management method of FIG. 8. **[0005]** The characteristics and advantages of the present invention will become more apparent from the following description, given by way of example.

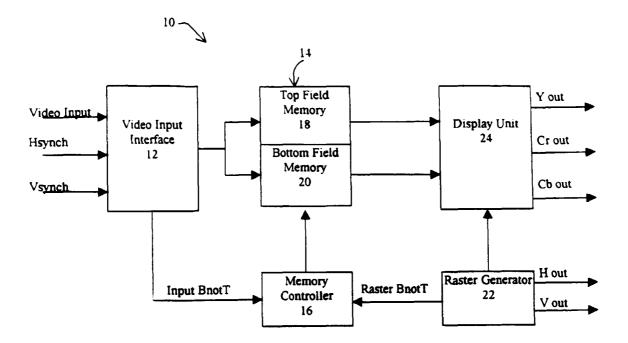

**[0006]** Referring to FIG. 1, the video processing circuitry 10 of a standard Digital TV receiver is shown. A video input interface 12 is coupled to a memory 14 and a memory controller 16. Memory controller 16 controls the buffering of MPEG compliant video data, CCIR 601/656 compliant video data, and digitized analog signals in memory 14, as described in further detail below. A raster generator 22 is also coupled to memory controller 16 as well as to a display unit 24 that includes display format conversion circuitry and OSD overlay circuitry.

[0007] Video input interface 12 is a video input port that manages the demuxing, sync processing, and field type detection of an input video signal. Video input interface 12 is capable of operating in two modes. One mode for receiving a CCIR 601/656 compliant bitstream and the other mode for receiving digitized analog signals. In the first mode, video input interface 12 extracts a known top/bottom field indication from a CCIR 601/656 compliant bitstream. In the second mode, blanking information is provided on Hsynch and Vsynch inputs of video input interface 12 and video input interface 12 derives the top/bottom field indication from the relative timing of the Hsynch and Vsynch inputs. More specifically, for an interlaced signal the Vsynch input will toggle between aligning with the Hsynch input and occurring between consecutive Hsynch inputs. For a progressive signal the Vsynch input will not toggle and will either align with the Hsynch input or occur between consecutive Hsynch inputs. Thus, alternating top and bottom indicators will be derived for an interlaced signal and either top or bottom indicators will be derived for a progressive signal. Once the top/bottom field indication is extracted (in the case of a CCIR compliant bitstream) or derived (in the case of a digitized analog signal), video input interface 12 generates an Input BnotT signal based on the top/bottom field indication and passes the signal to memory controller 16. More specifically, a field type detector (not shown) within video input interface 12 generates a "high" Input BnotT signal in response to a bottom field indicator and generates a "low" Input BnotT signal in response to a top field indicator.

**[0008]** It should be noted that MPEG decoding circuitry (not shown to simplify the drawings) may be distinct from or integrated with video input interface 12 for the decoding of an MPEG compliant bitstream, as known by those skilled in the art. During the decoding of an MPEG compliant bitstream, memory controller 16, in response to signals generated by the MPEG decoding circuitry, utilizes memory 14 for buffering the incoming compressed bitstream, storing anchor frames, and for storing the decoded video frames. Once a frame of video has been stored in memory 14 it is processed by display unit 24 in the same fashion as the processing of the CCIR 601/656 compliant and interlaced video sig-

nals described below.

Memory controller 16 manages the transfer [0009] of video data (e.g., MPEG compliant data, CCIR 601/656 compliant data, interlaced fields, and progressively scanned frames) to and from memory 14. More specifically, memory 14 is partitioned into two buffers (top field memory 18 and bottom field memory 20) and memory controller 16 manages the input of the video data to buffers 18 and 20 based upon the state of the Input BnotT signal transmitted by video input interface 12 or, in the case of the reception of an MPEG compliant datastream, based upon a signal generated by MPEG decoding circuitry. Memory controller 16 also manages the output of the stored video data from buffers 18 and 20 to display unit 24 which, in turn, processes the outputted data such that the data is adapted to a desired display format and combined with a desired OSD. Memory controller 16 manages the output of the video data from buffers 18 and 20 based upon the state of a Raster BnotT signal transmitted by raster generator 22.

[0010] The Raster BnotT and Input BnotT signals are generated separately and may not be phase or frequency locked. Video input interface 12 generates the Input BnotT signal based on the top/bottom field indicators extracted from a CCIR 601/656 compliant bitstream or derived from the relationship between the Hsynch and Vsynch inputs of a digitized analog signal (e.g., an interlaced or progressive signal). Raster generator 22 generates the Raster BnotT signal asynchronously from the Input BnotT signal. The Raster BnotT signal is an independent raster signal generated by counters driven from VCXO derived pixel clock. The Raster BnotT signal provides a stable drive signal to the deflection system of display unit 24 and controls the sequence of fields retrieved from memory. Although the asynchronous relationship between the Input BnotT and Raster BnotT signals does not interfere with the storage and retrieval of MPEG compliant data, CCIR 601/656 compliant data, and interlaced video data, the asynchronous relationship interferes with the storage and retrieval of progressively scanned video data (e.g., video data in a 240p vertical format), as shown below.

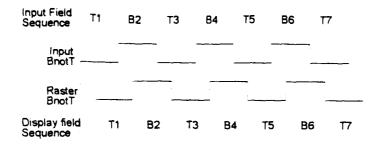

[0011] Referring now to FIG. 2, a timing diagram for the storage and retrieval of an interlaced signal is shown. More particularly, the relationship between the input video data, output video data, Input BnotT signal and Raster BnotT signal is shown. An indexed sequence of fields represents the memory location of the input and output video signal data, where T = top field memory and B = bottom field memory. Memory controller 16 writes the input data into bottom field memory 20 upon reception of a "high" Input BnotT signal and writes the input data into top field memory 18 upon reception of a "low" Input BnotT signal. Similarly, memory controller 16 reads the output data from bottom memory 16 upon reception of a "high" Raster BnotT signal and reads the output data from top field memory 18

upon reception of a "low" Raster BnotT signal. As shown in FIG. 2, the asynchronous relationship between the Input BnotT and Raster BnotT signals does not interfere with the proper storage and retrieval of video data for interlaced video signals.

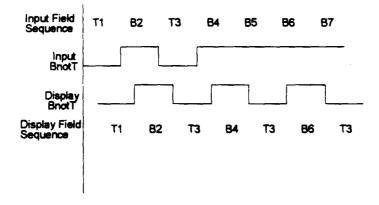

Referring now to FIG. 3, a timing diagram [0012] illustrating the storage and retrieval of video data for an interlaced video signal followed by a progressive video signal is shown. Fields 1-4 correspond to fields of interlaced video data and are stored and retrieved from top 10 and bottom field memories 18 and 20, as discussed above in the description of FIG. 2. Field 5 corresponds to a first frame of progressively scanned video data (e.g., a progressive video signal received from a game console or VCR that has been turned on by a user). At 15 Field 5 the Input BnotT signal remains "high" indicating that the progressively scanned video data, for this exemplary timing diagram, has the same Hsynch/Vsynch relationship as the Field 4 portion of the 20 interlaced video data. Since Input BnotT remains "high" memory controller 16 writes the frame of progressively scanned video data into bottom field memory 20. At fields 6 and 7 memory controller 16 continues to write the frames of progressively scanned video data into bottom field memory 20 since the top/bottom indication 25 associated with the frames of progressively scanned video data does not change. In response to the reception of the Raster BnotT signal, memory controller 16 correctly reads the fields of interlaced video data from memory 14 (fields 1-4). However, memory controller 16 30 incorrectly reads the frames of progressively scanned video data from memory 14 (fields 5-7). More specifically, at fields 5 and 7 memory controller 16 reads stale video data from memory 14 (i.e., the interlaced video data of field 3) due to the reception of a "low" Raster 35 BnotT signal from raster generator 22. This stale data will continue to be read out of top field memory 14 during the processing of the progressively scanned video data and will cause significant distortions in the video image displayed to a user. The present invention is 40 directed to correcting this problem.

**[0013]** Referring now to FIG. 4, a block diagram of video processing circuitry 30 of the present invention is shown and includes a system microcontroller 26 coupled to the video processing elements 10 of FIG. 1. More specifically, system microcontroller 26 is coupled to memory controller 16, raster generator 22, and display unit 24 such that video data in a progressively scanned format, an interlaced format, a CCIR 601/656 compliant format, or a MPEG compliant format is correctly stored in and retrieved from memory 14.

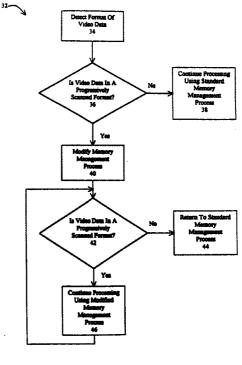

**[0014]** Referring now to FIG. 5, in conjunction with FIG. 4, a method 32 of processing progressively scanned video data is shown. The progressively scanned video data may be a 240p input generated by a video game console, VCR, cable system text generator, or the like. Initially, system microcontroller 26, at step 34, determines the format of the video data

3

45

50

15

20

25

30

35

received by video input interface 12 by reading the Input BnotT signal received by memory controller 16. As explained above, when the Input BnotT signal toggles between high and low states the video format is not progressive (e.g., fields 1-4 of FIG. 3). When the Input BnotT signal remains constant (i.e., low or high) for two or more consecutive periods the video format is progressive (e.g., fields 5-7 of FIG. 3). It should be noted that system microcontroller 26 may determine if video data in an MPEG compliant format is being received by monitoring the signals generated by MPEG decoding circuitry, as known by those skilled in the art. Next, at step 36, system microcontroller 26 determines if the video data is in a progressively scanned format. If not, system microcontroller 26, at step 38, continues to process the video data using the standard memory management process described above. If so, system microcontroller 26, at step 40, modifies or partially overrides the memory management process in accordance with the present invention, as described in further detail below. Afterwards, at step 42, system microcontroller 26 continues to monitor the Input BnotT signal received by memory controller 16 to determine if the video data is still being received in a progressively scanned format. If not, system microcontroller 26, at step 44, returns to the standard memory management process used for the processing of non-progressive video data. If so, system microcontroller 26, at step 46, continues to process the progressively scanned video data using the modified memory management process of step 40 and returns to step 42 to monitor the Input BnotT signal.

[0015] Referring now to FIGS. 6 and 7, in conjunction with FIG. 4, one memory management process 50 of the present invention is shown. After the format of the video data received by video input interface 12 is identified as progressive, system microcontroller 26, at step 52, monitors the state of the Input BnotT signal to identify which memory buffer (i.e., top field memory 18 or bottom field memory 20) is being written with the progressively scanned video data. Once the memory is identified, system microcontroller 26, at step 54, dynamically reprograms raster generator 22 such that memory controller 16 correctly reads the progressively scanned video data from the identified memory buffer (i.e., top field memory 18 or bottom field memory 20). As shown in the exemplary timing diagram of FIG. 7, if system microcontroller 26 determines that progressive video data is being written into bottom field memory 20 (i.e., the Input BnotT signal is "high"), system microcontroller 26 dynamically reprograms raster generator 22 to output a "high" Raster BnotT signal. The "high" Raster BnotT signal will force memory controller 16 to read the progressive video data from bottom field memory 20. System microcontroller 26, at step 56, also dynamically reprograms display unit 24 to process the progressively scanned video data received from the identified memory buffer of memory 14. For example, system microcontroller 26 may dynamically reprogram display unit 24

to convert a 240p signal retrieved from memory 14 to 540p, 1080i, or some other vertical format required by a monitor or TV.

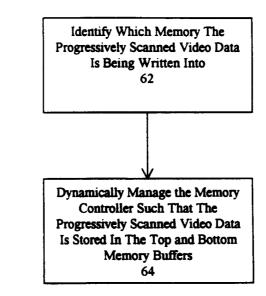

[0016] Turning now to FIG. 8, in conjunction with FIG. 4, an alternative memory management process 60 of the present invention is shown. After the video data format received by video input interface 12 is identified as progressive, system microcontroller 26, at step 62, monitors the state of the Input BnotT signal to identify 10 which memory buffer (i.e., top field memory 18 or bottom field memory 20) is being written with the progressively scanned video data. Next, at step 64, system microcontroller 26 dynamically manages memory controller 16 such that memory controller 16 alternately writes the progressively scanned video data into top and bottom field memories 18 and 20 of memory 14.

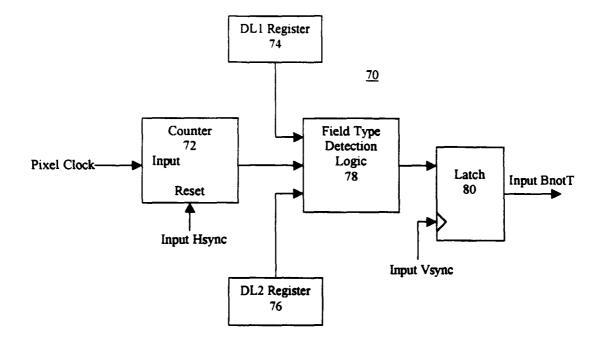

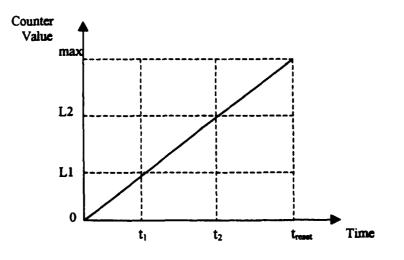

[0017] In order to force memory controller 16 to alternately write the progressively scanned video data, system microcontroller 26 must override the Input BnotT signal. As stated previously, a field type detector within Video Input Interface 12 generates the Input BnotT signal. A block diagram of an exemplary field type detector 70 is shown in FIG. 9 and a timing diagram for field type detector 70 is shown in FIG. 10. Field type detector 70 includes a horizontal sample counter 72 having a pixel clock and Hsynch as inputs and having an output coupled to field type detector logic 78. An input of field type detector logic 78 is also coupled to an output of a first register 74 which, in turn, is coupled to system microcontroller 26 (not shown in FIG. 9). Similarly, another input of field type detector logic 78 is coupled to an output of a second register 76 which, in turn, is coupled to system microcontroller 26 (not shown in FIG. 9). An output of field type detector logic 78 is coupled to an input of a latch 80. Latch 80 generates the Input BnotT signal and is triggered by a Vsynch signal. [0018] In operation, horizontal sample counter 72 is

driven by the input pixel clock and is reset and restarted by an Hsynch signal. The output of counter 72 is compared to system microcontroller programmable values 40 L1 and L2 stored in registers 74 and 76, respectively. During standard operation (when input BnotT is not being overridden), if the output of counter 72 is between value L1 and value L2 (during the time t1 < t < t2) the output of field type detection logic 78 is high and the 45 Input BnotT signal from latch 80 is high. In response to the high Input BnotT signal, memory controller 16 reads data into bottom field memory 20. During standard operation, if the output of counter 72 is below L1 or above L2 (during the time t<t1 OR t> t2) the output of field type detection logic 78 is low and the input BnotT signal is low. As a result, memory controller 16 writes video data into top field memory 18.

[0019] As described above, system microcontroller 55 26 detects the presence of progressively scanned video data by monitoring two or more identical Input BnotT signals. If a progressively scanned video signal is detected, the value of registers 74 and 76 may be

4

10

15

20

25

30

35

45

50

55

adjusted to force the Input BnotT signal into desired states (i.e., into states that will cause memory controller 16 to write the progressively scanned video data into alternating top and bottom memories 18 and 20).

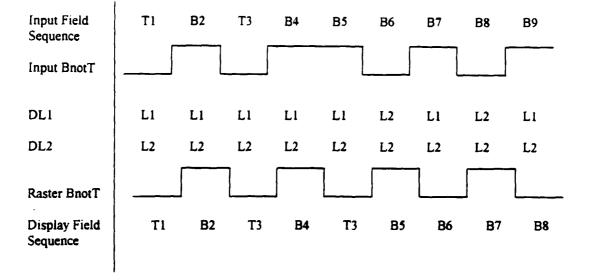

[0020] Turning to FIG. 11, in conjunction with Figs. 9 and 10, a timing diagram illustrating the operation of field type detector 70 in the override mode is illustrated. For fields numbered 1 through 4, the input signal is interlaced. At field 5, the input signal becomes progressive. Microcontroller 26 detects the progressive signal and determines whether the first segment (e.g., a 240p frame) of the progressive signal is being stored in top field memory 18 or bottom field memory 20. If the first segment of the progressive signal is stored in bottom field memory 20 (as shown), microcontroller 26 sets registers 74 and 76 equal to the same value (e.g., L2) for the next segment of the progressive signal. This forces Input BnotT low on field 6 since the output of counter can never be between the values in registers 74 and 76 if both registers contain the same value. Forcing Input BnotT low causes field 6 to overwrite the stale data in the top field memory 18 (i.e., the data corresponding to field 3). Afterwards, system microcontroller 26 alternates between allowing Input BnotT to go high and forcing Input BnotT to go low such that the progressive video data is written into top and bottom field memories 18 and 20. If the first segment of the progressive signal had been stored in top field memory 18 (not shown in FIG. 11), microcontroller 26 would set register 74 equal to zero and set register 76 equal to or greater than the maximum value that counter 72 could reach before being reset by a Hsynch input. This would force Input BnotT high since the output of counter could never be less than the value stored in register 74 or greater than the value stored in register 76. Forcing Input BnotT high would cause the next segment of the progressive signal to overwrite the stale data in that would be present in the bottom field memory 20. Afterwards, system microcontroller 26 would alternately write the progressive signal into top and bottom field memories 18 40 and 20 in a manner similar to that shown in FIG. 11.

Thus according to the principle of the [0021] present invention, there is provided a method of memory management for buffering digital video data of various formats (i.e., progressive, interlaced, CCIR 601/656 compliant, and MPEG compliant formats) in a video memory that is partitioned into first and second buffers. While the present invention has been [0022] described with reference to the preferred embodiments, it is apparent that that various changes may be made in the embodiments without departing from the spirit and the scope of the invention, as defined by the appended claims.

## Claims

1. A memory management process for buffering video signals in a memory, the process characterised by the steps of:

identifying a format of a received video signal;

- buffering the received video signal in the memory in accordance with a standard buffering mode if the received video signal is in a first format; and

- partially overriding the standard buffering mode to buffer the received video signal in the memory if the received video signal is in a second format.

- 2. The process of claim 1, characterised in that the second format is a digitised analog progressive (p) format or a 240p vertical format.

- 3. The process of claim 1 or 2, characterised in that the received signal in the second format is generated by one of a video game console, a VCR, and a cable text generator.

- 4. The process of any of claims 1 to 3, characterised in that the first format is one of an interlaced format, a CCIR 601/656 compliant format, and an MPEG compliant format.

- 5. The memory management process of any of claims 1 to 4, characterised in that the memory is partitioned into first and second buffers and the step of partially overriding the standard buffering mode includes the step of:

- overriding the standard buffering mode such that the received video signal is only written into and read from one of the first or second buffers, or is alternately written into and read from the first and second buffers.

- 6. A buffering system in a digital TV receiver for process-ing video signals having a plurality of formats, the buffering system characterised by:

- a memory for buffering the video signals;

- a controller for adapting the memory to buffer video signals in accordance with a first buffering mode and a second buffering mode, the second buffering mode being a partial override of the first buffering mode and being utilized for the buffering of a video signal having a progressive format.

- 7. The buffering system of claim 6, characterised in that the controller adapts the memory to buffer video signals in accordance with the first buffering mode when the video signals are in one of an interlaced format, a CCIR 601/656 compliant format, and an MPEG compliant format.

- 8. The buffering system of claim 6 or 7, characterised in that the progressive format is a 240p vertical format, or a digitised analog progressive format.

- **9.** The buffering system of any of claims 6 to 8, char- *5* acterised in that the video signal having a progressive format is generated by one of a video game console, a VCR, and a cable text generator.

- 10. The buffering system of any of claims 6 to 9, characterised in that the memory is partitioned into first and second buffers and the second buffering mode partially overrides the first buffering mode such that the video signal having the progressive format is written into and read from one of the first or second buffers, or is alternately written into and read from the first and second buffers.

- **11.** The buffering system of any of claims 6 to 10, characterised in that the first buffering mode is a standard buffering mode for buffering video signals in the memory and the second buffering mode partially overrides the first buffering mode such that the video signal having the progressive format is buffered in the memory without the loss of frames of data.

35

40

45

50

EP 1 069 768 A2

**FIG.** 1

FIG. 3

FIG. 4

FIG. 5

\$

•

FIG. 6

60 -

**FIG. 8**

**FIG. 10**

**FIG. 11**