(11) **EP 1 083 471 A1**

(12) **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication: 14.03.2001 Bulletin 2001/11

(21) Numéro de dépôt: **00119687.2**

(22) Date de dépôt: 08.09.2000

(51) Int. CI.<sup>7</sup>: **G05F 1/46**, H03K 17/56, G05F 1/565

(84) Etats contractants désignés:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE

Etats d'extension désignés:

AL LT LV MK RO SI

(30) Priorité: 10.09.1999 FR 9911492

(71) Demandeur: STMicroelectronics SA 94250 Gentilly Cedex (FR)

(72) Inventeur: Gailhard, Bruno 13530 Trets (FR)

(74) Mandataire: Marchand, André

OMNIPAT,

24 Place des Martyrs de la Résistance

13100 Aix-en-Provence (FR)

# (54) Régulateur de tension

(57) L'invention concerne un régulateur de tension (10) comprenant un condensateur ( $C_{REG}$ ) délivrant sur son anode une tension régulée ( $V_{REG}$ ), un interrupteur de régulation (SW1) pour connecter le condensateur ( $C_{REG}$ ) à une source de tension ( $V_{DD}$ ), et des moyens de régulation (11) agencés pour fermer l'interrupteur (SW1) quand la tension régulée ( $V_{REG}$ ) est inférieure à une première tension de référence ( $V_{REF1}$ ). Selon

l'invention, le régulateur (10) comprend au moins un interrupteur ballast (SW2) en parallèle avec l'interrupteur de régulation (SW1), et des moyens (11) pour ouvrir l'interrupteur de régulation (SW1) et fermer l'interrupteur ballast (SW2) pendant une phase de démarrage du régulateur.

EP 1 083 471 A1

### Description

**[0001]** La présente invention concerne un régulateur de tension comprenant un condensateur délivrant sur son anode une tension régulée, un interrupteur de régulation pour connecter le condensateur à une source de tension et des moyens de régulation agencés pour fermer l'interrupteur quand la tension régulée est inférieure à une première tension de référence.

**[0002]** Les régulateurs de tension trouvent diverses applications dans le domaine de l'électronique, par exemple pour délivrer une tension régulée servant à alimenter électriquement les ports d'un microprocesseur.

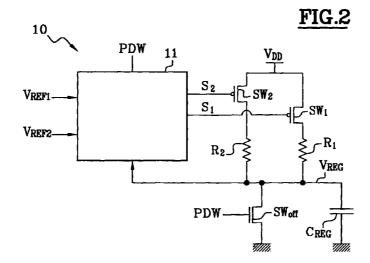

[0003] La figure 1 représente un régulateur de tension classique 1, incorporé dans un microprocesseur 2. Le microprocesseur 2 est alimenté par une pile électrique 3 de résistance interne  $r_i$ , délivrant une tension  $V_{DD}$ . Le régulateur 1 comprend un condensateur externe  $C_{REG}$  délivrant sur son anode une tension régulée  $V_{REG}$ . L'anode du condensateur  $C_{REG}$  est reliée à l'anode de la pile 3 par l'intermédiaire d'un interrupteur de régulation  $SW_1$  présentant une résistance série  $R_1$  nulle ou de faible valeur. L'interrupteur  $SW_1$  est piloté par la sortie d'un circuit suiveur CP recevant sur son entrée positive la tension régulée  $V_{REG}$  et sur son entrée négative une tension de référence  $V_{REF}$ . La tension  $V_{REF}$  est classiquement une tension dite de band-gap présentant une bonne stabilité en fonction de la température, générée au moyen de diodes à jonction PN et de miroirs de courant. Le circuit suiveur CP est contrôlé par un signal PDW (Power-Down) et l'anode du condensateur  $C_{REG}$  est reliée à la masse par un interrupteur  $SW_{OFF}$  piloté par le signal PDW. Lorsque le signal PDW est égal à 1, le circuit suiveur CP est bloqué et l'interrupteur  $SW_{OFF}$  est fermé. Le régulateur 1 est à l'arrêt et le condensateur  $C_{REG}$  est déchargé.

[0004] L'inconvénient d'un tel régulateur est de présenter une forte consommation de courant au démarrage. Ainsi, lorsque le signal PDW est mis à 0, le condensateur  $C_{REG}$  est déchargé et la tension  $V_{REG}$  est nulle. La sortie du circuit suiveur CP passe à 0 et l'interrupteur  $SW_1$  se ferme. L'application de la tension  $V_{DD}$  sur le condensateur  $C_{REG}$  provoque un fort appel de courant et une chute importante de la tension d'alimentation  $V_{DD}$  du microprocesseur 2, en raison de la résistance interne  $r_i$  de la pile 3. Si au même instant d'autres éléments du microprocesseur 2 consomment un courant non négligeable, il peut se produire que la tension  $V_{DD}$  devienne inférieure à la tension minimale de fonctionnement du microprocesseur 2, de sorte que le microprocesseur 2 se bloque.

[0005] La présente invention vise à pallier cet inconvénient.

[0006] Plus particulièrement, la présente invention vise à limiter le courant de démarrage d'un régulateur sans augmenter la résistance série de l'interrupteur de régulation.

**[0007]** A cet effet, la présente invention prévoit un régulateur du type décrit ci-dessus, comprenant au moins un interrupteur ballast en parallèle avec l'interrupteur de régulation, et des moyens pour ouvrir l'interrupteur de régulation et fermer l'interrupteur ballast au moins pendant une phase de démarrage du régulateur, jusqu'à ce que le condensateur soit au moins partiellement chargé.

**[0008]** Selon un mode de réalisation, le régulateur comprend des moyens pour ouvrir l'interrupteur de régulation et fermer l'interrupteur ballast quand la tension régulée est inférieure à une deuxième tension de référence inférieure à la première tension de référence.

[0009] Selon un mode de réalisation, la deuxième tension de référence est une fraction de la première tension de référence.

[0010] Selon un mode de réalisation, un signal commun de commande de l'interrupteur de régulation et de l'interrupteur ballast est appliqué à l'interrupteur de régulation par l'intermédiaire d'un interrupteur inhibiteur.

**[0011]** Selon un mode de réalisation, l'interrupteur inhibiteur est piloté par un signal délivré par un comparateur recevant en entrée la tension régulée et une deuxième tension de référence inférieure à la première tension de référence.

[0012] Selon un mode de réalisation, le régulateur comprend un circuit suiveur recevant en entrée la tension régulée et la première tension de référence, le circuit suiveur délivrant un signal de régulation, et un comparateur recevant en entrée la tension régulée et une deuxième tension de référence inférieure à la première tension de référence. Le signal de régulation est appliqué sur l'entrée de commande de l'interrupteur ballast et est appliqué sur l'entrée de commande de l'interrupteur de régulation par l'intermédiaire d'un interrupteur inhibiteur. La sortie du comparateur est appliquée sur l'entrée de commande de l'interrupteur inhibiteur.

[0013] Selon un mode de réalisation, l'interrupteur ballast est un transistor MOS comprenant une résistance intrinsèque non négligeable.

[0014] Selon un mode de réalisation, la source de tension est une pile électrique.

**[0015]** La présente invention concerne également un circuit intégré, notamment un microprocesseur, comprenant un régulateur selon l'invention.

[0016] Ces objets, caractéristiques et avantages de la présente invention seront exposés plus en détail dans la description suivante d'un régulateur de tension selon l'invention, en relation avec les figures jointes parmi lesquelles :

- la figure 1 précédemment décrite est le schéma électrique d'un régulateur de tension classique,

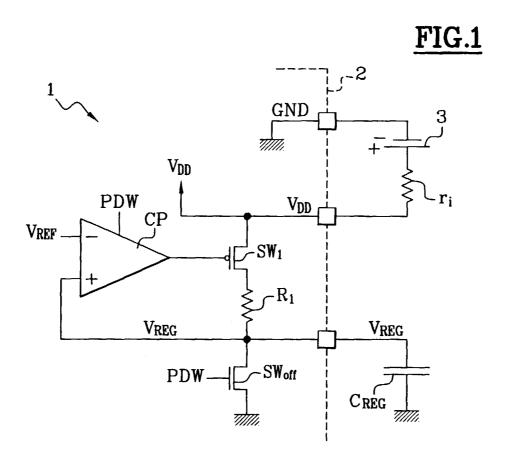

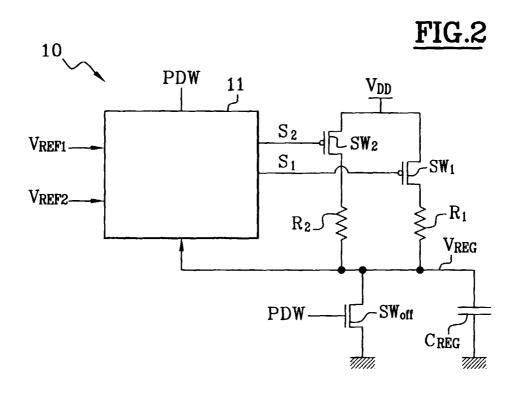

- la figure 2 est le schéma de principe d'un régulateur de tension selon l'invention, et

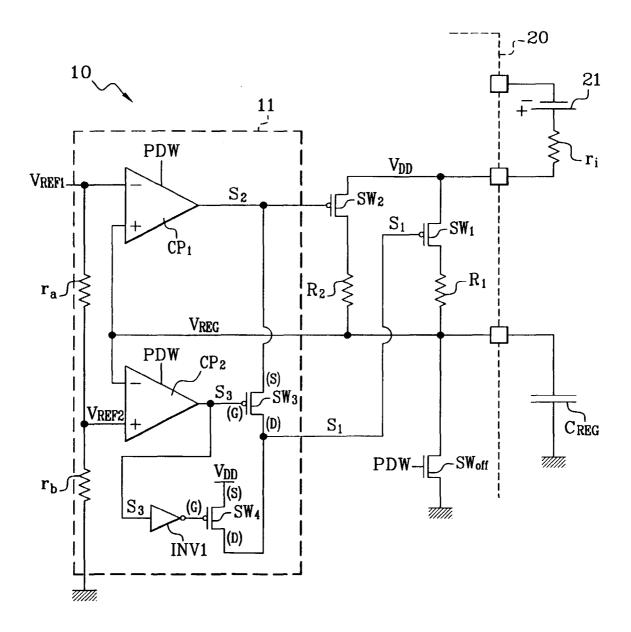

- la figure 3 est le schéma électrique d'un mode de réalisation d'un régulateur de tension selon l'invention.

[0017] La figure 2 représente un régulateur de tension selon l'invention. Le régulateur 10 comprend de façon classique un condensateur C<sub>REG</sub> dont l'anode est reliée à une source de tension V<sub>DD</sub> par un interrupteur de régulation SW1, ici un transistor PMOS, comportant une résistance série R1 nulle ou de faible valeur. L'anode du condensateur C<sub>REG</sub>, qui délivre une tension régulée V<sub>REG</sub>, est reliée à la masse par un interrupteur SW<sub>OFF</sub> piloté par un signal de remise à zéro PDW (Power-Down).

[0018] Selon l'invention, un interrupteur ballast SW2 est connecté en parallèle avec l'interrupteur SW1. L'interrupteur SW2 présente une résistance série R2 non négligeable, par exemple de l'ordre de quelques centaines d'ohms. L'interrupteur SW2 est ici un transistor PMOS et la résistance R2 est la résistance intrinsèque du transistor, c'est-à-dire sa résistance série (R<sub>ON</sub>) à l'étant passant. La valeur de la résistance R2 est ainsi déterminée par le choix du rapport W/L entre la largeur W et la longueur L de la grille du transistor.

[0019] Les interrupteurs SW1, SW2 sont pilotés par un circuit 11, représenté ici sous forme de bloc, contrôlé par le signal PDW. Le circuit 11 reçoit en entrée la tension V<sub>REG</sub>, une première tension de référence V<sub>REF1</sub> et une deuxième tension de référence V<sub>REF2</sub>. La tension V<sub>REF2</sub> est inférieure à V<sub>REF1</sub> et est par exemple égale à 0,75 V<sub>REF1</sub>. Le circuit 11 délivre un signal S1 de commande de l'interrupteur SW1 et un signal S2 de commande de l'interrupteur SW2 (les signaux S1, S2 étant ici appliqués sur les grilles des transistors PMOS).

[0020] Lorsque le signal PDW est à 1, le circuit 11 est bloqué et l'interrupteur  $SW_{OFF}$  est fermé. Le condensateur  $C_{REG}$  est déchargé et la tension  $V_{REG}$  est nulle. Lorsque le signal PDW est mis à 0, le circuit 11 démarre et le condensateur  $C_{REG}$  se charge. Le fonctionnement du régulateur 10 et du circuit 11 est décrit par le tableau 1 ci-après. Les interrupteurs SW1, SW2 étant ici des transistors PMOS, la valeur active des signaux S1, S2 correspondant à la fermeture des interrupteurs SW1, SW2 (état passant) est la valeur 0 (grille des transistors à la masse). Lorsque les signaux S1, S2 sont à 1 (tension  $V_{DD}$ ), les interrupteurs sont ouverts (transistors dans l'état bloqué).

25

30

35

15

5

#### Tableau 1

| V <sub>REG</sub>                                              | S1 | SW1    | S2     | SW2             |

|---------------------------------------------------------------|----|--------|--------|-----------------|

| (E1) V <sub>REG</sub> < V <sub>REF2</sub>                     | 1  | ouvert | 0      | fermé           |

| (E2) V <sub>REF2</sub> < V <sub>REG</sub> < V <sub>REF1</sub> | 0  | fermé  | 0 ou 1 | fermé ou ouvert |

| (E3) V <sub>REG</sub> > V <sub>REF1</sub>                     | 1  | ouvert | 1      | ouvert          |

[0021] Ainsi, au démarrage du régulateur 10, le condensateur  $C_{REG}$  se charge en deux périodes E1, E2. Pendant la période E1, l'interrupteur ballast SW2 est fermé et l'interrupteur de régulation SW1 est ouvert. La charge du condensateur  $C_{REG}$  s'effectue par l'intermédiaire de l'interrupteur ballast SW2 et le courant de démarrage est limité par la résistance R2. Le risque de voir la tension d'alimentation  $V_{DD}$  diminuer fortement est ainsi supprimé, notamment lorsque la tension  $V_{DD}$  est délivrée par une pile électrique ou un générateur de tension ayant une résistance interne non négligeable.

**[0022]** La période E2 intervient quand la tension  $V_{REG}$  dépasse le seuil  $V_{REF2}$ . L'interrupteur SW1 se ferme et le cycle de charge du condensateur  $C_{REG}$  se termine rapidement puisque la résistance R1 est nulle ou de faible valeur. Pendant la période E2, l'interrupteur ballast SW2 peut, indifféremment, être maintenu ouvert ou fermé.

[0023] Lorsque le condensateur C<sub>REG</sub> est chargé, le régulateur 10 fonctionne de façon classique, l'interrupteur de régulation SW1 étant fermé (période E2) ou ouvert (période E3) selon que la tension V<sub>REG</sub> est inférieure ou supérieure à V<sub>REF1</sub>. La tension V<sub>REG</sub> est ainsi asservie au voisinage de V<sub>REF1</sub> avec alternance des périodes E2 et E3. Pendant les périodes de dépassement E3, l'interrupteur ballast SW2 est toujours ouvert.

**[0024]** Un mode de réalisation avantageux du circuit 11 est représenté sur la figure 3. De façon non limitative, le régulateur 10 est représenté incorporé dans un circuit intégré 20, par exemple un microprocesseur, et la tension  $V_{DD}$  est délivrée par une pile électrique 21 de résistance interne  $r_i$ .

[0025] Le circuit 11 comprend un amplificateur opérationnel C1 agencé en circuit suiveur et un comparateur CP2. Le circuit suiveur CP1 et le comparateur CP2 sont contrôlés par le signal PDW. Le circuit suiveur CP1 reçoit sur son entrée négative la tension  $V_{REF1}$  et sur son entrée positive la tension régulée  $V_{REG}$ . La sortie du circuit suiveur CP1 délivre le signal S2 qui est appliqué sur l'entrée de commande de l'interrupteur SW2. Le comparateur CP2 reçoit sur son entrée positive la tension  $V_{REF2}$  et sur son entrée négative la tension  $V_{REG}$ . La tension  $V_{REF2}$  est obtenue ici par division de la tension  $V_{REF1}$  au moyen d'un pont diviseur comprenant deux résistances  $V_{REF2}$ 0. La sortie du comparateur CP2 délivre un signal S3 qui est appliqué sur l'entrée de commande d'un interrupteur SW3, ici un transistor PMOS, ainsi qu'à l'entrée d'une porte inverseuse INV1. La sortie de la porte INV1 est connectée à l'entrée de commande d'un

3

#### EP 1 083 471 A1

interrupteur SW4, ici un transistor PMOS. L'entrée de l'interrupteur SW4 (source du transistor) reçoit la tension V<sub>DD</sub> et l'entrée de l'interrupteur SW3 reçoit le signal S2. Les sorties des interrupteurs SW3 et SW4 (drains) sont connectées ensemble et délivrent le signal S1 qui est appliqué sur l'entrée de commande de l'interrupteur SW1.

[0026] Le fonctionnement du circuit 11, décrit par le tableau 2 ci-après, est équivalent au fonctionnement décrit par le tableau 1 ci-dessus. Pendant la première période E1 de charge du condensateur C<sub>REG</sub> le signal S1 est égal à 0 et le signal S3 égal à 1. L'interrupteur ballast SW2 est fermé, l'interrupteur SW3 ouvert (transistor bloqué) et l'interrupteur SW4 fermé. Le signal S1 est à 1 (tension V<sub>DD</sub>) et l'interrupteur de régulation SW1 est maintenu ouvert. Pendant la deuxième période de charge E2, le signal S2 reste à 0, le signal S3 passe à 0, l'interrupteur SW3 se ferme et l'interrupteur SW4 s'ouvre. Le signal S1 recopie le signal S2 par l'intermédiaire de l'interrupteur SW3 et l'interrupteur de régulation SW1 se ferme.

Tableau 2

S2 SW2 SW1  $V_{REG}$ **S3** SW3 SW4 S<sub>1</sub> (E1) V<sub>REG</sub> < V<sub>REF2</sub> 0 fermé 1 ouvert fermé 1 ouvert  $(E2) V_{REF2} < V_{REG} < V_{REF1}$ 0 0 0 fermé fermé ouvert fermé  $(E3) V_{REG} > V_{REF1}$ 1 0 ouvert fermé ouvert ouvert

20

10

15

[0027] On voit dans le tableau 2 que l'interrupteur SW3 est un interrupteur inhibiteur permettant, pendant la première période de charge E1, de ne pas transmettre à l'interrupteur SW1 le signal de régulation S2, de sorte que l'interrupteur SW1 ne se ferme pas. L'interrupteur SW4 est un élément auxiliaire permettant d'éviter que la grille du transistor interrupteur SW1 soit portée à un potentiel flottant (haute impédance) quand l'interrupteur SW3 est ouvert. Bien entendu, diverses variantes sont envisageables selon le mode de fonctionnement des interrupteurs utilisés, qui peuvent être du type normalement ouvert, du type normalement fermé, ou du type n'acceptant pas un signal indéfini sur l'entrée de commande.

[0028] Ce mode de réalisation du circuit 11 peut également faire l'objet de diverses variantes en ce qui concerne la commande de l'interrupteur inhibiteur SW3. Par exemple, le signal S3 peut être délivré par une minuterie que l'on active au démarrage du régulateur 10, ou être délivré par le microprocesseur 20 après exécution d'un programme de temporisation. Dans ce cas, l'interrupteur de régulation SW1 reste ouvert jusqu'à ce que le signal S3 soit mis à 0 par la minuterie ou le microprocesseur. En pratique, la durée de la temporisation doit être calculée en fonction de la capacité du condensateur  $C_{\mathsf{REG}}$ .

[0029] Ce mode de réalisation du circuit 11 présente toutefois l'avantage de garantir une mise en service automatique de l'interrupteur de régulation SW1 lorsque le seuil V<sub>REF2</sub> est atteint, quelle que soit la capacité C<sub>REG</sub> et sans qu'il soit nécessaire de générer un signal de temporisation au moyen d'une minuterie ou d'un programme. Comme autre avantage, le signal S3 délivré par le comparateur CP2 peut être utilisé par le microprocesseur pour surveiller l'état du régulateur 10. Par exemple, le passage à 1 du signal S1 en cours de fonctionnement est représentatif d'une surcharge du régulateur. Enfin, dans certaines applications, le signal S3 peut être combiné de façon logique à d'autres signaux émis par le microprocesseur avant d'être appliqué à l'interrupteur inhibiteur SW3, pour que le microprocesseur puisse forcer à l'état ouvert ou fermé l'interrupteur régulateur SW1 si cela s'avère nécessaire.

**[0030]** Enfin, bien que l'on ait indiqué ci-dessus que la résistance R2 est la résistance intrinsèque de l'interrupteur ballast SW2, il va de soi que le terme "interrupteur ballast" peut désigner, dans la description et les revendications, un interrupteur de résistance nulle connecté en série avec une résistance R2, ou un interrupteur de résistance intrinsèque R2<sub>a</sub> connecté en série avec une résistance complémentaire R2<sub>b</sub>.

## Revendications

45

50

55

- 1. Régulateur de tension (10) comprenant un condensateur (C<sub>REG</sub>) délivrant sur son anode une tension régulée (V<sub>REG</sub>), un interrupteur de régulation (SW1) pour connecter le condensateur (C<sub>REG</sub>) à une source (21) de tension (V<sub>DD</sub>), et des moyens de régulation agencés pour fermer l'interrupteur (SW1) quand la tension régulée (V<sub>REG</sub>) est inférieure à une première tension de référence (V<sub>REF1</sub>), caractérisé en ce qu'il comprend :

- au moins un interrupteur ballast (SW2) en parallèle avec l'interrupteur de régulation (SW1), et

- des moyens (11, CP1, CP2, SW3, SW4) pour ouvrir l'interrupteur de régulation (SW1) et fermer l'interrupteur ballast (SW2) au moins pendant une phase de démarrage du régulateur, jusqu'à ce que le condensateur (C<sub>REG</sub>) soit au moins partiellement chargé.

#### EP 1 083 471 A1

- 2. Régulateur selon la revendication 1, caractérisé en ce qu'il comprend des moyens (11, CP1, CP2, SW3, SW4) pour ouvrir l'interrupteur de régulation (SW1) et fermer l'interrupteur ballast (SW2) quand la tension régulée (V<sub>REG</sub>) est inférieure à une deuxième tension de référence (V<sub>REF2</sub>) inférieure à la première tension de référence (V<sub>REF1</sub>).

- 5 **3.** Régulateur selon la revendication 2, dans lequel la deuxième tension de référence (V<sub>REF2</sub>) est une fraction de la première tension de référence (V<sub>REF1</sub>).

- 4. Régulateur selon l'une des revendications 1 à 3, dans lequel un signal (S2) commun de commande de l'interrupteur de régulation (SW1) et de l'interrupteur ballast (SW2) est appliqué à l'interrupteur de régulation (SW1) par l'intermédiaire d'un interrupteur inhibiteur (SW3).

- 5. Régulateur selon la revendication 4, dans lequel l'interrupteur inhibiteur (SW3) est piloté par un signal (S3) délivré par un comparateur (CP2) recevant en entrée la tension régulée (V<sub>REG</sub>) et une deuxième tension de référence (V<sub>REF2</sub>) inférieure à la première tension de référence (V<sub>REF1</sub>).

- 6. Régulateur selon l'une des revendications 1 à 5, comprenant un circuit suiveur (CP1) et un comparateur (CP2), dans lequel le circuit suiveur (CP1) reçoit en entrée la tension régulée (V<sub>REG</sub>) et la première tension de référence (V<sub>REF1</sub>) et délivre un signal de régulation (S2), le comparateur (CP2) reçoit en entrée la tension régulée (V<sub>REG</sub>) et une deuxième tension de référence (V<sub>REF2</sub>) inférieure à la première tension de référence (V<sub>REF1</sub>), le signal de régulation (S2) est appliqué sur l'entrée de commande de l'interrupteur ballast (SW2) et est appliqué sur l'entrée de commande de l'interrupteur inhibiteur (SW3), et la sortie du comparateur (CP2) est appliquée sur l'entrée de commande de l'interrupteur inhibiteur (SW3).

- 7. Régulateur selon l'une des revendications 1 à 6, dans lequel l'interrupteur ballast (SW2) est un transistor MOS comprenant une résistance intrinsèque (R2) non négligeable.

- 8. Régulateur selon l'une des revendications 1 à 7, dans lequel la source (21) de tension (V<sub>DD</sub>) est une pile électrique.

- 9. Circuit intégré (20), comprenant un régulateur selon l'une des revendications 1 à 8.

10

15

20

25

30

35

40

45

50

55

10. Microprocesseur (20), comprenant un régulateur selon l'une des revendications 1 à 8.

5

# FIG.3

# RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande EP 00 11 9687

| Catégorie                                                 | Citation du document avec in                                                                                                                                                                                   |                                                                                          | Revendication | CLASSEMENT DE LA                             |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------|----------------------------------------------|

| Jacogone                                                  | des parties pertine                                                                                                                                                                                            | ntes                                                                                     | concernée     | DEMANDE (Int.CI.7)                           |

| Α                                                         | US 5 861 737 A (PIEP<br>19 janvier 1999 (199<br>* le document en ent                                                                                                                                           | 9-01-19)                                                                                 | 1-10          | G05F1/565                                    |

| A                                                         | KMETZ G L: "SOFT-ST<br>AT OV"<br>EDN ELECTRICAL DESIG<br>PUBLISHING CO. NEWTO<br>vol. 41, no. 12, 6 j<br>page 104,106 XP00062<br>ISSN: 0012-7515<br>* abrégé *                                                 | N NEWS,US,CAHNERS<br>N, MASSACHUSETTS,<br>uin 1996 (1996-06-06)                          | 1-10          |                                              |

| A                                                         | EP 0 309 922 A (SIEM<br>5 avril 1989 (1989-0<br>* le document en ent<br>-                                                                                                                                      | 4-05)                                                                                    | 1-10          |                                              |

|                                                           |                                                                                                                                                                                                                |                                                                                          |               | DOMAINES TECHNIQUES<br>RECHERCHES (Int.Cl.7) |

|                                                           |                                                                                                                                                                                                                |                                                                                          |               | G05F                                         |

|                                                           |                                                                                                                                                                                                                |                                                                                          |               |                                              |

| Le pré                                                    | sent rapport a été établi pour toute                                                                                                                                                                           | s les revendications                                                                     | _             |                                              |

| L                                                         | ieu de la recherche                                                                                                                                                                                            | Date d'achèvement de la recherche                                                        |               | Examinateur                                  |

|                                                           | LA HAYE                                                                                                                                                                                                        | 29 novembre 200                                                                          | 00 Sch        | obert, D                                     |

| X : parti<br>Y : parti<br>autre<br>A : arriè<br>O : divul | TEGORIE DES DOCUMENTS CITES<br>sulièrement pertinent à lui seul<br>sulièrement pertinent en combinaison au<br>document de la même catégorie<br>re-plan technologique<br>gation non-écrite<br>ment intercalaire | E : document de l<br>date de dépôt<br>vec un D : cité dans la de<br>L : cité pour d'auti |               | s publié à la                                |

# ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

EP 00 11 9687

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Les dits members sont contenus au fichier informatique de l'Office européen des brevets à la date du Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

29-11-2000

| Document brevet cité<br>au rapport de recherche | Date de publication | Membre(s) de la famille de brevet(s)                              | Date de publication                                           |

|-------------------------------------------------|---------------------|-------------------------------------------------------------------|---------------------------------------------------------------|

| US 5861737 A                                    | 19-01-1999          | US 5698973 A US 6034516 A CA 2210616 A EP 0823681 A JP 10163839 A | 16-12-199<br>07-03-200<br>31-01-199<br>11-02-199<br>19-06-199 |

| EP 0309922 A                                    | 05-04-1989          | DE 3876923 A                                                      | 04-02-199                                                     |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

|                                                 |                     |                                                                   |                                                               |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82