# Europäisches Patentamt European Patent Office Office européen des brevets

(11) **EP 1 118 922 A1**

(12)

# **EUROPÄISCHE PATENTANMELDUNG**

(43) Veröffentlichungstag:25.07.2001 Patentblatt 2001/30

(51) Int Cl.<sup>7</sup>: **G05F 1/595**

(21) Anmeldenummer: 00127024.8

(22) Anmeldetag: 09.12.2000

(84) Benannte Vertragsstaaten:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE TR

Benannte Erstreckungsstaaten:

AL LT LV MK RO SI

(30) Priorität: 19.01.2000 DE 10002037

(71) Anmelder: ELMOS Semiconductor AG 44227 Dortmund (DE)

(72) Erfinder: Krücke, Ludger 58453 Witten (DE)

(74) Vertreter: Hilleringmann, Jochen, Dipl.-Ing. et al Patentanwälte von Kreisler-Selting-Werner, Bahnhofsvorplatz 1 (Deichmannhaus) 50667 Köln (DE)

## (54) Schaltungsanordnung zum Betreiben einer Last über zwei Transistoren

(57)Die Schaltungsanordnung zum Betreiben einer Last über zwei mit der Last in Reihe zu schaltende Transistoren ist mit einem ersten Transistor (M1) versehen. der einen mit einem ersten Steuersignal beaufschlagbaren Steuereingang und einem in Abhängigkeit von dem ersten Steuersignal steuerbaren Leitungspfad aufweist, wobei der über den Leitungspfad fließende Strom auf einen ersten Maximalwert ( $I_{llm(M1)}$ ) begrenzt ist. Ferner weist die Schaltungsanordnung einen zweiten Transistor (M2) auf, der einen mit einem zweiten Steuersignal beaufschlagbaren Steuereingang und einem in Abhängigkeit von dem zweiten Steuersignal steuerbaren Leitungspfad aufweist, wobei der über den Leitungspfad fließende Strom auf einen zweiten Maximalwert  $(I_{IIm(M2)})$  begrenzt ist. Der erste Maximalwert  $(I_{IIm(M1)})$ ist größer als der zweite Maximalwert ( $I_{lim(M2)}$ ). Die Last (R) ist in Reihe mit den Leitungspfaden des ersten und des zweiten Transistors (M1,M2) verschaltbar. Bei von einem Strom mit der Größe des zweiten Maximalwerts durchflossener Last ist das erste Steuersignal an dem Steuereingang des ersten Transistors derart einstellbar, dass über den Leitungspfad des ersten Transistors eine Spannung fällt, die größer ist als diejenige Spannung, die abfällt, wenn über dem Leitungspfad des ersten Transistors ein Strom mit der Größe des zweiten Maximalwerts fließt.

FIG. 2

#### Beschreibung

**[0001]** Die Erfindung betrifft eine Schaltungsanordnung mit zwei Transistoren, die in Reihe mit einer zu betreibenden Last zu verschalten sind.

[0002] Es gibt zahlreiche technische Anwendungen für Schaltungsanordnungen, mit denen über zwei Treibertransistoren eine mit diesen in Reihe geschaltete Last angesteuert wird. Ein typisches Beispiel für eine über eine derartige Ausgangsstufe angesteuerte Last ist das elektrische Anzündelement des Gasgenerators eines Kfz-Airbag. Bei diesem Anwendungsbeispiel wird über eine kurze Zeit eine definierte Mindestleistung zum Zünden des elektrischen Anzündelements in diesem umgesetzt. Die Energieversorgung besteht hierbei im wesentlichen aus einem Energiespeicher, der beispielsweise einen Kondensator aufweist. Zum Schutz der Treibertransistoren, aber auch zum Schutz davor, dass durch die Last ein zu großer Strom fließt, wird eine Ausgangsstufe strombegrenzt ausgelegt, was durch die Verwendung von Transistoren mit Strombegrenzung realisiert wird.

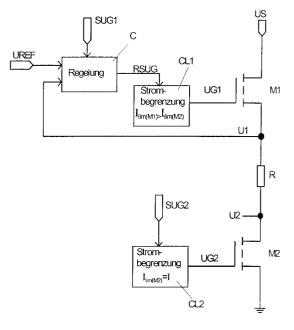

[0003] Eine bekannte Schaltungsanordnung mit Strombegrenzung ist in Fig. 1 dargestellt. Bei einer solchen strombegrenzten Ausgangsstufe besteht im allgemeinen das Problem darin, dass die elektrische Verlustleistung auf die beiden Transistoren M1 und M2 ungleichmäßig und damit schlecht verteilt ist.

[0004] Bei der bekannten Schaltungsanordnung nach Fig. 1 wird eine Last R, die resistiv, kapazitiv oder induktiv sein kann, durch die beiden Transistoren M1 und M2, bei denen es sich um Bipolar- oder Feldeffekt-Transistoren handeln kann, bestromt. Da die Last R von den beiden Transistoren M1 und M2 weit entfernt angeordnet sein kann, ist zur Vermeidung von Schäden im Betrieb und bei der Montage eine Kurzschlusssicherung bzw. Strombegrenzung für die beiden Transistoren M1 und M2 erforderlich. Andernfalls hätten Kurzschlüsse der Zuführleitungen mit den Potentialen U1 und U2 gegen eine positive oder negative Versorgung eine Beschädigung der Transistoren M1 bzw. M2 zur Folge.

[0005] Eine Begrenzung des Stromes kann aber auch für die Last R erforderlich sein. So soll beispielsweise vermieden werden, dass zu Beginn oder zum Ende eines Einschaltzustandes Überströme fließen. Ferner kann es auch angezeigt sein, derartige Überströme deshalb zu unterbinden, weil andernfalls der die Schaltungsanordnung speisende Energiespeicher sich zu schnell entlädt. Dies sollte beispielsweise bei einer Kfz-Anwendung der erfindungsgemäßen Schaltungsanordnung zum Zünden der Anzündelemente der Gasgeneratoren mehrerer Airbag verhindert werden. Damit nämlich noch nach dem Zusammenbruch des Bordnetzes dennoch sämtliche Airbag auslösen können, darf jedem Anzündelement kein größerer Strom als der Zündstrom zugeführt werden, da andernfalls die Energie im Energiespeicher nicht zum Zünden sämtlicher erforderlicher Airbag ausreichend wäre.

[0006] Die Strombegrenzung in den Transistoren M1 und M2 erfolgt, wie bereits oben kurz erwähnt, in der an sich bekannten Weise durch Shunt-Widerstände oder durch Messung des Spannungsabfalls über den Transistoren oder eines Teils dieser Transistoren. Dabei ist es physikalisch nicht möglich, dass sich über beide Transistoren derselbe Spannungsabfall und damit dieselbe Leistung einstellt. Der Grund hierfür ist darin zu sehen, dass die Transistoren aufgrund von Exemplarstreuungen unterschiedlich große Begrenzungsströme aufweisen. Dies hat zur Folge, dass die Begrenzung an einem der beiden Transistoren M1,M2 stets stärker wirken wird als an dem jeweils anderen. Über einen der beiden Transistoren M1,M2 wird sich also ein sehr großer Spannungsabfall einstellen, womit der weitaus größere Teil der Leistung von diesem Transistor aufgenommen werden muss. In der Schaltungsanordnung gemäß Fig. 1 wird angenommen, dass die Strombegrenzung über dem Transistor M2 geringfügig kleiner ist als über dem Transistor M1; mit anderen Worten gilt also, dass  $I_{lim(M1)}$  größer ist als  $I_{lim(M2)}$ .

[0007] Geht man weiter davon aus, dass die Einschaltwiderstände der Transistoren M1 und M2 bei Vollansteuerung kleiner sind als der Widerstand der Last R und dass der sich aus der Reihenschaltung ergebende Strom größer als die Strombegrenzung an einem der beiden Transistoren M1,M2 ist, wird sich beim Betrieb ein sehr großer Spannungsabfall U2 über dem Transistor M2 und damit eine sehr große Leistungsaufnahme durch den Transistor M2 ergeben. Der Transistor M1 wird voll angesteuert bleiben und durch den geringen Spannungsabfall über diesem Transistor wird nur eine geringe Leistung aufgenommen. Der Rest der Leistung wird über die Last R aufgenommen. Die große Leistungsaufnahme im Transistor M2 kann zu einer sehr starken Erwärmung und schließlich Schädigung dieses Transistors führen. Im allgemeinen ist zumindest eine starke Überdimensionierung des Leistungsaufnahmevermögens des Transistors M2 erforderlich. Dies ist wiederum von Nachteil in Bezug auf den Flächenverbrauch des Transistors, wenn man sich vor Augen führt, dass die Schaltungsanordnung insgesamt als integrierte Schaltung vorliegt.

[0008] Eine Möglichkeit, eine Ungleichverteilung der Verlustleistungen in den Transistoren M1 und M2 zu verhindern bzw. einer derartigen Ungleichverteilung entgegenzuwirken, besteht darin, die beiden Transistoren M1 und M2 miteinander zu verkoppeln, so dass man durch Erkennung der Strombegrenzung am Transistor M2 schaltungstechnisch auf den Transistor M1 einwirken kann, indem man beispielsweise dessen Strombegrenzung kurzzeitig heruntersetzt. Damit würden dann die beiden Transistoren M1 und M2 wechselweise in die Strombegrenzung laufen, was zu nicht gewollten Stromschwingungserscheinungen führt. Außerdem ist es in einer Vielzahl von Anwendungsfällen unerwünscht und teilweise aufgrund großer Entfernungen kaum möglich, die Transistoren M1 und M2 zusätzlich zu verkoppeln,

20

um die Strombegrenzung des einen Transistors in Abhängigkeit von dem Ansprechen der Strombegrenzung des anderen Transistors zu regeln.

[0009] Aus DE-A-15 13 168 ist eine Ausgangsstufe zum Betreiben einer Last bekannt, bei der zwei in Serie geschaltete Transistoren in Reihe mit einer zu betreibenden Last geschaltet sind. Einer der beiden Transistoren ist derart gesteuert, dass der über seinen Leitungspfad fließende Strom auf einen Maximalwert begrenzt ist.

**[0010]** Der Erfindung liegt die Aufgabe zugrunde, eine Schaltungsanordnung zum Betreiben einer Last über zwei in Reihe mit der Last zu schaltende Transistoren zu schaffen, mit der es auf einfache Weise möglich ist, die Verlustleistung gleichmäßig auf beide Transistoren zu verteilen.

**[0011]** Zur Lösung dieser Aufgabe wird mit der Erfindung eine Schaltungsanordnung vorgeschlagen, die versehen ist mit

- einem ersten Transistor, der einen mit einem ersten Steuersignal beaufschlagbaren Steuereingang und einem in Abhängigkeit von dem ersten Steuersignal steuerbaren Leitungspfad aufweist, wobei der über den Leitungspfad fließende Strom auf einen ersten Maximalwert begrenzt ist.

- einem zweiten Transistor, der einen mit einem zweiten Steuersignal beaufschlagbaren Steuereingang und einem in Abhängigkeit von dem zweiten Steuersignal steuerbaren Leitungspfad aufweist, wobei der über den Leitungspfad fließende Strom auf einen zweiten Maximalwert begrenzt ist,

- wobei

- der erste Maximalwert größer ist als der zweite Maximalwert.

- die Last in Reihe mit den Leitungspfaden des ersten und des zweiten Transistors verschaltbar ist und

- bei von einem Strom mit der Größe des zweiten Maximalwerts durchflossener Last das erste Steuersignal an dem Steuereingang des ersten Transistors derart einstellbar ist, dass über den Leitungspfad des ersten Transistors eine Spannung fällt, die größer ist als diejenige Spannung, die abfällt, wenn über dem Leitungspfad des ersten Transistors ein Strom mit der Größe des zweiten Maximalwerts fließt.

[0012] Bei der erfindungsgemäßen Schaltungsanordnung sind die beiden Transistoren an ihren Steuereingängen jeweils mit Strombegrenzungsschaltungen verbunden, die dafür sorgen 'dass die über die Leitungspfade der Transistoren fließenden Ströme auf erste bzw. zweite Maximalwerte begrenzt sind. Der Strombegrenzungswert des ersten Transistors ist dabei größer als der Strombegrenzungswert des zweiten Transistors. Dies ist, wie bereits oben im Zusammenhang mit der

Beschreibung der im Stand der Technik bekannten Schaltungsanordnung erwähnt, aufgrund vom Exemplarstreuungen der Transistoren an sich der Normalfall. Dieser Normalfall wird erfindungsgemäß bewusst ausgenutzt, indem nämlich der Spannungsabfall über dem ersten Transistor bei in der Strombegrenzung befindlichem zweiten Transistor erhöht wird, um somit einen Teil der andernfalls vom zweiten Transistor aufgenommenen Leistung auf den ersten Transistor zu übertragen. Denn erfindungsgemäß ist das Steuersignal an dem Steuereingang des ersten Transistor dann, wenn ein Strom mit der Größe des zweiten Maximalwerts fließt, derart einstellbar, dass über den Leitungspfad des ersten Transistors eine Spannung abfällt, die größer ist als diejenige Spannung, die abfallen würde, wenn über dem Leitungspfad des ersten Transistors ein Strom mit der Größe des zweiten Maximalwerts fließt.

[0013] Die Beeinflussung des Steuersignals am Steuereingang des ersten Transistors kann durch einfache Rückführung des Spannungsabfalls über dem ersten Transistor realisiert werden. Eine Verkopplung bzw. zusätzliche Verschaltung der Strombegrenzungsschaltungen beider Transistoren ist also bei der erfindungsgemäßen Schaltungsanordnung nicht erforderlich, so dass durch denkbar geringen Aufwand eine gleichmäßigere Verteilung der in den beiden Transistoren umzusetzenden Verlustleistung erzielt wird bzw. verhindert wird, dass einer der beiden Transistoren deutlich mehr Verlustleistung aufzunehmen hat als der andere.

[0014] In vorteilhafter Weiterbildung ist ein Vergleicher zum Vergleich des Spannungsabfalls über dem Leitungspfad des ersten Transistors mit einer Referenzspannung vorgesehen. Dieser Vergleicher gibt dann, wenn der Spannungsabfall über dem Leitungspfad des ersten Transistors größer ist als die Referenzspannung, ein Ausgangssignal zur Beeinflussung des ersten Steuersignals für den Steuereingang des ersten Transistors aus. Eine noch einfachere Rückführung des Spannungsabfalls über dem ersten Transistor auf dessen Steuereingang wird dadurch realisiert, dass die Strombegrenzungsschaltung des ersten Transistors in Abhängigkeit von einer eine Referenzspannung liefernden ersten Spannungsquelle gesteuert ist und dass der erste Transistor als Spannungsfolger geschaltet ist. Damit kann der Spannungsabfall über dem ersten Transistor zumindest für eine definierte Zeit oder einen definierten Betriebszustand nicht größer werden als die Referenzspannung, es gilt also, dass der Spannungsabfall über dem Transistor im wesentlichen gleich der Referenzspannung ist.

**[0015]** Nachfolgend wird die Erfindung anhand der Zeichnung näher erläutert. Im einzelnen zeigen:

Fig. 1 eine Schaltungsanordnung gemäß dem Stand der Technik und

Fign. 2 bis 4 verschiedene Ausführungsbeispiele einer erfindungsgemäßen Schal-

55

tungsanordnung zum Betreiben einer Last über zwei mit der Last in Reihe zu schaltende Transistoren.

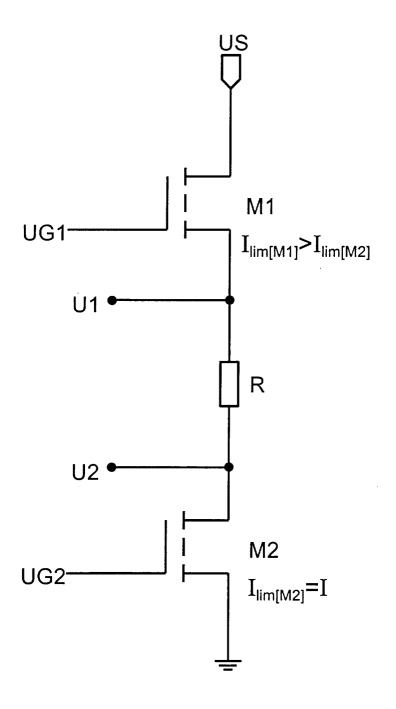

[0016] Die Schaltungsanordnung gemäß Fig. 2 zeigt eine erste erfindungsgemäße Möglichkeit einer verbesserten Leistungsverteilung auf die beiden Transistoren M1 und M2 bei Stromfluss durch die Last R. Den Transistoren bzw. Stellgliedern werden bewusst unterschiedliche Strombegrenzungen eingeprägt. Dabei dient die Speisespannung SUG2 der Strombegrenzungsschaltung CL2 für den Transistor M2 zur Erzeugung der Steuerspannung UG2 für den Transistor M2. In der Strombegrenzungsschaltung CL2 für den Transistor M2 wird diese Spannung so geregelt, dass über dem Transistor M2 ein maximaler Strom I<sub>lim(M2)</sub> eingestellt wird. Ähnliches geschieht normalerweise auch für den Transistor M1. Erfindungsgemäß jedoch wird bewusst eine Strombegrenzung für den Transistor M1 eingestellt, welche größer ist als die Strombegrenzung für den Transistor M2. Es gilt also:

$I_{lim(M1)}$  ist größer als  $I_{lim(M2)}$ .

[0017] Das bedeutet, dass im Fall einer Überlast als erstes immer der Spannungsabfall U2 über M2 erhöht wird, da I<sub>lim(M2)</sub> die Begrenzung bestimmt. Der Transistor M1 würde normalerweise relativ wenig belastet werden. Durch eine Rückführung wird der Spannungsabfall (Differenz zwischen US und U1) über dem Transistor M1 mit einer Referenzspannung UREF in der Regelung C verglichen. Die Steuerspannung UG1 für den Transistor M1 wird durch die Strombegrenzungsschaltung CL1 des Transistors M1 so eingestellt, dass zusätzlich zu der Strombegrenzung  $I_{lim(M1)}$  an U1 Spannungsgleichheit mit UREF besteht. Es gilt also zumindest für eine definierte Zeit oder einen definierten Betriebszustand, dass U1 gleich UREF ist. Damit wird der Spannungsabfall über dem Transistor M1 künstlich erhöht und ein Teil der andernfalls von dem Transistor M2 aufzunehmenden Leistung wird auf den Transistor M1 "gezogen".

[0018] Die Referenzspannung UREF ist frei wählbar und damit ist auch die Leistungsverteilung auf die beiden Transistoren M1 und M2 frei wählbar. Die Referenzspannung UREF kann über einen Spannungsteiler aus der Versorgungsspannung US erzeugt werden oder mit einer festen Spannung beaufschlagt werden, so dass bei Überschreiten dieser Spannung an U1 der Spannungsabfall und damit die Leistungsaufnahme minimiert wird oder dann erst voll wirksam wird. Auch Kombinationen aus festen und proportionalen Spannungsanteilen an UREF oder eine Änderung über der Zeit sind möglich.

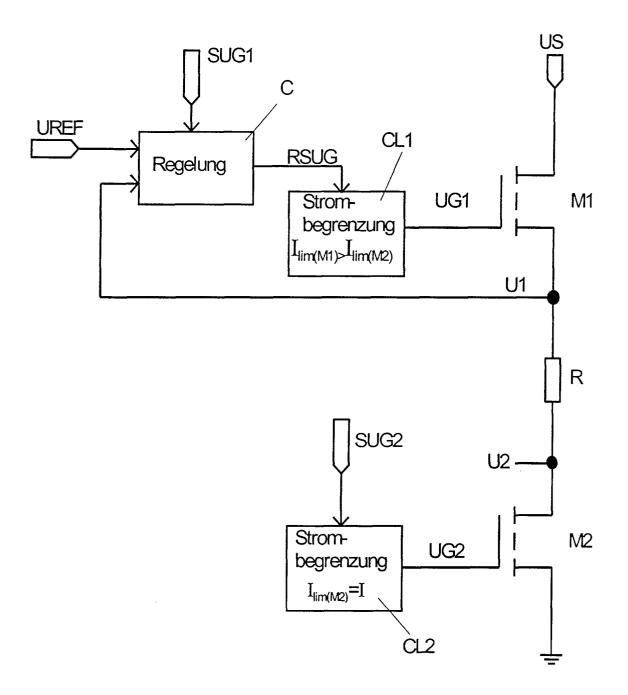

[0019] Ein weiteres Ausführungsbeispiel der erfindungsgemäßen Schaltungsanordnung zeigt Fig. 3. Diese Schaltungsanordnung ist gegenüber der Schaltungsanordnung gemäß Fig. 2 insofern vereinfacht, als auf die Rückführung der Spannung an U1 verzichtet wird und die zum Steuern der Strombegrenzungsschaltung

CL1 für den Transistor M1 benötigte Steuerspannung RSUG1 der Schaltungsanordnung gemäß Fig. 2 direkt aus der Referenzspannung UREF erzeugt wird. Dies gelingt, indem der Transistor M1 als Spannungsfolger geschaltet ist. Auch in dem Beispiel gemäß Fig. 3 gilt zumindest für eine definierte Zeit oder einen definierten Betriebszustand, dass die Spannung an U1 im wesentlichen gleich der Referenzspannung UREF ist.

[0020] Mit der erfindungsgemäßen Schaltungsanordnung lässt sich ein weiter Bereich von Leistungsverteilungen über Ort, Arbeitsbedingungen (Spannung) und Zeit einstellen, ohne dass es einer Verkopplung der Strombegrenzungsschaltungen der beiden Transistoren M1 und M2 bedarf. Das bedeutet, dass die Transistoren M1 und M2 örtlich weit auseinanderliegend angeordnet sein können. Damit können auf einfache Weise die Transistoren M1 und M2 in ihren Belastbarkeiten optimiert werden.

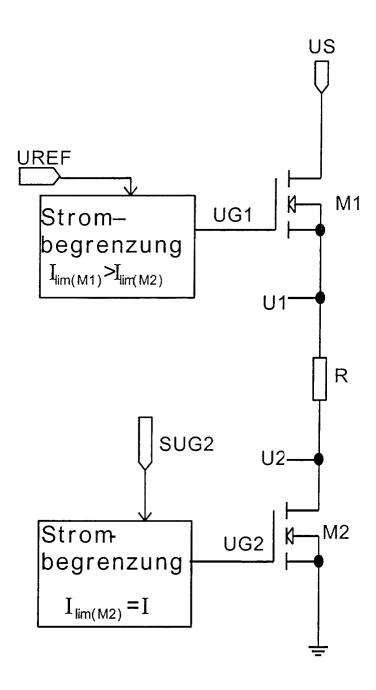

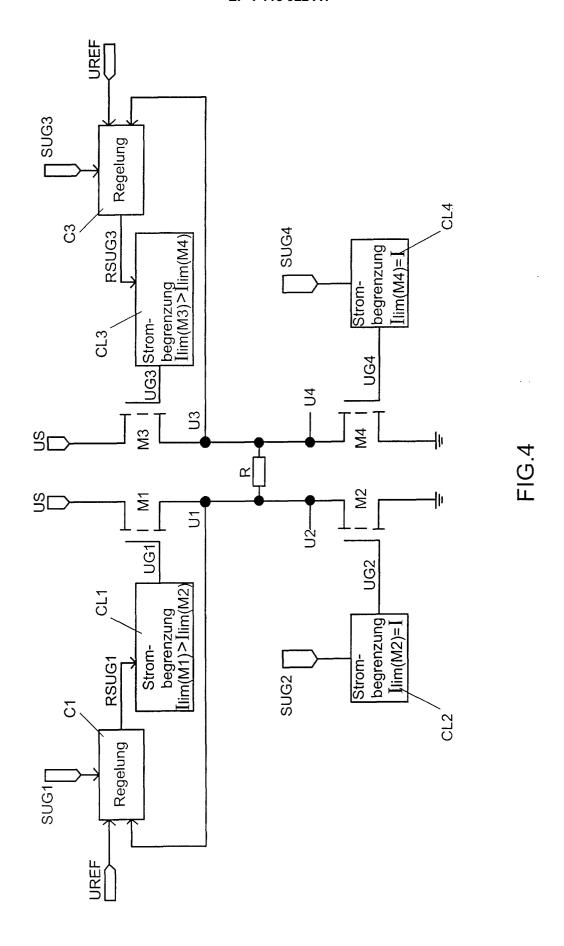

[0021] In den hier beschriebenen Ausführungsbeispielen ist stets angenommen worden, dass der Spannungsabfall über dem Transistor M1 künstlich erhöht wird. Es ist aber auch ebenso denkbar, den Spannungsabfall über dem Transistor M2 künstlich zu erhöhen; mit anderen Worten können die in den Fign. 2 und 3 gezeigten Schaltungsanordnungen auch umgekehrt realisiert werden. In diesen Fällen würde die Referenzspannung UREF auf U2 wirken und I<sub>lim(M2)</sub> größer als I<sub>lim(M1)</sub> sein. [0022] Die in den Fign. 2 und 3 dargestellten Schaltungsanordnungen lassen sich auch zu einer (Voll-) Brückenschaltung ergänzen. Fig. 4 zeigt eine solche Vollbrückenschaltung für die Schaltungsvariante gemäß Fig. 2. Je nach Richtung des Stroms durch die Last R fließt dieser entweder über das Transistorenpaar M1,M4 oder M2,M3.

### Patentansprüche

40

50

- Schaltungsanordnung zum Betreiben einer Last über zwei mit der Last in Reihe zu schaltende Transistoren, mit

- einem ersten Transistor (M1), der einen mit einem ersten Steuersignal beaufschlagbaren Steuereingang und einem in Abhängigkeit von dem ersten Steuersignal steuerbaren Leitungspfad aufweist, wobei der über den Leitungspfad fließende Strom auf einen ersten Maximalwert (I<sub>lim(M1)</sub>) begrenzt ist.

- einem zweiten Transistor (M2), der einen mit einem zweiten Steuersignal beaufschlagbaren Steuereingang und einem in Abhängigkeit von dem zweiten Steuersignal steuerbaren Leitungspfad aufweist, wobei der über den Leitungspfad fließende Strom auf einen zweiten Maximalwert (I<sub>lim(M2)</sub>) begrenzt ist,

- wobei

- der erste Maximalwert (I<sub>lim(M1)</sub>) größer ist als der zweite Maximalwert (I<sub>lim(M2)</sub>),

- die Last (R) in Reihe mit den Leitungspfaden des ersten und des zweiten Transistors (M<sub>1</sub>,M<sub>2</sub>) verschaltbar ist und

- bei von einem Strom mit der Größe des zweiten Maximalwerts durchflossener Last (R) das erste Steuersignal an dem Steuereingang des ersten Transistors (M1) derart einstellbar ist, dass über den Leitungspfad des ersten Transistors (M1) eine Spannung abfällt, die größer ist als diejenige Spannung, die abfällt, wenn über dem Leitungspfad des ersten Transistors (M1) ein Strom mit der Größe des zweiten Maximalwerts fließt.

- 2. Schaltungsanordnung nach Anspruch 1, dadurch gekennzeichnet, dass ein Vergleicher C1 zum Vergleich des Spannungsabfalls über dem Leitungspfad des ersten Transistors (M1) mit einer Referenzspannung vorgesehen ist und dass der Vergleicher C1 dann, wenn der Spannungsabfall größer ist als die Referenzspannung, ein Ausgangssignal zur Beeinflussung des ersten Steuersignals für den Steuereingang des ersten Transistors (M1) ausgibt.

- 3. Schaltungsanordnung nach Anspruch 1, dadurch gekennzeichnet, dass das erste Steuersignal am Steuereingang des ersten Transistors (M1) in Abhängigkeit von einer eine Referenzspannung liefernden externen Spannungsquelle einstellbar ist und dass der erste Transistor (M1) als Spannungsfolger geschaltet ist.

15

20

25

30

35

40

45

50

55

FIG. 1 Stand der Technik

FIG. 2

FIG. 3

# **EUROPÄISCHER RECHERCHENBERICHT**

Nummer der Anmeldung EP 00 12 7024

|                                                         | EINSCHLÄGIG                                                                                                                                                                                                              | E DOKUMENTE                                                                                           |                                                                               |                                            |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------|

| Kategorie                                               | Kennzeichnung des Doku<br>der maßgeblich                                                                                                                                                                                 | ments mit Angabe, soweit erforderlich,<br>nen Teile                                                   | Betrifft<br>Anspruch                                                          | KLASSIFIKATION DER<br>ANMELDUNG (Int.Cl.7) |

| X<br>A                                                  | GB 1 105 259 A (GOI<br>6. März 1968 (1968-                                                                                                                                                                               |                                                                                                       | 1                                                                             | G05F1/595                                  |

| A                                                       | Abbildungen 1-3 *                                                                                                                                                                                                        | Serile 2, Zerre 36;                                                                                   | 2,3                                                                           |                                            |

| A                                                       | 25. September 1963                                                                                                                                                                                                       | INGHOUSE BRAKE & SIGNAL)<br>(1963-09-25)<br>5 - Seite 3, Zeile 42;                                    | 1-3                                                                           |                                            |

| Α                                                       | AG) 15. März 1965 (                                                                                                                                                                                                      | DARD TELEPHON & RADIO<br>1965-03-15)<br>3 - Seite 3, Zeile 72;                                        | 1-3                                                                           |                                            |

| Α                                                       | KK), 24. Juli 1984                                                                                                                                                                                                       | P-317),<br>1984-11-28)<br>MATSUSHITA DENKI SANGYO<br>(1984-07-24)                                     | 1-3                                                                           |                                            |

|                                                         | * Zusammenfassung *                                                                                                                                                                                                      |                                                                                                       |                                                                               | RECHERCHIERTE<br>SACHGEBIETE (Int.Cl.7)    |

|                                                         |                                                                                                                                                                                                                          |                                                                                                       |                                                                               | G05F                                       |

|                                                         |                                                                                                                                                                                                                          |                                                                                                       |                                                                               |                                            |

| Der vo                                                  |                                                                                                                                                                                                                          | rde für alle Patentansprüche erstellt                                                                 |                                                                               |                                            |

|                                                         | Recherchenort                                                                                                                                                                                                            | Abschlußdatum der Recherche                                                                           | 1                                                                             | Prûfer                                     |

| **************************************                  | MÜNCHEN                                                                                                                                                                                                                  | 17. April 2001                                                                                        | Jone                                                                          | da, S                                      |

| X : von i<br>Y : von i<br>ande<br>A : techi<br>O : nich | ATEGORIE DER GENANNTEN DOK<br>besonderer Bedeutung allein betrach<br>besonderer Bedeutung in Verbindung<br>ren Veröffentlichung derselben Kate-<br>nologischer Hintergrund<br>ischriftliche Offenbarung<br>chenliteratur | E : älteres Patentdok<br>nach dem Anmed<br>mit einer D : in der Anmedun<br>gorie L : aus anderen Grür | ument, das jedoc<br>dedatum veröffen<br>g angeführtes Dol<br>nden angeführtes | tlicht worden ist<br>kument<br>Dokument    |

EPO FORM 1503 03.82 (P04C03)

## ANHANG ZUM EUROPÄISCHEN RECHERCHENBERICHT ÜBER DIE EUROPÄISCHE PATENTANMELDUNG NR.

EP 00 12 7024

In diesem Anhang sind die Mitglieder der Patentfamilien der im obengenannten europäischen Recherchenbericht angeführten Patentdokumente angegeben.

Die Angaben über die Familienmitglieder entsprechen dem Stand der Datei des Europäischen Patentamts am Diese Angaben dienen nur zur Unterrichtung und erfolgen ohne Gewähr.

17-04-2001

| Im Recherchenbericht<br>angeführtes Patentdokument |   | Datum der<br>Veröffentlichung | Mitglied(er) der<br>Patentfamilie                                                              | Datum der<br>Veröffentlichung                                              |

|----------------------------------------------------|---|-------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| GB 1105259                                         | Α | 06-03-1968                    | DE 1513168 A                                                                                   | 09-10-196                                                                  |

| GB 937506                                          | Α | 25-09-1963                    | KEINE                                                                                          |                                                                            |

| CH 389039                                          | A | 15-03-1965                    | KEINE                                                                                          |                                                                            |

| JP 59128617                                        | A | 24-07-1984                    | JP 1759831 C<br>JP 4043285 B<br>DE 3401055 A<br>GB 2135483 A,B<br>US 4535276 A<br>US 4608524 A | 20-05-199<br>16-07-199<br>16-08-198<br>30-08-198<br>13-08-198<br>26-08-198 |

EPO FORM P0461

Für nähere Einzelheiten zu diesem Anhang : siehe Amtsblatt des Europäischen Patentamts, Nr.12/82