(19)

Europäisches Patentamt

European Patent Office

## Office européen des brevets

(11)

EP 1 160 642 A1

(12)

## EUROPÄISCHE PATENTANMELDUNG

(43) Veröffentlichungstag:

**05.12.2001 Patentblatt 2001/49**

(51) Int Cl.<sup>7</sup>: **G05F 3/26**

(21) Anmeldenummer: **01109666.6**

(22) Anmeldetag: 19.04.2001

(84) Benannte Vertragsstaaten:

**AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU

MC NL PT SE TR**

Benannte Erstreckungsstaaten:

**AL LT LV MK RO SI**

(30) Priorität: **31.05.2000 DE 10026793**

(72) Erfinder: **Boldt, Jürgen, Dr.-Ing.**

**01277 Dresden (DE)**

(74) Vertreter: **Patentanwälte**

**Lippert, Stachow, Schmidt & Partner**

**Krenkelstrasse 3**

**01309 Dresden (DE)**

(30) Priorität: 31.05.2000 DE 10026793

(71) Anmelder: **Zentrum Mikroelektronik Dresden GmbH**

**D-01109 Dresden (DE)**

## (54) Strombegrenzungsschaltung

(57) Die Erfindung betrifft eine Schaltungsanordnung zur Strombegrenzung veränderlicher Lastströme in Schaltungen mit einer Stromeinspeisung für eine Reihenschaltung bestehend aus einem Laststrom-Steuer-FET und einem Verbraucher, wobei die Reihenschaltung zwischen Stromeinspeisung und Masse geschaltet wird. Die Aufgabe der Erfindung besteht darin, eine Laststrombegrenzung so auszuführen, daß diese dem Verbraucher den möglichst vollständigen Betriebsspannungsbereich zur Verfügung stellt. Dies wird dadurch gelöst, daß die Stromspeisung des Laststromes über einen Strompfad, dem Laststrompfad, eines Stromspiegels erfolgt, wobei in einem anderen Strompfad des

Stromspiegels, dem Stromspiegel-Steuerpfad, durch die sinnvolle Einkopplung des vom Verbraucher verursachten Laststrompotentiales über einem Strombegrenzungswiderstand ein repräsentativer gespiegelter Laststrom geprägt wird und dessen Potentialwirkung über einen Differenzverstärker mit einer Referenzspannung verglichen und nachfolgend mit dem verstärkten Differenzsignal das gemeinsame Gate der Stromspiegel-FETs angesteuert wird. Hierbei kann für die Stromspiegel-Transistoren ein solcher Arbeitspunkt realisiert werden, der auch bei Vorliegen des maximalen Laststromes eine niedrige Source-Drainspannung und damit ein maximaler Betriebsspannungsbereich ermöglicht.

## Beschreibung

**[0001]** Die Erfindung betrifft eine Schaltungsanordnung zur Strombegrenzung veränderlicher Lastströme in Schaltungen mit einer Stromeinspeisung für eine Reihenschaltung, bestehend aus einem Laststrom-Steuer-FET und einem Verbraucher, wobei die Reihenschaltung zwischen Stromeinspeisung und Masse geschaltet wird, mit einem Differenzverstärker, der mit einem ersten und einem zweiten Eingang sowie einem Ausgang versehen ist, wobei an dem zweiten Eingang eine Referenzspannungsquelle angeschlossen ist und der Ausgang mit dem Gate des Laststrom-Steuer-FET verbunden ist und einer Betriebsspannungsquelle.

**[0002]** Treten in Schaltungen Verbraucher mit hohen Lastströmen auf, variieren diese insbesondere in ihrer Größe sehr stark, ergeben sich wegen des nur endlich kleinen Innenwiderstandes der Betriebsspannungsquelle Schwankungen der Betriebsspannung, die sich auf alle angeschlossenen Schaltungsteile störend auswirken. Daher kommen zur Betriebsspannungsstabilisierung verschiedene technische Lösungen, insbesondere Strombegrenzungsschaltungen für die Begrenzung des Laststromes, zum Einsatz. Diese Strombegrenzungsschaltungen werden so dimensioniert, daß sie im Laststrompfad nur solch einen maximalen Laststrom für den Verbraucher zur Verfügung stellen, bei dem einerseits die Funktion des Verbrauchers nicht beeinträchtigt wird, andererseits die bei dieser Belastung der Betriebsspannungsquelle resultierende Betriebsspannungsänderung sich für alle Schaltungsteile nicht störend auswirkt.

**[0003]** Es ist nunmehr bekannt, daß in derartigen Strombegrenzungsschaltungen der Laststrompfad als eine Reihenschaltung von einem Stromquellenwiderstand, einem Laststrom-Steuer-FET und des Verbrauchers ausgeführt wird. Zusätzlich wird ein Differenzverstärker so geschaltet, daß ein Eingang des Differenzverstärkers eine Referenzspannung, der andere Eingang das Spannungspotential, welches sich über dem Stromquellenwiderstand eingestellt hat, auswertet und am Ausgang das verstärkte Differenzsignal über das Gate des Laststrom-Steuer-FET den Laststrom regelt. Der Stromquellenwiderstand ist so dimensioniert, daß bei anliegendem maximalen Laststrom im Laststrompfad der Laststrom-Steuer-FET mit der Laststrombegrenzung einsetzt.

**[0004]** Als nachteilig erweisen sich solche Strombegrenzungsschaltungen dahingehend, daß zur Stromeinspeisung in den Verbraucher, z.B. durch einen Stromquellenwiderstand, ein Spannungshub zwischen Betriebsspannungsquelle und Verbraucher vorgesehen werden muß, so daß für den Verbraucher nur ein erheblich verringrigerter Nutzberreich der Betriebsspannung zur Verfügung gestellt werden kann.

**[0005]** Der Erfindung liegt nunmehr die Aufgabe zu grunde, eine Laststrombegrenzung so auszuführen, daß diese dem Verbraucher den möglichst vollständi-

gen Betriebsspannungsbereich zu Verfügung stellt.

**[0006]** Die der Erfindung zugrunde liegenden Aufgabe wird durch die Schaltungsanordnung derartig gelöst, daß die Stromeinspeisung über einen neu eingeführten Stromspiegel erfolgt, dessen einer Strompfad, der Laststrompfad, der über den Laststrom-Steuer-FET den Laststrom des Verbrauchers trägt, dessen anderer Strompfad als Stromspiegel-Steuerpfad ausgeführt wird und der über den Stromspiegel-Steuer-FET einen gespiegelter Laststrom trägt. Gemäß dem üblichen konstruktivem Aufbau von Stromspiegeln sind die Transistoren des Stromspiegels, Laststrom-Steuer-FET und Stromspiegel-Steuer-FET, z.B. auf dem gleichen Substrat eines Schaltkreises angeordnet, haben einen gemeinsamen Gateanschluß und sind in ihrer Geometrie so dimensioniert, daß bei Ansteuerung beider Transistoren im gleichen Arbeitspunkt sich das Verhältnis Laststrom : gespiegelter Laststrom wie n:1 verhält.

**[0007]** Erfindungsgemäß wird das über dem Verbraucher sich einstellende Spannungspotential nicht unmittelbar vom Differenzverstärker ausgewertet, sondern dieses wird mittels zusätzlich ausgeführtem Spannungsfolger-Operationsverstärker abgetastet und ausgangsseitig über das Gate eines Stromspiegel-Koppel-FET so eingekoppelt, daß die Laststromgröße des Laststrompfades im Stromspiegel-Steuerpfad über einen Strombegrenzungswiderstand potentialmäßig repräsentiert wird. Hierbei wird dieses repräsentative Spannungspotential an einem Eingang des Differenzverstärkers ausgewertet und es wird gemeinsam mit der am anderen Eingang anliegenden Referenzspannung am Ausgang des Differenzverstärkers ein verstärktes Differenzsignal gebildet und zur Ansteuerung des gemeinsamen Gates der Stromspiegel-FET verwendet. Diese Ansteuerung der Stromspiegel-FET erfolgt in einem solchen Arbeitspunkt, der bei Erreichen des vorgesehenen maximalen Laststromes die Source-Drainspannung der Stromspiegel-FET noch als Restspannung hinreichend klein realisiert damit diese für die Verbraucherfunktion vernachlässigbar ist.

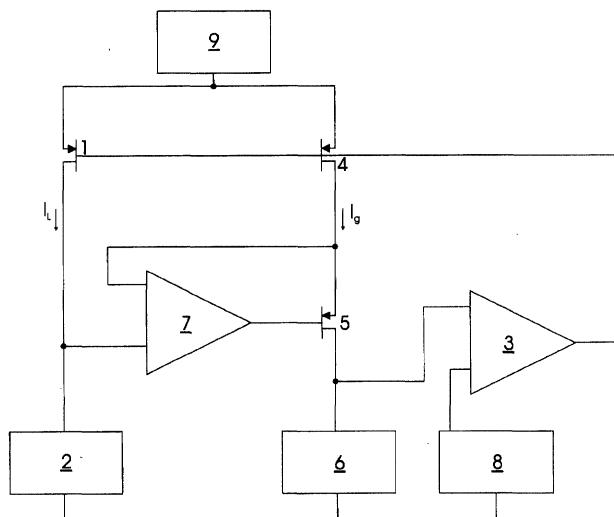

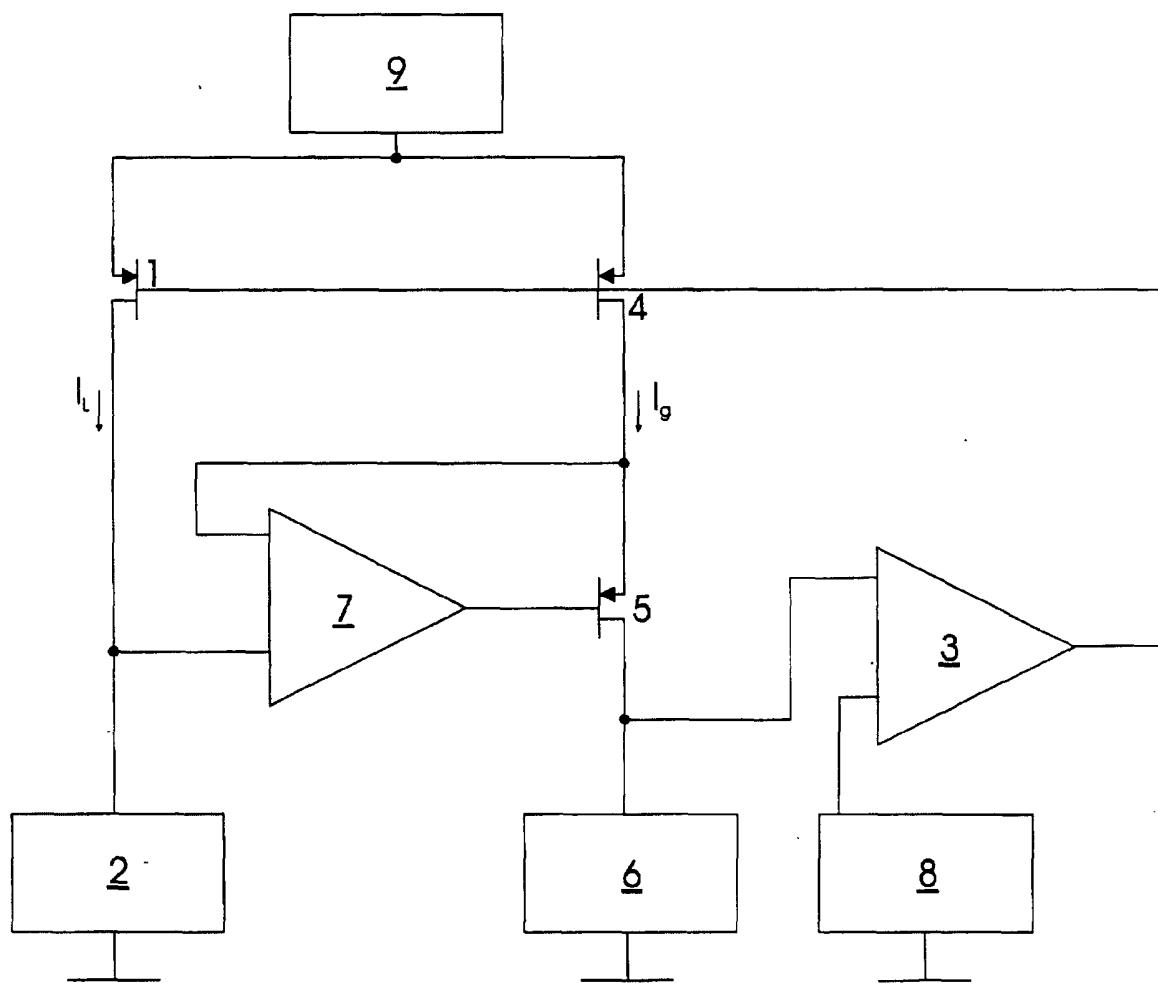

**[0008]** Die Erfindung soll nachfolgend anhand eines Ausführungsbeispiels näher erläutert werden. Die zugehörige Zeichnung zeigt ein Blockschaltbild der erfindungsgemäßen Schaltungsanordnung

**[0009]** Wie in der Zeichnung ersichtlich, bilden Laststrom-Steuer-FET und Stromspiegel-Steuer-FET einen Stromspiegel und sind an die Betriebsspannung angeschlossen. Durch die Reihenschaltung des Laststrom-Steuer-FET mit dem Verbraucher fließt in diesem Strompfad des Stromspiegels ein Laststrom. Das über dem Verbraucher sich einstellende Spannungspotential wird über einen angeschlossenen Eingang des Operationsverstärkers abgetastet. Da der Operationsverstärker ausgangsseitig das Gate des Stromspiegel-Koppel-FET ansteuert und durch die Verbindung des anderen Eingangs des Operationsverstärkers mit dem Source-Anschluß des Stromspiegel-Koppel-FET als Spannungsfolger geschaltet ist, folgt auch das Potential am

Drain-Anschluß des Stromspiegel-Steuer-FET dem durch den Laststrom am Verbraucher erzeugten Spannungspotential. Dadurch ist gewährleistet, daß das Stromspiegelverhältnis exakt 1:n beträgt. Der um den Faktor n gespiegelte Laststrom erzeugt über dem Strombegrenzungswiderstand einen Spannungsabfall. Dieses Potential liegt am Eingang des Differenzverstärkers an. Dort wird es mit der Referenzspannung der an dem anderen Eingang des Differenzverstärkers geschalteten Referenzspannungsquelle verglichen. Übersteigt dieses Potential die Referenzspannung der Referenzspannungsquelle so steuert das am Ausgang des Differenzverstärkers verstärkte Differenzsignal durch die Ansteuerung der gemeinsamen Gate-Anschlüsse von Stromspiegel-Steuer-FET und Laststrom-Steuer-FET durch Potentialanstieg deren Source-Drain Strecke zu und die Strombegrenzung setzt ein. Der Einsatzpunkt dieser Strombegrenzung kann durch Abgleich des Strombegrenzungswiderstandes oder der Referenzspannungsquelle erfolgen.

#### Bezugszeichenliste

#### [0010]

|       |                             |    |

|-------|-----------------------------|----|

| 1     | Laststrom-Steuer-FET        | 25 |

| 2     | Verbraucher                 |    |

| 3     | Differenzverstärker         |    |

| 4     | Stromspiegel-Steuer-FET     |    |

| 5     | Stromspiegel-Koppel-FET     | 30 |

| 6     | Strombegrenzungswiderstand  |    |

| 7     | zweiter Differenzverstärker |    |

| 8     | Referenzspannungsquelle     |    |

| 9     | Betriebsspannungsquelle     |    |

| $I_L$ | Laststrom                   | 35 |

| $I_g$ | gespiegelter Laststrom      |    |

#### Patentansprüche

1. Schaltungsanordnung zur Strombegrenzung veränderlicher Lastströme in Schaltungen mit einer Stromeinspeisung für eine Reihenschaltung bestehend aus einem Laststrom-Steuer-FET und einem Verbraucher, wobei die Reihenschaltung zwischen Stromeinspeisung und Masse geschaltet wird, mit einem Differenzverstärker, der mit einem ersten und einem zweiten Eingang sowie einem Ausgang versehen ist, wobei an dem zweiten Eingang eine Referenzspannungsquelle angeschlossen ist und der Ausgang mit dem Gate des Laststrom-Steuer-FET verbunden ist, und einer Betriebsspannungsquelle **dadurch gekennzeichnet**,

**daß** ein Stromspiegel angeordnet ist, der aus einem Stromspiegel-Steuer-FET (4) und dem Laststrom-Steuer-FET (1) besteht, daß der Sourceanschluß des Laststrom-Steuer-FET (1) und der Sourceanschluß des Stromspiegel-Steuer-FET (4) mit der

Betriebsspannungsquelle (9) verbunden ist und daß dem Stromspiegel ein Stromspiegel-Steuerpfad zugeordnet ist, bestehend aus einem Stromspiegel-Koppel-FET (5), dessen Sourceanschluß mit dem Drainanschluß des Stromspiegel-Steuer-FET (4) verbunden ist und dessen Drainanschluß mit dem ersten Eingang des Differenzverstärkers (3) verbunden ist, und einem Strombegrenzungswiderstand (6), wobei der Drainanschluß des Stromspiegel-Koppel-FET (5) zusätzlich mit dem Strombegrenzungswiderstand (6) in Reihe nach Masse geschaltet ist, daß der Ausgang des Differenzverstärker (3) mit dem Gate des Stromspiegel-Steuer-FET (4) verbunden ist, daß ein zweiter Differenzverstärker(7) mit einem ersten und zweiten Eingang und einem Ausgang angeordnet ist, wobei der erste Eingang des zweiten Differenzverstärkers (7) mit dem Sourceanschluß des Stromspiegel-Koppel-FET (5), der zweite Eingang des zweiten Differenzverstärkers (7) mit dem Verbraucher (2) und dem Drainanschluß des Laststrom-Steuer-FET (1) verbunden ist und der Ausgang an das Gate des Stromspiegel-Koppel-FET (5) angeschlossen ist.

Europäisches

Patentamt

EUROPÄISCHER RECHERCHENBERICHT

Nummer der Anmeldung

EP 01 10 9666

| EINSCHLÄGIGE DOKUMENTE                                                                            |                                                                                                                                                                                                                                                                                                                              |                     |                                                 |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------|

| Kategorie                                                                                         | Kennzeichnung des Dokuments mit Angabe, soweit erforderlich, der maßgeblichen Teile                                                                                                                                                                                                                                          | Betrift<br>Anspruch | KLASSIFIKATION DER<br>ANMELDUNG (Int.Cl.7)      |

| A                                                                                                 | EP 0 994 402 A (LUCENT TECHNOLOGIES INC)<br>19. April 2000 (2000-04-19)<br>* Zusammenfassung *<br>---                                                                                                                                                                                                                        | 1                   | G05F3/26                                        |

| A                                                                                                 | US 6 064 267 A (LEWYN LANNY)<br>16. Mai 2000 (2000-05-16)<br>* Spalte 1, Zeile 9 - Spalte 3, Zeile 25 *<br>---                                                                                                                                                                                                               | 1                   |                                                 |

| A                                                                                                 | US 5 519 310 A (BARTLETT DONALD M)<br>21. Mai 1996 (1996-05-21)<br>* Spalte 1, Zeile 11 - Spalte 2, Zeile 18<br>*<br>---                                                                                                                                                                                                     | 1                   |                                                 |

| A                                                                                                 | US 5 847 556 A (KOTHANDARAMAN MAKESHWAR ET AL) 8. Dezember 1998 (1998-12-08)<br>* Zusammenfassung *<br>---                                                                                                                                                                                                                   | 1                   |                                                 |

| A                                                                                                 | EP 0 356 570 A (SIEMENS AG)<br>7. März 1990 (1990-03-07)<br>* Zusammenfassung *<br>---                                                                                                                                                                                                                                       | 1                   |                                                 |

| A                                                                                                 | SERRANO T ET AL: "THE ACTIVE-INPUT<br>REGULATED-CASCODE CURRENT MIRROR"<br>IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS<br>I: FUNDAMENTAL THEORY AND APPLICATIONS,<br>IEEE INC. NEW YORK, US,<br>Bd. 41, Nr. 6, 1. Juni 1994 (1994-06-01),<br>Seiten 464-467, XP000460535<br>ISSN: 1057-7122<br>* das ganze Dokument *<br>----- | 1                   | RECHERCHIERTE<br>SACHGEBiete (Int.Cl.7)<br>G05F |

| Der vorliegende Recherchenbericht wurde für alle Patentansprüche erstellt                         |                                                                                                                                                                                                                                                                                                                              |                     |                                                 |

| Recherchenort                                                                                     | Abschlußdatum der Recherche                                                                                                                                                                                                                                                                                                  | Prüfer              |                                                 |

| DEN HAAG                                                                                          | 5. Oktober 2001                                                                                                                                                                                                                                                                                                              | Schobert, D         |                                                 |

| KATEGORIE DER GENANNTEN DOKUMENTE                                                                 |                                                                                                                                                                                                                                                                                                                              |                     |                                                 |

| X : von besonderer Bedeutung allein betrachtet                                                    | T : der Erfindung zugrunde liegende Theorien oder Grundsätze                                                                                                                                                                                                                                                                 |                     |                                                 |

| Y : von besonderer Bedeutung in Verbindung mit einer anderen Veröffentlichung derselben Kategorie | E : älteres Patentdokument, das jedoch erst am oder nach dem Anmelde datum veröffentlicht worden ist                                                                                                                                                                                                                         |                     |                                                 |

| A : technologischer Hintergrund                                                                   | D : in der Anmeldung angeführtes Dokument                                                                                                                                                                                                                                                                                    |                     |                                                 |

| O : nichtschriftliche Offenbarung                                                                 | L : aus anderen Gründen angeführtes Dokument                                                                                                                                                                                                                                                                                 |                     |                                                 |

| P : Zwischenliteratur                                                                             | & : Mitglied der gleichen Patentfamilie, übereinstimmendes Dokument                                                                                                                                                                                                                                                          |                     |                                                 |

**ANHANG ZUM EUROPÄISCHEN RECHERCHENBERICHT

ÜBER DIE EUROPÄISCHE PATENTANMELDUNG NR.**

EP 01 10 9666

In diesem Anhang sind die Mitglieder der Patentfamilien der im obengenannten europäischen Recherchenbericht angeführten Patentdokumente angegeben.

Die Angaben über die Familienmitglieder entsprechen dem Stand der Datei des Europäischen Patentamts am

Diese Angaben dienen nur zur Unterrichtung und erfolgen ohne Gewähr.

05-10-2001

| Im Recherchenbericht<br>angeführtes Patentdokument |   | Datum der<br>Veröffentlichung |          | Mitglied(er) der<br>Patentfamilie |  | Datum der<br>Veröffentlichung |

|----------------------------------------------------|---|-------------------------------|----------|-----------------------------------|--|-------------------------------|

| EP 0994402                                         | A | 19-04-2000                    | EP<br>US | 0994402 A1<br>6194957 B1          |  | 19-04-2000<br>27-02-2001      |

| US 6064267                                         | A | 16-05-2000                    | AU<br>WO | 6046299 A<br>0020942 A1           |  | 26-04-2000<br>13-04-2000      |

| US 5519310                                         | A | 21-05-1996                    | JP       | 7122946 A                         |  | 12-05-1995                    |

| US 5847556                                         | A | 08-12-1998                    | EP<br>JP | 0924590 A1<br>11272346 A          |  | 23-06-1999<br>08-10-1999      |

| EP 0356570                                         | A | 07-03-1990                    | EP<br>DE | 0356570 A1<br>3913446 A1          |  | 07-03-1990<br>15-03-1990      |