(19)

Europäisches Patentamt

European Patent Office

Office européen des brevets

(11)

EP 1 209 954 A1

(12)

## EUROPEAN PATENT APPLICATION

(43) Date of publication:

**29.05.2002 Bulletin 2002/22**

(51) Int Cl.<sup>7</sup>: **H05B 41/00, H05B 41/28,**

**H05B 39/04, G05F 1/00**

(21) Application number: **00310431.2**

(22) Date of filing: **24.11.2000**

(84) Designated Contracting States:

**AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU**

**MC NL PT SE TR**

Designated Extension States:

**AL LT LV MK RO SI**

(71) Applicant: **City University of Hong Kong**

**Kowloon (CN)**

(72) Inventors:

- **Hui, Shu-Yuen Ron**

**Shatin, N.T., Hong Kong (CN)**

• **Chung, Shu-Hung Henry, Flat A, 19th Floor**

**Hong Kong (CN)**

(74) Representative:

**Watkin, Timothy Lawrence Harvey**

**Lloyd Wise, Tregear & Co.,**

**Commonwealth House,**

**1-19 New Oxford Street**

**London, WC1A 1LW (GB)**

### (54) Dimming control of electronic ballasts

(57) The invention provides an apparatus and a method for controlling the power output of a fluorescent lamp in order to provide dimming control. The fluorescent lamp is driven by an electronic ballast, for example a half-bridge resonant inverter, and the electronic ballast is switched at a constant frequency and with a constant duty-cycle, but with a variable DC voltage power input.

Dimming control is provided by variation of the DC voltage power supply. The variable DC supply may be obtained from an AC source followed by a power factor corrected AC-DC variable converter, or a DC source followed by a variable DC-DC converter.

## Description

### FIELD OF THE INVENTION

**[0001]** This invention relates to an apparatus and method for the dimming control of an electronic ballast for a fluorescent lamp. In particular the invention relates to an apparatus and method for such dimming control that generates low electromagnetic interference and low switching stress.

### BACKGROUND OF THE INVENTION

**[0002]** Electronic ballasts for the high-frequency operation of fluorescent lamps have been increasingly adopted as an energy efficient solution in residential, commercial and industrial lighting applications. Electronic ballasts have a number of advantages including improved efficiency of the overall system, higher lumen output per watt and longer lifetime of the fluorescent lamps. Electronic ballasts are in effect switched mode power electronic circuits, and most modern electronic ballast designs employ series resonant converters as the power circuits for driving the lamps.

### PRIOR ART

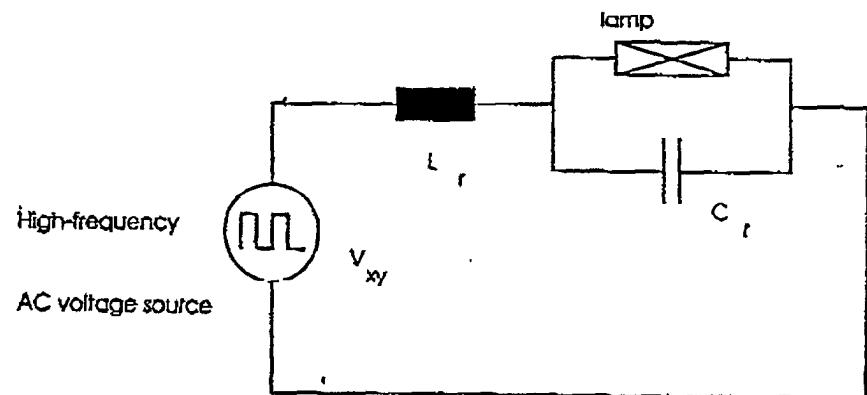

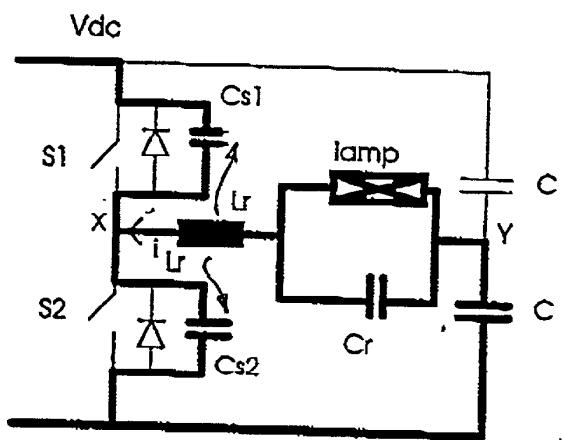

**[0003]** Fig.1 shows a conventional electronic ballast design. The basic concept of this design is to use the resonant voltage across the resonant capacitor  $C_r$  to cause the lamp arc to strike at high frequency, typically from 25kHz to 50kHz. Because of the high frequency of the excitation voltage the lamp is essentially in a continuous on-state, which provides high-quality illumination without any unwanted flickering effect.

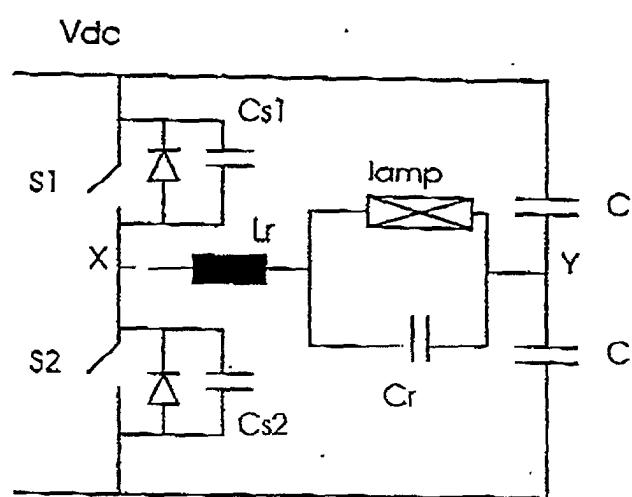

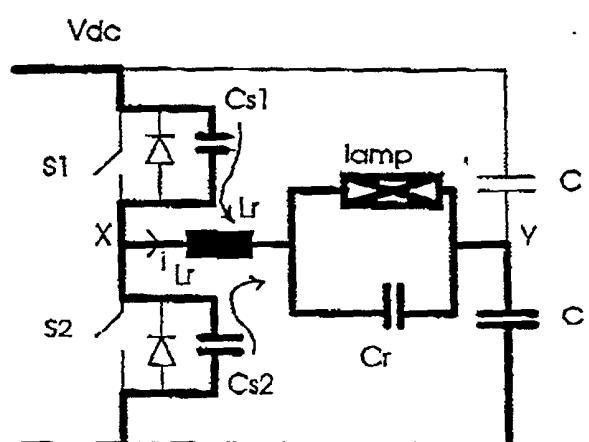

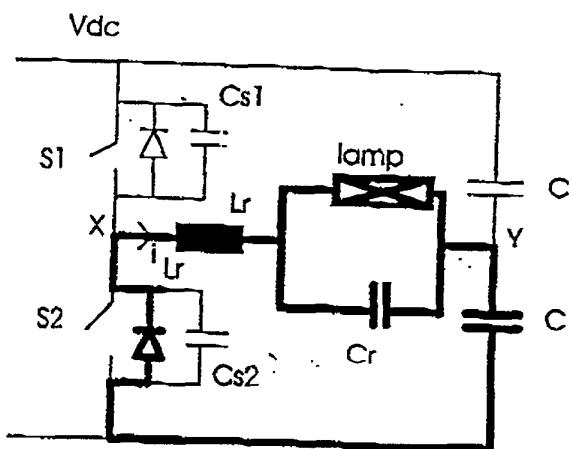

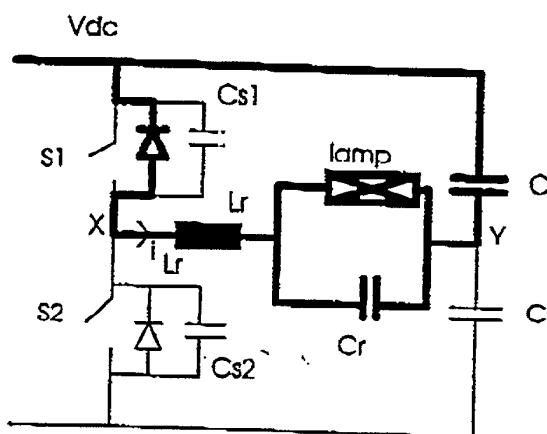

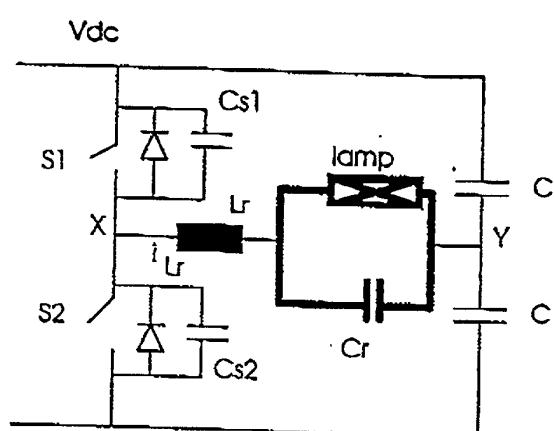

**[0004]** Fig.2 shows a conventional implementation of a half-bridge series resonant inverter for an electronic ballast application. In this arrangement the two switches S1 and S2 are complementary switches (ie when S1 is on S2 is off, and vice versa). If the potential at point Y is taken as the zero voltage reference point, then voltage  $V_{xy}$  will have the values  $\pm V_{dc}/2$  where  $V_{dc}$  is the DC voltage applied to the ballast circuit either by an AC-DC converter if the power source is AC or by a DC-DC converter if the power source is DC. The operation of this conventional circuit will now be described for the purposes of illustration.

**[0005]** The two capacitors C are much larger than the resonant capacitor  $C_r$  and provide a stable DC voltage nominally at  $V_{dc}/2$  at the point Y. By operating the switching frequency  $f_{sw}$  of S1 and S2 slightly higher than the resonant frequency  $f_r$  of inductor  $L_r$  and capacitor  $C_r$ , the resonant load becomes inductive. If the current ( $i_{Lr}$ ) in the inductor  $L_r$  is continuous, S1 and S2 can be turned on under zero-voltage. This zero-voltage switching is desirable because it reduces turn-on switching loss and minimises the electromagnetic interference (EMI) from the power switches. If additional small capacitors  $Cs1$

and  $Cs2$  are added as shown in Fig.2, switches S1 and S2 can also be turned off under zero-voltage as long as the inductor current ( $i_{Lr}$ ) is continuous.

**[0006]** Series resonant converter designs such as that shown in Fig.2 are very popular. One reason for this popularity, for example, is that a circuit of this design can be used for a multiple lamp system simply by connecting several sets of resonant tanks and lamps across points X and Y. This flexibility greatly reduces the ballast cost per lamp.

**[0007]** Difficulties arise with the circuit of Fig.2, however, when it is desired to provide a method of dimming control. Most electronic ballasts employ a nominally constant converter DC voltage and in order to control the light intensity of the fluorescent lamp dimming control is provided. Two methods of providing dimming control are commonly used in this type of ballast arrangement; duty cycle control and variation of switching frequency and these will now both be described.

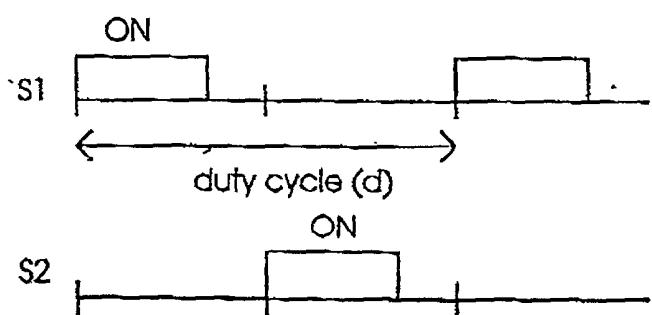

**[0008]** The first method of dimming control is by control of the duty cycle ( $d$ ) of the two switches S1 and S2. The ideal duty cycle is 0.5 but in practice the maximum  $d$  should be slightly less than 0.5 so that a small dead-time when both switches are off is provided to avoid shoot-through in S1 and S2. Fig.3 shows typical waveforms of the gating signals of S1 and S2. By controlling the turn-on and turn-off times of the two switches the voltage applied to the series resonant circuit can be controlled. This method is not without its drawbacks however, especially at low duty-cycles, ie at low applied voltage, as will be seen from the following.

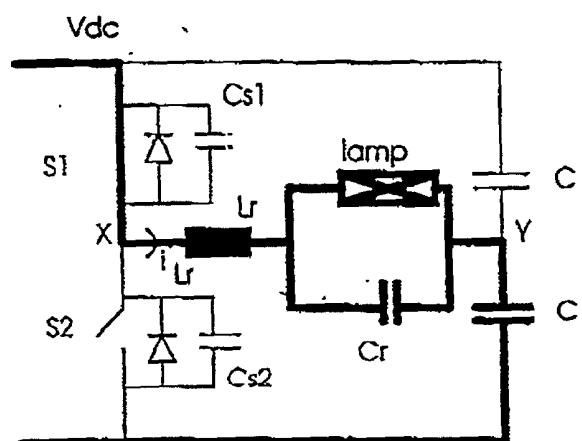

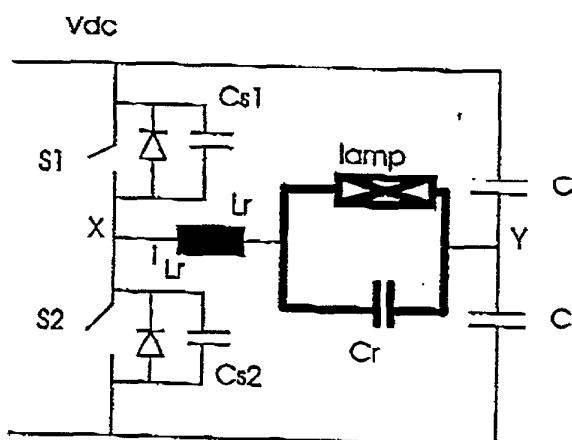

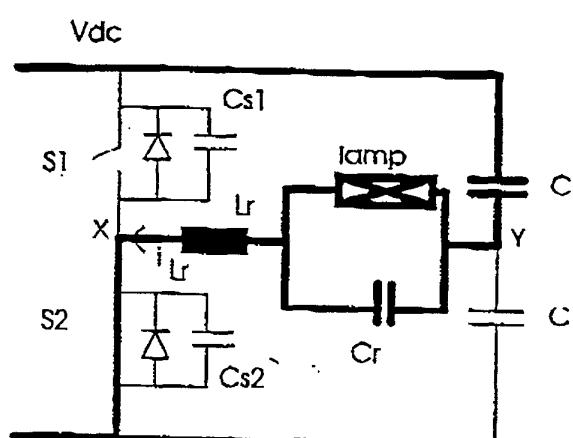

**[0009]** A major advantage of the circuit of Fig.2 is that the switches can be turned on and off under zero-voltage conditions which substantially reduces EMI emission and switching stress in the power switches. However as will be seen below, if the duty cycle is too small the inductor current may become discontinuous and the zero-voltage switching conditions will be lost and the switches will suffer switching stress, leading to reduced reliability and increased EMI emission. This can be seen from the following explanation of the operating modes of the power converter which are described with reference to Fig.4 of the accompanying drawings which schematically highlight the main current paths.

**[0010]** Fig.4(a) shows a first stage in which switch S1 is ON while switch S2 is OFF and the main current path is highlighted in bold. In a second stage shown in Fig.4 (b) the two switches are OFF while  $Cs1$  is charged up to  $V_{DC}$  and  $Cs2$  is discharged. When  $Cs2$  is discharged the anti-parallel diode of S2 will start to conduct. Again the main current path is highlighted in bold. Fig.4(c) shows this third stage in which the two switches S1 and S2 are both still OFF and the anti-parallel diode is conducting clamping the voltage across S2 to almost 0V and when the switch S2 is later turned on again it is turned on under this zero-voltage condition. However, this assumes that the inductor current is continuous. If the duty cycle is too small the inductor current may de-

cay to zero before the switch S2 is turned on again giving the condition shown in Fig.4(d). If the inductor current falls to zero before S2 is switched on again, the voltage across S2 is not clamped to near zero and as both switches are turned off the voltage across S2 and thus Cs2 will rise. When in the next stage S2 is turned on again the energy stored in Cs2 will be dissipated in S2 causing high discharge current and high switching loss and stress in S2.

**[0011]** In the next stage shown in Fig.4(e) S2 is ON while S1 is OFF and the inductor current becomes negative. As both switches once more go to OFF, shown in Fig.4(f), the anti-parallel diode of S1 starts to conduct clamping the voltage across S1 to near zero (Fig.4(g)). Again, as with S2, if the duty cycle is not too small S1 will be switched on again before the inductor current decays to zero and so will be switched on while still clamped to near zero voltage, with the advantages discussed above. If the duty cycle is too small, however, the inductor current will decay to zero before S1 is switched on again causing the voltage across S1 and Cs1 to rise. When S1 is finally turned on again the energy stored in Cs1 is dissipated in S1 as discussed above with regard to S2 and with the same problems. This possibility is shown in Fig.4(h).

**[0012]** Thus if dimming control by variation of duty cycle is provided, soft switching is possible provided that the inductor current is continuous. However if the duty cycle is reduced too far then the inductor current may at points in the cycle decay to zero and non-zero-voltage switching takes place with its attendant disadvantages of higher EMI emission and higher switching stress.

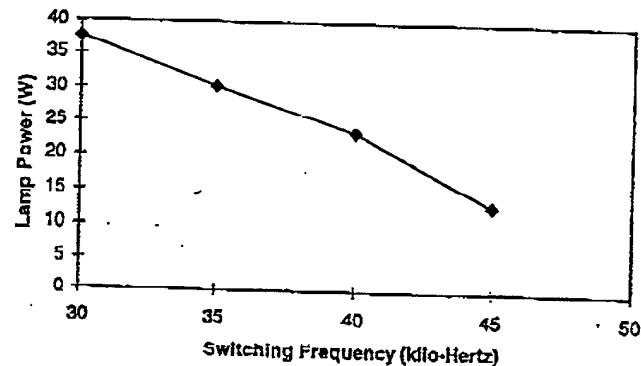

**[0013]** As an alternative to dimming control by duty cycle variation, it is also known to provide dimming control by varying the switching frequency. If the switching frequency is increased, the inductor impedance is increased and thus the inductor current is reduced. This allows the output of a fluorescent lamp to be controlled by varying the switching frequency and Fig.5 shows the power of a 4-ft 40W fluorescent lamp plotted against switching frequency. It can be seen that the lamp power, and therefore the intensity of the emitted light, decreases with increasing switching frequency.

**[0014]** Dimming control by varying switching frequency has its own disadvantages however. These include the following points:

1. If the inverter bridge is not soft-switched the switching loss of the inverter will be increased leading to reduced efficiency.

2. In order to achieve dimming control at low lamp power operation, the switching frequency range has to be very wide (eg from 25kHz to 65kHz) and in practice the frequency range of the magnetic cores, the gate drive circuits and electronic control circuit may all act to limit the range of dimming control.

3. Soft-switching is not easy to achieve over the entire switching frequency range. In particular, at light

loads soft-switching cannot be achieved and the switching stress is large. The switching transients due to hard-switching are a major source of EMI emissions.

5 4. The power range of the dimming control is limited if the switching frequency range is small. A typical range of dimming control is from 100% load to 25% load.

## 10 SUMMARY OF THE INVENTION

**[0015]** Viewed from one broad aspect the present invention provides apparatus for controlling the power output of a fluorescent lamp comprising, an electronic ballast for driving said fluorescent lamp, power supply means for providing DC power input to said electronic ballast, and means for varying the voltage of said DC power input to said electronic ballast.

**[0016]** In one embodiment the power supply may 20 comprise an AC power input followed by an AC-DC converter capable of providing a (i) power factor correction and (ii) variable DC output. Such converters may comprise a diode bridge followed by one of (a) a flyback converter, (b) a Cuk converter, (c) a SEPIC converter, (d) a 25 Shepherd-Taylor converter, and (e) a boost converter. Preferably this front end converter uses soft-switching.

**[0017]** Alternatively in another embodiment the power supply may comprise a DC power input followed by a 30 DC-DC converter capable of providing a variable DC output. The converter may be a step-down or a step-up/step-down converter.

**[0018]** Preferably the electronic ballast comprises a 35 half-bridge series resonant inverter. The ballast preferably comprises two switches soft-switched at a constant frequency slightly higher than the resonant frequency of an inductor-capacitor tank of the ballast. The switches are preferably switched at a constant duty-cycle, preferably as close as possible to 0.5 while providing a short deadtime therebetween to prevent shoot-through.

**[0019]** Viewed from another broad aspect the present 40 invention provides a method for controlling the power output of a fluorescent lamp driven by means of an electronic ballast in the form of a half-bridge resonant inverter, comprising operating said ballast at a constant duty cycle and a constant frequency and providing a variable 45 DC power input to said ballast.

## BRIEF DESCRIPTION OF THE DRAWINGS

50 **[0020]** Some embodiments of the invention will now be described by way of example and with reference to the accompanying drawings, in which;

55 Fig.1 is a simplified schematic drawing of a series-resonant inverter based electronic ballast of the prior art,

Fig.2 is a schematic diagram of a half-bridge series resonant inverter based electronic ballast of the pri-

or art,

Fig.3 illustrates typical waveforms of gating signals for the switches of the ballast of Fig.2,

Figs.4(a)-(h) illustrate successive operational stages of the ballast of Fig.2 with the main current path of each stage being highlighted in bold,

Fig.5 is a plot showing expected lamp power against switching frequency in an alternative prior art method of dimming control,

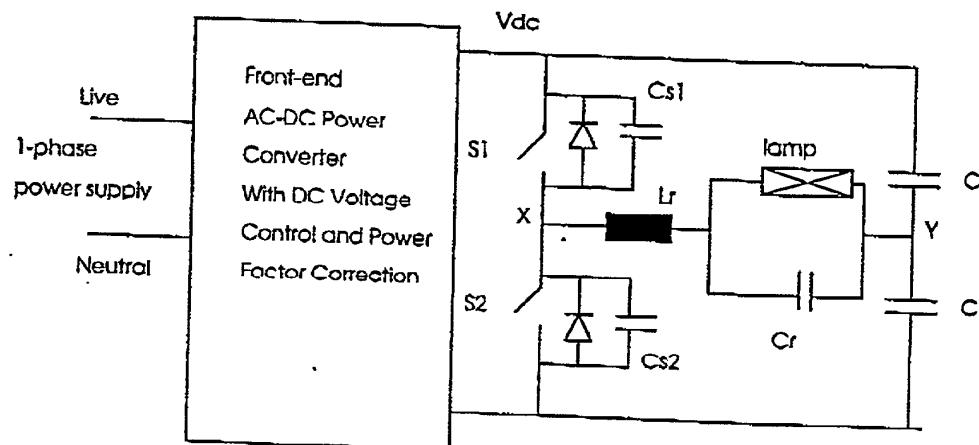

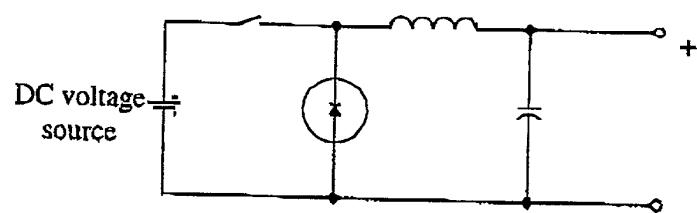

Fig.6 is a schematic diagram of an electronic ballast provided with dimming control in accordance with a first embodiment of this invention,

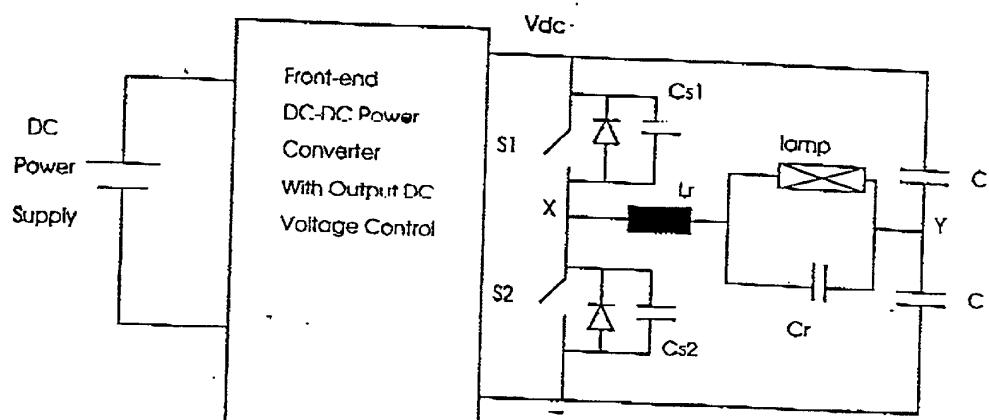

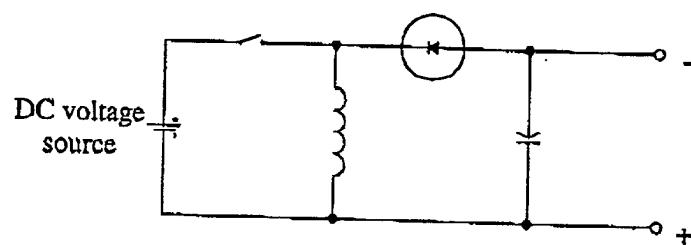

Fig.7 is a view corresponding to Fig.6 of a second embodiment of the invention,

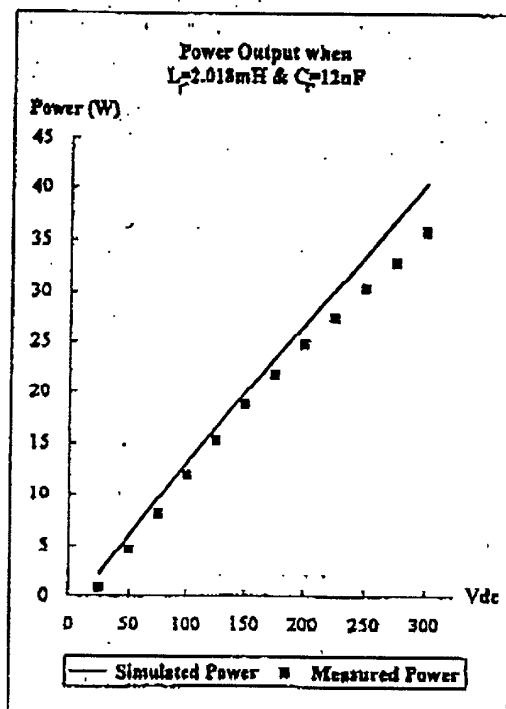

Fig.8 is a plot showing lamp power output as a function of converter voltage,

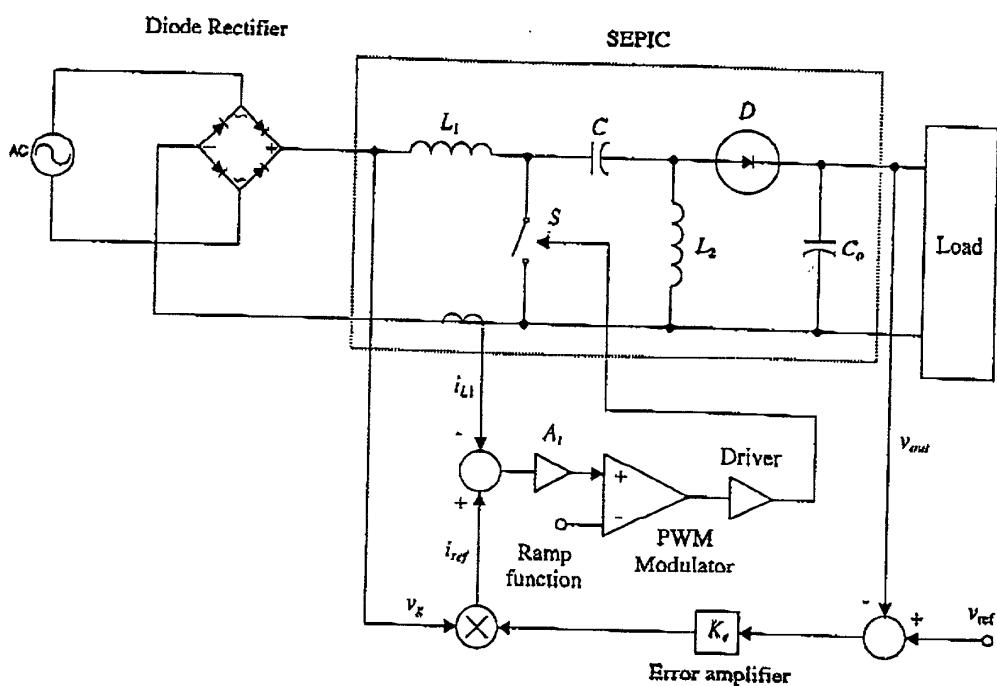

Fig.9 schematically illustrates one form of AC-DC converter that may be used in the present invention,

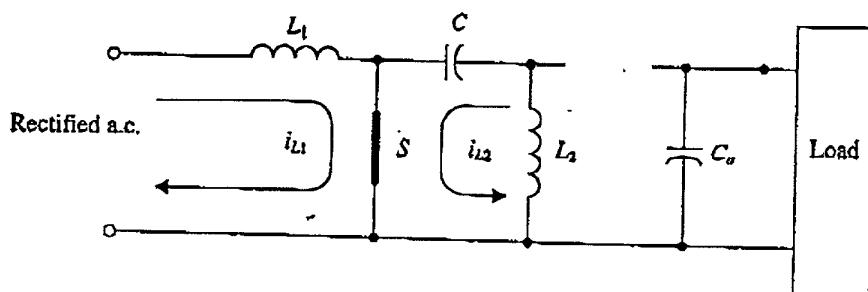

Figs.10(a) and (b) illustrate alternate topologies for the converter of Fig.9,

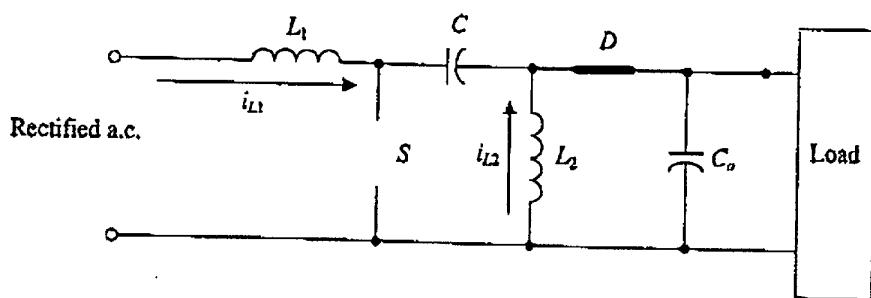

Fig.11 schematically illustrates another form of AC-DC converter that may be used in the present invention,

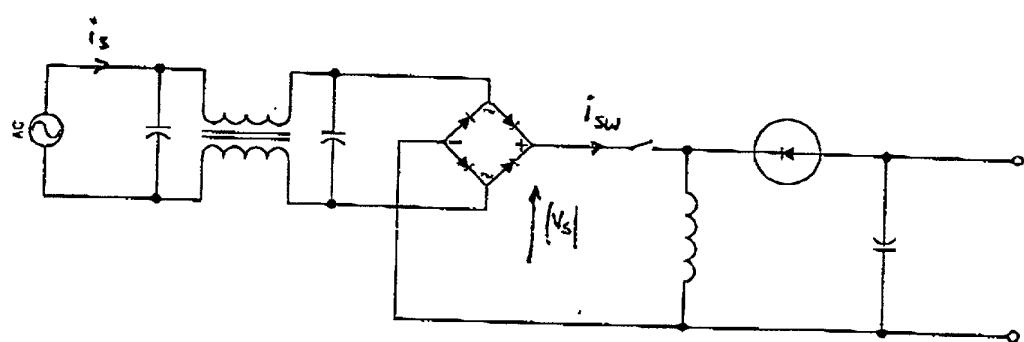

Fig.12 shows typical waveforms for the switch current and the input phase current in the converter of Fig.11,

Fig.13 shows one form of DC-DC converter that may be used in another embodiment of the present invention, and

Fig.14 shows an alternate form of DC-DC converter.

#### DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS

**[0021]** In the present invention, dimming control is achieved by the use of a variable converter DC voltage as the means to provide a smooth and desirable dimming control for a fluorescent lamp system. Referring to Fig.6 it will be seen that a power converter is inserted between the input power supply and the half-bridge circuit with the power converter being able to produce a variable  $V_{DC}$  output to the half-bridge circuit. Fig.6 assumes that the power supply is AC and so the converter is an AC-DC converter, but as shown in Fig.7 the same principle can apply when the input power supply is DC by providing a front-end DC-DC converter with control of the output DC voltage,

**[0022]** In the present invention the output DC voltage  $V_{DC}$  of the front-end converter is controlled in order to control the lamp power. A constant duty-cycle (nearly 0.5) is used for the switching of the half-bridge inverter in order to ensure a wide power range of continuous inductor current operation and thus soft-switching operation. This has the further advantage of making switching control simple. A constant switching frequency is used in the converter so that the resonant  $L$ - $C$  circuit can be optimised for any given type of lamp.

**[0023]** As shown in Fig.6 if the input power supply is

an AC supply, the front end converter must naturally be an AC-Dc converter. Examples of suitable AC DC converters include (a) a diode bridge followed by a flyback converter, (b) a diode bridge followed by a Cuk converter, (c) a diode bridge followed by a Sepic converter, (d) a diode bridge followed by a Shepherd-Taylor converter, and (e) a diode bridge followed by a boost converter.

These five AC-DC converters can provide input power factor correction in order to reduce voltage harmonics and current harmonics in the AC power supply. In addition, to further reduce EMI emissions, soft-switching is preferably incorporated into the front-end converter. This may be achieved by adding an auxiliary circuit to the front-end converter.

**[0024]** A significant advantage of controlling  $V_{DC}$  to provide dimming control is that lamp power decreases smoothly and almost linearly with decreasing  $V_{DC}$ . This can be seen from Fig.7 which shows simulated and measured lamp power values as a function of  $V_{DC}$  for a

4-ft 40W lamp under a constant duty cycle and constant switching frequency. From Fig.7 it can be seen that there is a substantially linear relationship between lamp power and  $V_{DC}$  which makes dimming control very easy and convenient.

**[0025]** Fig.9 illustrates an embodiment comprising a front-end SEPIC (single-ended-primary-inductance-converter). In consideration of this embodiment the half-bridge resonant electronic ballast can be considered as the load. The SEPIC comprises one controlled switch  $S$  and one uncontrolled switch  $D$ . The controlled switch  $S$  can be a MOSFET, BJT, IGBT or the like and its conduction state is determined by the gate signal  $v_{gate}$ . In order to avoid needing to use an input line filter the converter is operated in continuous conduction mode where

two circuit topologies are switched alternately in one cycle. These topologies are shown in Fig.10.

**[0026]** In the first topology - shown in Fig.10(a) -  $S$  is on while  $D$  is reverse biased and the currents in the inductors  $L_1$  and  $L_2$  ( $i_{L1}$  and  $i_{L2}$ ) increase. When  $i_{L1}$  reaches a programmed threshold value  $S$  will be switched off. This leads to the second topology shown in Fig.10(b) where  $S$  is off and  $D$  conducts. The output capacitor  $C_o$  is then charged by the sum of the currents in  $L_1$  and  $L_2$ .

**[0027]** The input current of the SEPIC is controlled to follow the full-rectified waveform of the sinusoidal input voltage  $v_g$  by pulse-width modulation (PWM) control. In this technique the reference signal  $i_{ref}$  for the current-shaping feedback loop is proportional to  $v_g$ . The input current is sensed and compared to the reference signal

and an identified error signal is amplified by a current loop amplifier  $A_1$  the output of which is compared to a ramp function. In this way the duty ratio of  $S$  may be adjusted in order to minimize the error between the reference current and the sensed line current. Thus, the output voltage is in fact controlled by adjusting the reference current  $i_{ref}$ . This requires a multiplier circuit in the voltage feedback loop, and an error amplifier  $K_e$ , such as a proportional-plus-integral controller, is used to

process the error between the output voltage  $v_{out}$  and a reference voltage  $v_{ref}$  to give a necessary signal to one of the multiplier inputs so that  $v_{out}$  will follow the desired magnitude of  $v_{ref}$ .

**[0028]** Fig.11 illustrates an alternative embodiment with an AC-DC front-end converter. In this embodiment the front-end converter comprises an AC-DC flyback converter. The input voltage to the flyback converter (enclosed in the dashed box) is the rectified version of the AC input voltage  $v_s$ , and if the flyback converter is switched so that the flyback inductor current  $i_L$  is discontinuous, the envelope of the current pulses will follow the shape of the rectified voltage waveform. The input L-C filter reduces the current ripple and thus the input phase current  $i_s$  is sinusoidal as shown in Fig.12. If the switching frequency is high, say 20kHz to 100kHz, the current ripple becomes negligible. In this embodiment the AC-DC converter shapes the current into a sinusoidal curve so as to achieve a unitary power factor (ie current is sinusoidal and in phase with the input voltage). The magnitude of the input AC voltage may be fixed by the mains supply (220V say) but the input current magnitude can be controlled and thus the output of the AC-DC converter may be controlled by controlling the magnitude of the input AC current.

**[0029]** Where the input power supply is DC the choice of the most suitable DC-DC converter depends on the voltage level of the input DC supply, and hence whether a step-up or a step-down converter is necessary. Examples of possible DC-DC front-end converters are shown in Fig.13 and Fig.14. Fig.13 shows a possible step-down (buck) converter, while Fig.14 shows a flyback converter that may be either a step-up or step-down converter.

**[0030]** Thus it will be seen that in its preferred forms the present invention provides a ballast comprising a front-end converter that can provide a variable DC voltage output. The front-end converter can be a power-factor-corrected AC-DC converter (preferably with soft-switching) if the input supply is AC, and a DC-DC converter if the input supply is DC. The DC output voltage of the front-end converter is fed to a soft-switched half-bridge inverter with an inductor-capacitor resonant circuit. The fluorescent lamp is connected across the resonant capacitor. The two switches in the half-bridge inverter are switched at a constant frequency slightly higher than the resonant frequency of the inductor-capacitor tank. The two inverter switches are switched in a complementary manner with a large constant duty cycle in order to achieve soft-switching in the half-bridge inverter over a wide power range.

**[0031]** To control the brightness of the lamp to provide a dimming control, the lamp power is simply controlled by varying the DC output voltage of the front-end converter. This allows the inverter bridge to operate under continuous inductor current mode regardless of the power output of the lamp, ie from nominal DC voltage for full lamp power down to very low DC voltage for low lamp power, thereby reducing EMI emissions from the

inverter bridge over a wide power range. Together with power-factor-corrected and soft-switched front-end AC-DC or DC-DC converter, the present invention allows the entire ballast system to have low conducted and radiated EMI emission, low switching losses and stress, and thus high reliability. The present invention may also be applied to single or multi-lamp systems.

10 **Claims**

1. Apparatus for controlling the power output of a fluorescent lamp comprising, an electronic ballast for driving said fluorescent lamp, power supply means for providing DC power input to said electronic ballast, and means for varying the voltage of said DC power input to said electronic ballast.

2. Apparatus as claimed in claim 1 wherein said ballast comprises a half-bridge series resonant inverter.

3. Apparatus as claimed in claim 1 wherein said power supply means comprises an AC power supply and wherein a power factor corrected AC-DC converter capable of producing a variable DC output is provided between said power supply and said electronic ballast.

4. Apparatus as claimed in claim 3 wherein said AC-DC converter comprises a diode bridge followed by one of (a) a flyback converter, (b) a Cuk converter, (c) a Sepic converter, (d) a Shepherd-Taylor converter, and (e) a boost converter.

5. Apparatus as claimed in claim 4 wherein said converter uses soft-switching.

6. Apparatus as claimed in claim 1 wherein said power supply means comprises a DC power supply and wherein a DC-DC converter capable of producing a DC output is provided between said power supply means and said electronic ballast.

7. Apparatus as claimed in claim 6 wherein said DC DC converter is a step-down converter.

8. Apparatus as claimed in claim 6 wherein said DC DC converter is a step-down or step-up converter.

9. Apparatus as claimed in claim 1 wherein said electronic ballast comprises two switches soft-switched at a constant frequency slightly higher than the resonant frequency of an inductor-capacitor tank of said ballast.

10. Apparatus as claimed in claim 9 wherein said switches are switched at a constant duty-cycle.

11. Apparatus as claimed in claim 10 wherein said duty cycle is slightly below 0.5.

12. A method for controlling the power output of a fluorescent lamp driven by means of an electronic ballast in the form of a half-bridge resonant inverter, comprising operating said ballast at a constant duty cycle and a constant frequency and providing a variable DC power input to said ballast. 5

10

15

20

25

30

35

40

45

50

55

FIG. 1

FIG. 2

FIG. 3

FIG. 4(a)

FIG. 4(s)

FIG. 4(c)

FIG. 4(d)

FIG. 4(e)

FIG. 4(f)

FIG. 4(g)

FIG. 4(h)

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10(a)

Topology 1

FIG. 10(s)

Topology 2

FIG. 11

FIG. 12

FIG. 13

FIG. 14

## EUROPEAN SEARCH REPORT

Application Number

EP 00 31 0431

| DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                          |                                                                               |                   | CLASSIFICATION OF THE APPLICATION (Int.Cl.7) |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------|----------------------------------------------|--|--|

| Category                                                                                                                                                                                                                                                                     | Citation of document with indication, where appropriate, of relevant passages | Relevant to claim | CLASSIFICATION OF THE APPLICATION (Int.Cl.7) |  |  |

| X                                                                                                                                                                                                                                                                            | WO 00 48433 A (KONINKL PHILIPS ELECTRONICS NV) 17 August 2000 (2000-08-17)    | 1-3,6,9,<br>10,12 | H05B41/00                                    |  |  |

| A                                                                                                                                                                                                                                                                            | * page 1, line 1-26 *                                                         | 4,5,7,9,<br>11    | H05B41/28                                    |  |  |

|                                                                                                                                                                                                                                                                              | * page 3, line 22 - page 8, line 12;<br>claims 1-10; figures 1,5,6 *          | -----             | H05B39/04                                    |  |  |

| X                                                                                                                                                                                                                                                                            | US 5 289 083 A (QUAZI FAZLE S)<br>22 February 1994 (1994-02-22)               | 1-3,6,9,<br>10,12 | G05F1/00                                     |  |  |

| A                                                                                                                                                                                                                                                                            | * column 1, line 18 - column 2, line 54 *                                     | 4,5,7,9,<br>11    |                                              |  |  |

|                                                                                                                                                                                                                                                                              | * column 3, line 46 - column 7, line 20;<br>claims 1-7; figure 2 *            | -----             |                                              |  |  |

| X                                                                                                                                                                                                                                                                            | US 5 488 269 A (KACHMARIK DAVID J ET AL)<br>30 January 1996 (1996-01-30)      | 1-3,6,9,<br>10,12 |                                              |  |  |

| A                                                                                                                                                                                                                                                                            | * column 1, line 13 - column 2, line 12 *                                     | 4,5,7,9,<br>11    |                                              |  |  |

|                                                                                                                                                                                                                                                                              | * column 3, line 7 - column 7, line 32;<br>claims 1-14; figures 1,2,6 *       | -----             |                                              |  |  |

|                                                                                                                                                                                                                                                                              |                                                                               |                   | TECHNICAL FIELDS<br>SEARCHED (Int.Cl.7)      |  |  |

|                                                                                                                                                                                                                                                                              |                                                                               |                   | H05B<br>G05F                                 |  |  |

| The present search report has been drawn up for all claims                                                                                                                                                                                                                   |                                                                               |                   |                                              |  |  |

| Place of search                                                                                                                                                                                                                                                              | Date of completion of the search                                              | Examiner          |                                              |  |  |

| MUNICH                                                                                                                                                                                                                                                                       | 1 February 2001                                                               | Pierron, P        |                                              |  |  |

| CATEGORY OF CITED DOCUMENTS                                                                                                                                                                                                                                                  |                                                                               |                   |                                              |  |  |

| X : particularly relevant if taken alone<br>Y : particularly relevant if combined with another document of the same category<br>A : technological background<br>O : non-written disclosure<br>P : intermediate document                                                      |                                                                               |                   |                                              |  |  |

| T : theory or principle underlying the invention<br>E : earlier patent document, but published on, or after the filing date<br>D : document cited in the application<br>L : document cited for other reasons<br>& : member of the same patent family, corresponding document |                                                                               |                   |                                              |  |  |

ANNEX TO THE EUROPEAN SEARCH REPORT

ON EUROPEAN PATENT APPLICATION NO.

EP 00 31 0431

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

01-02-2001

| Patent document<br>cited in search report |   | Publication<br>date |    | Patent family<br>member(s) | Publication<br>date |

|-------------------------------------------|---|---------------------|----|----------------------------|---------------------|

| WO 0048433                                | A | 17-08-2000          | EP | 1070440 A                  | 24-01-2001          |

| US 5289083                                | A | 22-02-1994          | AU | 642862 B                   | 04-11-1993          |

|                                           |   |                     | AU | 5106690 A                  | 05-09-1990          |

|                                           |   |                     | AU | 674187 B                   | 12-12-1996          |

|                                           |   |                     | AU | 5492894 A                  | 14-04-1994          |

|                                           |   |                     | CA | 2046278 A                  | 11-08-1990          |

|                                           |   |                     | EP | 0462120 A                  | 27-12-1991          |

|                                           |   |                     | WO | 9009729 A                  | 23-08-1990          |

| US 5488269                                | A | 30-01-1996          | CN | 1135155 A                  | 06-11-1996          |

|                                           |   |                     | EP | 0726696 A                  | 14-08-1996          |

|                                           |   |                     | JP | 8336235 A                  | 17-12-1996          |