(12)

# **EUROPÄISCHE PATENTANMELDUNG**

(43) Veröffentlichungstag:

26.06.2002 Patentblatt 2002/26

(21) Anmeldenummer: 01000708.6

(22) Anmeldetag: 05.12.2001

(84) Benannte Vertragsstaaten:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE TR

Benannte Erstreckungsstaaten:

AL LT LV MK RO SI

(30) Priorität: 06.12.2000 DE 10060483

(71) Anmelder:

Philips Corporate Intellectual Property GmbH 52066 Aachen (DE)

Benannte Vertragsstaaten:

DE

Koninklijke Philips Electronics N.V. 5621 BA Eindhoven (NL)

Benannte Vertragsstaaten:

**FR GB**

(72) Erfinder: Kohsiek, Cord Heinrich Weisshausstrasse 2 52066, Aachen (DE)

(51) Int CI.7: H03G 7/00

(74) Vertreter: Volmer, Georg, Dipl.-Ing. et al Philips Intellectual Property & Standards, Weisshausstrasse 2 52066 Aachen (DE)

#### (54) Schaltungsanordnung

- (57) Um eine Schaltungsanordnung (100) sowie ein Verfahren zum Erzeugen und Verstärken eines in seiner Amplitude begrenzten Gleichspannungssignals, dessen Pegelspannung im wesentlichen proportional zum Logarithmus der Spannungsamplitude eines Eingangssignals ist, zu schaffen, durch die die Pegelanzeige, das heißt die Pegelspannung des in der Schaltungsanordnung sowie mittels des Verfahrens erzeugten und verstärkten Gleichspannungssignals nur von der Amplitude, nicht jedoch von der Frequenz des Eingangssignals abhängt, wird vorgeschlagen,

- dass der letzten Verstärkungsstufe (30), insbesondere den Kollektorschaltungen der letzten Verstärkungsstufe (30) einer mindestens zwei Verstär-

- kungsstufen (10; 20; 30) aufweisenden Verstärkerschaltung eine Frequenz-(FM-)Demodulatoreinheit (40) nachgeschaltet ist,

- dass der Frequenz-(FM-)Demodulatoreinheit (40) mindestens eine Quadriererstufe (50, 60, 70) zum Quadrieren des Ausgangssignals der Frequenz-(FM-)Demodulatoreinheit (40), insbesondere des Wechselspannungsanteils des Ausgangssignals der Frequenz-(FM-)Demodulatoreinheit (40), nachgeschaltet ist und

- dass mindestens eine Stromaddierereinheit (80) zum Addieren der Pegelspannung des Ausgangssignals der Quadriererstufe (50, 60, 70) mit der Pegelspannung der Verstärkungsstufen (10; 20; 30) vorgesehen ist.

#### Beschreibung

[0001] Die Erfindung betrifft eine Schaltungsanordnung sowie ein Verfahren zum Erzeugen und Verstärken eines in seiner Amplitude begrenzten Gleichspannungssignals, dessen Pegelspannung im wesentlichen proportional zum Logarithmus der Spannungsamplitude eines Eingengssignals ist; allgemeiner bezieht sich die vorliegende Erfindung auf das Gebiet der analogen integrierten Schaltungen.

[0002] Derartige Schaltungsanordnungen sowie derartige Verfahren erfüllen eine zweifache Funktion: Zum einen dienen sie der Verstärkung eines Wechselspannungssignals, das der Schaltungsanordnung über deren Eingangsanschlüsse zugeführt wird; gleichzeitig wird durch eine derartige Schaltungsanordnung sowie durch ein derartiges Verfahren die Amplitude des Ausgangssignals begrenzt. Demzufolge ist für eine derartige Schaltungsanordnung auch der Begriff "Begrenzerverstärker" geläufig; solche Begrenzerverstärker kommen beispielsweise bei der frequenzmodulierten ZF-Verstärkung in Radioempfängern oder auch bei der Trägergewinnung aus amplitudenmodulierten Signalen zum Einsatz

[0003] Wird nun bei einem derartigen Begrenzerverstärker eine einfache Erweiterung, beispielsweise in Form einer Gleichrichterstufe, vorgenommen, so läßt sich eine Gleichspannung erzeugen, die in weiten Bereichen proportional zum Logarithmus der Amplitude der Spannung des Eingangssignals ist; trägt man mithin die Amplitude des Ausgangssignals gegen den Logarithmus der Amplitude der Eingangsspannung auf, so ergibt sich über weite Bereiche der Eingangsspannung eine Gerade mit im wesentlichen konstanter Steigung; diese Gerade wird gemeinhin als "Pegelkennlinie" bezeichnet.

[0004] In bezug auf derartige Schaltungsanordnungen sowie auf derartige Verfahren zum Erzeugen und Verstärken eines in seiner Amplitude begrenzten Gleichspannungssignals ist nun zu berücksichtigen, dass die Pegelspannung des Gleichspannungssignals bei frequenzmoduliertem Eingangssignal (sogenanntem "FM-moduliertem Eingangssignal") dann verfälscht wird, wenn das Eingangssignal zuvor eine Schaltung mit frequenzabhängigem Amplitudengang, beispielsweise in Form eines Zwischenfrequenzfilters, durchlaufen hat. In einer solchen Schaltung erfolgt eine Umwandlung von Frequenzmodulation (FM) in Amplitudenmodulation (AM), die sich dann in der Pegelspannung des Gleichspannungssignals unweigerlich als unerwünschte Pegelschwankung auswirkt, obwohl das Eingangssignal im Grunde genommen lediglich frequenzmoduliert (FM) war.

[0005] Ausgehend von den vorstehend dargelegten Nachteilen und Unzulänglichkeiten liegt der vorliegenden Erfindung die Aufgabe zugrunde, eine Schaltungsanordnung sowie ein Verfahren der eingangs genannten Art zur Verfügung zu stellen, durch die die Pegelan-

zeige, das heißt die Pegelspannung des in der Schaltungsanordnung sowie mittels des Verfahrens erzeugten und verstärkten Gleichspannungssignals nur von der Amplitude, nicht jedoch von der Frequenz des Eingangssignals abhängt.

[0006] Diese Aufgabe wird durch eine Schaltungsanordnung mit den im Anspruch 1 angegebenen Merkmalen sowie durch ein Verfahren mit den im Anspruch 17 angegebenen Merkmalen gelöst. Vorteilhafte Ausgestaltungen und zweckmäßige Weiterbildungen der vorliegenden Erfindung sind in den jeweiligen Unteransprüchen gekennzeichnet.

[0007] Gemäß der Lehre der vorliegenden Erfindung erfolgt mithin eine Korrektur des Pegelsignals mittels eines aus der Frequenz-(FM-)Demodulatoreinheit gewonnenen Korrektursignals dergestalt, dass der Einfluß des frequenzabhängigen Amplitudengangs auf das Pegelsignal kompensiert wird; dies bedeutet mit anderen Worten, dass das durch die vorliegende Erfindung erzeugte und verstärkte, in seiner Amplitude begrenzte Gleichspannungssignal, dessen Pegelspannung im wesentlichen proportional zum Logarithmus der Spannungsamplitude eines Eingangssignals ist, nur noch Informationen über die Amplitude, nicht jedoch über die Frequenz enthält.

[0008] Der Fachmann wird in diesem Zusammenhang mithin insbesondere zu schätzen wissen, dass durch die vorliegende Erfindung eine korrigierende Kompensation des Einflusses der Frequenzmodulation auf die (logarithmische) Pegelanzeigespannung erfolgt; eine derartige Kompensation wird dadurch erforderlich, dass frequenzmodulierte Signale nach Durchlaufen einer Filterstufe zuvor nicht vorhandene Amplitudenschwankungen aufweisen, denn die Filterstufe hat eine frequenzabhängige Durchlaßdämpfung. Durch die vorliegende Erfindung ist es auf für den Fachmann überraschende Weise möglich, dass die Aussagen der Pegelspannung über den Signalpegel erheblich genauer werden, so dass sich völlig neue Anwendungen für die Schaltungsanordnung erschließen.

[0009] Der Kern der vorliegenden Erfindung ist darin zu sehen, dass zunächst die Pegelinformation des Eingangssignals mittels der mindestens einen Verstärkerschaltung mit den mindestens zwei Verstärkungsstufen angezeigt und/oder erfaßt wird. Nachdem das Ausgangssignal der letzten Verstärkungsstufe, insbesondere der Kollektorschaltungen der letzten Verstärkungsstufe, mittels der mindestens einen Frequenz-(FM-)Demodulatoreinheit frequenzdemoduliert ist, erfolgt in der mindestens einen Quadriererstufe ein Korrigieren des Ausgangssignals der Frequenz-(FM-)Demodulatoreinheit, insbesondere des Wechselspannungsanteils des Ausgangssignals der Freguenz-(FM-)Demodulatoreinheit. Schließlich wird in mindestens einer Stromaddierereinheit die Pegelspannung des Ausgangssignals der Quadriererstufe mit der Pegelspannung der Verstärkungsstufen addiert.

[0010] Gemäß einer bevorzugten Ausgestaltungs-

20

form der vorliegenden Erfindung wird die Quadrierestufe durch mindestens eine insbesondere nicht-gegengekoppelte Differenzverstärkerstufe, durch mindestens eine der Differenzverstärkerstufe zugeordnete Zwischenstufe sowie durch mindestens eine nachgeschaltete Multipliziererstufe zum Multiplizieren des Ausgangssignals der Zwischenstufe gebildet. Dieses Multiplikationsprodukt wird in der mindestens einen Stromaddierereinheit zu den Pegelkennlinienanteilen der Verstärkungsstufen addiert.

[0011] In diesem Zusammenhang kann die Pegelspannung des Ausgangssignals der Quadriererstufe jeweils an verschiedene der Verstärkerschaltung vorgeschaltete Schaltungen mit frequenzabhängigem Amplitudengang, beispielsweise an Zwischenfrequenzfilter mit jeweils verschieden gekrümmten Filterdurchlaßkurven, angepaßt werden, indem die Verstärkung der Quadriererstufe variiert wird.

[0012] Die Differenzverstärkerstufe ist zweckmäßigerweise an den Ausgang der Frequenzdemodulatorstufe geschaltet; prinzipiell handelt es sich in diesem Zusammenhang bei einem Differenzverstärker um einen linear verstärkenden Gleichspannungsverstärker, dessen Ausgangsspannung zur Differenz der beiden Eingangsspannungen proportional ist; die Grundschaltung weist zwei am Emitteranschluß zusammengeschaltete Transistoren auf, die aus einer gemeinsamen Konstantstromquelle gespeist werden; der Differenzverstärker ist im Regelfall symmetrisch aufgebaut, weil sich dann Temperatureinflüsse und Nichtlinearitäten weitestgehend kompensieren, woraus ein geringes Offsetverhalten resultiert.

[0013] In bezug auf die vorliegende Erfindung ist zu berücksichtigen, dass zwar aus dem Stand der Technik eine Möglichkeit bekannt ist, den Fehler in einer Frequenz-(FM-)Demodulatoreinheit, der durch die Gruppenlaufzeit eines vor der Frequenz-(FM-)Demodulatoreinheit angeordneten Filters verursacht wird, zu kompensieren (vgl. Druckschrift JP 61-187402); ferner ist im Stand der Technik neben verschiedenen Typen von Frequenz-(FM-) Demodulatoreinheiten (vgl. etwa die Druckschriften DE-OS 17 66 837, JP-A-04-207209, JP-A-11-055038, JP-A-57-015505 oder auch JP-A-60-070804) auch das Filtern des Ausgangssignals eines Begrenzerverstärkers vor einer Frequenz-(FM-) Demodulatoreinheit zum Vermeiden von Verzerrungen offenbart (vgl. JP-A-55-083347).

[0014] Allerdings behandelt keines der vorgenannten Dokumente aus dem Stand der Technik die Frage der Erfassung nicht nur der Amplitude, sondern - infolge der frequenzabhängigen Transfercharakteristik - auch der Frequenz des Eingangssignals; dies bedeutet mit anderen Worten, dass die Dokumente aus dem Stand der Technik keinerlei Anregungen in bezug auf die Reduzierung des unerwünschten Einflusses des frequenzabhängigen Amplitudengangs liefern.

[0015] Die Erfindung betrifft schließlich auch eine integrierte Schaltung, insbesondere eine analoge inte-

grierte Schaltung, aufweisend mindestens eine Schaltungsanordnung der vorstehend beschriebenen Art und/oder arbeitend gemäß einem Verfahren der vorstehend beschriebenen Art.

[0016] Ein Ausführungsbeispiel der vorliegenden Erfindung wird nachstehend anhand der Zeichnungen näher erläutert.

Es zeigt:

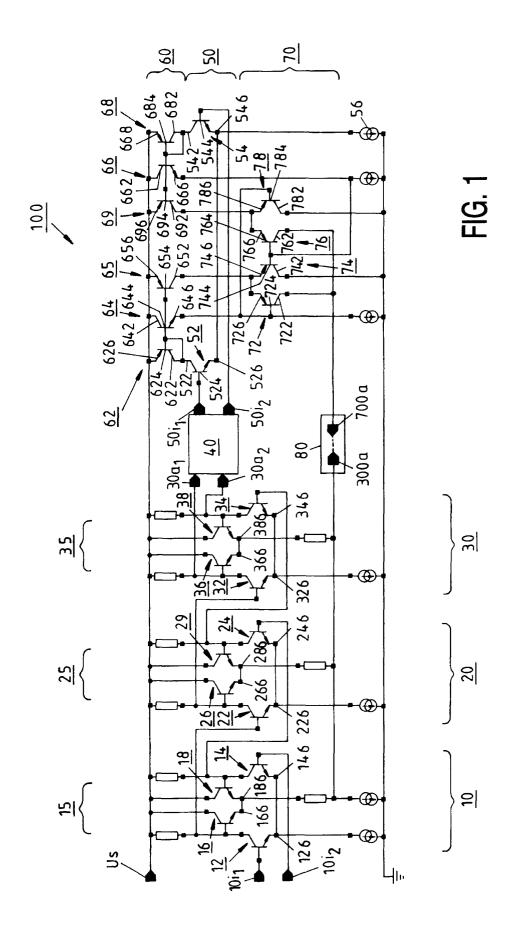

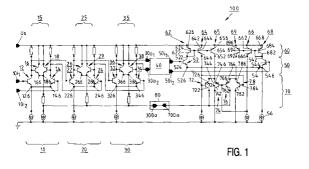

Fig. 1 ein Ausführungsbeispiel einer Schaltungsanordnung gemäß der vorliegenden Erfindung, in schematischer Prinzipdarstellung;

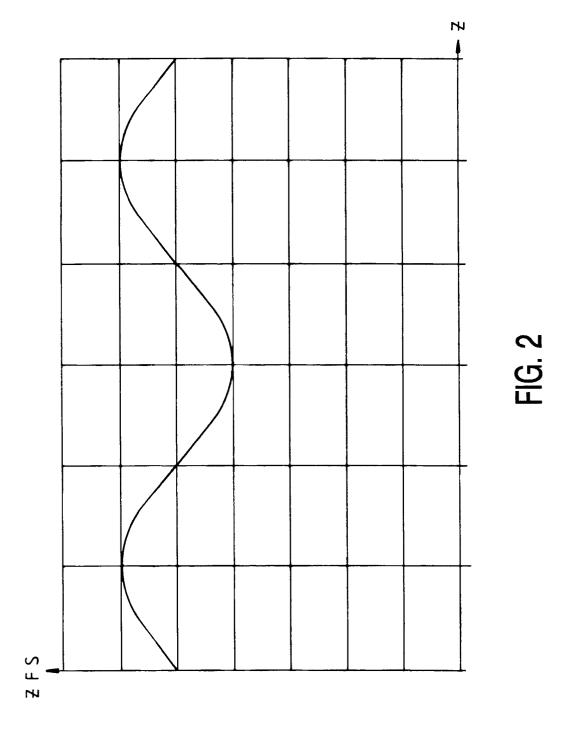

Fig. 2 ein Diagramm, in dem die Momentanfrequenz eines Zwischenfrequenzsignals gegen die Zeit Z aufgetragen ist;

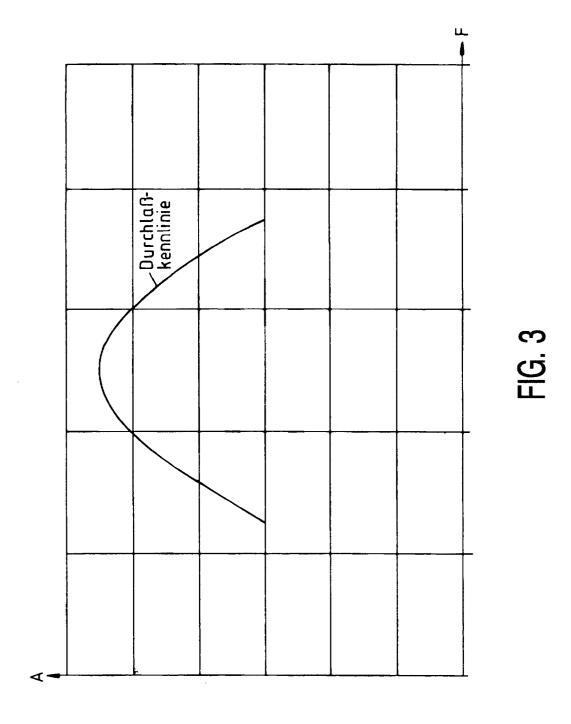

Fig. 3 ein Diagramm, in dem die in bezug auf die Amplitude gewölbte Durchlaßkennlinie eines integrierten Filters gegen die Frequenz F aufgetragen ist:

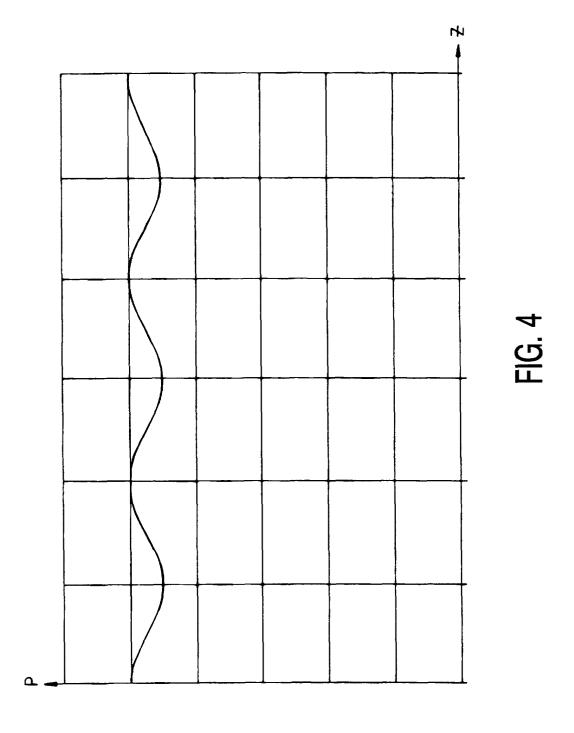

Fig 4 ein Diagramm, in dem die von der im integrierten Filter (vgl. Fig. 3) entstehenden Pegelschwankung überlagerte Pegelspannung oder "Pegelinformation" gegen die Zeit Z aufgetragen ist;

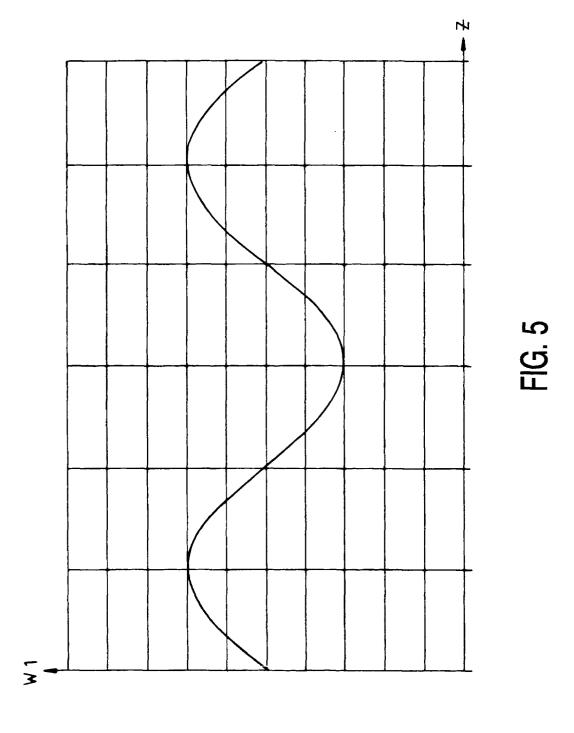

Fig. 5 ein Diagramm, in dem der Wechselspannungsanteil des Ausgangssignals der Frequenz-(FM-)Demodulatoreinheit gegen die Zeit aufgetragen ist;

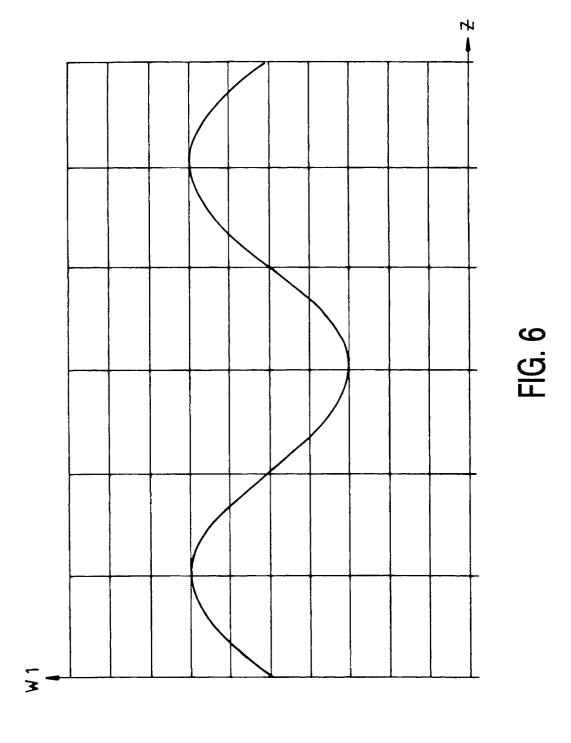

Fig 6 ein Diagramm, in dem der in der Korrekturschaltung quadrierte Wechselspannungsanteil des Ausgangssignals der Frequenz-(FM-)Demodulatoreinheit (vgl. Fig. 5) gegen die Zeit aufgetragen ist; und

Fig. 7 ein Diagramm, in dem die korrigierte Pegelspannung, das heißt das zum Pegelsignal der Verstärkerschaltung addierte Korrektursignal der Quadriererstufe gegen die Zeit aufgetragen ist.

[0017] Im integrierten Schaltkreis eines frequenzmodulierten (FM) Radioempfängers wird das Zwischenfrequenzsignal (Frequenz des Zwischenfrequenzsignals ZFS) (vgl. Figur 2) durch ein integriertes Filter mit gewölbter Durchlaßkennlinie (vgl. Figur 3) geschickt, bevor es über die beiden Eingangsanschlüsse 10i1 und 10i2 in die anhand Figur 1 exemplarisch veranschaulichte Schaltungsanordnung 100 gelangt, die aus diesem Signal die Pegelinformation gewinnt und ein in seiner Amplitude A begrenztes Gleichspannungssignal erzeugt und verstärkt, dessen an einer Stromaddierereinheit 80 (vgl. Figur 1) gemessene Pegelspannung im wesentlichen proportional zum Logarithmus der Spannungsamplitude des Signals ist.

[0018] Hierzu weist die Schaltungsanordnung 100 ei-

ne Verstärkerschaltung mit drei Verstärkungsstufen 10 bzw. 20 bzw. 30 auf. Jede dieser drei Verstärkungsstufen 10 bzw. 20 bzw. 30 wiederum weist zwei npn-Transistoren 12, 14 bzw. 22, 24 bzw. 32, 34 auf, deren jeweilige Emitteranschlüsse 126, 146 bzw. 226, 246 bzw. 326, 346 zusammengeschaltet sind.

[0019] Um nun eine Gleichspannung zu erzeugen, die in weiten Bereichen proportional zum Logarithmus der Amplitude der Spannung der über den ersten Eingangsanschluß 10i1 der ersten Verstärkungsstufe 10 sowie über den zweiten Eingangsanschluß 10i2 der ersten Verstärkungsstufe 10 zugeführten Eingangssignale ist, ist innerhalb jeder der Verstärkungsstufen 10 bzw. 20 bzw. 30 mindestens eine Gleichrichterstufe 15 bzw. 25 bzw. 35 vorgesehen; jede dieser Gleichrichterstufen 15 bzw. 25 bzw. 35 wiederum weist zwei npn-Transistoren 16, 18 bzw. 26, 28 bzw. 36, 38 auf, deren jeweilige Emitteranschlüsse 166, 186 bzw. 266, 286 bzw. 366, 386 zusammengeschaltet sind.

[0020] Da nun die in der Verstärkerschaltung gewonnene Pegelinformation von der im integrierten Filter (vgl. Figur 3) entstehenden Pegelschwankung überlagert ist (Pegelspannung mit überlagerter Pegelschwankung P) (vgl. Figur 4), wird zum Kompensieren dieses Fehlers der Wechselspannungsanteil des Ausgangssignals (Wechselspannungsanteil des Ausgangssignals der Freqenz-(FM)Demodulatoreinheit W1) (vgl. Figur 5) der Frequenz-(FM-)Demodulatoreinheit 40 in der als Korrekturschaltung fungierenden Quadriererstufe 50, 60, 70 quadriert (quadrierter Wechselspannungsanteil des Ausgangssignals der Frequenz-(FM)Demodulatoreinheit W2) (vgl. Figur 6) und als Korrektursignal zum Pegelsignal der Verstärkerschaltung addiert (korrigierte Regelspannung KP) (vgl. Figur 7).

[0021] Hierzu ist parallel an den Ausgang des Frequenzdemodulators 40, dessen Eingang mit dem Ausgang der letzten Verstärkungsstufe 30 verbunden ist, eine nicht-gegengekoppelte Differenzverstärkerstufe 50 geschaltet; im speziellen ist jeweils ein Ausgangsanschluß 30o1 bzw. 30o2 der letzten Verstärkungsstufe 30 über die Frequenz-(FM-)Demodulatoreinheit 40 mit der jeweiligen Basis 524 bzw. 544 zweier npn-Transistoren 52 bzw. 54 verbunden. Diese Differenzverstärkerstufe 50 ist an eine Stromquelle 56 angeschlossen, wobei die jeweiligen Emitteranschlüsse 526 bzw. 546 der beiden npn-Transistoren 52 bzw. 54 zusammengeschaltet und an die Stromquelle 56 angeschlossen sind.

[0022] Wie des weiteren aus Figur 1 hervorgeht, ist der Differenzverstärkerstufe 50 eine Zwischenstufe 60 zugeordnet, indem die Kollektoren 522 bzw. 542 der npn-Transistoren 52 bzw. 54 mit der Zwischenstufe 60 verbunden sind. Die Zwischenstufe 60 weist vier Transistoren 62 bzw. 64 und 66 bzw. 68, nämlich zwei pnp-Transistoren 62, 68 und zwei npn-Transistoren 64, 66, auf, die zumindest partiell an eine Versorgungsspannung Us angeschlossen sind. Des weiteren sind der Zwischenstufe 60 noch zwei pnp-Transistoren 65, 69 zugeordnet.

[0023] Der Differenzverstärkerstufe 50 und der Zwischenstufe 60 ist eine Multipliziererstufe 70 zum Multiplizieren der Ausgangssignale der Zwischenstufe 60 (vgl. Übergang von Figur 5 auf Figur 6) nachgeschaltet. Dieses multiplizierte Ausgangssignal - genauer dessen Pegelspannung - wird dann in der Stromaddierereinheit 80 zur jeweiligen Pegelspannung der Verstärkungsstufen 10, 20, 30 addiert.

[0024] Im speziellen weist diese Multipliziererstufe 70 vier pnp-Transistoren 72 bzw. 74 und 76 bzw. 78 auf. Hierbei sind der Kollektor 742 des zweiten pnp-Transistors 74 sowie der Kollektor 782 des vierten pnp-Transistors 78 an ein Referenzpotential, nämlich an das Erdpotential angeschlossen, wohingegen der Kollektor 722 des ersten pnp-Transistors 72 sowie der Kollektor 762 des dritten pnp-Transistors 76 mit dem Ausgangsanschluß 700o der Quadriererstufe 50, 60, 70 verbunden sind. Des weiteren sind die Basis 724 des ersten pnp-Transistors 72 sowie die Basis 784 des vierten pnp-Transistors 78 mit dem Emitter 646 des zweiten Transistors 64 der Zwischenstufe 60 verbunden, wohingegen die Basis 744 des zweiten pnp-Transistors 74 sowie die Basis 764 des dritten pnp-Transistors 76 ebenso wie die jeweiligen Emitter 726 bzw. 746 sowie 766 bzw. 786 miteinander verbunden sind.

[0025] Durch die anhand Figur 1 exemplarisch veranschaulichte Schaltungsanordnung 100 wird bewirkt, dass die Pegelanzeige, das heißt die Pegelspannung des in der Schaltungsanordnung 100 sowie mittels des Verfahrens erzeugten und verstärkten Gleichspannungssignals nur von der Amplitude, nicht jedoch von der Frequenz des Eingangssignals abhängt.

### BEZUGSZEICHENLISTE

Schaltungsanordnung

#### [0026]

100

|    | •                     |                                               |  |  |

|----|-----------------------|-----------------------------------------------|--|--|

|    | 10                    | erste Verstärkungsstufe                       |  |  |

| 40 | 10i1                  | erster Eingangsanschluß der ersten Verstär-   |  |  |

|    |                       | kungsstufe 10                                 |  |  |

|    | 10i2                  | zweiter Eingangsanschluß der ersten Verstär-  |  |  |

|    |                       | kungsstufe 10                                 |  |  |

|    | 12                    | erster Transistor, insbesondere erster npn-   |  |  |

| 45 |                       | Transistor, der ersten Verstärkungsstufe 10   |  |  |

|    | 126                   | Emitter des ersten Transistors 12 der ersten  |  |  |

|    |                       | Verstärkungsstufe 10                          |  |  |

|    | 14                    | zweiter Transistor, insbesondere zweiter npn- |  |  |

|    |                       | Transistor, der ersten Verstärkungsstufe 10   |  |  |

| 50 | 146                   | Emitter des zweiten Transistors 14 der ersten |  |  |

|    |                       | Verstärkungsstufe 10                          |  |  |

|    | 15                    | erste Gleichrichterstufe                      |  |  |

|    | 16                    | erster Transistor, insbesondere erster npn-   |  |  |

|    |                       | Transistor, der ersten Gleichrichterstufe 15  |  |  |

| 55 | 166                   | Emitter des ersten Transistors 16 der ersten  |  |  |

|    | Gleichrichterstufe 15 |                                               |  |  |

|    | 18                    | zweiter Transistor, insbesondere zweiter npn- |  |  |

|    | -                     |                                               |  |  |

Transistor, der ersten Gleichrichterstufe 15

| 186  | Emitter des zweiten Transistors 18 der ersten     |    |     | verstärkerstufe 50                              |

|------|---------------------------------------------------|----|-----|-------------------------------------------------|

|      | Gleichrichterstufe 15                             |    | 54  | zweiter Transistor, insbesondere zweiter npn-   |

| 20   | zweite Verstärkungsstufe                          |    |     | Transistor, der Differenzverstärkerstufe 50     |

| 22   | erster Transistor, insbesondere erster npn-       |    | 542 | Kollektor des zweiten Transistors 54 der Diffe- |

|      | Transistor, der zweiten Verstärkungsstufe 20      | 5  |     | renzverstärkerstufe 50                          |

| 226  | Emitter des ersten Transistors 22 der zweiten     |    | 544 | Basis des zweiten Transistors 54 der Differenz- |

|      | Verstärkungsstufe 20                              |    |     | verstärkerstufe 50                              |

| 24   | zweiter Transistor, insbesondere zweiter npn-     |    | 546 | Emitter des zweiten Transistors 54 der Diffe-   |

|      | Transistor, der zweiten Verstärkungsstufe 20      |    |     | renzverstärkerstufe 50                          |

| 246  | Emitter des zweiten Transistors 24 der zweiten    | 10 | 56  | Stromquelle                                     |

|      | Verstärkungsstufe 20                              |    | 60  | Zwischenstufe                                   |

| 25   | zweite Gleichrichterstufe                         |    | 62  | erster Transistor, insbesondere erster pnp-     |

| 26   | erster Transistor, insbesondere erster npn-       |    | 02  | Transistor, der Zwischenstufe 60                |

| 20   | Transistor, der zweiten Gleichrichterstufe 25     |    | 622 | Kollektor des ersten Transistors 62 der Zwi-    |

| 266  | Emitter des ersten Transistors 26 der zweiten     | 15 | 022 | schenstufe 60                                   |

| 200  | Gleichrichterstufe 25                             | 10 | 624 | Basis des ersten Transistors 62 der Zwischen-   |

| 20   |                                                   |    | 024 |                                                 |

| 28   | zweiter Transistor, insbesondere zweiter npn-     |    | 000 | stufe 60                                        |

| 000  | Transistor, der zweiten Gleichrichterstufe 25     |    | 626 | Emitter des ersten Transistors 62 der Zwi-      |

| 286  | Emitter des zweiten Transistors 28 der zweiten    |    | 0.4 | schenstufe 60                                   |

|      | Gleichrichterstufe 25                             | 20 | 64  | zweiter Transistor, insbesondere erster npn-    |

| 30   | dritte Verstärkungsstufe = letzte Verstärkungs-   |    |     | Transistor, der Zwischenstufe 60                |

|      | stufe                                             |    | 642 | Kollektor des zweiten Transistors 64 der Zwi-   |

| 30o1 | erster Ausgangsanschluß der letzten Verstär-      |    |     | schenstufe 60                                   |

|      | kungsstufe 30                                     |    | 644 | Basis des zweiten Transistos 64 der Zwischen-   |

| 30o2 | zweiter Ausgangsanschluß der letzten Verstär-     | 25 |     | stufe 60                                        |

|      | kungsstufe 30                                     |    | 646 | Emitter des zweiten Transistors 64 der Zwi-     |

| 300o | Ausgangsanschluß der Verstärkerschaltung          |    |     | schenstufe 60                                   |

| 32   | erster Transistor, insbesondere erster npn-       |    | 65  | erster der Zwischenstufe 60 zugeordneter        |

|      | Transistor, der letzten Verstärkungsstufe 30      |    |     | Transistor, insbesondere pnp-Transistor         |

| 326  | Emitter des ersten Transistors 32 der letzten     | 30 | 652 | Kollektor des ersten zugeordneten Transistors   |

|      | Verstärkungsstufe 30                              |    |     | 65                                              |

| 34   | zweiter Transistor, insbesondere zweiter npn-     |    | 654 | Basis des ersten zugeordneten Transistors 65    |

|      | Transistor, der letzten Verstärkungsstufe 30      |    | 656 | Emitter des ersten zugeordneten Transistors     |

| 346  | Emitter des zweiten Transistors 34 der letzten    |    |     | 65                                              |

|      | Verstärkungsstufe 30                              | 35 | 66  | dritter Transistor, insbesondere zweiter npn-   |

| 35   | dritte Gleichrichterstufe = letzte Gleichrichter- |    |     | Transistor, der Zwischenstufe 60                |

|      | stufe                                             |    | 662 | Kollektor des dritten Transistors 66 der Zwi-   |

| 36   | erster Transistor, insbesondere erster npn-       |    | 002 | schenstufe 60                                   |

| 00   | Transistor, der letzten Gleichrichterstufe 35     |    | 664 | Basis des dritten Transistors 66 der Zwischen-  |

| 366  | Emitter des ersten Transistors 36 der letzten     | 40 | 004 | stufe 60                                        |

| 300  | Gleichrichterstufe 35                             | 40 | 666 | Emitter des dritten Transistors 66 der Zwi-     |

| 38   | zweiter Transistor, insbesondere zweiter npn-     |    | 000 | schenstufe 60                                   |

| 30   | •                                                 |    | 00  |                                                 |

| 200  | Transistor, der letzten Gleichrichterstufe 35     |    | 68  | vierter Transistor, insbesondere zweiter pnp-   |

| 386  | Emitter des zweiten Transistors 38 der letzten    |    | 000 | Transistor, der Zwischenstufe 60                |

|      | Gleichrichterstufe 35                             | 45 | 682 | Kollektor des vierten Transistors 68 der Zwi-   |

| 40   | Frequenz-(FM-)Demodulatoreinheit                  |    |     | schenstufe 60                                   |

| 50   | Differenzverstärkerstufe                          |    | 684 | Basis des vierten Transistors 68 der Zwischen-  |

| 50i1 | erster Eingangsanschluß der Differenzverstär-     |    |     | stufe 60                                        |

|      | kerstufe 50                                       |    | 686 | Emitter des vierten Transistors 68 der Zwi-     |

| 50i2 | zweiter Eingangsanschluß der Differenzver-        | 50 |     | schenstufe 60                                   |

|      | stärkerstufe 50                                   |    | 69  | zweiter der Zwischenstufe 60 zugeordneter       |

| 52   | erster Transistor, insbesondere erster npn-       |    |     | Transistor, insbesondere pnp-Transistor         |

|      | Transistor, der Differenzverstärkerstufe 50       |    | 692 | Kollektor des zweiten zugeordneten Transi-      |

| 522  | Kollektor des ersten Transistors 52 der Diffe-    |    |     | stors 69                                        |

|      | renzverstärkerstufe 50                            | 55 | 694 | Basis des zweiten zugeordneten Transistors      |

| 524  | Basis des ersten Transistors 52 der Differenz-    |    |     | 69                                              |

|      | verstärkerstufe 50                                |    | 696 | Emitter des zweiten zugeordneten Transistors    |

| 526  | Emitter des ersten Transistors 52 der Differenz-  |    |     | 69                                              |

10

20

70 Multipliziererstufe 700o Ausgangsanschluß der Multipliziererstufe 70 72 erster Transistor, insbesondere erster pnp-Transistor, der Multipliziererstufe 70 Kollektor des ersten Transistors 72 der Multi-722 pliziererstufe 70 724 Basis des ersten Transistors 72 der Multipliziererstufe 70 726 Emitter des ersten Transistors 72 der Multipliziererstufe 70 74 zweiter Transistor, insbesondere zweiter pnp-Transistor, der Multipliziererstufe 70 742 Kollektor des zweiten Transistors 74 der Multipliziererstufe 70 744 Basis des zweiten Transistors 74 der Multipliziererstufe 70 746 Emitter des zweiten Transistors 74 der Multipliziererstufe 70 76 dritter Transistor, insbesondere dritter pnp-Transistor, der Multipliziererstufe 70 762 Kollektor des dritten Transistors 76 der Multipliziererstufe 70 764 Basis des dritten Transistors 76 der Multipliziererstufe 70 766 Emitter des dritten Transistors 76 der Multipli- 25 ziererstufe 70 78 vierter Transistor, insbesondere vierter pnp-Transistor, der Multipliziererstufe 70 782 Kollektor des vierten Transistors 78 der Multipliziererstufe 70 Basis des vierten Transistors 78 der Multipli-784 ziererstufe 70 786 Emitter des vierten Transistors 78 der Multipliziererstufe 70 80 Stromaddierereinheit

### **Patentansprüche**

Us

1. Schaltungsanordnung (100) zum Erzeugen und Verstärken eines in seiner Amplitude begrenzten Gleichspannungssignals, dessen Pegelspannung im wesentlichen proportional zum Logarithmus der Spannungsamplitude eines Eingangssignals ist, dadurch gekennzeichnet,

Versorgungsspannung

- dass der letzten Verstärkungsstufe (30), insbesondere den Kollektorschaltungen der letzten Verstärkungsstufe (30) einer mindestens zwei Verstärkungsstufen (10; 20; 30) aufweisenden Verstärkerschaltung eine Frequenz-(FM-)Demodulatoreinheit (40) nachgeschaltet ist,

- dass der Frequenz-(FM-)Demodulatoreinheit (40) mindestens eine Quadriererstufe (50, 60, 70) zum Quadrieren des Ausgangssignals der Frequenz-(FM-)Demodulatoreinheit (40), insbesondere des Wechselspannungsanteils des

- Ausgangssignals der Frequenz-(FM-)Demodulatoreinheit (40), nachgeschaltet ist und

- dass mindestens eine Stromaddierereinheit (80) zum Addieren der Pegelspannung des Ausgangssignals der Quadriererstufe (50, 60, 70) mit der Pegelspannung der Verstärkungsstufen (10; 20; 30) vorgesehen ist.

- Schaltungsanordnung (100) gemäß Anspruch 1, dadurch gekennzeichnet,

dass unter Bildung der Quadriererstufe (50, 60, 70)

- mindestens eine gegengekoppelte oder nichtgegengekoppelte Differenzverstärkerstufe (50) an den Ausgang eines Frequenzdemodulators (40) geschaltet ist,

- dass der Differenzvestärkerstufe (50) mindestens eine Zwischenstufe (60) zugeordnet ist

- dass der Differenzverstärkerstufe (50) und der Zwischenstufe (60) mindestens eine Multipliziererstufe (70) zum Multiplizieren des Ausgangssignals der Zwischenstufe (60) nachgeschaltet ist.

- Schaltungsanordnung (100) gemäß Anspruch 2, dadurch gekennzeichnet,

dass die Zwischenstufe (60) mindestens eine Stromspegeleinheit aufweist.

4. Schaltungsanordnung (100) gemäß Anspruch 2

#### dadurch gekennzeichnet,

dass die Differenzverstärkerstufe (50) an mindestens eine Stromquelle (56) angeschlossen ist.

5. Schaltungsanordnung (100) gemäß Anspruch 4, dadurch gekennzeichnet,

dass die Kennlinie der Pegelspannung der Schaltungsanordnung (100)

- durch Erhöhen der von der Stromquelle (56) zur Verfügung gestellten Stromstärke und/oder

- durch Zwischenschalten hochohmiger Widerstände

zu kleineren Pegelspannungen der Schaltungsanordnung (100) hin verlängerbar ist.

6. Schaltungsanordnung (100) gemäß mindestens einem der Ansprüche 2 bis 5,

### dadurch gekennzeichnet,

dass die Differenzverstärkerstufe (50) mindestens zwei Transistoren (52, 54), insbesondere npn-Transistoren, aufweist.

7. Schaltungsanordnung (100) gemäß Anspruch 6, dadurch gekennzeichnet,

6

40

35

30

50

55

45

**dass** die Emitter (526, 546) der Transistoren (52, 54) miteinander verbunden sind und an die Stromquelle (56) angeschlossen sind.

Schaltungsanordnung (100) gemäß Anspruch 6 oder 7.

## dadurch gekennzeichnet,

dass jeweils ein Ausgangsanschluß (30o1 bzw. 30o2) der letzten Verstärkungsstufe (30) über die Frequenz-(FM-)Demodulatoreinheit (40) mit der jeweiligen Basis (524 bzw. 544) der Transistoren (52 bzw. 54) verbunden ist.

9. Schaltungsanordnung (100) gemäß mindestens einem der Ansprüche 6 bis 8,

### dadurch gekennzeichnet,

dass die Kollektoren (522 bzw. 542) der Transistoren (52 bzw. 54) mit der Zwischenstufe (60) verbunden sind.

**10.** Schaltungsanordnung (100) gemäß mindestens einem der Ansprüche 2 bis 9,

#### dadurch gekennzeichnet,

dass die Zwischenstufe (60) mindestens vier Transistoren (62 bzw. 64, 66 bzw. 68), insbesondere mindestens zwei pnp-Transistoren (62, 68) und mindestens zwei npn-Transistoren (64, 66), aufweist, die zumindest partiell an eine Versorgungsspannung (Us) angeschlossen sind.

**11.** Schaltungsanordnung (100) gemäß mindestens einem der Ansprüche 2 bis 10,

#### dadurch gekennzeichnet,

dass der Zwischenstufe (60) mindestens zwei Transistoren (65, 69), insbesondere mindestens 35 zwei pnp-Transistoren, zugeordnet sind.

**12.** Schaltungsanordnung (100) gemäß mindestens einem der Ansprüche 2 bis 11,

### dadurch gekennzeichnet,

dass die Multipliziererstufe (70) mindestens vier Transistoren (72 bzw. 74, 76 bzw. 78), insbesondere pnp-Transistoren, aufweist,

- deren jeweiliger Kollektor (742, 782) an ein Referenzpotential angsschlossen ist bzw. deren jeweiliger Kollektor (722, 762) mit dem Ausgangsanschluß (700o) der Quadriererstufe (50, 60, 70) verbunden ist,

- deren jeweilige Basis (724, 784) mit dem Emitter (646) des zweiten Transistors (64) der Zwischenstufe (60) verbunden ist bzw. deren jeweilige Basen (744, 764) miteinander verbunden sind und

- deren jeweilige Emitter (726 bzw. 746, 766 bzw.

786) miteinander verbunden sind.

- 13. Schaltungsanordnung (100) gemäß Anspruch 12,

#### dadurch gekennzeichnet,

dass das Referenzpotential das Erdpotential und/ oder das Massepotential ist.

**14.** Schaltungsanordnung (100) gemäß mindestens einem der Ansprüche 1 bis 13,

#### dadurch gekennzeichnet,

dass jede der Verstärkungsstufen (10; 20; 30) mindestens zwei Transistoren (12, 14; 22, 24; 32, 34), insbesondere mindestens zwei npn-Transistoren, aufweist, deren jeweilige Emitter (126, 146; 226, 246; 326, 346) miteinander verbunden sind.

**15.** Schaltungsanordnung (100) gemäß mindestens einem der Ansprüche 1 bis 14.

### dadurch gekennzeichnet,

dass innerhalb jeder der Verstärkungsstufen (10; 20; 30) mindestens eine Gleichrichterstufe (15; 25; 35) vorgesehen ist.

**16.** Schaltungsanordnung (100) gemäß Anspruch 15, dadurch gekennzeichnet,

dass jede der Gleichrichterstufen (15; 25; 35) mindestens zwei Transistoren (16, 18; 26, 28; 36, 38), insbesondere mindestens zwei npn-Transistoren, aufweist, deren jeweilige Emitter (166, 186; 266, 286; 366, 386) miteinander verbunden sind.

- 17. Integrierte Schaltung insbesondere analoge integrierte Schaltung, aufweisend mindestens eine Schaltungsanordnung (100) gemäß mindestens einem der Ansprüche 1 bis 16.

- 18. Verfahren zum Erzeugen und Verstärken eines in seiner Amplitude begrenzten Gleichspannungssignals, dessen Pegelspannung im wesentlichen proportional zum Logarithmus der Spannungsamplitude eines Eingangssignals ist,

gekennzeichnet durch die folgenden Schritte:

- Anzeigen und/oder Erfassen der Pegelinformation des Eingangssignals mittels mindestens einer Verstärkerschaltung mit mindestens einer Verstärkungsstufe (10; 20; 30);

- Demodulieren des Ausgangssignals der letzten Verstärkungsstufe (30), insbesondere der Kollektorschaltungen der letzten Verstärkungsstufe (30), mittels mindestens einer Frequenz-(FM-)Demodulatoreinheit (40);

- Quadrieren des Ausgangssignals der Frequenz-(FM-)Demodulatoreinheit (40), insbesondere des Wechselspannungsanteils des Ausgangssignals der Frequenz-(FM-) Demodulatoreinheit (40), mittels mindestens einer Quadriererstufe (50, 60, 70); und

- Addieren der Pegelspannung des Ausgangssignals der Quadriererstufe (50, 60, 70) mit der Pegelspannung der Verstärkungsstufen (10;

40

20

15

7

20; 30) mittels mindestens einer Stromaddierereinheit (80).

## 19. Verfahren gemäß Anspruch 18,

## dadurch gekennzeichnet,

dass die Pegelspannung des Ausgangssignals der Quadriererstufe (50, 60, 70) jeweils an verschiedene der Verstärkerschaltung vorgeschaltete Schaltungen mit frequenzabhängigem Amplitudengang, beispielsweise an Zwischenfrequenzfilter mit jeweils verschieden gekrümmten Filterdurchlaßkurven, angepaßt wird, indem die Verstärkung der Quadriererstufe (50, 60, 70) variiert wird.