(19)

Europäisches Patentamt

European Patent Office

Office européen des brevets

(11)

EP 1 231 748 A1

(12)

## EUROPÄISCHE PATENTANMELDUNG

(43) Veröffentlichungstag:

14.08.2002 Patentblatt 2002/33

(51) Int Cl. 7: H04L 25/06

(21) Anmeldenummer: 01103107.7

(22) Anmeldetag: 09.02.2001

(84) Benannte Vertragsstaaten:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU

MC NL PT SE TR

Benannte Erstreckungsstaaten:

AL LT LV MK RO SI

(71) Anmelder: SIEMENS AKTIENGESELLSCHAFT

80333 München (DE)

(72) Erfinder:

• Bock, Harald, Dr.

86150 Augsburg (DE)

• Faerbert, Andreas, Dr.

81827 München (DE)

• Peisl, Wolfgang, Dr.

81245 München (DE)

### (54) Verfahren und Anordnung zur Regelung der Entscheiderschwelle und der Abtasttaktphase eines Datenregenerators für ein binäres Signal

(57) Bei diesem Verfahren werden Fehlerkorrektursignale (K1, K0) für fehlerhafte 1-Bits und 0-Bits zur Regelung der Entscheiderschwelle (TH) einer Entschei-

derstufe (1) verwendet. Weitere Phasen-Korrektursignale (KBT, KAT) zwischen Übergängen von Binärsignalen dienen zur Phasenregelung eines Abtasttaktsignals (TS).

FIG 1

**Beschreibung**

[0001] Die Erfindung betrifft ein Verfahren zur Regelung der Entscheiderschwelle und/oder der Phase eines Abtasttaktsignals eines Datenregenerators für ein binäres Signal durch Auswertung von Fehlerkorrektursignalen.

5 [0002] Es sind zahlreiche Schaltungen bekannt, bei der die Entscheiderschwelle eines Datenregenerators und die Phase des Abtasttaktes auf Grund von Kriterien korrigiert werden, die aus dem empfangenen Signal gewonnen werden. Daneben gibt es eine weitere Gruppe von Datenregeneratoren, die bei einem redundanten Binärsignal die Fehlererkennung/Fehlerkorrektur zur Steuerung der Entscheiderschwelle und der Phasenlage nutzen.

10 [0003] Aus der Offenlegungsschrift DE 197 17 642 A1 ist ein Verfahren bekannt, bei dem die Entscheiderschwelle und die Phase mit Hilfe einer Steuerung variiert werden, bis die Fehlerrate ein Minimum erreicht. Bei diesem Verfahren pendeln die Phasenlage und die Schwelle stets um das Optimum herum.

15 [0004] Aus dem Patent US 4,360,926 ist eine digitale PLL (Phasenregeleinrichtung) bekannt, bei der sowohl ein Phasenvergleich zwischen dem empfangenen Signal und dem Abtasttakt durchgeführt wird, als auch zusätzlich Information des Fehlerdetektors zur Optimierung verwendet wird.

20 [0005] Aufgabe der Erfindung ist es, Verfahren zur Optimierung der Entscheiderschwelle und/oder der Phasenlage des Abtasttaktes anzugeben. Außerdem ist eine geeignete Anordnung anzugeben.

[0006] Diese Aufgabe wird durch die unabhängigen Ansprüche gelöst.

25 [0007] Sowohl die Entscheiderschwelle als auch die Abtastphase oder beides können durch Verwendung der Korrektursignale in Zusammenhang mit der Berücksichtigung des logischen Zustandes des binären Signals geregelt werden.

[0008] Ein Vorteil dieses Verfahrens ist es, dass es auch bei größeren Bitfehlerraten arbeitet.

30 [0009] Zur Regelung der Entscheiderschwelle wird die Differenz zwischen der Anzahl der korrigierten 1-Bits, das heißt, das korrigierte Bit wird eine binäre Null, und der Anzahl der korrigierten 0-Bits, hier erfolgt eine Korrektur in eine binäre Eins, verwendet. Es ist auch die Auswertung des Quotienten aus korrigierten 1-Bits zu 0-Bits (oder umgekehrt) möglich. Bei ungleichgewichtigen Codes sollte die Relation von binären Einsen zu binären Nullen berücksichtigt werden.

35 [0010] Die Korrektursignale werden ebenfalls zur Regelung der Phase eines Abtasttaktes verwendet. Hierzu wird überprüft, ob die Anzahl der Korrekturen vor oder nach einem Übergang zwischen zwei unterschiedlichen (korrigierten) Binärzuständen größer ist.

40 [0011] Eine entsprechende Anordnung ist rein digital realisierbar, so dass Probleme durch Temperaturabhängigkeit oder Alterung wie bei den herkömmlichen Taktregeneratoren vermieden werden.

[0012] Vorteilhaft ist auch eine Überwachung der Häufigkeit von Korrekturen, die bei gleichbleibenden Übertragungsbedingungen die Arbeitsweise der Regelung wiedergibt. Bei optimierter Abtastung ist die Häufigkeit von Korrekturen ein Kriterium für die Signalqualität, das außerdem zur Steuerung der Zeitkonstanten der Regeleinrichtungen verwendet werden.

[0013] Vorteilhaft ist auch eine Begrenzung der Variationsbreite der Entscheiderschwelle, damit die Betriebsfähigkeit immer gewährleistet ist.

[0014] Das erfindungsgemäße Verfahren kann auch mit den herkömmlichen analogen Verfahren, bei denen zur Phasenkorrektur das Empfangssignal mit dem Abtasttaktsignal verglichen wird, kombiniert werden.

45 [0015] Die Erfindung wird anhand eines Ausführungsbeispiels näher erläutert.

[0016] Es zeigen:

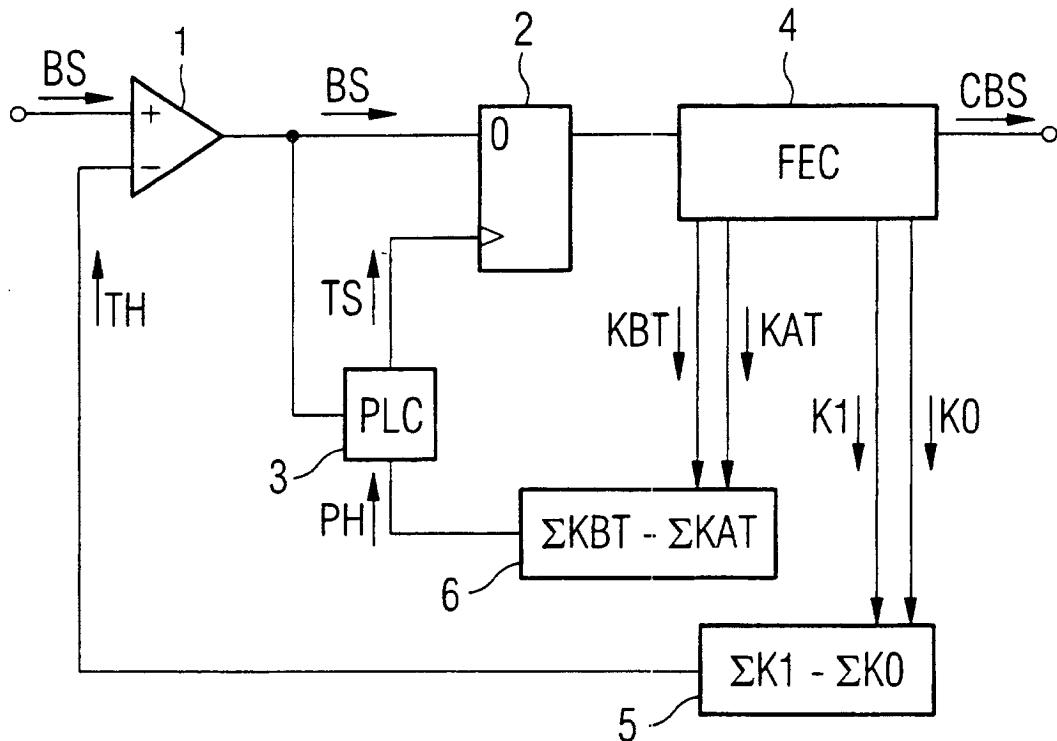

Figur 1 ein Prinzipschaltbild eines Datenregenerators,

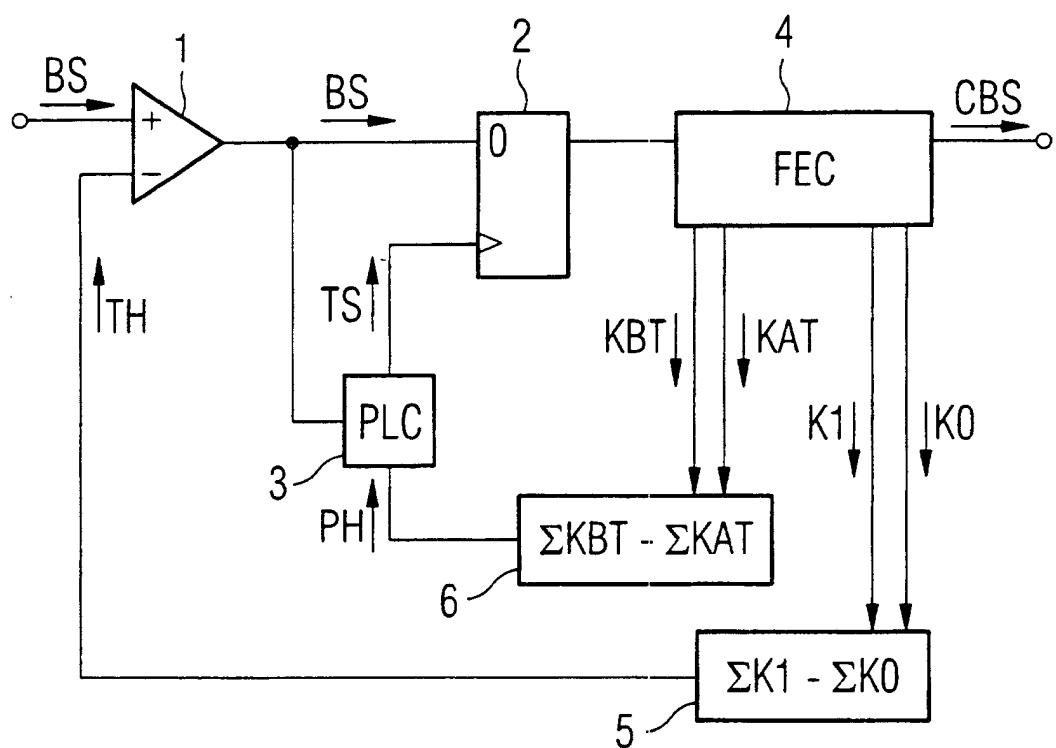

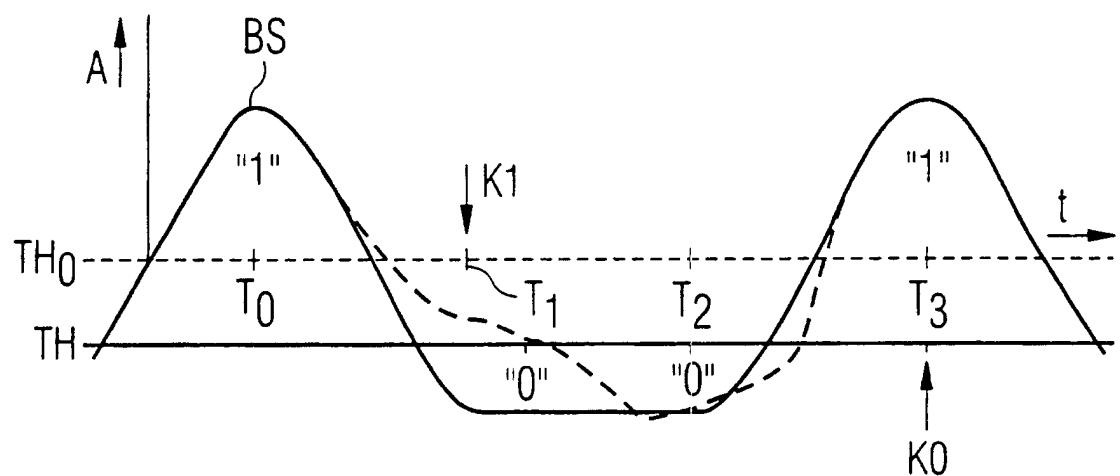

45 Figur 2 ein Zeitdiagramm zur Regelung der Entscheiderschwelle und

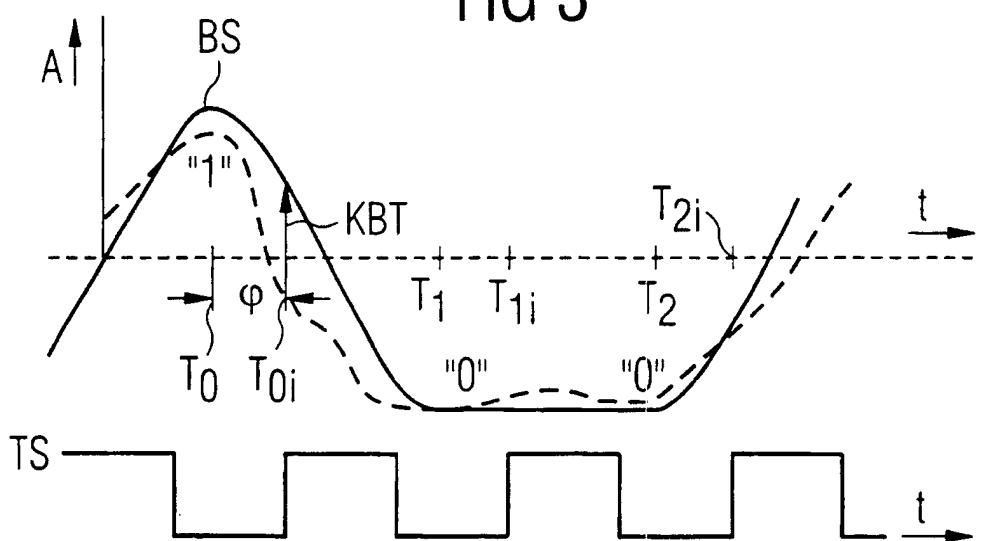

Figur 3 ein Zeitdiagramm zur Regelung der Phase des Abtasttaktes.

50 [0017] In **Figur 1** ist der erfindungsgemäße Datenregenerator 1 - 6 dargestellt. Einer Entscheiderstufe 1 wird das Signal BS zugeführt und mit einem Vergleichswert, der Entscheiderschwelle TH, verglichen. Das binäre Ausgangssignal der Entscheiderstufe 1 wird dem Dateneingang D einer Abtastkippstufe 2 zugeführt und dessen Datenbits werden im Idealfall jeweils in der Bitmitte mit einem Abtasttaktsignal TS abgetaktet (gespeichert), das von einem nicht dargestellten gesteuerten Oszillator (VCO) eines Taktregenerators 3 (z. B. eines Phasenregelkreises PLL) erzeugt wird. Vom Datenausgang der Abtastkippstufe 2 gelangt das binäre Signal zu einer Fehlerkorrekturseinrichtung (FEC) 4, die an ihrem Datenausgang ein korrigiertes Binärsignal CBS abgibt.

55 [0018] Die Fehlerkorrekturseinrichtung 4 erkennt auf Grund von redundanten Information, welche Bits des binären Signals gestört sind und korrigiert diese durch Invertieren. Die Korrektursignale werden hier mit dem Binärzustand des noch unkorrigierten Bits kombiniert (gleichwertig ist eine logische Verknüpfung mit dem Zustand des korrigierten Bits)

und als Korrektursignale K1 beziehungsweise K0 ausgegeben. K1 bedeutet, dass ein als Binärzustand "1" in der Abtastkippstufe 2 gespeichertes Bit in den Binärzustand "0" korrigiert wird; K0 bedeutet eine Korrektur des Binärzustandes "0" in den Binärzustand "1". Ein Entscheiderschwelle-Regler 5 bildet die Differenz zwischen den Summen der K1-Korrektursignale und K0-Korrektursignale  $\Sigma K1 - \Sigma K0$  und verschiebt entsprechend die Schwelle TH der Entscheiderstufe 1. Die Meßintervalle können der Bitfehlerrate angepaßt werden; auch kann bis zu einer bestimmten Anzahl von Korrekturvorgängen gezählt werden oder beide Methoden werden kombiniert.

[0019] Im Diagramm **Figur 2** ist der zeitliche Verlauf der Amplitude A eines ungestörte binären Signals BS als Funktion der Zeit t als durchgezogene Linie dargestellt, das empfangsseitig zu Zeitpunkten  $T_0, T_1, T_2, \dots$  abgetastet wird. Die Entscheiderschwelle (Abtastschwelle) TH liegt jedoch nicht bei ihrem Idealwert  $TH_0$  (gestrichelt), sondern wesentlich tiefer. Ein ideales Signal BS wird jetzt noch richtig abgetastet. Kommen jetzt aber Signalverzerrungen hinzu, dann ist bei einem gestörten Signal - gestrichelt dargestellt - eine Verfälschung der binären "0" in eine binäre "1" sehr leicht möglich, was durch einen Korrekturvorgang K1 wieder rückgängig gemacht wird. Überwiegen die Korrektursignale K1 gegenüber den weit weniger wahrscheinlichen Korrektursignalen K0, dann muss die Entscheiderschwelle TH in Richtung der optimalen Schwelle  $S_0$ , hier hin zu höheren Werten, verschoben werden. Unter der Voraussetzung, dass die binäre "1" den höheren Pegel aufweist, gilt für die Entscheiderschwelle TH:

$$(1) \quad \Sigma K1 > \Sigma K0 \Rightarrow TH \text{ höher}$$

$$(2) \quad \Sigma K1 < \Sigma K0 \Rightarrow TH \text{ niedriger}$$

[0020] Bei einem ungleichgewichtigen Code gilt entsprechend (einschließlich mathematischer Umformungen):

$$(3) \quad \frac{\Sigma K1}{N0} > \frac{\Sigma K0}{N1} \Rightarrow TH \text{ höher}$$

$$(4) \quad \frac{\Sigma K1}{N0} < \frac{\Sigma K0}{N1} \Rightarrow TH \text{ niedriger}$$

[0021] Ebenso können, wie einleitend erwähnt, die Quotienten der aufsummierten Korrektursignale mit dem Quotienten der Summe der binären Nullen N0 mit der Summe der binären Einsen N1 verglichen werden, wodurch ebenfalls das Verhältnis von binären Nullen zu Einsen berücksichtigt wird.

[0022] Der Bereich, in dem eine Verschiebung der Entscheiderschwelle möglich ist, kann begrenzt werden, so dass der Taktregenerator bzw. der Empfänger stets im funktionsfähig bleibt.

[0023] In einer ähnlichen Weise werden Korrektursignale KBT (before transition) und KAT vor (after transition) und nach dem Übergang zwischen zwei Binärzuständen gewonnen. Dies erfolgt wieder durch Kombination des Korrektursignals mit jeweils einem (korrigierten) Bit vor und nach dem Übergang zwischen zwei binären Zuständen des korrigierten Signals, das in der Regel dem ursprünglichen binären Signal entspricht.

[0024] **Figur 3** zeigt wieder den Amplitudenverlauf des binären Signals BS in Abhängigkeit von der Zeit t. Die Soll-Abtastzeitpunkte sind mit  $T_0, T_1, T_2, \dots$  gekennzeichnet, die Ist-Zeitpunkte dagegen mit  $T_{0i}, T_{1i}, T_{2i}$ . Durch einen Phasenfehler  $\varphi$  des Abtastsignals gegenüber dem idealen Abtastzeitpunkt bzw. dem Signal, kurz als Phase bezeichnet, werden Fehlabtastungen bei Zustandswechseln wahrscheinlicher. Dadurch, dass der Abtastzeitpunkt  $T_{0i}$  näher an den Übergang zwischen den binären Zuständen heranrückt, erfolgt bei zusätzlichen Beeinflussungen/Störungen des binären Signals BS - gestrichelt dargestellt - eine "fehlerhafte" Abtastung. Hier wird ein O-Bit abgetastet, das durch einen Korrekturvorgang KBT in ein 1-Bit korrigiert wird. Zum Zeitpunkt  $T_{1i}$  spielt die Phasenverschiebung des Taktsignals dagegen keine Rolle, da kein Signalübergang in der Nähe stattfindet. Erst in der Nähe des Zeitpunkts  $T_{2i}$  ändert sich der binäre Zustand wieder von "0" in "1", wodurch die Wahrscheinlichkeit für eine fehlerhafte Abtastung wieder ansteigt. Bei der dargestellten Bitfolge wird es beim Übergang von "1" nach "0" durch den dann beibehaltenen Binärzustand "0" mit einer hohen Wahrscheinlichkeit mehr Phasen-Korrekturen KBT geben als nach dem Übergang.

[0025] Wird das Bit vor dem Signalübergang bei einem gestrichelt dargestellten gestörten Signals fälschlich als "0" abgetastet und anschließend korrigiert, wird ein Phasen-Korrektursignal KBT abgegeben, das hier die Korrektur einer binären "0" in eine "1" angibt. Da das nächste (gegebenenfalls korrigierte) Bit eine Null ist, ist im idealen oder ersatzweise korrigierten Binärsignal ein Übergang zwischen den Binärzuständen vorhanden. Wird dagegen das Bit nach dem Übergang korrigiert, wird ein Phasen-Korrektursignal KAT (After Transition) abgegeben. Diese Signale werden in einem Phasenregler 6 summiert und die Summen miteinander verglichen. Das Ergebnis dieser Vergleichs, ein Taktphasen-Korrektursignal PH, steuert bzw. korrigiert die Phasenlage des Taktsignals TS in Relation zum binären Signal BS bis die Anzahl beider Korrektursignale den gleichen Wert hat. Es gilt

(5)  $\sum KBT > \sum KAT \Rightarrow$  Phase TS beschleunigen bzw. Frequenz erhöhen

5 (6)  $\sum KBT < \sum KAT \Rightarrow$  Phase TS verzögern bzw. Frequenz erniedrigen

[0026] Die Phasendifferenz  $\varphi$  des Taktsignals TS gegenüber dem idealen Abtastzeitpunkten  $T_0, T_1, T_2, \dots$  für das binäre Signal BS ist beim dargestellten Beispiel zu verringern. Entsprechendes gilt bei einer voreilenden Phase des Taktsignals.

10 [0027] Im Ausführungsbeispiel Figur 1 wird die Phase des von dem Taktregenerator 3, hier als Phasenregelkreis (PLL) ausgebildet, erzeugten Taktsignals korrigiert. In der Regel wird die Korrektur gering sein und kann auch begrenzt werden. Die Veränderung der Phase kann in beliebiger Weise erfolgen, besonders einfach durch Eingriff in den Phasenregelkreis wie im Ausführungsbeispiel.

15 [0028] Ohne zusätzliche Maßnahmen arbeitet das Verfahren nur, wenn vor bzw. nach einem Übergang zwischen den Binärzuständen der Binärzustand für mindestens ein weiteres Bit erhalten bleibt. Bei einem 1010-Wechsel heben sich die Phasen-Korrektursignale mit großer Wahrscheinlichkeit auf; sie können auch durch Auswertung der Bitfolgen unterdrückt werden. Bei einem andauernden Wechsel von binären Nullen und binären Einsen wird die Phasenkorrektur ohne Zusatzmaßnahmen nicht erreicht; dieser Fall tritt jedoch bei einer üblichen Datenübertragung nicht auf und außerdem bleibt die Funktion der analogen Phasenregelung erhalten.

20 [0029] Durch eine Überwachung der Korrekturrate kann die Übertragungsstrecke überprüft werden und die Regel-einrichtungen des Datenregenerators gesteuert werden.

### Patentansprüche

- 25 1. Verfahren zur Regelung der Entscheiderschwelle (TH) bei der Abtastung eines binären Signals (BS) durch Aus-wertung von Fehlerkorrektursignalen,

**dadurch gekennzeichnet,**

**dass** als fehlerhaft erkannte 1-Bits und als fehlerhaft erkannte 0-Bits gezählt werden,

30 die Anzahl ( $\Sigma K1$ ) der als fehlerhaft erkannten 1-Bits und die Anzahl ( $\Sigma K0$ ) der als fehlerhaft erkannten 0-Bits aus-gewertet wird und

**dass** die Entscheiderschwelle (TH) entsprechend derart verstellt wird, dass ein optimales Verhältnis der als feh-lerhaft erkannten 1-Bits und 0-Bits erreicht wird.

- 35 2. Verfahren nach Anspruch 1,

**dadurch gekennzeichnet,**

**dass** die Differenz ( $\Sigma K1 - \Sigma K0$ ) zwischen den als fehlerhaft erkannten 1-Bits und 0-Bits gebildet wird und dass diese Differenz in ein Stellsignal für die Entscheiderschwelle (TH) umgesetzt wird.

- 40 3. Verfahren nach Anspruch 2,

**dadurch gekennzeichnet,**

**dass** bei gleichgewichtigen Codes die Entscheiderschwelle (TH) derart eingestellt wird, dass die Differenz ( $\Sigma K1 - \Sigma K0$ ) Null wird.

- 45 4. Verfahren nach Anspruch 2,

**dadurch gekennzeichnet,**

**dass** bei ungleichgewichtigen Codes das Verhältnis von 1-Bits zu 0-Bits des binären Signals (BS) berücksichtigt wird.

- 50 5. Verfahren nach Anspruch 4,

**dadurch gekennzeichnet,**

**dass** bei ungleichgewichtigen Codes das Verhältnis von als fehlerhaft erkannten 1-Bits ( $\Sigma K1$ ) zur Gesamtzahl der 0-Bits ( $N0$ ) gebildet wird,

**dass** das Verhältnis der als fehlerhaft erkannten 0-Bits ( $\Sigma K0$ ) zur Gesamtzahl ( $N0$ ) der 1-Bits ( $N1$ ) gebildet wird,

55 **dass** ein Vergleich beider Quotienten durchgeführt wird

und **dass** die Entscheiderschwelle auf Grund dieses Vergleichs derart eingestellt wird, dass die Differenz zwischen den Quotienten Null wird.

6. Verfahren zur Regelung der relativen Phase eines Abtasttaktsignals (TS) zur Phase eines binären Signals (BS) durch Auswertung von Fehlerkorrektursignalen,

**dadurch gekennzeichnet**,

**dass** vor einem Übergang zwischen den Binärzuständen als fehlerhaft erkannte Bits (KBT) und nach einem Übergang zwischen den Binärzuständen als fehlerhaft erkannte Bits (KAT) gezählt und die Summen ( $\Sigma$ KBT,  $\Sigma$ KAT) ausgewertet werden und

**dass** die Phase des Abtasttaktsignals (TS) derart verstellt wird, dass zumindest annähernd die selbe Anzahl der als fehlerhaft erkannte Bits ( $\Sigma$ KBT,  $\Sigma$ KAT) vor und nach einem Übergang zwischen den Binärzuständen auftritt.

- 10 7. Verfahren nach Anspruch 6,

**dadurch gekennzeichnet**,

**dass** nur Übergänge bei bestimmten Binärfolgen ausgewertet werden und/oder nur ein bestimmter Übergang zwischen den Binärzuständen ausgewertet wird.

- 15 8. Verfahren nach einem der vorhergehenden Ansprüche,

**dadurch gekennzeichnet**,

**dass** Korrektursignale einer Fehlerkorrektureinrichtung (4) logisch kombiniert mit dem jeweiligen Binärzustand als fehlerhaft erkanntes Bits (K1, K0) ausgewertet werden und/oder dass Korrektursignale vor und nach dem Übergang zwischen den Binärzuständen als Phasen-Korrektursignale (KBT, KAT) ausgewertet werden.

- 20 9. Verfahren nach einem der vorhergehenden Ansprüche,

**dadurch gekennzeichnet**,

**dass** die Entscheiderschwelle (TH) für das binäre Signal (BS) und die Phase des Abtasttaktsignals (TS) geregelt werden.

- 25 10. Verfahren nach einem der vorhergehenden Ansprüche,

**dadurch gekennzeichnet**,

**dass** der Anteil der als fehlerhaft angesehen Bits zur Steuerung der Zeitkonstanten einer Regelungen verwendet wird.

- 30 11. Anordnung zur Regelung der Entscheiderschwelle (TH) eines Datenregenerators (1-5) mit einer Entscheiderstufe (1), der ein binäres Signal (BS) und ein Vergleichssignal (TH) zugeführt werden, mit einer Abtastkippstufe (2), deren Dateneingang (D) mit dem Ausgang der Entscheiderstufe (1) verbunden ist, und mit einem steuerbaren Taktregenerator (3), der ein Abtasttaktsignal (TS) für die Abtastkippstufe (2) erzeugt und von einer Fehlerkorrektureinrichtung (4) gesteuert wird,

**dadurch gekennzeichnet**,

**dass** ein erster Regler (5) vorgesehen ist, dem von der Fehlerkorrektureinrichtung (4) ein erstes Korrektursignal (K1) zugeführt wird, das eine Korrektur eines 1-Bits anzeigt, und dem ein zweites Korrektursignal (K0) zugeführt wird, das die Korrektur eines 0-Bits angibt,

40 **dass** der erste Regler separat beide Korrektursignale summiert und deren Anzahl oder Verhältnis bewertet und dass der erste Regler (5) ein Steuersignal erzeugt, das die Höhe der Vergleichssignals (TH) bestimmt.

- 45 12. Anordnung zur Regelung der Phase ( $\phi$ ) eines Abtasttaktsignals (TS) mit einem Taktregenerator (3), der, von einer Fehlerkorrektureinrichtung (4) gesteuert, dieses Abtasttaktsignal (TS) erzeugt, mit dem ein binäres Signal (BS) in eine Abtastkippstufe (2) abgetaktet wird,

**dadurch gekennzeichnet**,

**dass** ein zweiter Regler (6) vorgesehen ist, dem von der Fehlerkorrektureinrichtung (4) ein erstes Phasen-Korrektursignal (KBT) zugeführt wird, das die Korrektur eines Bits vor einem Signalübergang zwischen zwei binären Zuständen angibt, und dem ein zweites Phasenkorrektursignal (KAT) zugeführt wird, das die Korrektur eines Bits nach einem Signalübergang zwischen zwei binären Zuständen angibt, der die Korrektursignale (KBT, KAT) zählt, die Summen ( $\Sigma$ KBT,  $\Sigma$ KAT) vergleicht und ein Phasenkorrektursignal (PH) erzeugt, das die Phase des Abtasttaktsignals (TS) derart verstellt, dass zumindest annähernd die selbe Anzahl von Korrektursignalen ( $\Sigma$ KBT,  $\Sigma$ KAT) vor und nach einem Übergang zwischen den Binärzuständen auftritt.

- 55 13. Anordnung zur Regelung der Entscheiderschwelle (TH) und der Phase ( $\phi$ ) des Abtasttaktsignals (TS) eines Datenregenerators (1-6) nach den Ansprüchen 12 und 13.

FIG 1

FIG 2

FIG 3

Europäisches

Patentamt

**EUROPÄISCHER RECHERCHENBERICHT**

Nummer der Anmeldung

EP 01 10 3107

| <b>EINSCHLÄGIGE DOKUMENTE</b>                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                              |                     |                                            |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------|--|--|

| Kategorie                                                                                                                                                                                                                                                                                                                                             | Kennzeichnung des Dokuments mit Angabe, soweit erforderlich, der maßgeblichen Teile                                                                          | Betitl.<br>Anspruch | KLASSIFIKATION DER<br>ANMELDUNG (Int.Cl.7) |  |  |

| X                                                                                                                                                                                                                                                                                                                                                     | EP 0 328 266 A (NORTHERN TELECOM LTD)<br>16. August 1989 (1989-08-16)<br>* Spalte 4, Zeile 10 – Zeile 48 *<br>* Spalte 7, Zeile 57 – Spalte 8, Zeile 11<br>* | 1-13                | H04L25/06                                  |  |  |

| A,D                                                                                                                                                                                                                                                                                                                                                   | DE 197 17 642 A (SIEMENS AG)<br>5. November 1998 (1998-11-05)<br>* Zusammenfassung *                                                                         | 1-13                |                                            |  |  |

| A                                                                                                                                                                                                                                                                                                                                                     | WO 99 12315 A (SIEMENS AG)<br>11. März 1999 (1999-03-11)<br>* Zusammenfassung *                                                                              | 1-13                |                                            |  |  |

| E                                                                                                                                                                                                                                                                                                                                                     | EP 1 085 713 A (MARCONI COMM LTD)<br>21. März 2001 (2001-03-21)<br>* Spalte 1, Zeile 47 – Spalte 2, Zeile 22<br>*                                            | 1-5,11              |                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                              |                     |                                            |  |  |

| RECHERCHIERTE<br>SACHGEBiete (Int.Cl.7)                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |                     |                                            |  |  |

| H04L                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                              |                     |                                            |  |  |

| <p>Der vorliegende Recherchenbericht wurde für alle Patentansprüche erstellt</p>                                                                                                                                                                                                                                                                      |                                                                                                                                                              |                     |                                            |  |  |

| Recherchenort                                                                                                                                                                                                                                                                                                                                         | Abgeschlußdatum der Recherche                                                                                                                                | Prüfer              |                                            |  |  |

| DEN HAAG                                                                                                                                                                                                                                                                                                                                              | 20. Juli 2001                                                                                                                                                | Orozco Roura, C     |                                            |  |  |

| <p><b>KATEGORIE DER GENANNTEN DOKUMENTE</b></p> <p>X : von besonderer Bedeutung allein betrachtet<br/>Y : von besonderer Bedeutung in Verbindung mit einer anderen Veröffentlichung derselben Kategorie<br/>A : technologischer Hintergrund<br/>O : nichtschriftliche Offenbarung<br/>P : Zwischenliteratur</p>                                       |                                                                                                                                                              |                     |                                            |  |  |

| <p>T : der Erfindung zugrunde liegende Theorien oder Grundsätze<br/>E : älteres Patentdokument, das jedoch erst am oder nach dem Anmeldeatum veröffentlicht worden ist<br/>D : in der Anmeldung angeführtes Dokument<br/>L : aus anderen Gründen angeführtes Dokument<br/>&amp; : Mitglied der gleichen Patentfamilie, übereinstimmendes Dokument</p> |                                                                                                                                                              |                     |                                            |  |  |

**ANHANG ZUM EUROPÄISCHEN RECHERCHENBERICHT

ÜBER DIE EUROPÄISCHE PATENTANMELDUNG NR.**

EP 01 10 3107

In diesem Anhang sind die Mitglieder der Patentfamilien der im obengenannten europäischen Recherchenbericht angeführten Patentdokumente angegeben.

Die Angaben über die Familienmitglieder entsprechen dem Stand der Datei des Europäischen Patentamts am

Diese Angaben dienen nur zur Unterichtung und erfolgen ohne Gewähr.

20-07-2001

| Im Recherchenbericht<br>angeführtes Patentdokument |   | Datum der<br>Veröffentlichung |  | Mitglied(er) der<br>Patentfamilie                                                                                                                 |  | Datum der<br>Veröffentlichung                                                                                              |

|----------------------------------------------------|---|-------------------------------|--|---------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------|

| EP 0328266                                         | A | 16-08-1989                    |  | US 4823360 A<br>CA 1279914 A<br>CN 1038731 A, B<br>DE 68916053 D<br>DE 68916053 T<br>JP 1874239 C<br>JP 2007745 A<br>JP 5086096 B<br>KR 9206280 B |  | 18-04-1989<br>05-02-1991<br>10-01-1990<br>21-07-1994<br>22-09-1994<br>26-09-1994<br>11-01-1990<br>09-12-1993<br>03-08-1992 |

| DE 19717642                                        | A | 05-11-1998                    |  | BR 9808995 A<br>CN 1253684 T<br>WO 9849801 A<br>EP 0978176 A                                                                                      |  | 08-08-2000<br>17-05-2000<br>05-11-1998<br>09-02-2000                                                                       |

| WO 9912315                                         | A | 11-03-1999                    |  | DE 19738362 A                                                                                                                                     |  | 04-03-1999                                                                                                                 |

| EP 1085713                                         | A | 21-03-2001                    |  | GB 2354412 A<br>AU 5948100 A<br>CN 1289192 A<br>NO 20004653 A                                                                                     |  | 21-03-2001<br>22-03-2001<br>28-03-2001<br>19-03-2001                                                                       |