(11) **EP 1 246 197 A1**

(12)

# **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication: **02.10.2002 Bulletin 2002/40**

(51) Int Cl.<sup>7</sup>: **G11C 16/12**

(21) Numéro de dépôt: 02366003.8

(22) Date de dépôt: 05.03.2002

(84) Etats contractants désignés:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE TR

Etats d'extension désignés:

AL LT LV MK RO SI

(30) Priorité: 12.03.2001 FR 0103284

(71) Demandeur: STMicroelectronics S.A. 92120 Montrouge (FR)

(72) Inventeurs:

- Naura, David

57070 Metz (FR)

- Bertrand, Bertrand 57070 Metz (FR)

- Chehadi, Mohamad 57070 Metz (FR)

- (74) Mandataire: Bentz, Jean-Paul et al Cabinet Ballot

9 rue Claude Chappe

57070 Metz (FR)

# (54) Circuit et procédé associé d'effacement ou de programmation d'une cellule mémoire

(57) L'invention concerne un circuit (200) et un procédé associé de production d'une tension d'effacement ou de programmation d'une cellule mémoire, comprenant un condensateur (C), et un circuit de décharge (207) connecté à une première borne (TOP) du condensateur (C)) pour décharger le condensateur (C).

Selon l'invention, le circuit de décharge (207) du condensateur (C) comprend

- un premier transistor (309), dont un drain est con-

necté à la première borne (TOP) du condensateur (C), pour activer le circuit de décharge (207) lorsqu'un signal de décharge (DECHARGE) est reçu,

une branche de décharge lente (305, 306) et une branche de décharge rapide (307, 308), connectées en parallèle à la source du premier transistor (309), pour produire un faible ou un fort courant de décharge (IDECH0) du condensateur (C) en fonction d'un signal de sélection (MODE) d'un mode de fonctionnement du circuit.

25

#### **Description**

**[0001]** L'invention concerne un circuit et un procédé associé d'effacement ou de programmation d'une cellule mémoire. L'invention est notamment intéressante pour des mémoires de type non volatile, électriquement programmables et effaçables, par exemple des mémoires de type EEPROM, flash EPROM, etc.

**[0002]** Le composant principal d'une cellule mémoire de ces mémoires est un transistor de mémorisation de type à grille flottante comprenant un drain, une source, une grille de commande et une grille flottante qui mémorise une information. La programmation d'une cellule mémoire est le plus souvent réalisée en deux étapes : une étape d'effacement suivie d'une étape d'écriture.

[0003] Pour réaliser une étape d'effacement de la cellule mémoire, on applique par exemple une haute tension sur la grille de commande du transistor de mémorisation et une tension nulle sur son drain et sur sa source. Ainsi, la différence de potentiel entre la grille de commande et le drain du transistor de mémorisation entraîne la création d'un champ électrique entre la grille de commande et le drain, qui a pour conséquence la migration d'électrons depuis la source et le drain vers la grille flottante et donc la décharge de la grille flottante.

[0004] Inversement, pour réaliser une étape d'écriture de la cellule mémoire, on applique une tension nulle

[0004] Inversement, pour réaliser une étape d'écriture de la cellule mémoire, on applique une tension nulle sur la grille de commande du transistor de mémorisation et une haute tension sur son drain, sa source étant portée à un potentiel flottant. La différence de potentiel entre la grille de commande et le drain du transistor de mémorisation entraîne la création d'un champ électrique de polarité opposée, qui a pour conséquence la migration d'électrons en sens inverse, depuis la grille flottante du transistor de mémorisation vers son drain.

**[0005]** Pour réaliser une étape d'écriture ou d'effacement de la cellule mémoire, il est ainsi nécessaire de disposer d'une haute tension d'effacement ou de programmation, de l'ordre de 15 à 20 V, qui est appliquée sur l'une ou l'autre des électrodes du transistor de mémorisation de la cellule mémoire, selon l'opération à effectuer.

[0006] Cependant, la couche d'oxyde comprise entre la grille flottante et le drain du transistor de mémorisation est peu épaisse et fragile. Aussi, lorsque la tension appliquée sur les électrodes du transistor de mémorisation est supérieure à une tension dite tunnel, elle ne doit pas varier brutalement. En effet, une variation brutale de la tension entraîne la création d'un courant important entre la grille flottante et le drain ou la source du transistor. Un courant trop important entraînerait une fragilisation, voire une détérioration de la couche d'oxyde.

[0007] On rappelle que la tension tunnel est la tension minimale nécessaire pour qu'une charge transite par effet tunnel à travers la couche d'oxyde, entre la grille flottante et le drain d'un transistor à grille flottante. Typiquement, la valeur de la tension tunnel est de l'ordre de 10 V. [0008] Pour obtenir une tension variant progressive-

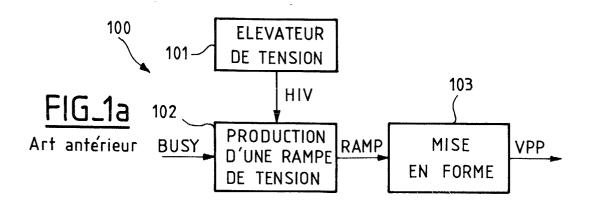

ment et lentement, on utilise classiquement un circuit d'effacement ou de programmation dont un exemple connu est présenté schématiquement sur la figure 1a; il comprend un élévateur de tension 101, un circuit 102 de production d'une rampe de tension et un circuit 103 de mise en forme, tous trois alimentés par une basse tension d'alimentation VDD (non représentée sur la figure 1a), de l'ordre de 2 à 3 V pour une technologie 0,25 μm.

[0009] Le circuit élévateur de tension 101 est par exemple de type pompe de charge ; il produit une haute tension HIV de l'ordre de 15 à 20 V à partir de la basse tension d'alimentation VDD.

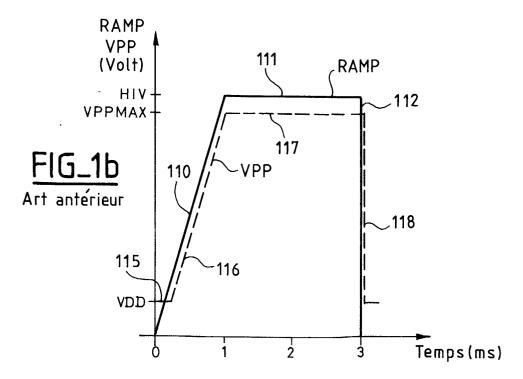

**[0010]** Le circuit 102 produit, à partir de la haute tension HIV, une tension en rampe RAMP, qui a par exemple la forme représentée en trait continu sur la figure 1b. Elle comprend :

- une phase ascendante 110 au cours de laquelle la tension RAMP augmente de façon continue jusqu'à sa valeur maximale VMAX, qui est par exemple égale à la haute tension HIV,

- un plateau de tension 111 pendant lequel la tension RAMP est constante, égale à la valeur VMAX,

- une chute de tension 112.

[0011] Le circuit de génération de rampe 102 comprend classiquement un circuit de charge et de décharge d'un condensateur de puissance ; ce circuit est alimenté par une source de courant qui fournit un courant de référence IREF. La phase ascendante 110 de la tension RAMP est obtenue en chargeant un condensateur avec un courant de charge ICH. Le plateau de tension 111 est quant à lui obtenu par la décharge de ce même condensateur avec un courant de décharge IDECH.

[0012] Les courants de charge et / ou de décharge utilisés sont le plus souvent, mais pas nécessairement, proportionnels à IREF et constants. Ils sont le plus souvent différents l'un de l'autre. La phase ascendante 110 peut être plus longue ou plus courte que le plateau de tension 111, selon la valeur du courant ICH par rapport à celle du courant IDECH.

**[0013]** La phase ascendante 110 et le plateau de tension 111 ont une durée totale TRAMP qui correspond à la durée d'une opération d'effacement (ou de programmation).

[0014] Un choix convenable de la capacité du condensateur ainsi que du courant de référence IREF permet d'optimiser la pente de la phase ascendante 110 ainsi que la durée totale TRAMP. Ce choix est en général un compromis fait à partir des critères suivants :

lorsque la tension appliquée sur les électrodes du transistor de mémorisation est supérieure à la tension tunnel, elle ne doit pas varier brutalement comme on l'a vu précédemment. Pour cela, la pente de la phase ascendante 110 ne doit pas dépasser une valeur limite.

- la durée totale TRAMP doit être suffisamment longue pour que la tension RAMP ait le temps d'atteindre sa valeur maximale VMAX,

- le plateau de tension doit durer suffisamment longtemps pour assurer la réalisation complète d'une étape d'effacement ou de programmation,

- la durée totale TRAMP doit être la plus faible possible.

**[0015]** Le circuit de mise en forme 103 reçoit la tension RAMP et produit une haute tension d'effacement ou de programmation VPP qui est appliquée sur l'une ou l'autre les électrodes d'une cellule mémoire (non représentée figure 1a), selon qu'une programmation ou un effacement de la cellule mémoire est envisagé.

**[0016]** La haute tension d'effacement ou de programmation VPP a par exemple la forme représentée en tirets sur la figure 1b ; elle comprend :

- un premier plateau de tension 115, pendant lequel la tension VPP est égale à la basse tension d'alimentation VDD,

- une phase ascendante 116 suivie d'un second plateau de tension 117, la tension VPP est ici égale à la tension RAMP, à une chute de tension VTN près dans un transistor,

- une chute de tension 118, au cours de laquelle la tension VPP redescend à la valeur VDD.

**[0017]** La tension VPP suit ainsi les variations de la tension RAMP, à une chute de tension VTN près, de l'ordre de 2 V, qui correspond approximativement à la tension de seuil de conduction d'un transistor de type N.

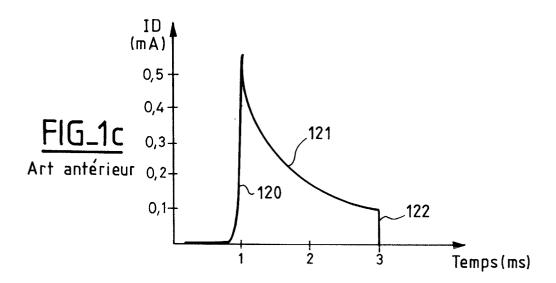

[0018] Lors d'une programmation d'une cellule mémoire, une tension nulle est appliquée sur la grille de commande du transistor à grille flottante, une tension égale à VPP est appliquée sur le drain du transistor et sa source est laissée à un potentiel flottant. Le courant ID circulant entre le drain et la source du transistor a dans ce cas l'allure représentée sur la figure 1c.

[0019] Le courant ID est nul lorsque la tension VPP est croissante et inférieure à la tension tunnel, puis il croît brutalement (réf. 120) depuis une valeur nulle jusqu'à une valeur maximale IDMAX lorsque VPP dépasse la tension tunnel. La valeur IDMAX est atteinte lorsque VPP atteint sa valeur maximale VPPMAX. Le courant ID redescend ensuite (réf. 121) pendant toute la durée du plateau 117, puis il chute brutalement à zéro (réf. 122) lorsque la tension VPP chute (118) à sa valeur minimale VDD.

**[0020]** Lors d'un effacement de la cellule mémoire, le courant circulant entre le drain et la source a une allure similaire, il circule simplement en sens inverse par rapport au cas d'une programmation.

**[0021]** Le temps d'effacement TER (ou de programmation TWR) de la cellule mémoire est de l'ordre de TRAMP, environ 3 ms. Le temps d'effacement ou de programmation d'une cellule mémoire est ainsi relative-

ment long, ce qui peut être particulièrement dommageable dans certains cas.

[0022] Par exemple, lors de la fabrication des mémoires, toutes les cellules de la mémoire sont soumises notamment à un test d'endurance, consistant généralement à exécuter successivement plusieurs opérations (de l'ordre de 500 opérations) d'effacement et / ou de programmation, pour vérifier si les cellules ont été correctement réalisées ou pas, et si elles vérifient les spécifications demandées en matière de résistance à l'usage notamment.

[0023] Ce test d'endurance représente seulement un test parmi l'ensemble des tests effectués lors de la réalisation d'une mémoire, cependant ce seul test est particulièrement long puisqu'il dure environ 2 s, ce qui représente environ la moitié de la durée totale d'une phase complète de test d'une mémoire.

**[0024]** Un but de l'invention est de diminuer les temps d'effacement ou de programmation d'une cellule mémoire sans nuire à la qualité de la cellule. Ceci permettra notamment de réduire de manière importante la durée du test d'endurance d'une mémoire en sortie de chaîne de production.

**[0025]** L'invention concerne ainsi un circuit de production d'une tension d'effacement ou de programmation d'une cellule mémoire, comprenant un condensateur, et un circuit de décharge connecté à une première borne du condensateur pour décharger le condensateur.

**[0026]** Selon l'invention, le circuit de décharge du condensateur comprend :

- un premier transistor, dont un drain est connecté à la première borne du condensateur, pour activer le circuit de décharge lorsqu'un signal de décharge est appliqué sur la grille de commande du premier transistor,

- une branche de décharge lente connectée à la source du premier transistor, pour produire un faible courant de décharge du condensateur lorsque le signal de décharge est reçu, et

- une branche de décharge rapide, connectée à la source du premier transistor, pour produire un courant de décharge rapide du condensateur lorsque le signal de décharge et un signal de sélection d'un mode de fonctionnement sont reçus simultanément

[0027] Ainsi, selon l'invention, on utilise un courant de décharge IDECH qui prend deux valeurs. Ceci permet, selon la valeur utilisée, de conserver ou de réduire (voire de supprimer) le plateau des tensions RAMP, VPP, puisque la durée du plateau est proportionnelle à la valeur du courant IDECH. Le choix de l'une ou l'autre des valeurs du courant IDECH est fait par l'utilisateur.

**[0028]** Le circuit de production d'une tension d'effacement ou de programmation d'une cellule mémoire selon l'invention fonctionne de la manière suivante.

40

[0029] Il est activé lorsqu'il reçoit le signal de décharge. De plus, si aucun signal de sélection de mode n'est reçu, le circuit selon l'invention est dans un mode de fonctionnement standard, et son fonctionnement dans ce cas est similaire à celui d'un circuit selon l'art antérieur. En particulier, la décharge du condensateur s'effectue, lorsque le signal de décharge est reçu, dans des conditions similaires à celle d'un condensateur d'un circuit selon l'art antérieur et la durée du plateau correspondant est du même ordre de grandeur. On choisit pour cela un courant de décharge lente du même ordre de grandeur que le courant de décharge utilisé dans un circuit selon l'art antérieur.

[0030] Par contre, si un signal de sélection est reçu, alors le circuit selon l'invention est dans un mode de fonctionnement spécifique. Dans ce cas, on décharge très rapidement le condensateur, pour réduire ou supprimer la phase de plateau et réduire ainsi le temps d'effacement ou de programmation. La branche de décharge rapide fournit pour cela le fort courant de décharge, qui est par exemple 20 à 40 fois le faible courant de décharge produit par la branche de décharge lente.

**[0031]** En réduisant ou supprimant le plateau, on réduit bien sûr d'autant la durée d'une étape d'effacement ou de programmation d'une cellule mémoire. En choisissant un fort courant de décharge adéquat, on peut ainsi diminuer par deux la durée d'une telle étape.

**[0032]** Il est à noter que, dans le cas d'une suppression complète du plateau, l'effacement ou la programmation d'une cellule n'est assuré qu'à 70% environ. Ceci peut être gênant pour certaines applications, mais pas pour toutes.

[0033] Par exemple, dans un mode de fonctionnement normal d'une cellule mémoire, il est important d'assurer une programmation complète, afin d'assurer d'une part une bonne conservation des données dans le temps, et d'autre part une réalisation correcte d'une éventuelle lecture.

[0034] Inversement, pour réaliser un test d'endurance sur une cellule mémoire, il n'est pas indispensable d'assurer un effacement ou une programmation complète de la cellule. Il suffit que la tension de d'effacement ou de programmation appliquée et le courant dans la cellule créé par cette tension atteignent leurs valeurs maximales : l'objectif de ce test est en effet seulement de voir le comportement dans le temps de la cellule lorsqu'elle supporte une forte tension et / ou un fort courant. [0035] Le circuit de production d'une tension d'effacement ou de programmation d'une cellule mémoire de l'invention permet ainsi de réaliser différents types d'effacement ou de programmation de cellules mémoire, dans les meilleures conditions possibles, notamment en terme de temps, de tensions appliquées, de courant créés, etc.

**[0036]** La branche de décharge lente comprend par exemple un deuxième transistor, dont un drain est connecté à la source du premier transistor et dont une source est connectée à une masse du circuit, le faible cou-

rant de décharge étant proportionnel à un courant de référence appliqué sur la grille de commande du deuxième transistor. Le deuxième transistor peut également être remplacé par une série de transistors associés en parallèle.

**[0037]** La branche de décharge rapide comprend par exemple :

- un troisième transistor, dont un drain est connecté à la source du premier transistor, le signal de sélection de mode étant appliqué sur la grille de commande du troisième transistor, et

- un quatrième transistor, dont un drain est connecté à une source du troisième transistor et dont une source est connectée à la masse du circuit, le courant de référence étant appliqué sur la grille de commande du quatrième transistor. Le quatrième transistor peut également être remplacé par une série de transistors associés en parallèle.

[0038] La taille (en terme de rapport longueur sur la largeur de grille W/L) du quatrième transistor est supérieure à la taille du deuxième transistor. Ainsi, le courant qui traverse le quatrième transistor, lorsqu'il est passant, est supérieur à celui qui traverse le deuxième transistor. Par exemple, la taille du quatrième transistor est 10 à 100 fois supérieure à la taille du deuxième transistor.

[0039] Selon un autre mode de réalisation de l'invention, le circuit de production d'une tension d'effacement ou de programmation d'une cellule mémoire comprend également un circuit de charge, connecté à une deuxième borne du condensateur pour charger le condensateur, qui comporte :

- une branche de charge lente connectée à la deuxième borne du condensateur, pour produire un faible courant de charge lorsque un signal d'activation est recu, et

- une branche de charge rapide, connectée à la deuxième borne du condensateur, pour produire un fort courant de charge du condensateur si le signal de sélection de mode et un signal de niveau de tension sont reçus simultanément, le signal de niveau de tension indiquant qu'une tension d'effacement ou de programmation fournie par le circuit de production d'une tension d'effacement ou de programmation est inférieure à une tension de seuil.

**[0040]** On obtient ainsi une charge du condensateur, et donc une croissance de la tension d'effacement ou de programmation, qui varie selon le mode de fonctionnement du circuit :

- lorsque le signal de sélection de mode est inactif, la croissance de la tension de programmation ou d'effacement est lente, selon une seule pente,

- lorsque le signal de sélection de mode est actif, la

croissance de la tension de programmation ou d'effacement est effectuée selon deux pentes : une pente rapide lorsque la tension d'effacement ou de programmation est inférieure à une valeur seuil, et une pente lente sinon. Ainsi, lorsque la tension devient supérieure à la valeur seuil, sa croissance est similaire à celle d'un fonctionnement standard (signal de sélection de mode inactif).

**[0041]** Ceci permet de ne pas varier trop rapidement la tension appliquée sur les oxydes de la cellule mémoire lorsque cette tension a dépassé la tension tunnel de la cellule

**[0042]** Selon un autre mode de réalisation encore, le circuit de production d'une tension d'effacement ou de programmation de l'invention comprend également :

- un circuit de génération d'une rampe de tension, pour produire une rampe de tension, à partir des potentiels sur la première borne et la deuxième borne du condensateur, et

- un circuit de mise en forme, comprenant un huitième transistor, une haute tension étant appliquée sur une borne du huitième transistor, et la tension d'effacement ou de programmation étant fournie sur une autre borne du huitième transistor. Le huitième transistor est choisi de préférence de type P: la tension d'effacement ou de programmation peut ainsi atteindre la valeur de la haute tension puisque un tel transistor de type P ne présente pas de chute de tension à ses bornes lorsqu'il est passant.

**[0043]** Enfin, l'invention concerne également un procédé de production d'une tension d'effacement ou de programmation d'une cellule mémoire, au cours duquel on charge un condensateur en appliquant un courant de charge sur une deuxième borne au cours d'une première étape, puis on décharge le condensateur en appliquant un courant de décharge sur une première borne du condensateur au cours d'une deuxième étape.

**[0044]** Selon l'invention, au cours de la deuxième étape, le courant de décharge prend une faible valeur ou une forte valeur supérieure à la première valeur, en fonction d'un mode de fonctionnement.

[0045] L'invention sera mieux comprise et d'autres caractéristiques et avantages apparaîtront à la lecture de la description qui va suivre, d'un exemple de mise en oeuvre d'un circuit d'effacement ou de programmation selon l'invention. La description est à lire en relation aux dessins annexés dans lesquels :

- la figure 1a est un schéma fonctionnel illustrant un circuit d'effacement ou de programmation d'une cellule mémoire, selon l'art antérieur,

- les figures 1b, 1c sont des diagrammes temporels montrant des signaux à certains points du circuit d'effacement ou de programmation de la figure 1a,

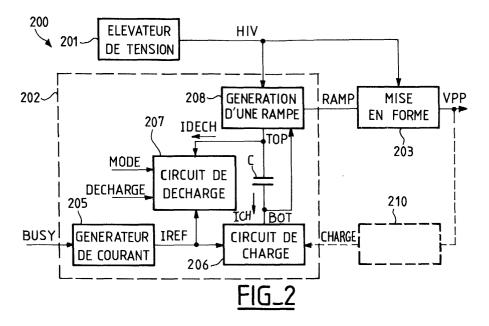

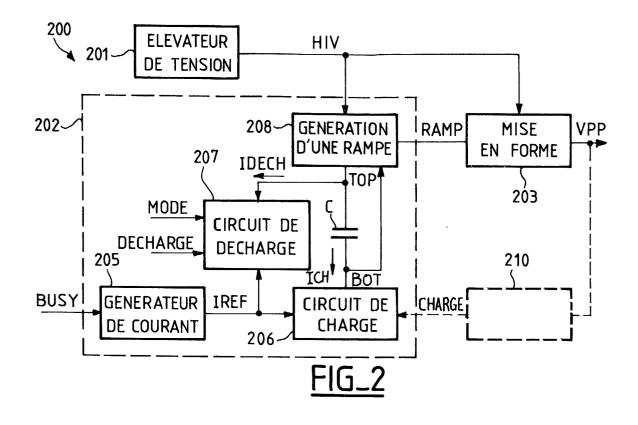

- la figure 2 est un schéma fonctionnel illustrant un

- circuit d'effacement ou de programmation, selon l'invention.

- la figure 4 est un schéma électronique illustrant certains éléments du schéma de la figure 2,

- les figures 3, 5a à 5i sont des diagrammes temporels des signaux à certains points du circuit de la figure 2.

**[0046]** Les figures 1a à 1c correspondent à un état de la technique connu et ont été précédemment décrites. Elles ne seront par détaillées ci-dessous.

**[0047]** Le circuit 200 de production d'une tension d'effacement ou de programmation selon l'invention comprend un élévateur de tension 201, un circuit de production d'une rampe de tension 202 et un circuit de mise en forme 203.

[0048] L'élévateur de tension 201 est par exemple identique à celui utilisé dans le circuit de la figure la, il produit une haute tension continue et stable HIV constante, de l'ordre de 20 V. Le circuit 201 est activé par un signal d'activation BUSY (non représenté) fourni par un circuit de commande extérieur.

[0049] Le circuit de production d'une rampe de tension 202 produit une tension en rampe RAMP, à partir de la haute tension HIV. Le circuit 202 est activé par le signal d'activation BUSY, fourni par un circuit extérieur. [0050] Le circuit 202 comprend un condensateur C, un générateur de courant 205, un circuit 206 de charge du condensateur C, un circuit 207 de décharge du condensateur C, et un circuit de génération d'une rampe de tension 208.

**[0051]** Le générateur de courant 205 produit, sur une borne de sortie, un courant de référence IREF constant lorsqu'il est activé par le signal BUSY, appliqué sur une borne d'entrée de commande du générateur de courant 205

[0052] Le condensateur C est un condensateur de puissance, ayant une capacité de l'ordre de 5 à 10 pF. [0053] Le circuit de charge 206 comprend une borne d'entrée connectée à la borne de sortie du générateur de courant 205 et une borne de sortie connectée à un pôle du condensateur C sur lequel est produit un potentiel BOT. Le circuit de charge 206 produit un courant de charge ICH à partir du courant de référence IREF, le courant ICH étant utilisé pour charger le condensateur C. ICH est ici constant et proportionnel à IREF.

[0054] Le circuit de décharge 207 comprend une borne d'entrée connectée à la borne de sortie du générateur de courant 205, deux bornes d'entrée de commande sur lesquelles sont appliqués deux signaux de commande DECHARGE, MODE et une borne de sortie connectée à l'autre pôle du condensateur C sur lequel est produit un potentiel TOP. Le circuit de décharge 206 produit un courant de décharge IDECH à partir du courant de référence IREF et des signaux de commande DECHARGE, MODE, le courant IDECH étant utilisé pour décharger le condensateur C. IDECH ici est proportionnel à IREF et il varie de la manière suivante, en fonction

50

des signaux de commande DECHARGE, MODE :

9

IDECH = 0 si DECHARGE = 0

IDECH = IDECH0 si DECHARGE = 1 et MODE = 0 IDECH = IDECH1 si DECHARGE = 1 et MODE = 1

**[0055]** Le signal DECHARGE est ainsi utilisé pour activer le circuit de décharge 207, et le signal MODE permet de choisir entre deux valeurs IDECH0, IDECH1 possibles pour le courant de décharge IDECH, en fonction d'un mode de fonctionnement choisi.

[0056] IDECH1 est choisi supérieur à IDECH0, voire très supérieur à IDECH0. Par exemple, IDECH0 est choisi de l'ordre de IREF, et IDECH1 est choisi de l'ordre de 10 à 100 fois le courant IREF. Les courants IDECH0, IDECH1 sont fixés lors de la réalisation du circuit.

**[0057]** Le circuit 208 de génération d'une rampe de tension produit une tension RAMP à partir de la haute tension HIV, et des potentiels BOT, TOP aux pôles du condensateur C. La tension RAMP varie de la manière suivante :

- Au cours d'une première phase (phase de croissance), la tension RAMP est croissante, selon une pente proportionnelle au courant de charge ICH du condensateur C,

- Au cours d'une deuxième phase (phase de plateau), la tension RAMP est constante, la durée de cette deuxième phase étant proportionnelle à la valeur du courant de décharge IDECH utilisé, ainsi :

- Si MODE = 0, alors le courant IDECH est égal à IDECH0 et la durée du plateau est dans ce cas du même ordre de grandeur que la durée de la phase de croissance ou que la durée de la phase de plateau lorsqu'un circuit selon l'art antérieur est utilisé. La durée de la phase de plateau est ainsi de l'ordre de 1 ms. Par contre,

- Si MODE = 1, alors le courant IDECH est égal à IDECH1 et la durée du plateau est plus courte. Le plateau disparaît même complètement si la valeur IDECH1 est très supérieure à IDECH0.

### [0058] En d'autres termes :

- Si MODE = 0, le fonctionnement du circuit selon l'invention est similaire à celui d'un circuit selon l'art antérieur.

- si MODE = 1 par contre, on décharge très rapidement le condensateur C, pour réduire ou supprimer la phase de plateau et réduire ainsi le temps d'effacement ou de programmation.

[0059] Enfin, le circuit de mise en forme 203, activé par le signal BUSY (non représenté figure 2) produit la tension d'effacement ou de programmation VPP à partir de la tension RAMP. La tension VPP varie de la manière suivante :

si BUSY est actif: VPP = VDD si RAMP < VDD et</li>

VPP = RAMP si RAMP ≥ VDD

si BUSY est inactif: VPP = VDD.

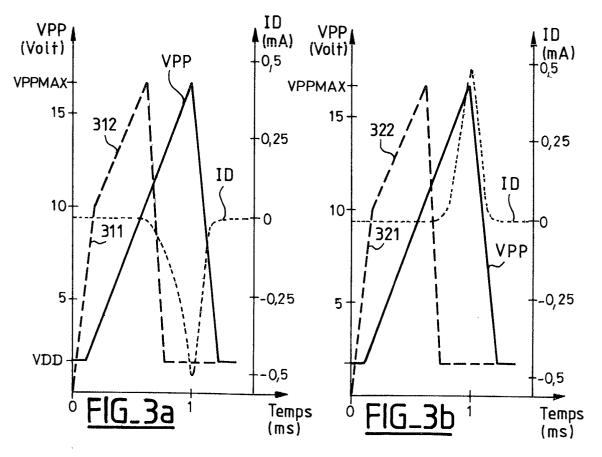

[0060] Le fonctionnement du circuit de la figure 2 va maintenant être décrit en relation avec les diagrammes des figures 3a et 3b, qui montrent l'évolution de la tension VPP appliquée sur les électrodes du transistor à grille flottante d'une cellule mémoire (non représentée) et du courant ID circulant entre le drain et la source de ce transistor dans le cas d'un effacement puis d'une programmation de la cellule mémoire.

**[0061]** Dans l'exemple, on choisit un courant IDECH0 égal IREF et un courant IDECH1 égal à 40\*IREF. On suppose par ailleurs que le signal MODE est actif.

[0062] Un circuit de commutation (non représenté) est connecté entre le circuit 200 selon l'invention et la cellule mémoire ; il permet d'appliquer la tension VPP sur l'une ou l'autre des électrodes du transistor à grille flottante de la cellule mémoire selon l'opération (effacement ou programmation) à effectuer.

**[0063]** Lors de la phase d'effacement de la cellule mémoire (figure 3a), la tension VPP est appliquée sur la grille de commande du transistor à grille flottante, et une tension nulle est appliquée sur son drain et sur sa source.

**[0064]** Initialement, la tension RAMPest nulle, de même que les potentiels TOP et BOT aux pôles du condensateur C. La tension VPP est égale à VDD.

[0065] Lorsque le signal BUSY est activé, la tension RAMP croît selon une pente constante (car ICH est constant) et atteint un maximum. VPP commence à croître lorsque RAMP est supérieure à VDD et elle suit les variations de RAMP. Les tension RAMP, VPP restent ensuite constantes pendant un temps quasi nul (et donc non représenté figure 3a) correspondant à la décharge du condensateur C avec le courant IDECH1. Puis elles chutent respectivement à 0 V et à VDD.

**[0066]** Le courant ID circulant entre le drain et la grille flottante du transistor de mémorisation est nul lorsque VPP est inférieure à la tension tunnel VT du transistor. Puis ID chute brutalement (figure 3a, courbe en pointillés) pour atteindre une valeur minimale lorsque la tension VPP atteint son maximum, puis ID revient à 0 lorsque VPP atteint la valeur VDD.La tension tunnel est dans l'exemple de 10 V.

[0067] Lors de la programmation de la cellule mémoire (figure 3b), la tension VPP est appliquée sur le drain du transistor à grille flottante, une tension nulle est appliquée sur sa grille de commande et sa source est laissée à un potentiel flottant. Les tensions RAMP, VPP évoluent de manière similaire à leur évolution dans le cas d'un effacement de la cellule. Le courant ID évolue par contre en sens contraire.

**[0068]** Le circuit de la figure 2 est amélioré par l'ajout d'un circuit de détection de tension 210 et par la modification du circuit de charge 206.

[0069] Le circuit de détection de tension 210 mesure le niveau de la tension d'effacement ou de programma-

tion VPP, et fournit un signal CHARGE ayant les caractéristiques suivantes :

CHARGE est actif si VPP < VS CHARGE est inactif si VPP ≥ VS,

où VS est une tension de seuil. VS est choisie légèrement inférieure à la tension tunnel VT du transistor à grille flottante d'une cellule mémoire.

[0070] Le circuit de charge modifié comprend une borne d'entrée connectée à la borne de sortie du générateur de courant 205 pour recevoir le courant IREF, une borne d'entrée connectée à une borne de sortie du circuit de détection de tension 210 pour recevoir le signal CHARGE, et une borne de sortie connectée comme précédemment au pôle BOT du condensateur C. Le circuit de charge 206 produit un courant de charge ICH à partir du courant de référence IREF, en fonction du signal CHARGE. Le courant ICH a les propriétés suivantes :

ICH = ICH0 si CHARGE est actif ICH = ICH1 si CHARGE est inactif

**[0071]** Le courant ICH0 est choisi supérieur au courant ICH1. Dans un exemple, ICH0 = 10\*ICH1.

[0072] Ainsi, lorsque la tension VPP est inférieure à VS, le courant ICH0 est produit, qui permet de charger rapidement le condensateur C, et donc d'augmenter rapidement la valeur des tensions RAMP, VPP, selon une première pente (réf. 311, 321, figure 3a, 3b, courbes en tirets). Puis, lorsque la tension VPP atteint et dépasse la tension de seuil VS, le courant produit par le circuit de charge prend la valeur ICH1, de sorte que la croissance des tensions RAMP, VPP est limitée (312, 322). On obtient ainsi des tensions RAMP, VPP, croissant selon deux pentes, une première pente rapide 311, 321, et une deuxième pente lente 312, 322. Les variations de ID sont bien sûr modifiées en conséquence.

[0073] Cette amélioration permet ainsi de conserver aux tensions RAMP, VPP une croissance limitée en particulier lorsque la tension tunnel est atteinte : ceci est important car les oxydes du transistor à grille flottante sont particulièrement fragiles au delà de cette valeur. Cette amélioration permet par contre de réduire encore de manière importante le temps de montée des tensions RAMP, VPP, et en conséquence, les temps de programmation et/ ou d'effacement de la cellule mémoire.

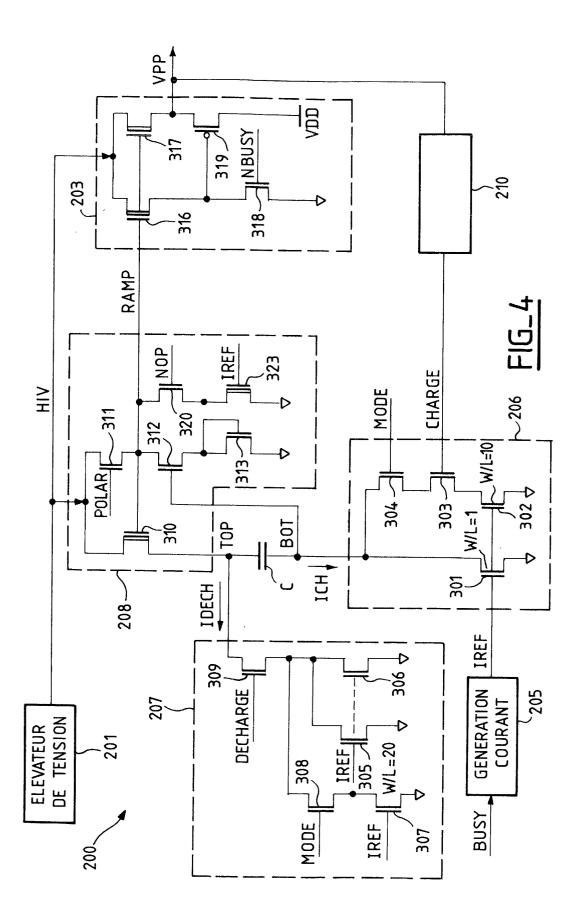

**[0074]** La figure 4 détaille des modes de réalisation de certains éléments du circuit 200 de production d'une tension d'effacement ou de programmation de la figure 2.

[0075] Le circuit de charge 206 comprend un transistor N 301, dont une source est connectée à une masse du circuit. Le transistor reçoit sur sa grille le courant de référence IREF et un courant ICH1 circule entre son drain et sa source.

**[0076]** Ainsi réalisé, le circuit 206 permet la charge du condensateur C à courant constant ICH1, pour fournir une tension RAMP croissante selon une seule pente.

[0077] Selon le mode amélioré de réalisation, le circuit de charge 206 comprend également deux transis-

tors N 302, 303. Les drains des transistors 301, 303 sont connectés ensemble au pôle BOT du condensateur C. La source du transistor 303 est connectée au drain du transistor 302 dont la source est connectée à la masse. Enfin, le courant IREF est appliqué sur la grille du transitor.

Enfin, le courant IREF est appliqué sur la grille du transistor 302 et le signal de commande CHARGE est appliqué sur la grille du transistor 303.

[0078] Le transistor 302 est par exemple de taille (en terme de rapport longueur / largeur de grille W/L) neuf fois supérieure à celle du transistor 301, de sorte que, lorsqu'il est passant (c'est-à-dire lorsque le signal CHARGE est actif), le courant qui circule entre son drain et sa source est neuf fois supérieur au courant ICH1 circulant entre le drain et la source du transistor 301. Ce courant s'ajoute à ICH1 pour former le courant ICH0.

**[0079]** Rappelons que le signal CHARGE a les caractéristiques suivantes :

CHARGE est actif si VPP < VS CHARGE est inactif si VPP ≥ VS,

**[0080]** Ainsi amélioré, le circuit 206 permet de charger le condensateur C :

- lorsque VPP < VS, avec le courant ICH = ICH0, ICH0 étant égal au courant ICH1 circulant dans le transistor 301 additionné du courant circulant dans les transistors 302, 303, et

- lorsque VPP ≥ VS, avec le courant ICH = ICH1.

[0081] On a donc dans ce cas une phase de croissance des tensions RAMP, VPP en deux pentes : une première pente rapide lorsque VPP < VS, suivie d'une deuxième pente lente, lorsque VPP ≥ VS.

[0082] Le circuit 206 peut encore être amélioré par l'ajout d'un transistor 304, dont un drain est connecté au drain du transistor 301 et dont une source est connectée au drain du transistor 303, le transistor 304 recevant le signal de commande MODE sur sa grille de commande. Le transistor 304 permet à l'utilisateur du circuit 200 de choisir une croissance des tensions RAMP, VPP selon une seule pente ou selon deux pentes, en fixant le signal de commande MODE.

[0083] Le circuit de décharge 207 comprend trois transistors 307, 308, 309 de type N. Le transistor 309 a un drain connecté au pôle TOP du condensateur C et le signal de commande DECHARGE est appliqué sur sa grille, permettant ainsi d'activer le circuit de décharge 207

[0084] Le transistor 308 a un drain connecté à la source du transistor 309 et une source connectée à un drain du transistor 307, dont la source est connectée à la masse du circuit. Le signal de commande MODE est appliqué sur la grille du transistor 308 et le courant de référence IREF est appliqué sur la grille du transistor 307. Le transistors 307, 308 sont passants uniquement si le signal MODE est actif.

**[0085]** Le circuit 207 comprend également X transistors N associés en parallèle représentés par les transistors 305, 306, leurs drains étant connectés ensemble à

la source du transistor 309 et leurs sources étant connectés ensemble à la masse du circuit. Le courant IREF est appliqué sur les grilles communes des transistors 305, 306.

[0086] On notera que les X transistors associés en parallèle sont équivalents à un unique transistor de taille (W/L) égale à la somme des tailles de tous les transistors de l'ensemble 305, 306, c'est-à-dire de taille X fois supérieure si les transistors 305, 306 sont identiques.

[0087] La taille des transistors 305, 306 d'une part et 307 d'autre part, est choisie de sorte que :

- les transistors 305, 306 sont choisis de sorte que le courant IDECH0 qui les traverse lorsqu'ils sont passants soit assez faible, pour permettre la formation d'un plateau sur le signal RAMP de durée suffisamment longue pour assurer la programmation complète et certaine d'une cellule mémoire,

- le transistor 307 est choisi de taille beaucoup plus importante, de sorte que le plateau de la tension RAMP soit de durée réduite, voire nulle.

[0088] Par exemple, si les transistors 305, 306 sont équivalents à un transistor de taille W/L = 1, on peut choisir un transistor 307 de taille W/L = 10 à 100. Avec ce choix, la durée du plateau des tensions RAMP, VPP est divisée par 10 à 100 lorsque MODE est actif, elle devient ainsi négligeable par rapport à la durée de la phase ascendante de ces mêmes tensions.

[0089] Le circuit 207 permet de décharger le condensateur C :

- lorsque MODE est inactif, la décharge s'effectue avec le courant ICH = IDECH0, IDECH0 étant égal à la somme des courants circulant dans les transistors 305, 306, et

- lorsque MODE est actif, la décharge s'effectue avec le courant ICH = IDECH1, IDECH1 étant égal à la somme des courants circulant dans tous les transistors 305, 306, additionné du courant circulant dans le transistor 307.

**[0090]** Ainsi, selon le choix de l'utilisateur (MODE actif ou inactif), le plateau des tensions RAMP, VPP est soit d'une durée habituelle, équivalente à celle d'un circuit connu, soit de durée réduite voire nulle.

[0091] Le générateur de rampe 208 comprend quant à lui un transistor natif 310, quatre transistors de type N 311 à 313, 320, et un transistor N natif 321. Le générateur de rampe est réalisé selon un schéma connu ; il fournit la tension RAMP à partir de la tension HIV, et des potentiels TOP, BOT aux bornes du condensateur C.

[0092] Le transistor 310 a un drain connecté à une borne de sortie du circuit élévateur de tension 201 pour recevoir la haute tension continue HIV, et une source connectée au pôle TOP du condensateur C. Le drain du transistor 311 est connecté à la borne de sortie du circuit 201 et sa source est connectée au drain du transistor

312 dont la source est connecté au drain et à la grille du transistor 313. La source du transistor 313 est connectée à la masse. La grille du transistor 312 est connectée au pôle BOT du condensateur C, la grille du transistor 310 est connectée à la source du transistor 311, et un signal de commande POLAR est appliqué sur la grille du transistor 311. POLAR est ici égal à l'inverse de BUSY.

[0093] Le drain du transistor 320 est connecté à la grille du transistor 316 et sa source est connectée au drain du transistor 321 dont la source est connectée à la masse. Un signal de commande NOP est appliqué sur la grille de commande du transistor 320 et le courant IREF est appliqué sur la grille du transistor 321.

[0094] NOP est un signal de commande ayant les caractéristiques suivantes :

- si une seule opération (d'effacement ou de programmation) est envisagée, alors NOP est inverse du signal BUSY.

- si deux (ou plusieurs) opérations successives sont envisagées, par exemple une opération d'effacement suivie d'une opération de programmation, alors le signal BUSY est actif depuis le début de la première opération jusqu'à la fin de la deuxième opération; le signal NOP est quant à lui inverse du signal BUSY avant et pendant la première opération, pendant et après la deuxième opération, mais il devient ponctuellement égal au signal BUSY entre les deux opérations. Les signaux NOP, BUSY permettent ainsi de commander différemment les éléments du circuit 200, lorsque plusieurs opérations sont exécutées successivement, comme on le verra mieux par la suite.

**[0095]** Les transistors 320, 321 ont ainsi pour fonction de ramener la tension RAMP à 0 à la fin d'une étape d'effacement et / ou de programmation.

[0096] Le circuit de mise en forme 203 comprend deux transistors N natifs 316, 317, un transistor N 318, et un transistor P 319. Le circuit 203 est réalisé selon un schéma connu ; il produit la tension d'effacement ou de programmation VPP à partir de la tension RAMP.

[0097] La tension HIV est appliquée sur les drains des transistors 316, 317 qui sont connectés ensemble. La tension RAMP est appliquée sur les grilles des transistors 316, 317 connectées ensemble. Le drain du transistor 318 est connecté à la source du transistor 316, sa source est connectée à la masse et le signal NBUSY est appliqué sur sa grille de commande.

[0098] La source du transistor 319 et connectée à la source du transistor 317, sa grille est connectée au drain du transistor 318 et la tension d'alimentation VDD est appliquée sur son drain. La tension VPP est fournie sur la source du transistor 317.

**[0099]** En pratique, le circuit 203 joue le rôle d'un circuit de commutation, qui fournit soit la tension RAMP si la tension RAMP est supérieure à la tension d'alimen-

35

45

tation VDD, soit la tension d'alimentation VDD si la tension RAMP est inférieure à la tension VDD.

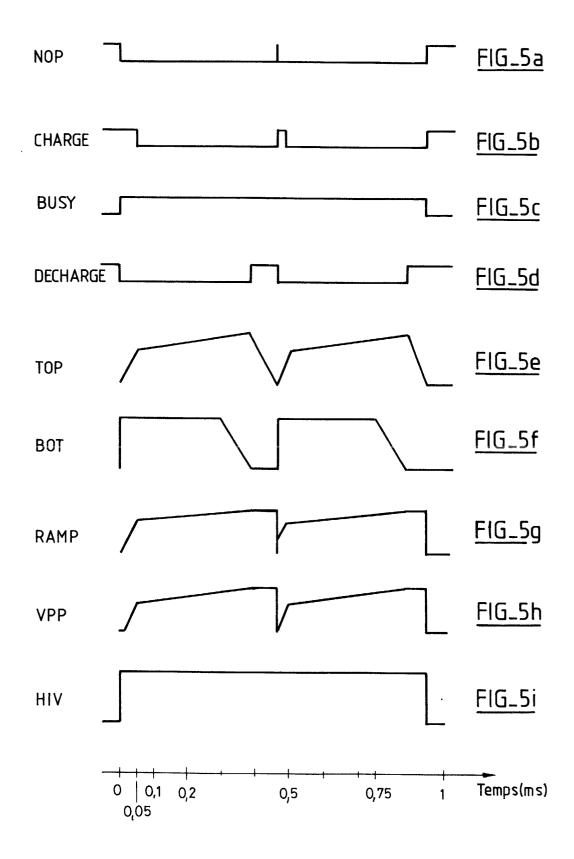

**[0100]** Les diagrammes des figures 5a à 5i montrent l'évolution des signaux de commande et des tensions en différents points du circuit de la figure 3 lorsqu'une opération d'effacement suivie d'une opération de programmation est réalisée, dans le cas suivant :

- le signal MODE est actif (égal à 1),

- HIV = 20 V

- VDD = 5 V

- VS = 10 V

- ICH0 = IREF et ICH1 = 10\*IREF

- IDECH1 = 40\*IREF et IDECH0 = IREF

- IREF = 100 nA

**[0101]** Initialement, les tensions HIV, RAMP, VPP, TOP, BOT sont nulles, les signaux de commande NOP, CHARGE, DECHARGE sont actifs, égaux à 1, et le signal BUSY est inactif, égal à 0.

[0102] Le circuit 200 est activé par le signal BUSY, qui passe à 1 à l'instant t0 = 0. Les signaux NOP, FS, DE-CHARGE passent à 0. La tension HIV grimpe immédiatement à sa valeur nominale. La tension VPP grimpe immédiatement à VDD, et la tension BOT grimpe également à sa valeur maximale, légèrement inférieure à HIVmax.

[0103] Comme CHARGE est actif, le courant de charge ICH est égal à ICH1, la charge rapide du condensateur C démarre, la tension TOP commence à grimper linéairement selon une pente rapide et la tension RAMP grimpe également selon la même pente par couplage capacitif entre la grille et la source du transistor 310. Comme RAMP < VDD, la tension VPP est égale à VDD, imposée par les transistors 317, 319.

**[0104]** Lorsque RAMP atteint la valeur VDD (au bout de 0.02 ms environ), la tension VPP devient égale à la tension RAMP, et les tensions VPP, RAMP, TOP continuent à grimper selon la même pente..

[0105] Lorsque VPP atteint VS = 10 V, le détecteur 210 désactive le signal CHARGE : le transistor 303 se bloque et le courant de charge diminue fortement : il prend la valeur ICH0. Les tensions TOP, RAMP, VPP continuent à croître, mais selon une pente beaucoup plus faible. Le potentiel BOT reste égal à sa valeur maximale.

[0106] Il arrive un moment où le potentiel TOP atteint une valeur maximale, égale à environ la tension HIV moins la chute de tension dans le transistor 310. Le condensateur continue à se charger le potentiel BOT diminue. Lorsque le potentiel BOT devient inférieur à la tension de seuil du transistor 312, le potentiel BOT annule le courant de charge ICH et rend le signal DECHARGE actif : le circuit de décharge est activé et le courant IDECH = IDECH1 est produit, qui décharge rapidement le condensateur C.

**[0107]** Le potentiel BOT atteint une valeur nulle, le potentiel TOP diminue rapidement. Par contre, la tension

RAMP reste constante, égale à sa valeur maximale car le transistor 312 est bloqué.

[0108] Lorsque le potentiel TOP devient inférieur à un potentiel seuil, il rend le signal DECHARGE inactif, la décharge du condensateur C est stoppée, si elle n'est pas déjà terminée. A cet instant précis, les signaux NOP, FS passent à 1 brièvement. En conséquence, la tension RAMP chute à 0 (transistor 320 passant) et la tension VPP chute à VDD puisque RAMP est inférieure à VDD (rôle des transistors 317, 319).

**[0109]** L'opération d'effacement se termine et l'opération de programmation commence alors : les signaux évoluent de manière similaire pour cette opération.

#### Revendications

Circuit (200) de production d'une tension d'effacement ou de programmation d'une cellule mémoire, comprenant un condensateur (C), et un circuit de décharge (207) connecté à une première borne (TOP) du condensateur (C)) pour décharger le condensateur (C),

caractérisé en ce que le circuit de décharge (207) du condensateur (C) comprend :

- un premier transistor (309), dont un drain est connecté à la première borne (TOP) du condensateur (C), pour activer le circuit de décharge (207) lorsqu'un signal de décharge (DE-CHARGE) est appliqué sur la grille de commande du premier transistor (309),

- une branche de décharge lente (305, 306) connectée à la source du premier transistor (309), pour produire un faible courant de décharge (IDECH0) du condensateur (C) lorsque le signal de décharge (DECHARGE) est reçu, et

- une branche de décharge rapide (307, 308), connectée à la source du premier transistor (309), pour produire un courant de décharge rapide (IDECH1) du condensateur (C) lorsque le signal de décharge (DECHARGE) et un signal de sélection (MODE) d'un mode de fonctionnement sont reçus simultanément.

- 2. Circuit selon la revendication 1, caractérisé en ce que la branche de décharge lente comprend un deuxième transistor (305, 306), dont un drain est connecté à la source du premier transistor (309) et dont une source est connectée à une masse du circuit, le faible courant de décharge étant proportionnel à un courant de référence (IREF) appliqué sur la grille de commande du deuxième transistor.

- 55 3. Circuit selon la revendication 2, caractérisé en ce que le deuxième transistor comprend une série de transistors (305, 306), comprenant un ou plusieurs transistors associés en parallèle, un drain commun

étant connecté à la source du premier transistor (309) et une source commune étant connectée à une masse du circuit, le fort courant de décharge étant proportionnel au courant de référence (IREF) appliqué sur une grille commune, le fort courant de décharge (IDECH1) étant supérieur au faible courant de décharge (IDECH0).

- **4.** Circuit selon la revendication 1, **caractérisé en ce que** la branche de décharge rapide comprend :

- un troisième transistor (308), dont un drain est connecté à la source du premier transistor (309), le signal de sélection de mode (MODE) étant appliqué sur la grille de commande du troisième transistor (308), et

- un quatrième transistor (307), dont un drain est connecté à une source du troisième transistor (308) et dont une source est connectée à la masse du circuit, le courant de référence (IREF) étant appliqué sur la grille de commande du quatrième transistor.

- 5. Circuit selon la revendication 4, caractérisé en ce que le quatrième transistor (307) comprend une série de transistors, comprenant un ou plusieurs transistors associés en parallèle, un drain commun étant connecté à la source du troisième transistor (308) et une source commune étant connectée à une masse du circuit, le courant de référence (IREF) étant appliqué sur une grille commune.

- 6. Circuit selon l'une des revendications 4 ou 5, caractérisé en ce que la taille du quatrième transistor (307) est supérieure à la taille du deuxième transistor (305, 306).

- Circuit selon la revendication 6, caractérisé en ce que la taille du quatrième transistor (307) est 10 à 100 fois supérieure à la taille du deuxième transistor

- 8. Circuit selon l'une des revendications 1 à 7, comprenant un circuit de charge (206) connecté à une deuxième borne (BOT) du condensateur (C), pour charger le condensateur (C), le circuit (200) étant caractérisé en ce que le circuit de charge (206) comprend :

- une branche de charge lente (301) connectée à la deuxième borne (BOT) du condensateur (C), pour produire un faible courant de charge (ICH0) lorsque un signal d'activation (BUSY) est reçu, et

- une branche de charge rapide (302, 303, 304), connectée à la deuxième borne (BOT) du condensateur (C), pour produire un fort courant de charge (ICH1) du condensateur (C) si le signal

de sélection (MODE) de mode et un signal de niveau de tension (CHARGE) sont reçus simultanément, le signal de niveau de tension (CHARGE) indiquant qu'une tension d'effacement ou de programmation (VPP) fournie par le circuit (200) de production d'une tension d'effacement ou de programmation est inférieure à une tension de seuil (VS).

- 9. Circuit selon la revendication 8, caractérisé en ce que la branche de charge rapide comprend :

- un cinquième transistor (302) dont une source est connectée à la masse,

- un sixième transistor (303), dont une source est connectée à un drain du cinquième transistor (302), le signal de niveau de tension (CHAR-GE) étant appliqué sur une grille de commande du sixième transistor (303), et

- un septième transistor (304), dont une source est connectée à un drain du sixième transistor (303), et dont un drain est connecté à la deuxième borne (BOT) du condensateur (c), le signal de sélection de mode (MODE) étant appliqué sur une grille de commande du septième transistor (304).

- **10.** Circuit selon l'une des revendications 1 à 9, caractérisé en ce qu'il comprend également :

- un circuit (208) de génération d'une rampe de tension, pour produire une rampe de tension (RAMP), à partir des potentiels sur la première borne (TOP) et la deuxième borne (BOT) du condensateur (C), et

- un circuit de mise en forme (203), comprenant un huitième transistor (317), une haute tension (HIV) étant appliquée sur une borne du huitième transistor (317), et la tension d'effacement ou de programmation (VPP) étant fournie sur une autre borne du huitième transistor (317),

le huitième transistor étant de type P.

11. Procédé de production d'une tension d'effacement ou de programmation d'une cellule mémoire, au cours duquel on charge un condensateur (C) en appliquant un courant de charge sur une deuxième borne (BOT) au cours d'une première étape, puis on décharge le condensateur (C) en appliquant un courant de décharge sur une première borne (TOP) du condensateur (C) au cours d'une deuxième étape,

le procédé étant caractérisé en ce que, au cours de la deuxième étape, le courant de décharge prend une faible valeur (IDECH0) ou une forte valeur (IDECH1) supérieure à la première valeur (IDECH0), en fonction d'un mode (MODE) de fonctionnement.

# Office européen RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande EP 02 36 6003

| Catégorie                                                                                                                                                                                         | Citation du document avec<br>des parties pertir                                          | indication, en cas de besoin,<br>nentes                                      | Revendication concernée                                                                                                                                                                   | CLASSEMENT DE LA<br>DEMANDE (Int.Cl.7)       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| A                                                                                                                                                                                                 | EP 0 762 428 A (SGS<br>MICROELECTRONICS)<br>12 mars 1997 (1997-                          | THOMSON<br>03-12)<br>28 - colonne 10, lign                                   | 1-3,5,<br>8-11                                                                                                                                                                            | G11C16/12                                    |

| A                                                                                                                                                                                                 | 24 mars 1999 (1999-                                                                      | MICROELECTRONICS SA) 03-24) 37 - colonne 7, ligne                            |                                                                                                                                                                                           |                                              |

| A                                                                                                                                                                                                 | FR 2 770 326 A (SGS THOMSON MICROELECTRONICS) 30 avril 1999 (1999-04-30) * figures 4,5 * |                                                                              | 1,2,8,                                                                                                                                                                                    |                                              |

|                                                                                                                                                                                                   |                                                                                          |                                                                              |                                                                                                                                                                                           | DOMAINES TECHNIQUES<br>RECHERCHES (Int.Cl.7) |

|                                                                                                                                                                                                   |                                                                                          |                                                                              |                                                                                                                                                                                           | G11C                                         |

|                                                                                                                                                                                                   |                                                                                          |                                                                              |                                                                                                                                                                                           |                                              |

| Le pr                                                                                                                                                                                             | ésent rapport a été établi pour tou                                                      | utes les revendications                                                      |                                                                                                                                                                                           |                                              |

| Lieu de la recherche                                                                                                                                                                              |                                                                                          | Date d'achèvement de la recherche<br>6 août 2002                             | Cum                                                                                                                                                                                       | Examinateur<br>Mrings, A                     |

| CATEGORIE DES DOCUMENTS CITES  X : particulièrement pertinent à lui seul Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie A : arrière—plan technologique |                                                                                          | S T: théorie ou p<br>E: document d<br>date de dép<br>avec un D: cité dans la | T: théorie ou principe à la base de l'Invention E: document de brevet antérieur, mais publié à la date de dépôt ou après cette date D: cité dans la demande L: cité pour d'autres raisons |                                              |

# ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

EP 02 36 6003

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Lesdits members sont contenus au fichier informatique de l'Office européen des brevets à la date du Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

06-08-2002

| Document brevet cité<br>au rapport de recherche |   | Date de publication |    | Membre(s) de la<br>familie de brevet(s) | Date de<br>publication       |

|-------------------------------------------------|---|---------------------|----|-----------------------------------------|------------------------------|

| P 0762428                                       | A | 12-03-1997          | FR | 2738386 A1                              | 07-03-1997                   |

|                                                 |   |                     | DE | 69600963 D1                             | 17-12 <b>-</b> 19 <b>9</b> 8 |

|                                                 |   |                     | DE | 69600963 T2                             | 01-04-1999                   |

|                                                 |   |                     | EP | 0762428 A1                              | 12-03-1997                   |

|                                                 |   |                     | US | 6034895 A                               | 07-03-2000                   |

|                                                 |   |                     | US | 5883833 A                               | 16-03-1999                   |

| P 0903750                                       | А | 24-03-1999          | FR | 2768846 A1                              | 26-03-1999                   |

|                                                 |   |                     | DE | 69800399 D1                             | 21-12-2000                   |

|                                                 |   |                     | DE | 69800399 T2                             | 15-03-2001                   |

|                                                 |   |                     | EP | 0903750 A1                              | 24-03-1999                   |

|                                                 |   |                     | US | 5995416 A                               | 30-11-1999                   |

| R 2770326                                       | Α | 30-04-1999          | FR | 2770326 A1                              | 30-04-1999                   |

|                                                 |   |                     | US | 6040994 A                               | 21-03-2000                   |

|                                                 |   |                     |    |                                         |                              |

|                                                 |   |                     |    |                                         |                              |

EPO FORM P0480

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82