(11) EP 1 248 175 A2

(12)

## **EUROPÄISCHE PATENTANMELDUNG**

(43) Veröffentlichungstag: 09.10.2002 Patentblatt 2002/41

(51) Int Cl.<sup>7</sup>: **G05F 3/26**, G05F 1/613

(21) Anmeldenummer: 02007177.5

(22) Anmeldetag: 28.03.2002

(84) Benannte Vertragsstaaten:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE TR

Benannte Erstreckungsstaaten:

AL LT LV MK RO SI

(30) Priorität: 30.03.2001 DE 10115813

(71) Anmelder: Infineon Technologies AG 81669 München (DE)

(72) Erfinder: Melcher, Gebhard 8045 Weinitzen (AT)

(74) Vertreter: Epping Hermann & Fischer Ridlerstrasse 55 80339 München (DE)

## (54) Parallelspannungsregler

(57) Die Erfindung betrifft einen Parallelspannungsregler mit einem steuerbaren Lastelement (MN2), das mit den Ausgangsklemmen des Parallelspannungsreglers verbunden ist, und eine Referenzspannungsquelle ( $V_{REF}$ ) zur Festlegung der Sollausgangsspannung. Der erfindungsgemäße Parallelspannungsregler ist dadurch gekennzeichnet, daß eine schnelle Regelung über zwei Stromspiegel (5, 6) erfolgt, wobei der erster

Stromspiegel (5) mit der Referenzspannungsquelle ( $V_{REF}$ ) im Steuerzweig des ersten Stromspiegels (5) liegt, der gesteuerte Zweig des ersten Stromspiegels (5) einerseits mit der Ausgangsspannung ( $V_{OUT}$ ) und andererseits mit dem Steuerzweig des zweiten Stromspiegels (6) verbunden ist und das steuerbare Lastelement (MN2) durch den gesteuerten Zweig des zweiten Stromspiegels (6) gebildet ist.

# FIG 2

EP 1 248 175 A2

#### Beschreibung

[0001] Die Erfindung betrifft einen Parallelspannungsregler mit einem steuerbaren Lastelement, das mit den Ausgangsklemmen des Parallelspannungsreglers verbunden ist, einer Referenzspannungsquelle zur Festlegung der Sollausgangsspannung und einer mit dem steuerbaren Lastelement und der Referenzspannungsquelle verbundenen Regelvorrichtung.

[0002] Parallelspannungsregler werden üblicherweise in den Fällen verwendet, in denen ein Längsspannungsabfall, wie er bei einem Serienspannungsregler auftritt, nicht erwünscht ist. Zwar ist der Längsspannungsabfall bei Vollaussteuerung der üblicherweise verwendeten Transistoren relativ gering, jedoch ist der Restspannungsabfall in bestimmten Anmwendungsfällen immer noch zu groß.

[0003] Bei Parallelreglern wird parallel zur Last ein steuerbares Lastelement angeordnet, durch das die Höhe der Ausgangsspannung durch Beeinflussung des Spannungsabfalls am Innenwiderstand der Quelle geregelt werden kann. Je größer der Strom durch das parallele Lastelement ist, desto größer ist der Spannungsabfall am Innenwiderstand und desto kleiner demzufolge die Spannung an den Ausgangsklemmen. In einer günstigen und vielfach angewandten Schaltung ist das steuerbare Lastelement durch einen MOSFET gebildet, der durch einen Operationsverstärker angesteuert wird. Die Ausgangsspannung, die bei einem Parallelregler gleich der Eingangsspannung ist, wird auf einen Eingang des Operationsverstärkers geführt, während der andere Eingang mit einer Referenzspannung beaufschlagt ist. Bei einer Abweichung der Ausgangsspannung von der Referenzspannung wird das steuerbare Lastelement, also der MOSFET, solange nachgeregelt, bis die Spannung wieder der Referenzspannung entspricht.

[0004] Parallelregler werden beispielsweise häufig bei kontaktlosen Chipkarten eingesetzt, wobei die Last im wesentlichen aus einem Mikrocontroller besteht. Die Stromquelle wird durch eine Spule gebildet, in der ein von einem Schreib-/Lesegerät erzeugtes Magnetfeld eine Spannung induziert, wobei die Höhe der übertragenen Leistung in starkem Maße davon abhängt, wie weit die kontaktlose Chipkarte von dem Schreib-/Lesegerät entfernt ist. Einerseits besteht das Bestreben, eine möglichst große Reichweite zu erzielen, daher ist ein Serienregler bei kontaktlosen Chipkarten ungeeignet, da der Spannungsabfall am Regeltransistor bereits die Reichweite verkürzt. Andererseits werden sehr hohe Spannungen induziert, wenn sich die kontaktlose Chipkarte in großer Nähe zu dem Schreib/Lesegerät befindet. In diesem Fall wird bei Verwendung eines Parallelspannungswandlers ein verhältnismäßig großer Strom über das steuerbare Lastelement aufgenommen, wobei sich die dadurch entstehenden Verluste nicht nachteilig auswirken, da in diesem Betriebsfall ohnehin genügend Leistung für den Mikrocontroller vorhanden ist.

[0005] Bekannte Parallelspannungsregler weisen jedoch den Nachteil auf, daß die Regelung über den Operationsverstärker verhältnismäßig langsam ist. Bei schnellen Laständerungen ist der Regelkreis nicht in der Lage, diese Schwankungen auszuregeln. Zur Erhöhung der Schnelligkeit des Operationsverstärkers besteht die Möglichkeit, dessen Ruhestrom auf einem großen Wert festzulegen. Dieser hohe Ruhestrom verschlechtert allerdings wiederum die Reichweite der kontaktlosen Chipkarte, so daß keine Verbesserung gegenüber einem Serienspannungsregler erzielt wird.

**[0006]** Die Aufgabe der vorliegenden Erfindung liegt also darin, einen Parallelspannungsregler anzugeben, der auch für sehr schnelle Laständerungen geeignet ist und einen geringen Ruhestrombedarf aufweist. Darüber hinaus soll der Spannungsregler einfach und somit platzsparend im Aufbau sein.

[0007] Diese Aufgabe wird durch einen Parallelspannungsregler der eingangs genannten Art gelöst, der dadurch gekennzeichnet ist, daß die Regelvorrichtung einen ersten Stromspiegel und einen zweiten Stromspiegel aufweist, wobei die Referenzspannungsquelle im Steuerzweig des ersten Stromspiegels liegt, der gesteuerte Zweig des ersten Stromspiegels einerseits mit der Ausgangsspannung und andererseits mit dem Steuerzweig des zweiten Stromspiegels verbunden ist und das steuerbare Lastelement durch den gesteuerten Zweig des zweiten Stromspiegels gebildet ist.

[0008] Durch die erfindungsgemäße Ausgestaltung des Parallelspannungsreglers ist der Regler sehr schnell, wobei gegenüber einem Operationsverstärker nachteilig ist, daß der Stromverstärkungsfaktor verhältnismäßig gering ist. Daher ist die Genauigkeit der geregelten Ausgangsspannung verhältnismäßig gering, was jedoch im beschriebenen Anwendungsfall ohne Bedeutung ist, da die zulässigen Toleranzen der Spannungsversorgung eines Mikrocontrollers relativ groß sind. Dafür können große Lastschwankungen, die innerhalb von kürzester Zeit von wenige Milliampère bis in den Ampèrebereich steigen können, aufgrund der großen Schnelligkeit des Regelkreises in einer ausreichenden Genauigkeit ausregelbar.

[0009] Ein weiterer Vorteil der erfindungsgemäßen Gestaltung des Parallelspannungsreglers liegt in der großen inhärenten Stabilität. Die Regelfunktion besitzt neben einem Lastpol, der dadurch begründet ist, daß es sich nicht um eine rein ohmsche Last handelt, sondern auch Kapazitäten bzw. parasitäre Kapazitäten vorhanden sind, nur einen weiteren Pol. Aufgrund des niederohmigen Knotens zwischen dem ersten und zweiten Stromspiegel ist dieser Pol sehr hochfrequent. Instabilitäten könnten somit nur bei sehr hohen Frequenzen auftreten, die außerhalb des üblicherweise zu erwartenden Bereichs liegen.

**[0010]** Jede der vorteilhaften Eigenschaften ist alleine für sich auch mit anderen Schaltungsvarianten nach dem Stand der Technik erzielbar. Der Vorteil der vorliegenden Schaltung gemäß der Erfindung liegt jedoch

20

darin, daß die Freiheit von Spannungsverlust nach dem Parallelreglerprinzip in Verbindung mit einem niedrigen Ruhestrom, hohem maximalen Laststrom und hoher Regelbandbreite möglich ist.

**[0011]** Die Erfindung wird nachfolgend anhand eines Ausführungsbeispiels näher erläutert. Es zeigt:

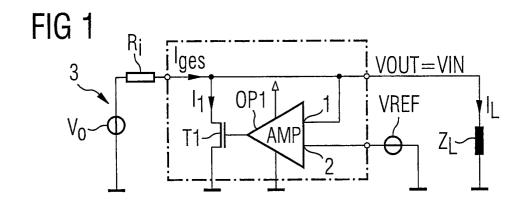

Figur 1 einen Parallelspannungsregler nach dem Stand der Technik,

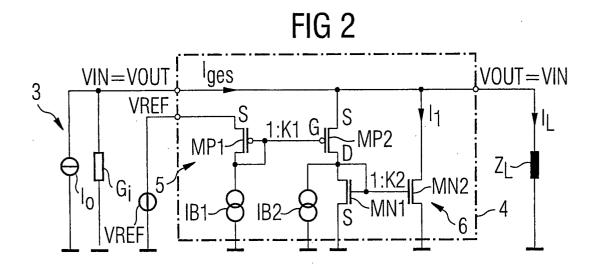

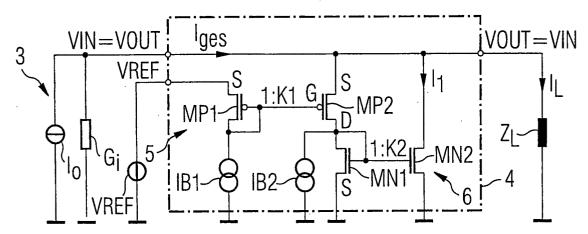

Figur 2 ein erstes Ausführungsbeispiel des erfindungsgemäßen Parallelspannungsreglers,

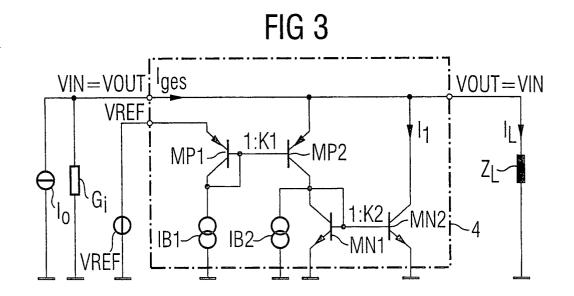

Figur 3 ein zweites Ausführungsbeispiel eines erfindungsgemäßen Parallelspannungsreglers,

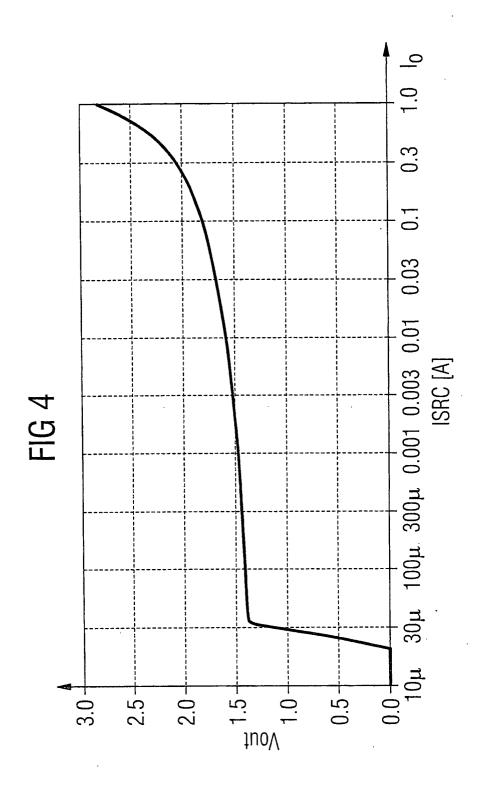

Figur 4 eine Kennlinie der Ausgangsspannung und

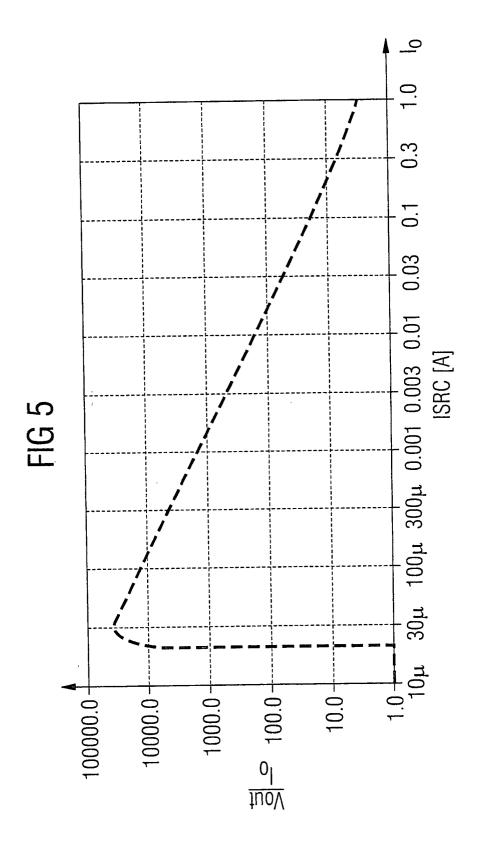

Figur 5 eine Widerstandskennlinie eines steuerbaren Lastelementes.

[0012] In der Figur 1 ist ein Parallelspannungsregler nach dem Stand der Technik dargestellt. Ein M0SFET T1 bildet ein steuerbares Lastelement. Der M0SFET T1 wird durch einen Operationsverstärker OP1 angesteuert. An dessen erstem Eingang 1 liegt die Ausgangsspannung V<sub>OLIT</sub> an. Der andere Eingang 2 ist mit einer Referenzspannung  $V_{\mbox{\scriptsize REF}}$  beaufschlagt. Bei einer Abweichung der Ausgangsspannung von dem durch V<sub>RFF</sub> vorgegebenen Sollwert wird der MOSFET T1 durch den Operationsverstärker OP1 so angesteuert, daß der Strom I1 durch den MOSFET T1 zunimmt (bei steigendem  $V_{OUT}$ ). Der Gesamtstrom  $I_{ges}$ , der von der Schaltung aufgenommen wird, steigt nun entsprechend dem Anstieg von I1 an. Dadurch fällt an einem Innenwiderstand Ri einer externen Spannungsquelle 3 eine zusätzliche Spannung ab, um die sich die Ausgangsspannung V<sub>OUT</sub> verringert. Bei nun wieder sinkender Ausgangsspannung V<sub>OUT</sub> wird der Strom I1 durch den MOSFET T1 heruntergeregelt, so daß der Ausgangszustand wieder hergestellt ist.

[0013] In der Figur 2 ist nun ein erfindungsgemäßer Parallelspannungsregler dargestellt. Parallel zu einer Last ZL befindet sich wiederum ein steuerbares Lastelement MN2, das ebenfalls als MOSFET ausgebildet ist. Der Gesamtstrom I<sub>ges</sub> am Eingang des Spannungsreglers 4 setzt sich im wesentlichen aus dem Ausgangsstrom I<sub>I</sub> und dem Strom I1 durch das steuerbare Lastelement MN2 zusammen. Durch zwei p-Kanal-FETs ist ein erster Stromspiegel 5 gebildet. Dessen Steuertransistor MP1 ist mit einer externen Referenzspannungsquelle V<sub>RFF</sub> verbunden. Der gesteuerte Transistor MP2 des ersten Stromspiegels 5 ist sourceseitig mit der auf V<sub>OUT</sub> liegenden Ausgangsklemme und drainseitig mit einem zweiten Stromspiegel 6 verbunden. Der zweite Stromspiegel 6 ist durch zwei n-Kanal-FETs MN1 und MN2 gebildet, wobei MN2 das steuerbare Lastelement ist. Während durch eine erste Stromquelle I<sub>B1</sub> der Strom

durch den Steuertransistor MP1 des ersten Stromspiegels 5 bestimmt wird, dient eine zweite Stromquelle  $I_{B2}$ , die zwischen ein Bezugspotential und den Drainanschluß des gesteuerten Transistors MP2 des ersten Stromspiegels 5 geschaltet ist, dazu, die Transistoren im aktiven Bereich zu halten. Ohne diese Maßnahme würde sich die Bandbreite der Schaltung erheblich verringern, da immer zuerst die Ladungen wieder aufgebaut werden müßten, die zur Steuerung des Stromes erforderlich sind.

[0014] Die Funktionsweise der Schaltung wird im folgenden unter der Annahme erläutert, daß die Ausgangsspannung VOLIT ansteigt. Durch das Ansteigen der Spannung V<sub>OUT</sub> vergrößert sich die Gate-Source-Spannung des Transistors MP2, da die Gatespannung konstant bleibt. Dies hat eine Erhöhung des Stromflusses durch den Transistor MP2 zur Folge. Entsprechend steigt auch der Strom durch den Transistor MN1 an, wobei dieser Wert daraufhin in den Transistor MN2, also das Lastelement, gespiegelt wird. Durch eine Erhöhung der Ausgangsspannung V<sub>QUT</sub> steigt somit der Strom I1 durch das steuerbare Lastelement an, der daraus folgende Anstieg des Gesamtstromes Iqes erhöht den Spannungsfall am Innenwiderstand der Quelle 3, die in der Figur 2 als Stromquelle I<sub>0</sub> mit parallel geschaltetem Leitwert Gi dargestellt ist. Dies ist gleichbedeutend mit einem Abfall der Ausgangsspannung VOLIT, bis der Ausgangszustand wieder hergestellt ist.

[0015] Bei einem Aufbau der Schaltung mit MOSFETs gemäß der Figur 2 berechnet sich der Strom I1 aus der Änderung der Gate-Source-Spannung  $U_{GS}$ . Der Strom durch den Transistor MP2 beträgt  $g_m \times \Delta U_{GS}$ , wobei  $g_m$  die Transkonduktanz des Transistors MP2 ist. Der Strom I1 berechnet sich nun zu diesem Wert multipliziert mit dem Spiegelungsfaktor k2 des zweiten Stromspiegels 6.

**[0016]** Die Figur 2 zeigt nur eine Realisierungmöglichkeit des erfindungsgemäßen Parallelspannungsreglers. Selbstverständlich sind auch andere Transistortypen einsetzbar, beispielsweise Bipolartransistoren, wobei eine solche Anordnung in der Figur 3 dargestellt ist.

[0017] Bipolartransistoren weisen gegenüber Feldefekttransistoren den Vorteil auf, daß der Kollektorstrom I<sub>C</sub> in einer exponentiellen Funktion von dem Basisstrom I<sub>B</sub> abhängig ist. Die entsprechende Kennlinie bei MOS-FETs ist dagegen quadratisch. Dadurch ergeben sich für den Bipolartranistor Vorteile im Regelverhalten. Bei der heute verwendeten Technologie sind jedoch in der Regel nur FETs verfügbar, weshalb trotz funktioneller Nachteile aus Kostengründen auf FETs zurückgegriffen wird. Nur in wenigen Sonderfällen werden trotzdem Bipolartransistoren eingesetzt. Die Schaltung der Figur 3 entspricht bis auf die Tatsache, daß statt p-Kanal-FETs pnp-Transistoren verwendet werden und statt n-Kanal-FETs npn-Transistoren zum Einsatz kommen, der Schaltungsanordnung von Figur 2.

[0018] Die Figur 4 zeigt nun die Kennlinie der Ausgangsspannung gegenüber dem Eingangsstrom. Zu

beachten ist dabei, daß der Strom auf der X-Achse logarithmisch aufgetragen ist. Über vier Dekaden ist eine verhältnismäßig gute Spannungsstabilität zu beobachten, wobei die Abweichung von der Nennspannung innerhalb des Toleranzbereiches eines Mikrocontrollers im eingangs genannten Anwendungsfall bei kontaktlosen Chipkarten liegt.

**[0019]** Die Figur 5 zeigt den Quotienten aus der Ausgangsspannung  $V_{out}$  und dem Eingangsstrom  $I_0$  aufgetragen über dem Eingangsstrom  $I_0$ . Dies entspricht quasi dem Widerstand des steuerbaren Lastelementes MN2 in Paralleschaltung mit der Last  $Z_L$ . Bei steigendem Strom sinkt der Widerstand ein einem großen Bereich linear, wobei die Linearität ebenfalls gemäß der Ausgangsspannung über vier Dekaden erhalten bleibt.

#### Bezugszeichenliste

#### [0020]

- 1 erster Eingang des Operationsverstärkers

- 2 zweiter Eingang des Operationsverstärkers

- 3 Quelle

- 4 Parallelspannungsregler

- 5 erster Stromspiegel

- 6 zweiter Stromspiegel

MP1 Steuertransistor des ersten Stromspiegels

MP2 gesteuerter Transistor des ersten Stromspiegels

gels

MN1 Steuertransistor des zweiten Stromspiegels

MN2 gesteuerter Transistor des zweiten Stromspiegels

Z<sub>L</sub> Last

V<sub>RFF</sub> Referenzspannungsquelle

$I_{B1}$  erste Stromquelle  $I_{B2}$  zweite Stromquelle

#### Patentansprüche

Parallelspannungsregler mit einem steuerbaren Lastelement (MN1), das mit den Ausgangsklemmen des Parallelspannungsreglers verbunden ist, einer Referenzspannungsquelle (V<sub>REF</sub>) zur Festlegung der Sollausgangsspannung und einer mit dem steuerbaren Lastelement (MN1) und der Referenzspannungsquelle (V<sub>REF</sub>) verbundenen Regelvorrichtung,

dadurch gekennzeichnet, daß die Regelvorrichtung einen ersten Stromspiegel (5) und einen zweiten Stromspiegel (6) aufweist, wobei

- die Referenzspannungsquelle (V<sub>REF</sub>) im Steuerzweig des ersten Stromspiegels (5) liegt,

- der gesteuerte Zweig des ersten Stromspiegels

(5) einerseits mit der Ausgangsspannung

(V<sub>OUT</sub>) und andererseits mit dem Steuerzweig des zweiten Stromspiegels (6) verbunden ist und

das steuerbare Lastelement (MN2) durch den gesteuerten Zweig des zweiten Stromspiegels (6) gebildet ist.

## Parallelspannungsregler nach Anspruch 1, dadurch gekennzeichnet, daß

der erste Stromspiegel (5) mit zwei p-Kanal-FETs und der zweite Stromspiegel (6) mit zwei n-Kanal-FESTs aufgebaut ist, wobei

- bei dem Steuertransistor (MP1) des ersten Stromspiegels (5) der Sourceanschluß mit der Referenzspannungsquelle (V<sub>REF</sub>) und der Drainanschluß mit dem Gate-Anschluß und einer ersten Stromquelle (I1) verbunden ist,

- bei dem gesteuerten Transistor (MP2) des ersten Stromspiegels der Source-Anschluß mit der Ausgangsspannung (V<sub>OUT</sub>) und der Drainanschluß mit dem Drainschluß des Steuertransistors (MN1) des zweiten Stromspiegels verbunden ist,

- bei dem Steuertransistor (MN1) des zweiten Stromspiegels (6) der Drain-Anschluß zusätzlich mit dem Gate-Anschluß verbunden ist und

- bei dem Steuertransistor (MN1) des zweiten Stromspiegels der Source-Anschluß mit einem Bezugspotential verbunden ist.

### Parallelspannungsregler nach Anspruch 2, dadurch gekennzeichnet, daß

mit dem Drain-Anschluß des gesteuerten Transistors (MP2) des ersten Stromspiegels (5) zusätzlich eine zweite Stromquelle (I<sub>B2</sub>) verbunden ist.

4

20

15

25

30

35

40

50

55