# Europäisches Patentamt European Patent Office Office européen des brevets

(11) **EP 1 248 176 A1**

(12)

# **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication: 09.10.2002 Bulletin 2002/41

(51) Int CI.7: **G05F 3/26**

(21) Numéro de dépôt: 02290442.9

(22) Date de dépôt: 22.02.2002

(84) Etats contractants désignés:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE TR

Etats d'extension désignés:

**AL LT LV MK RO SI**

(30) Priorité: 26.02.2001 FR 0102579

(71) Demandeur: STMicroelectronics S.A. 92120 Montrouge (FR)

- (72) Inventeur: Sirito-Olivier, Philippe 38120 Saint Egreve (FR)

- (74) Mandataire: Brykman, Georges c/o Brevalex

3, rue du Docteur Lancereaux

75008 Paris (FR)

- (54) Source de courant apte à fonctionner sous faible tension d'alimentation et à variation de courant avec la tension d'alimentation quasi nulle

(57) Il s'agit d'une source de courant destinée à être montée entre deux bornes d'alimentation (20, 21). Elle comporte un miroir de courant (Mi) et un coeur (C1) connectés l'un à l'autre. Le miroir (Mi) comporte un transistor pilote (T5) et au moins un transistor de recopie (T4). Le coeur (C1) comporte un premier transistor (T1), un second transistor (T2) et une résistance (R1).

Le premier transistor (T1) du coeur (C1) et le premier transistor (T4) de recopie reliés forment une première branche (25). La résistance (R1) et un second

transistor de recopie (T3) reliés forment une seconde branche (24). Le transistor pilote (T5) et le second transistor du coeur (T2) reliés forment une troisième branche (26). Ces branches sont à connecter entre les deux bornes d'alimentation. Le premier transistor (T1) du coeur est relié à la seconde branche (24) entre la résistance (R1) et le second transistor (T3) de recopie. Le second transistor (T2) du coeur est relié à la première branche (25) entre le premier transistor (T1) du coeur et le premier transistor de recopie (T4).

<u>Fig. 2</u>

#### Description

20

30

35

50

#### **DOMAINE TECHNIQUE**

[0001] La présente invention est relative à une source de courant apte à fonctionner sous faible tension d'alimentation et à variation de courant avec la tension d'alimentation quasi nulle

**[0002]** Ce type de source de courant est utilisé notamment pour polariser des circuits, par exemple des amplificateurs opérationnels, qui sont destinés à fonctionner sur de larges plages de tension. On peut penser par exemple à des appareils portables qui peuvent être alimentés soit avec batterie, soit sur secteur. Ces appareils peuvent être des appareils de radio, des appareils de lecture ou de reproduction du son. Lorsque ces appareils fonctionnent sur batterie la tension d'alimentation est relativement basse, de l'ordre de 3V par exemple et elle diminue avec l'usure des batteries jusqu'à atteindre environ 2V voire moins. Lorsque ces appareils fonctionnent sur secteur, la tension d'alimentation est de l'ordre de 5V. Il peut y avoir un rapport 2 voire 3 entre les deux tensions d'alimentation.

#### ETAT DE LA TECHNIQUE ANTERIEURE

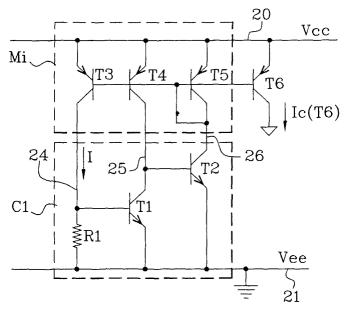

[0003] Actuellement les sources de courant employées dans ce type d'application sont telles que celle illustrée sur la figure 1.

[0004] Cette source de courant, réalisée dans l'exemple en technologie bipolaire, est connectée entre deux bornes d'alimentation, l'une 20 portée à un potentiel haut V<sub>CC</sub> et l'autre 21 portée à un potentiel bas Vee, généralement la masse.

[0005] La source comporte un coeur C et un miroir M de courant montés en série entre les deux bornes d'alimentation 20, 21. Le coeur C est la partie de la source qui régit l'équation du courant de la source. Ici, il s'agit d'une source dite en V<sub>BE</sub>/R. Le coeur C comporte un transistor Q1, une résistance R de fixation du courant et éventuellement un transistor additionnel Q2. Le coeur C est connecté à l'une des bornes d'alimentation 21, ici la borne 21 portée au potentiel Vee. Les transistors Q1, Q2 du coeur sont de même type, ici de type NPN.

**[0006]** Dans la suite de la description, une tension notée  $V_{BE}$  représente une tension base-émetteur et une tension notée  $V_{CE}$  représente une tension collecteur-émetteur.

[0007] Le miroir M comporte un transistor pilote Q5 et au moins un transistor de recopie Q4. Il est relié à l'autre borne d'alimentation 20, dans l'exemple celle portée au potentiel V<sub>CC</sub>. Les transistors de miroir Q4, Q5, de même type, ici de type PNP, sont complémentaires à ceux du coeur C. Ils sont réalisés en même temps et sont donc identiques.

**[0008]** Le transistor Q1 est connecté entre la borne d'alimentation 21 et le transistor de recopie Q4 du miroir M. Ces deux transistors Q1, Q4 forment entre les deux bornes d'alimentation 20, 21 une branche asservie 22.

[0009] La base du transistor Q1 est connectée à une première extrémité de la résistance R de fixation du courant, la seconde extrémité de la résistance R est connectée à la borne d'alimentation 21 portée au potentiel Vee. La première extrémité de la résistance R est aussi reliée au transistor pilote Q5 du miroir M via le transistor additionnel Q2. La résistance R de fixation du courant, le transistor additionnel Q2 et le transistor pilote Q5 forment entre les deux bornes d'alimentation 20, 21 une branche pilote 23.

[0010] Le transistor Q1 est monté en diode, c'est à dire que sa base est reliée à son collecteur via le transistor additionnel Q2.

[0011] Le miroir M est connecté à l'autre borne d'alimentation 20, ici celle portée au potentiel  $V_{CC}$ .

**[0012]** Le transistor de recopie Q4 du miroir M a son émetteur connecté à la borne d'alimentation 20 portée au potentiel V<sub>CC</sub>, son collecteur connecté au transistor Q1 du coeur C et sa base connectée à la base du transistor pilote Q5 du miroir M.

[0013] Le transistor pilote Q5 du miroir M a sa base connectée à la base du transistor de recopie Q4 du miroir M et à son collecteur. Il est monté en diode. Son collecteur est aussi relié à la résistance R du coeur C via le transistor additionnel Q2. L'émetteur du transistor pilote Q5 est connecté à la borne d'alimentation 20 portée au potentiel V<sub>CC</sub>.

**[0014]** Le courant de polarisation de la source est accessible au niveau du collecteur d'un transistor de sortie Q6 qui est monté en transistor de recopie vis à vis du miroir M. Son émetteur est connecté à la borne d'alimentation 20 portée au potentiel V<sub>CC</sub> et sa base à la base du transistor pilote Q5 du miroir M. Le transistor de sortie Q6 est identique au transistor pilote Q5.

[0015] Cette source de polarisation est décrite page 324 de l'ouvrage « Analysis and Design of Analog Integrated Circuit» de PR GRAY et R.G. MEYER, 3ème Edition.

[0016] Au premier ordre, on peut considérer que dans le coeur C, le courant I qui traverse la résistance R et qui correspond au courant collecteur du transistor Q2 est le même que celui qui circule dans la branche 22 par effet miroir. [0017] On a donc :

$$I = (V_T/R) \times ln(I/I_S)$$

avec V<sub>T</sub> tension thermique valant kT/q, dans ce rapport k est la constante de Boltzmann, T la température en degré Kelvin et q la charge de l'électron. I<sub>S</sub> représente le courant de saturation du transistor Q2.

[0018] La connaissance de l permet de déterminer l'expression du courant de polarisation lc(Q6) de la source au niveau du transistor de sortie Q6 :

$$Ic(Q6) = I \times (1+V_{CF}(Q6)/V_{FA}(Q6))/(1+V_{CF}(Q5)/V_{FA}(Q5))$$

avec  $V_{EA}(Q6)$  et  $V_{EA}(Q5)$  les tensions d'Early des transistors Q6 et Q5 respectivement. Elles sont égales, puisque les transistors Q6 et Q5 sont de même type PNP et identiques.

**[0019]** La tension  $V_{CE}(Q5)$  est égale à  $V_{BE}(Q5)$  puisque le transistor pilote Q5 est monté en diode. La tension  $V_{BE}(Q5)$  reste sensiblement constante lorsque  $V_{CC}$  varie.

[0020] Le courant lc(Q6) varie dans le même sens que la différence de potentiel entre les deux bornes d'alimentation 20, 21 car V<sub>CE</sub>(Q6) varie dans le même sens que cette différence de potentiel. Cette différence de potentiel est dans la suite de l'exposé assimilée à V<sub>CC</sub> puisqu'on a supposé que la borne d'alimentation 21 était au potentiel de la masse. [0021] Si l'on veut obtenir un courant de polarisation de sens inverse au courant lc(Q6) c'est-à-dire complémentaire au courant lc(Q6), on peut ajouter un second transistor de sortie Q3 monté en miroir avec le transistor Q1 du coeur. Dans ce second miroir, le transistor Q1 est le transistor pilote et le transistor Q3 est un transistor de recopie.

**[0022]** Ce transistor de recopie Q3 a sa base connectée à la base du transistor Q1, son émetteur connecté à la première borne d'alimentation 21 portée au potentiel Vee et son collecteur forme une autre sortie de la source.

[0023] Le courant collecteur du transistor Q3 est donné par :

10

20

25

35

40

45

50

$$I_{C}(Q3)=Ix(1+V_{CE}(Q3)/V_{EA}(Q3))/(1+V_{CE}(Q1)/V_{EA}(Q1))$$

$$I_{C}(Q3)=Ix(1+V_{CE}(Q3)/V_{EA}(Q3))/(1+(V_{BE}(Q1)+V_{BE}(Q2))/V_{EA}(Q1))$$

$V_{EA}(Q3)$  et  $V_{EA}(Q1)$  sont les tensions d'Early des transistors Q3 et Q1 respectivement, elles sont égales et correspondent à des tensions d'Early de transistors NPN puisque Q1 et Q3 sont tous les deux des transistors NPN identiques.

[0024] Ici encore  $V_{BE}(Q1)$  et  $V_{BE}(Q2)$  restent sensiblement constants lorsque  $V_{CC}$  varie mais  $V_{CE}(Q3)$  varie dans le même sens que  $V_{CC}$  et donc  $I_{CC}(Q3)$  varie dans le même sens que  $V_{CC}$ .

[0025] Les caractéristiques des circuits électroniques polarisés par une source de courant sont intrinsèquement liées à la consommation en courant de leurs composants. Par exemple, le gain d'un transistor est d'autant plus fort que le courant qui le traverse est fort. On cherche à avoir des caractéristiques les plus constantes possibles pour les maîtriser et donc à ce que le courant de polarisation soit le plus constant possible quelle que soit la valeur de la tension d'alimentation.

[0026] La source de courant de polarisation de la figure 1 ne donne pas toute satisfaction à ce point de vue.

[0027] De plus, cette source de courant de polarisation ne démarre que lorsque la tension d'alimentation  $V_{CC}$  atteint une valeur relativement élevée.

**[0028]** Cette caractéristique présente un inconvénient lorsque la tension d'alimentation provient d'une batterie et que celle-ci est relativement déchargée, la source de courant de polarisation risque de ne pas démarrer.

[0029] La tension d'alimentation minimale pour faire démarrer la source de courant est donnée par :

$$V_{CCmin} = V_{BE}(Q1) + V_{BE}(Q2) + V_{CEsat}(Q4)$$

soit 2V<sub>BE</sub> + V<sub>CEsat</sub>.

[0030] Cette équation provient de la branche 22. Dans la branche 23 on aurait :

$$V_{CCmin} = RI + V_{CEsat}(Q2) + V_{RE}(Q5)$$

$$V_{CCmin} = V_{BE}(Q1) + V_{CEsat}(Q2) + V_{BE}(Q5)$$

soit  $V_{CCmin} = 2V_{BE} + V_{CEsat}$ .

[0031] Avec des transistors bipolaires cette tension V<sub>CCmin</sub> est de l'ordre de 1,7 Volt.

# **EXPOSÉ DE L'INVENTION**

5

10

20

35

45

50

55

[0032] La présente invention a justement pour but de remédier aux inconvénients présentés par la source de courant illustrée à la figure 1.

**[0033]** Elle propose une source de courant dont le courant est quasiment constant lorsque la tension d'alimentation varie et qui de plus peut démarrer pour une faible valeur de tension d'alimentation.

**[0034]** Plus précisément, la présente invention est une source de courant destinée à être montée entre deux bornes d'alimentation. Elle comporte un miroir de courant et un coeur connectés l'un à l'autre et distincts. Ce miroir de courant et ce coeur forment plusieurs branches à connecter entre les deux bornes d'alimentation. Le miroir comporte un transistor pilote et au moins un transistor de recopie, le coeur comporte un premier transistor, un second transistor et une résistance.

[0035] Le premier transistor du coeur et le premier transistor de recopie reliés forment la première branche, la résistance et un second transistor de recopie du miroir reliés forment la seconde branche, le transistor pilote et le second transistor du coeur reliés forment la troisième branche, le premier transistor du coeur étant relié à la seconde branche entre la résistance et le second transistor de recopie, le second transistor du coeur étant relié à la première branche entre le premier transistor du coeur et le premier transistor de recopie.

**[0036]** Un transistor de sortie rend accessible le courant de la source, ce transistor étant un transistor de recopie supplémentaire du miroir mais placé hors branche.

**[0037]** Les transistors du miroir sont de même type. Il en est de même pour les transistors du coeur. De plus les transistors du coeur et les transistors du miroir sont complémentaires.

[0038] Les transistors du miroir peuvent être bipolaires.

[0039] De manière à compenser les courants de base des transistors de miroir, le transistor pilote du miroir peut être monté en diode à travers un transistor supplémentaire.

[0040] Les transistors du miroir peuvent être des transistors MOS.

[0041] De la même manière, les transistors du coeur peuvent être des transistors bipolaires ou des transistors MOS.

[0042] Le transistor supplémentaire peut être de type bipolaire ou de type MOS.

# **BRÈVE DESCRIPTION DES DESSINS**

**[0043]** D'autres caractéristiques et avantages de l'invention apparaîtront à la lecture de la description qui suit illustrée par les figures jointes.

[0044] La figure 1 (déjà décrite) est un schéma électrique d'une source de courant classique.

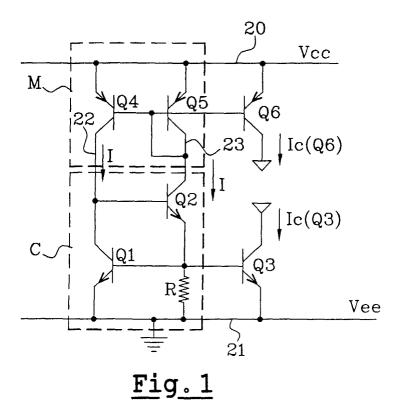

**[0045]** La figure 2 est un schéma électrique d'un exemple de source de courant selon l'invention réalisée en technologie bipolaire.

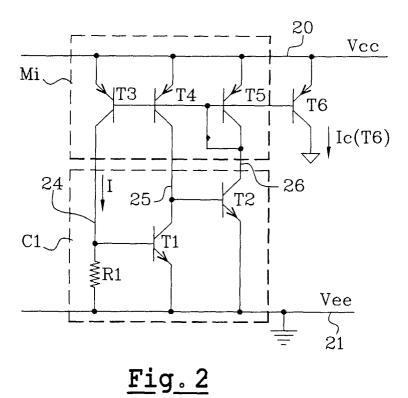

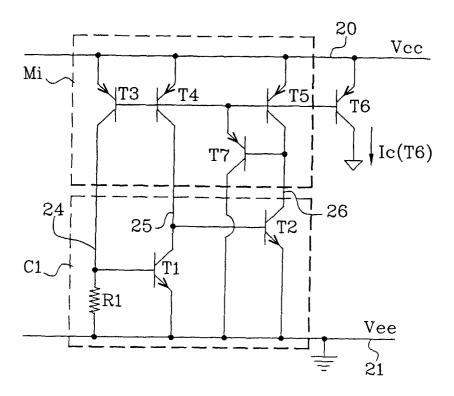

**[0046]** La figure 3 est un schéma électrique d'un autre exemple de source de courant selon l'invention réalisée en technologie bipolaire.

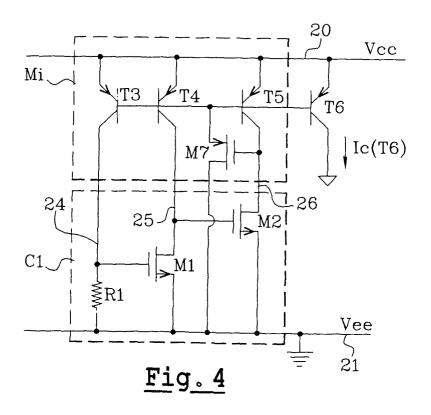

**[0047]** La figure 4 est un schéma électrique d'un autre exemple de source de courant selon l'invention avec le coeur en technologie MOS et le miroir de courant en technologie bipolaire.

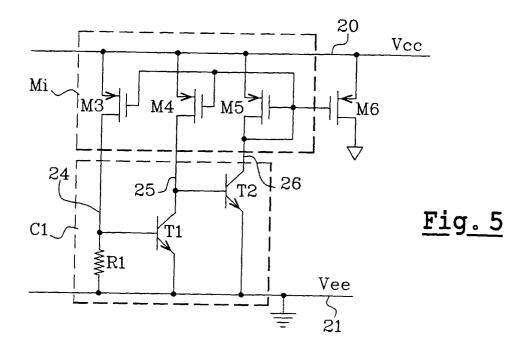

[0048] La figure 5 est un schéma électrique d'un exemple de source de courant selon l'invention avec le coeur en technologie bipolaire et le miroir de courant en technologie MOS.

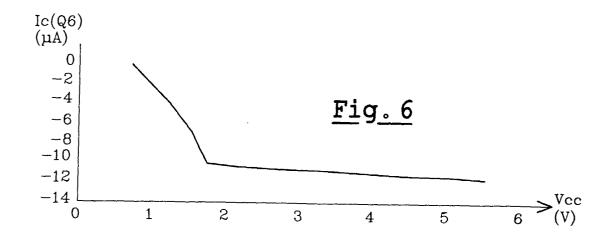

[0049] La figure 6 est un diagramme représentant le courant de la source de la figure 1 en fonction de la tension d'alimentation  $V_{CC}$ .

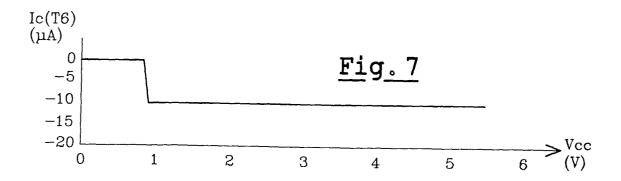

[0050] La figure 7 est un diagramme représentant le courant de la source de courant de la figure 2 en fonction de la tension d'alimentation  $V_{CC}$ .

# EXPOSÉ DÉTAILLÉ DE MODES DE RÉALISATION PARTICULIERS

[0051] On se réfère à la figure 2.

[0052] On retrouve comme sur la figure 1, les deux bornes d'alimentation 20, 21 l'une portée au potentiel haut V<sub>CC</sub> et l'autre portée au potentiel bas Vee, généralement la masse.

[0053] Lorsqu'on va parler de tension d'alimentation, il s'agit en fait de la différence de potentiel entre le potentiel  $V_{CC}$  de la borne d'alimentation 20 et le potentiel Vee de la borne d'alimentation 21. Dans ce cas, il s'agit de  $V_{CC}$

puisqu'on a supposé que la borne d'alimentation 21 était portée à la masse.

[0054] Cette source comporte plusieurs branches 24, 25, 26, chaque branche est montée entre les deux bornes d'alimentation.

[0055] Cette source de courant possède comme dans l'art antérieur un coeur C1 et un miroir de courant Mi distinct du coeur C1, ce miroir Mi et ce coeur C1 sont connectés l'un à l'autre. On va les détailler pour faire ressortir les différences avec l'art antérieur.

**[0056]** Le coeur C1 est connecté à l'une des bornes d'alimentation 21, ici la borne d'alimentation portée au potentiel Vee. Le coeur C1 est formé d'une résistance R1 de fixation du courant et de deux transistors T1, T2 de même type. Chacun de ces éléments appartient à une branche différente.

**[0057]** Le miroir de courant Mi est connecté à l'autre borne d'alimentation 20, ici la borne d'alimentation 20 portée au potentiel V<sub>CC</sub>. Le miroir de courant Mi comporte un transistor pilote T5 et deux transistors de recopie T4 et T3, ces trois transistors appartenant à des branches différentes.

**[0058]** Le premier transistor de recopie T4 et le premier transistor T1 du coeur C1 reliés forment la première branche 25. Le second transistor de recopie T3 et la résistance R1 reliés forment la seconde branche 24. Le transistor pilote T5, monté en diode, et le second transistor T2 du coeur C1 reliés forment la troisième branche 26.

**[0059]** Le premier transistor du coeur T1 est relié à la seconde branche 24 entre la résistance R1 et le second transistor de recopie T3. Le second transistor T2 du coeur C1 est relié à la première branche 25 entre le premier transistor de recopie T4 et le premier transistor T1 du coeur C1.

[0060] Dans l'exemple de la figure 2, les transistors de miroir Mi sont de même type, ici de type PNP. Les transistors du coeur C1 sont de même type, ici de type NPN, ils sont complémentaires des transistors de miroir.

[0061] On va décrire plus précisément les connexions des composants de la figure 2.

**[0062]** La résistance R1 a une de ses extrémités reliée à la borne d'alimentation 21 portée au potentiel Vee et son autre extrémité reliée d'une part à la base du premier transistor T1 du coeur C1 et d'autre part au collecteur du second transistor de recopie T3 du miroir Mi. Le second transistor de recopie T3 a son émetteur relié à la borne d'alimentation 20 portée au potentiel V<sub>CC</sub> et sa base reliée à la base du transistor pilote T5 du miroir Mi.

**[0063]** Le premier transistor T1 du coeur C1 a son émetteur relié à la borne d'alimentation 21 portée au potentiel Vee, et son collecteur relié d'une part au collecteur du premier transistor de recopie T4 du miroir Mi et d'autre part à la base du second transistor T2 du coeur C1. La base du premier transistor de recopie T4 est reliée à la base du transistor pilote T5 et son émetteur est relié à la borne d'alimentation 20 portée au potentiel V<sub>CC</sub>.

[0064] Le second transistor T2 du coeur C1 a son émetteur relié à la borne d'alimentation 21 portée au potentiel Vee et son collecteur relié au collecteur du transistor pilote T5. Le transistor pilote T5 a son émetteur relié à la borne d'alimentation portée au potentiel V<sub>CC</sub> et comme il est monté en diode, sa base et son collecteur sont reliés ensemble.

[0065] Le miroir Mi comporte de plus un transistor de sortie T6 qui permet de rendre accessible le courant de la

source. Ce transistor de sortie T6 est un transistor de recopie du miroir Mi. Il est monté comme dans la source conventionnelle de la figure 1.

**[0066]** Ainsi sa base est reliée à la base du transistor pilote T5, son émetteur est relié à la borne d'alimentation 20 portée au potentiel  $V_{CC}$  et son collecteur est destiné à être relié à un dispositif utilisateur du courant qui n'est pas représenté.

[0067] On va maintenant écrire les équations en courant qui régissent cette source de courant.

[0068] Dans le coeur, le courant traversant la résistance R1 est au premier ordre, tel que :

$$I = V_{RF}(T1)/R1$$

45

50

20

30

35

40

$$I = V_T \times ln(I/Is)$$

[0069] Is représente le courant de saturation du transistor T1.

**[0070]** En tenant compte de l'effet Early, le courant de polarisation de la source, disponible au niveau du collecteur du transistor T6, est tel que :

$$Ic(T6)=Ix(1+(V_{CE}(T6)/V_{EA}(T6))/(1+(V_{CE}(T5)/V_{EA}(T5)))$$

55

$$Ic(T6)=Ix(1+(V_{CE}(T6)/V_{EA}(T6))/(1+(V_{BE}(T5)/V_{EA}(T5))$$

[0071] Mais lorsque la tension d'alimentation V<sub>CC</sub> varie, le courant I va légèrement varier à cause des effets Early

des transistors T3 et T4. Le transistor T6 va avoir le même effet Early que le transistor T3 qui fournit le courant à la résistance R1. Précédemment, le transistor qui fournissait le courant à la résistance R était le transistor Q5, c'était précisément le transistor pilote du miroir M.

[0072] On obtient donc:

5

$$Ic(T6)=IX(1+(V_{CF}(T6)/V_{FA}(T6))/(1+(V_{CF}(T3)/V_{FA}(T5))$$

10 Ic(T6

$$Ic(T6)=Ix(1+(V_{CE}(T6)/V_{EA}(T6))/(1+((V_{CC}-V_{BE}(T1))/V_{EA}(T5))$$

[0073] Un composant (non représenté) du circuit à alimenter est destiné à être connecté entre le collecteur du transistor de sortie T6 et la borne d'alimentation 21 portée au potentiel Vee. La tension  $V_{CE}(T6)$  peut alors s'exprimer de la même manière que la tension  $V_{CE}(T3)$ , c'est à dire sous forme d'une différence de tension  $V_{CC}$  moins la tension aux bornes du composant (non représenté). En conséquence, les deux différences varient de la même manière en fonction de  $V_{CC}$  et leur rapport devient quasiment constant et indépendant de  $V_{CC}$ .

[0074] Le courant lc(T6) de la source de courant selon l'invention est quasiment constant lorsque la tension d'alimentation varie.

**[0075]** En ce qui concerne la tension d'alimentation minimum V<sub>CCmin</sub> assurant le démarrage de la source de courant, elle est donnée, pour la branche 24, par :

$$V_{CCmin} = V_{BE}(T1) + V_{CEesat}(T3)$$

Pour la branche 25 on a :

$$V_{CCmin} = V_{BE}(T2) + V_{Cesat}(T4)$$

30 Pour la branche 26 on obtient :

$$V_{CCmin} = V_{BE}(T5) + V_{Cesat}(T2)$$

35

40

45

50

20

[0076] Cette tension  $V_{CCmin}$  est de l'ordre d'un volt avec des transistors bipolaires.

[0077] On se réfère maintenant aux figures 6 et 7. Sur la figure 6, on voit qu'avec la source de la figure 1, le courant lc(Q6) varie entre -10 microampères et -12 microampères alors que la tension d'alimentation  $V_{CC}$  varie entre 1,7 Volt et 5,5 Volts. Sur la figure 7, on voit qu'avec la source de la figure 2, le courant lc(T6) reste à environ -10 microampères alors que la tension d'alimentation  $V_{CC}$  varie entre 0,9 Volt et 5,5 Volts.

**[0078]** Le démarrage est bien visible, il correspond au front raide des graphiques et se produit vers 1,7 Volt sur la figure 6 et vers 0,9 Volt sur la figure 7.

[0079] Les essais qui ont permis d'établir les graphiques des figures 6 et 7 montrent également que le courant lc (Q6) varie de +3,4%/V alors que le courant lc(T6) ne varie que de +0,03%/V. Les tensions d'Early des transistors NPN étaient de 75 Volts, celle des transistors PNP était de 62 Volts et le courant I étaient de 10 microampères environ.

**[0080]** On se réfère à la figure 3. Si la tension de démarrage faible n'est plus une contrainte à respecter, il est possible de monter le transistor pilote T5 du miroir Mi en diode à travers un transistor additionnel T7.

[0081] Le transistor additionnel T7, est un transistor PNP comme les autres transistors du miroir Mi. Sa base est reliée au collecteur du transistor pilote T5, son émetteur est relié à la base du transistor pilote T5 et son collecteur est relié à la borne d'alimentation 21 portée au potentiel Vee. Au lieu d'être un transistor bipolaire de même type que les transistors de miroir T3 à T6, le transistor additionnel pourrait être un transistor MOS. Cette variante est illustrée sur la figure 4.

[0082] Le transistor T7 sert à compenser les courants base des transistors du miroir Mi réalisés en technologie bipolaire.

[0083] Dans cette variante la tension d'alimentation minimum  $V_{CCmin}$  pour obtenir le démarrage devient :

$$V_{CCmin} = V_{BE}(T5) + V_{BE}(T7) + V_{CEsat}(T2)$$

soit  $V_{CCmin} = 2V_{BE} + V_{CEsat}$ .

[0084] Les configurations qui ont été décrites ne contenaient que des transistors bipolaires. Il est possible que le coeur C1 soit réalisé avec des transistors MOS comme l'illustre la figure 4. Le miroir Mi est identique à celui de la figure 3 à l'exception du transistor additionnel qui est maintenant un transistor MOS dénommé M7. Il pourrait être absent

[0085] Le coeur C1 comporte la résistance R1 et maintenant deux transistors MOS M1 et M2. Les branchements sont comparables à ceux de la figure 2. Le drain du transistor M1 est relié d'une part à la grille du transistor M2 et d'autre part au collecteur du transistor T4. La source du transistor M1 est reliée à la borne d'alimentation 21 portée au potentiel Vee. La grille du transistor M1 est reliée à l'une des extrémités de la résistance R1. La source du transistor M2 est reliée à la borne d'alimentation 21 portée au potentiel Vee, le drain du transistor M2 est relié au collecteur du transistor pilote T5.

[0086] Cette source de courant au lieu d'être qualifiée de source en V<sub>BE</sub>/R est qualifiée de source en V<sub>GS</sub>/R.

[0087] Une autre variante est représentée à la figure 5. Maintenant ce sont les transistors du miroir Mi qui sont des transistors MOS alors que les transistors du coeur C1 sont bipolaires comme sur la figure 2.

[0088] Le miroir Mi comporte maintenant un transistor pilote M5, deux transistors de recopie M4 et M3 et un transistor de sortie M6.

[0089] Les branchements sont comparables à ceux de la figure 2.

**[0090]** Le second transistor de recopie M3 a sa source reliée à la borne d'alimentation 20 portée au potentiel V<sub>cc</sub>, sa grille est reliée à la grille du transistor pilote M5, son drain est relié à la résistance R1 du coeur C1.

**[0091]** La grille du premier transistor de recopie M4 est reliée à la grille du transistor pilote M5, sa source est reliée à la borne d'alimentation 20 portée au potentiel V<sub>CC</sub> et son drain au collecteur du transistor T1 du coeur C1.

[0092] Le transistor pilote M5 a sa source reliée à la borne d'alimentation portée au potentiel V<sub>CC</sub> et comme il est monté en diode, sa grille et son drain sont reliés ensemble. Son drain est aussi relié au collecteur du transistor T2 du coeur C1.

**[0093]** Le transistor de sortie M6 a sa grille reliée à la grille du transistor pilote M5, sa source est reliée à la borne d'alimentation 20 portée au potentiel V<sub>CC</sub> et son drain est destiné à être relié à un dispositif utilisateur non représenté.

[0094] Il est bien sûr possible que la source de courant selon l'invention soit réalisée en totalité en technologie MOS en combinant le coeur C1 de la figure 4 et le miroir Mi de la figure 5.

**[0095]** Tous les transistors qui ont été décrits pourraient être remplacés par leurs complémentaires en inversant les bornes d'alimentation. Les émetteurs ou les sources des transistors qui étaient reliés à la borne d'alimentation portée au potentiel  $V_{CC}$  et inversement. Quant à la résistance R1 au lieu d'être reliée à la borne d'alimentation portée au potentiel  $V_{CC}$ , et le serait reliée à la borne d'alimentation portée au potentiel  $V_{CC}$ , et le serait reliée à la borne d'alimentation portée au potentiel  $V_{CC}$ . Le sens du courant au niveau du dispositif utilisateur serait inversé.

# Revendications

20

30

35

40

45

50

55

1. Source de courant destinée à être montée entre deux bornes d'alimentation (20, 21), comportant un miroir de courant (Mi) et un coeur (C1) connectés l'un à l'autre et distincts, ce miroir de courant (Mi) et ce coeur (C1) formant plusieurs branches (24, 25, 26) à connecter entre les deux bornes d'alimentation, le miroir (Mi) comportant un transistor pilote (T5) et au moins un transistor de recopie (T4), le coeur (C1) comportant un premier transistor (T1), un second transistor (T2) et une résistance (R1),

caractérisée en ce que le premier transistor (T1) du coeur (C1) et le premier transistor (T4) de recopie reliés forment la première branche (25), la résistance (R1) et un second transistor de recopie (T3) du miroir (Mi) reliés forment la seconde branche (24), le transistor pilote (T5) et le second transistor du coeur (T2) reliés forment la troisième branche (26), le premier transistor (T1) du coeur étant relié à la seconde branche (24) entre la résistance (R1) et le second transistor (T3) de recopie, le second transistor (T2) du coeur étant relié à la première branche (25) entre le premier transistor (T1) du coeur et le premier transistor de recopie (T4).

- 2. Source de courant selon la revendication 1, caractérisée en ce qu'un transistor de sortie (T6) rend accessible le courant de la source, ce transistor (T6) étant un transistor de recopie supplémentaire du miroir (Mi), ce transistor (T6) étant hors branche.

- 3. Source de courant selon l'une des revendications 1 ou 2, caractérisée en ce que les transistors (T3, T4, T5, T6) du miroir (Mi) sont de même type.

- **4.** Source de courant selon l'une des revendications 1 à 3, **caractérisée en ce que** les transistors (T1, T2) du coeur (C1) sont de même type.

- 5. Source de courant selon l'une des revendications 1 à 4, caractérisé en ce que les transistors (T1, T2) du coeur (C1) et les transistors (T3, T4, T5, T6) du miroir (Mi) sont complémentaires.

5

15

20

30

35

40

45

50

55

- **6.** Source de courant selon l'une des revendications 1 à 5, **caractérisée en ce que** les transistors (T3, T4, T5, T6) du miroir (Mi) sont bipolaires.

- 7. Source de courant selon la revendication 6, **caractérisée en ce que** le transistor pilote (T5) du miroir (Mi) est monté en diode à travers un transistor (T7) supplémentaire.

- 8. Source de courant selon l'une des revendications 1 à 5, caractérisé en ce que les transistors (T3, T4, T5, T6) du miroir (Mi) sont des transistors MOS.

- 9. Source de courant selon l'une des revendications 1 à 8, caractérisée en ce que les transistors (T1, T2) du coeur (C1) sont bipolaires.

- **10.** Source de courant selon l'une des revendications 1 à 8, **caractérisée en ce que** les transistors (T1, T2) du coeur (C1) sont des transistors MOS.

- **11.** Source de courant selon l'une des revendications 7 à 10, **caractérisée en ce que** le transistor supplémentaire (T7) est de type bipolaire.

- 25 **12.** Source de courant selon l'une des revendications 7 à 10, **caractérisée en ce que** le transistor supplémentaire (M7) est de type MOS.

Fig. 3

Numéro de la demande EP 02 29 0442

| Catégorie                                                | Citation du document avec<br>des parties pertir                                                                                                                                                                | indication, en cas de besoin,<br>nentes         | Revendication concernée | CLASSEMENT DE LA<br>DEMANDE (Int.Cl.7) |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------|----------------------------------------|

| A                                                        | DE 197 05 338 C (SI<br>18 juin 1998 (1998-<br>* le document en er                                                                                                                                              | 06-18)                                          | 1-12                    | G05F3/26                               |

| Α                                                        | US 4 605 892 A (SEE<br>12 août 1986 (1986-<br>* abrégé *                                                                                                                                                       | EVINCK EVERT ET AL)<br>08-12)                   | 1-12                    |                                        |

| Α                                                        | EP 0 524 498 A (NIF<br>27 janvier 1993 (19<br>* abrégé *                                                                                                                                                       |                                                 | 1-12                    |                                        |

| A                                                        | EP 0 472 202 A (NIP<br>26 février 1992 (19<br>* abrégé *                                                                                                                                                       | PPON ELECTRIC CO)<br>192-02-26)                 | 1-12                    |                                        |

| A                                                        | US 5 038 053 A (DJE<br>6 août 1991 (1991-0<br>* abrégé *                                                                                                                                                       | NGUERIAN ALEX B ET<br>18-06)                    | AL) 1-12                |                                        |

|                                                          |                                                                                                                                                                                                                | sac mas see just wer                            |                         | DOMAINES TECHNIQUES                    |

|                                                          |                                                                                                                                                                                                                |                                                 |                         | G05F                                   |

|                                                          |                                                                                                                                                                                                                |                                                 |                         |                                        |

| l e nrá                                                  | sent rapport a été établi pour tou                                                                                                                                                                             | ites les revendications                         |                         |                                        |

|                                                          | ieu de la recherche                                                                                                                                                                                            | Date d'achèvement de la recherche               |                         | Examinateur                            |

|                                                          | LA HAYE                                                                                                                                                                                                        | 8 juillet 200                                   | -                       | obert, D                               |

| X : parti<br>Y : parti<br>autre<br>A : arriè<br>O : divu | LITEGORIE DES DOCUMENTS CITE:<br>culièrement pertinent à lui seul<br>culièrement pertinent en combinaison<br>document de la même catégorie<br>re-plan technologique<br>gation non-écrite<br>iment intercalaire | vention<br>is publié à la<br>ment correspondant |                         |                                        |

EPO FORM 1503 03.82 (P04C02)

# ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

EP 02 29 0442

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Les dits members sont contenus au fichier informatique de l'Office européen des brevets à la date du Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

08-07-2002

| rche | publication |                                                          | famille de bre                                                                                                                | vet(s)                                                                                                                                                                                                                                                                                                                                                 | Date de publication                                                                                                                                                                                                                                                                                                                                                                            |

|------|-------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С    | 18-06-1998  | DE<br>WO<br>DE<br>EP<br>US                               | 9836342<br>59801762<br>0960366                                                                                                | A1<br>D1<br>A1                                                                                                                                                                                                                                                                                                                                         | 18-06-1998<br>20-08-1998<br>22-11-2001<br>01-12-1999<br>03-10-2000                                                                                                                                                                                                                                                                                                                             |

| A    | 12-08-1986  | NL<br>CA<br>DE<br>EP<br>HK<br>JP<br>JP<br>JP<br>KR<br>SG | 1210091<br>3573848<br>0155039<br>86691<br>1944807<br>6082308<br>60204019<br>9209548                                           | A1<br>A1<br>A<br>C<br>B<br>A<br>B1                                                                                                                                                                                                                                                                                                                     | 16-09-1985<br>19-08-1986<br>23-11-1989<br>18-09-1985<br>08-11-1991<br>23-06-1995<br>19-10-1994<br>15-10-1985<br>19-10-1992<br>04-01-1991                                                                                                                                                                                                                                                       |

| A    | 27-01-1993  | JP<br>DE<br>DE<br>EP<br>US                               | 69203169<br>69203169<br>0524498                                                                                               | D1<br>T2<br>A2                                                                                                                                                                                                                                                                                                                                         | 12-02-1993<br>03-08-1995<br>14-03-1996<br>27-01-1993<br>08-03-1994                                                                                                                                                                                                                                                                                                                             |

| А    | 26-02-1992  | JP<br>JP<br>DE<br>DE<br>EP<br>US                         | 4102107<br>69114079<br>69114079<br>0472202                                                                                    | A<br>D1<br>T2<br>A2                                                                                                                                                                                                                                                                                                                                    | 18-02-1998<br>03-04-1992<br>30-11-1995<br>23-05-1996<br>26-02-1992<br>19-01-1993                                                                                                                                                                                                                                                                                                               |

| A    | 06-08-1991  | AUCUN                                                    |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                |

|      |             |                                                          |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                |

|      |             |                                                          |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                |

|      | A           | A 12-08-1986  A 27-01-1993  A 26-02-1992                 | WO DE EP US  A 12-08-1986 NL CA DE EP HK JP JP JP JP DE DE EP US  A 27-01-1993 JP DE DE EP US  A 26-02-1992 JP JP DE DE EP US | MO 9836342 DE 59801762 EP 0960366 US 6128172  A 12-08-1986 NL 8400636 CA 1210091 DE 3573848 EP 0155039 HK 86691 JP 1944807 JP 6082308 JP 60204019 KR 9209548 SG 85890  A 27-01-1993 JP 5035350 DE 69203169 DE 69203169 DE 69203169 EP 0524498 US 5293112  A 26-02-1992 JP 2715642 JP 4102107 DE 69114079 DE 69114079 DE 69114079 EP 0472202 US 5180966 | W0 9836342 A1 DE 59801762 D1 EP 0960366 A1 US 6128172 A  A 12-08-1986 NL 8400636 A CA 1210091 A1 DE 3573848 D1 EP 0155039 A1 HK 86691 A JP 1944807 C JP 6082308 B JP 60204019 A KR 9209548 B1 SG 85890 G  A 27-01-1993 JP 5035350 A DE 69203169 D1 DE 69203169 T2 EP 0524498 A2 US 5293112 A  A 26-02-1992 JP 2715642 B2 JP 4102107 A DE 69114079 D1 DE 69114079 T2 EP 0472202 A2 US 5180966 A |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82