(19)

Europäisches Patentamt

European Patent Office

Office européen des brevets

(11)

EP 1 271 440 A1

(12)

## DEMANDE DE BREVET EUROPEEN

(43) Date de publication:

**02.01.2003 Bulletin 2003/01**

(51) Int Cl. 7: **G08B 17/10, G08B 17/00,

G01J 1/42**

(21) Numéro de dépôt: **01202429.5**

(22) Date de dépôt: **25.06.2001**

(84) Etats contractants désignés:

**AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU

MC NL PT SE TR**

Etats d'extension désignés:

**AL LT LV MK RO SI**

(71) Demandeur: **EM Microelectronic-Marin SA

2074 Marin (CH)**

(72) Inventeur: **Descombes, Arthur

3210 Kerzers (CH)**

(74) Mandataire: **Ravenel, Thierry Gérard Louis et al

I C B,

Ingénieurs Conseils en Brevets SA,

7, rue des Sors

2074 Marin (CH)**

### (54) Régulateur haute-tension comprenant un dispositif externe de regulation

(57) Il est décrit un circuit régulateur haute-tension (1) permettant de délivrer au moins une première tension de sortie régulée ( $V_{REG1}$ ,  $V_{REG2}$ ) à partir d'une tension d'entrée haute ( $V_{HV}$ ), ce circuit régulateur comprenant un dispositif externe de régulation (2) comprenant un terminal d'entrée (21) sur lequel est appliquée ladite tension d'entrée haute, un terminal de sortie (22) sur lequel est délivrée ladite première tension de sortie régulée, et un terminal de commande (23) relié à un circuit de commande (10) du dispositif externe de régulation.

Le dispositif externe de régulation (2) est commandé par un amplificateur différentiel (4) aux entrées duquel sont respectivement appliquées une tension divisée proportionnelle à la première tension de sortie régulée et une tension de référence déterminée ( $V_{REF}$ ), la sortie de cet amplificateur différentiel commandant l'état de conduction du dispositif externe de régulation (2) au travers d'un transistor MOSFET haute-tension (3) connecté par son drain au terminal de commande (23) du dispositif externe de régulation (2).

Fig.2

## Description

**[0001]** La présente invention concerne de manière générale un circuit régulateur haute-tension permettant de délivrer au moins une première tension de sortie régulée à partir d'une tension d'entrée haute, notamment de l'ordre de quelques dizaines de volts. Plus particulièrement, la présente invention concerne un tel régulateur haute-tension sous la forme d'un circuit intégré commandant un dispositif externe de régulation.

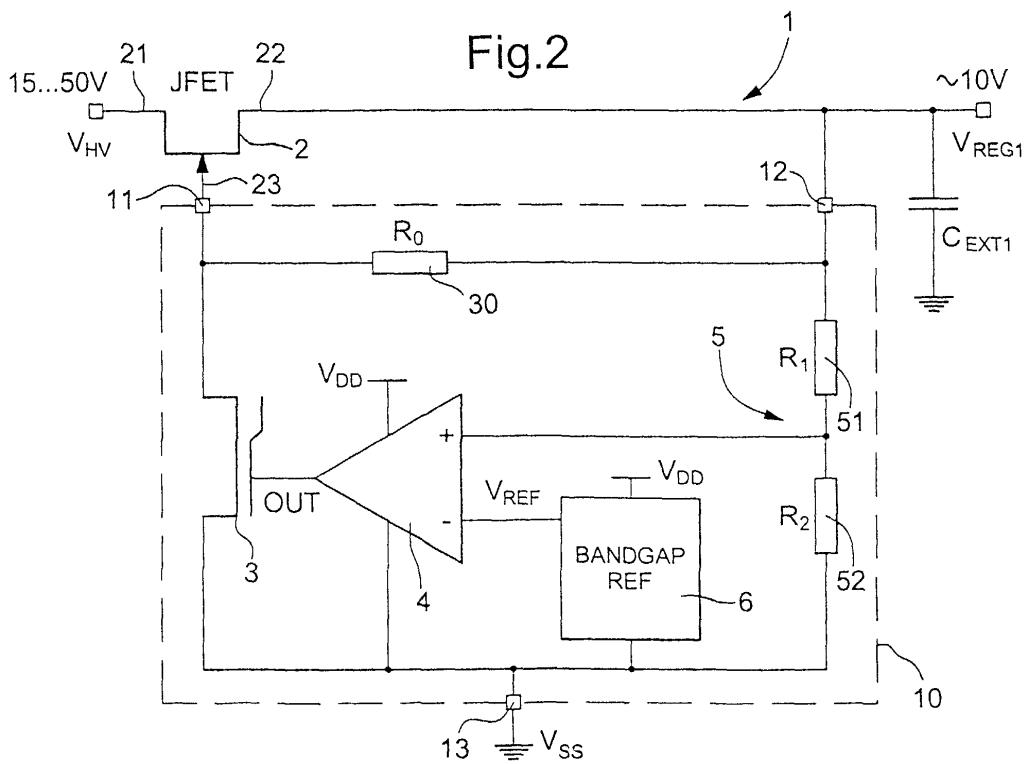

**[0002]** Diverses applications nécessitent la fourniture d'une tension régulée déterminée à partir d'une tension d'entrée haute, cette tension régulée étant notamment utilisée pour alimenter l'électronique d'un dispositif associé. La figure 1 montre un circuit régulateur désigné globalement par la référence numérique 1 comprenant un dispositif externe de régulation 2, constitué d'un transistor JFET, et un circuit de commande 10 de ce dispositif externe de régulation 2. Ce circuit régulateur 1 est conçu pour délivrer une tension de sortie régulée  $V_{REG}$  permettant l'alimentation d'un dispositif associé, non représenté. Cette tension de sortie régulée  $V_{REG}$  est dérivée d'une tension d'entrée  $V_{HV}$  de niveau haut de l'ordre de quelques dizaines de volts pouvant typiquement varier entre 15 et 30 volts.

**[0003]** Un tel circuit régulateur de tension est notamment utilisé dans des dispositifs de détection de fumée, comme décrit par exemple dans le document EP-A1-0 759 602, pour dériver une tension régulée de niveau bas (par exemple 5 volts) nécessaire entre autres à l'alimentation d'un microprocesseur du dispositif de détection de fumée. Dans le cadre d'une telle application, la tension de ligne alimentant les dispositifs de détection de fumée est par exemple de l'ordre de 15 à 30 volts.

**[0004]** Le circuit régulateur 1 de la figure 1 comprend typiquement un amplificateur différentiel 4 dont une entrée est connectée à la sortie d'une circuit diviseur de tension 5, formé dans cet exemple de deux résistances 51, 52 branchées en série, l'autre entrée de l'amplificateur différentiel 4 étant connectée à une cellule de référence 6 délivrant une tension de référence  $V_{REF}$ . Cette cellule de référence 6 est typiquement une cellule délivrant une tension de référence stable en température dite de « bandgap ». La sortie de l'amplificateur différentiel 4 est directement reliée à la grille du transistor JFET formant le dispositif de régulation 2.

**[0005]** L'agencement illustré dans la figure 1 assure ainsi que la tension présente au noeud de sortie du circuit diviseur de tension 5, à savoir le noeud de connexion entre les résistances 51 et 52, soit sensiblement égale à la tension de référence  $V_{REF}$ , les valeurs R1, R2 des résistances 51 et 52 étant choisies de sorte que la tension de sortie régulée  $V_{REG}$  du circuit régulateur 1 ait une valeur déterminée, par exemple de l'ordre de 5 volts. Cette tension régulée  $V_{REG}$  alimente notamment l'amplificateur différentiel 4 et la cellule de référence 6 du régulateur 1 comme illustré dans la figure 1.

**[0006]** Un inconvénient du circuit régulateur de la fi-

gure 1 réside notamment dans le choix du dispositif externe de régulation 2 et les coûts de ce dispositif de régulation. Dans l'exemple de la figure 1, on comprendra que le transistor JFET doit être choisi pour résister à des tensions drain-source relativement élevées (dans l'exemple de l'ordre de max. 25 volts), cette tension drain-source étant notamment fonction de la tension d'entrée haute  $V_{HV}$  et de la tension régulée  $V_{REG}$  que l'on désire délivrer en sortie du régulateur. On notera que le coût de ce transistor JFET augmente avec la tension drain-source maximale à laquelle cet élément de régulation peut être soumis. Il est donc désirable, notamment dans l'optique de réduire les coûts, de proposer une solution alternative à la solution présentée dans la figure 1.

**[0007]** Un autre inconvénient de la solution illustrée dans la figure 1 réside dans le fait que la grille du transistor JFET formant le dispositif externe de régulation 2 est directement commandée par la sortie de l'amplificateur différentiel 4. La tension de grille du transistor JFET est donc limitée par la tension de sortie de l'amplificateur différentiel 4 qui est elle-même dépendante de la technologie utilisée.

**[0008]** Un sérieux inconvénient de la solution de la figure 1 réside donc dans le fait que son application est limitée par la tension d'entrée haute susceptible d'être appliquée à l'entrée du régulateur ainsi que par la tension de sortie régulée que l'on désire délivrer. Ainsi, si la tension d'entrée haute venait à être augmentée et/ou si la tension de sortie régulée venait à être réduite, par exemple à 3 volts, les limites imposées par la technologie rendraient l'utilisation du circuit régulateur de la figure 1 trop coûteuse voire même impossible, en particulier lorsque l'on désire fabriquer ce régulateur dans une technologie inférieure au micron.

**[0009]** La présente invention a donc pour but de proposer une solution permettant de remédier aux inconvénients susmentionnés, et notamment proposer une solution permettant l'utilisation d'un dispositif de régulation externe moins coûteux ainsi qu'une solution pouvant être utilisée avec des tensions d'entrée hautes plus élevées.

**[0010]** Un autre but de la présente invention est de proposer une solution pouvant être réalisée et fabriquée dans une technologie CMOS inférieure au micron, en particulier dans une technologie CMOS 0.5 µm.

**[0011]** La présente invention a ainsi pour objet un régulateur haute-tension dont les caractéristiques sont énoncées dans la revendication 1.

**[0012]** Des modes de réalisation avantageux de la présente invention font l'objet des revendications indépendantes.

**[0013]** D'une manière générale, selon la présente invention, le dispositif de régulation externe est avantageusement commandé par l'intermédiaire d'un transistor MOSFET haute-tension spécifique susceptible de voir à ses bornes une tension drain-source de l'ordre de quelques dizaines de volts. De la sorte, les contraintes

imposées sur le dispositif de régulation ainsi que sur l'amplificateur différentiel sont moindres, ceci impliquant notamment des coûts moins élevés en ce qui concerne le dispositif de régulation externe.

**[0014]** Bien que la présente invention nécessite l'utilisation d'éléments additionnels, les coûts supplémentaires causés par l'adjonction de ces éléments sont néanmoins moindres que l'économie pouvant être espérée sur les coûts liés au dispositif de régulation externe. En outre, les transistors MOSFET haute-tension utilisés dans le cadre de la présente invention sont parfaitement compatibles avec la technologie CMOS standard et ne nécessitent pas ou peu de masques et/ou d'implantation additionnels pour leur fabrication.

**[0015]** Selon un mode de réalisation préféré de la présente invention, le circuit régulateur est agencé pour délivrer une première tension de sortie régulée, dite intermédiaire, ainsi qu'une seconde tension de sortie régulée permettant l'alimentation de certains composants du circuit régulateur, tels l'amplificateur différentiel et la cellule de référence du régulateur, ainsi que l'alimentation éventuelle de l'électronique d'un dispositif associé, tel par exemple le microprocesseur chargé des opérations d'un dispositif de détection de fumée. Selon ce mode de réalisation préféré, la tension régulée intermédiaire est par exemple utilisée, dans le cadre de l'application à un dispositif de détection de fumée, pour fournir le courant nécessaire à la génération de l'impulsion infrarouge par la diode infrarouge dont sont typiquement équipés ces dispositifs de détection.

**[0016]** Dans le cadre d'une application dans un détecteur de fumée et contrairement au circuit régulateur de la figure 1, on notera que ce mode de réalisation préféré de la présente invention permet le déplacement de la diode infrarouge de l'entrée sur la sortie du circuit régulateur où est délivrée la tension régulée intermédiaire. La tension nécessaire à la génération de l'impulsion infrarouge dans un dispositif de détection de fumée est typiquement de l'ordre d'une dizaine de volts, c'est-à-dire bien supérieure aux niveaux de tensions utilisés pour alimenter l'électronique du dispositif. Selon ce mode de réalisation de l'invention, cette tension régulée intermédiaire est d'un niveau inférieur à la tension d'entrée du circuit régulateur, permettant ainsi une réduction des pertes lors de la génération de l'impulsion infrarouge, et néanmoins supérieur à la tension d'alimentation de l'électronique afin d'assurer un niveau d'alimentation adéquat en vue de la génération de cette impulsion infrarouge.

**[0017]** Selon encore un autre mode de réalisation de la présente invention, le circuit régulateur est agencé de sorte que l'amplificateur différentiel commandant le dispositif de régulation externe présente une hystérèse, ceci assurant notamment une stabilité accrue du fonctionnement du régulateur.

**[0018]** D'autres caractéristiques et avantages de la présente invention apparaîtront plus clairement à la lecture de la description détaillée qui suit, faite en référence

aux dessins annexés donnés à titre d'exemples non limitatifs et dans lesquels :

- la figure 1, déjà présentée, est un schéma bloc d'un circuit régulateur haute-tension de l'art antérieur comprenant un dispositif externe de régulation constitué d'un transistor JFET à canal n ;

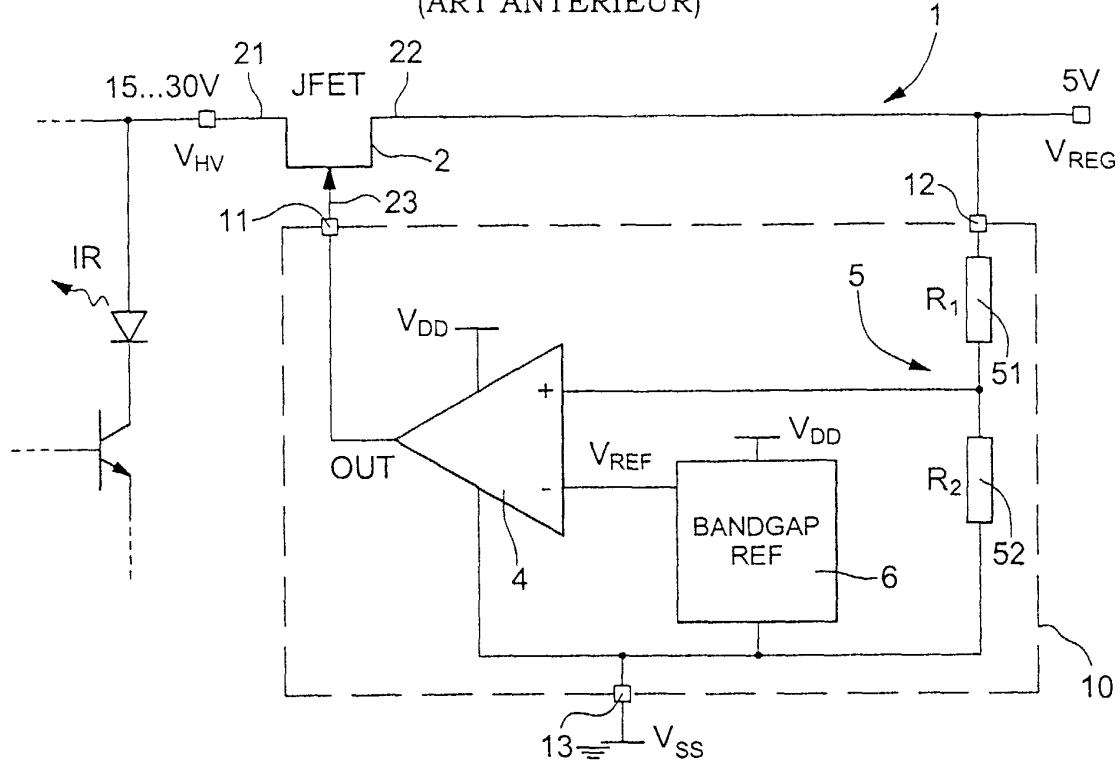

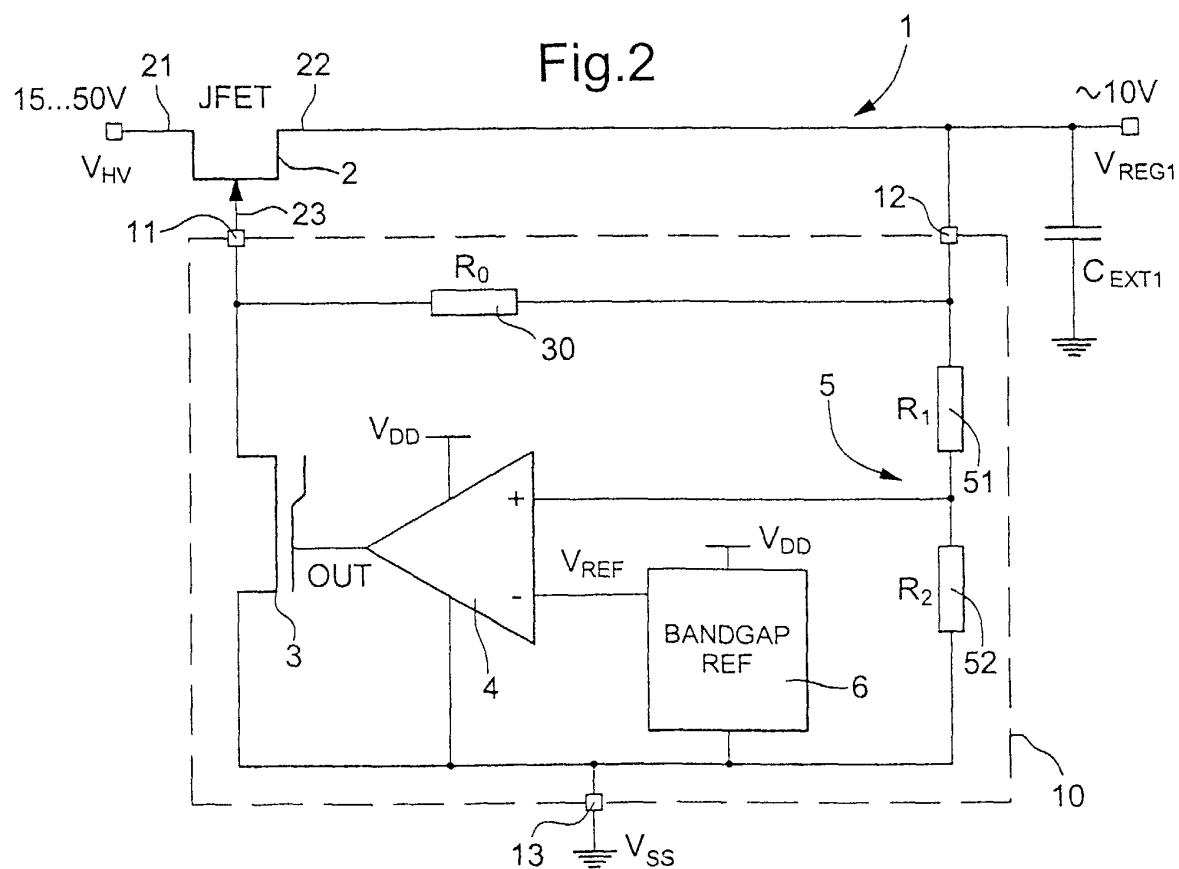

- la figure 2 est un schéma bloc général d'un circuit régulateur haute-tension selon la présente invention comprenant un dispositif externe de régulation constitué d'un transistor JFET à canal n ;

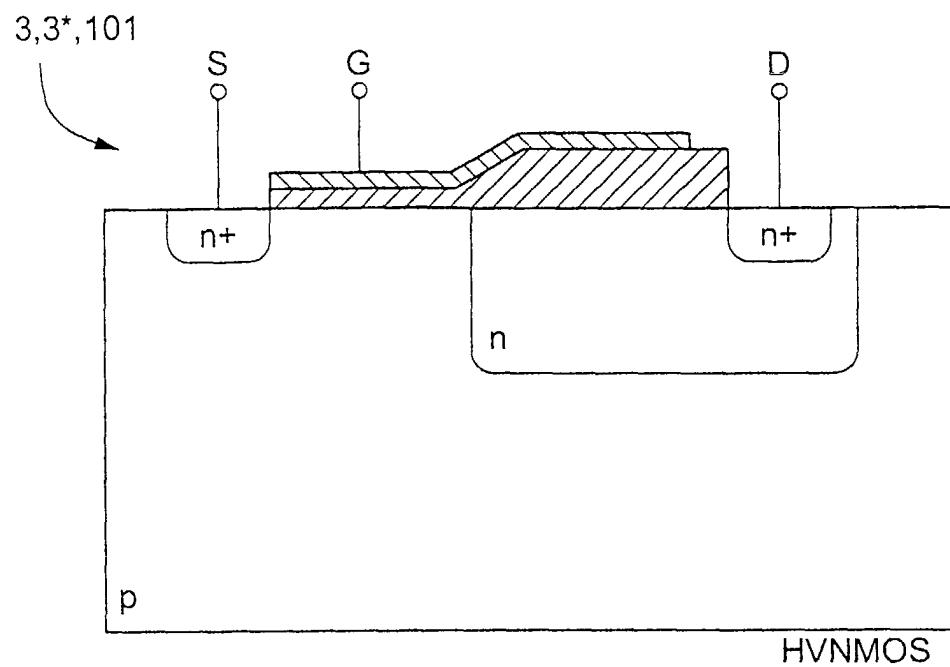

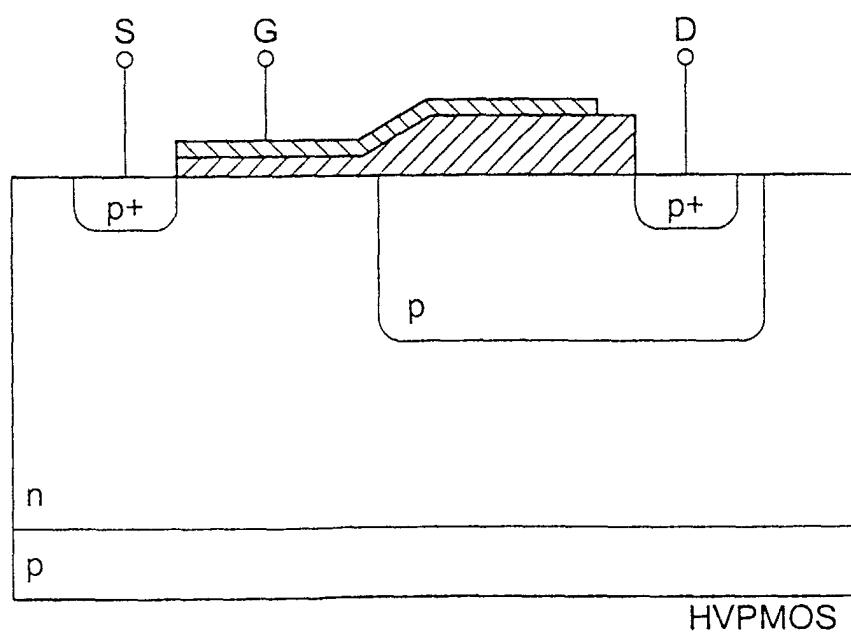

- les figures 3a et 3b sont des vues en coupe schématiques de transistors MOSFET à haute tension, respectivement à canal n et à canal p, réalisés selon une technologie CMOS standard ;

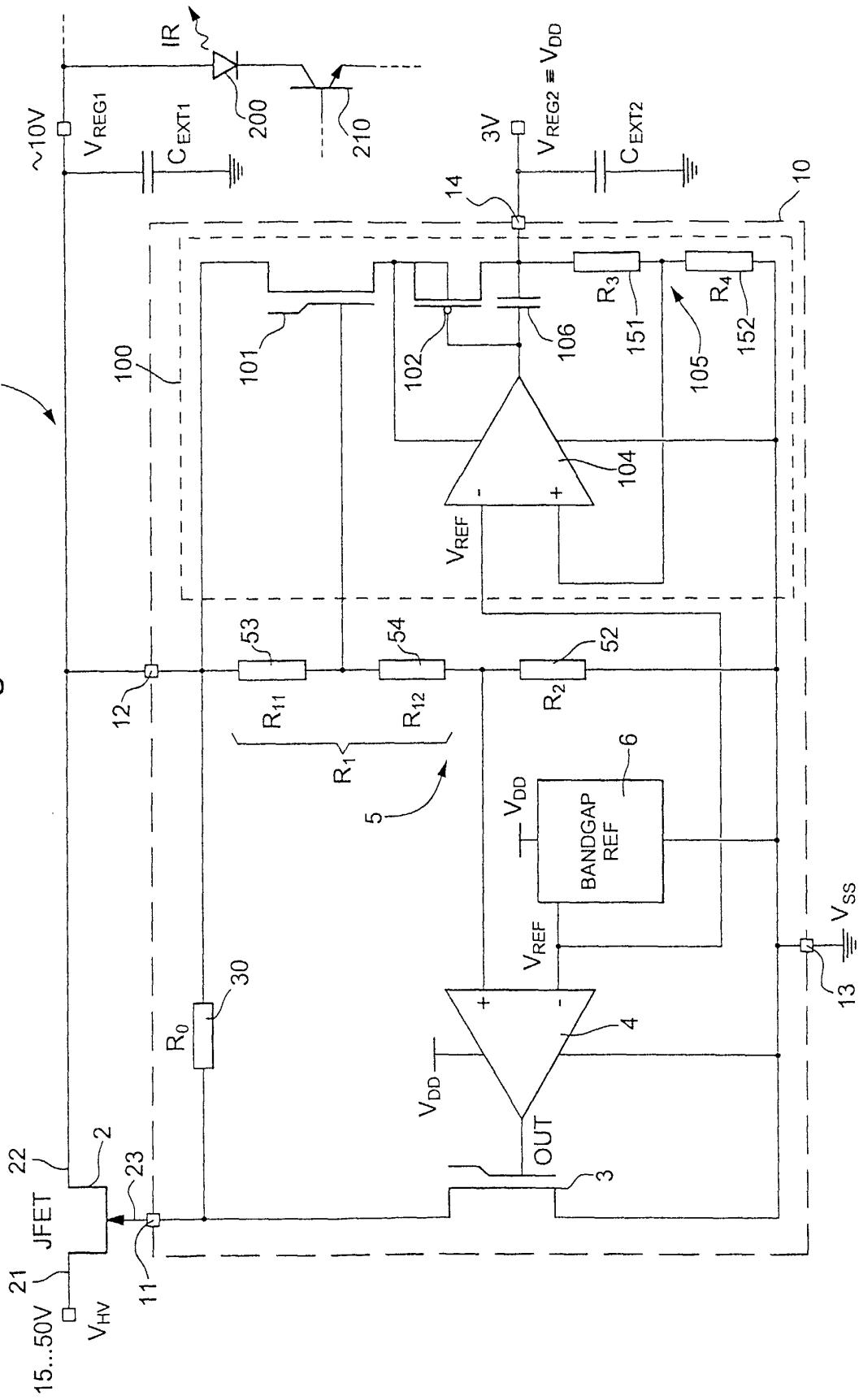

- la figure 4 montre une première variante de réalisation du circuit régulateur haute-tension selon l'invention permettant de délivrer une première tension de sortie régulée de niveau intermédiaire et une seconde tension de sortie régulée de niveau bas ou nominal permettant l'alimentation de composants électroniques ;

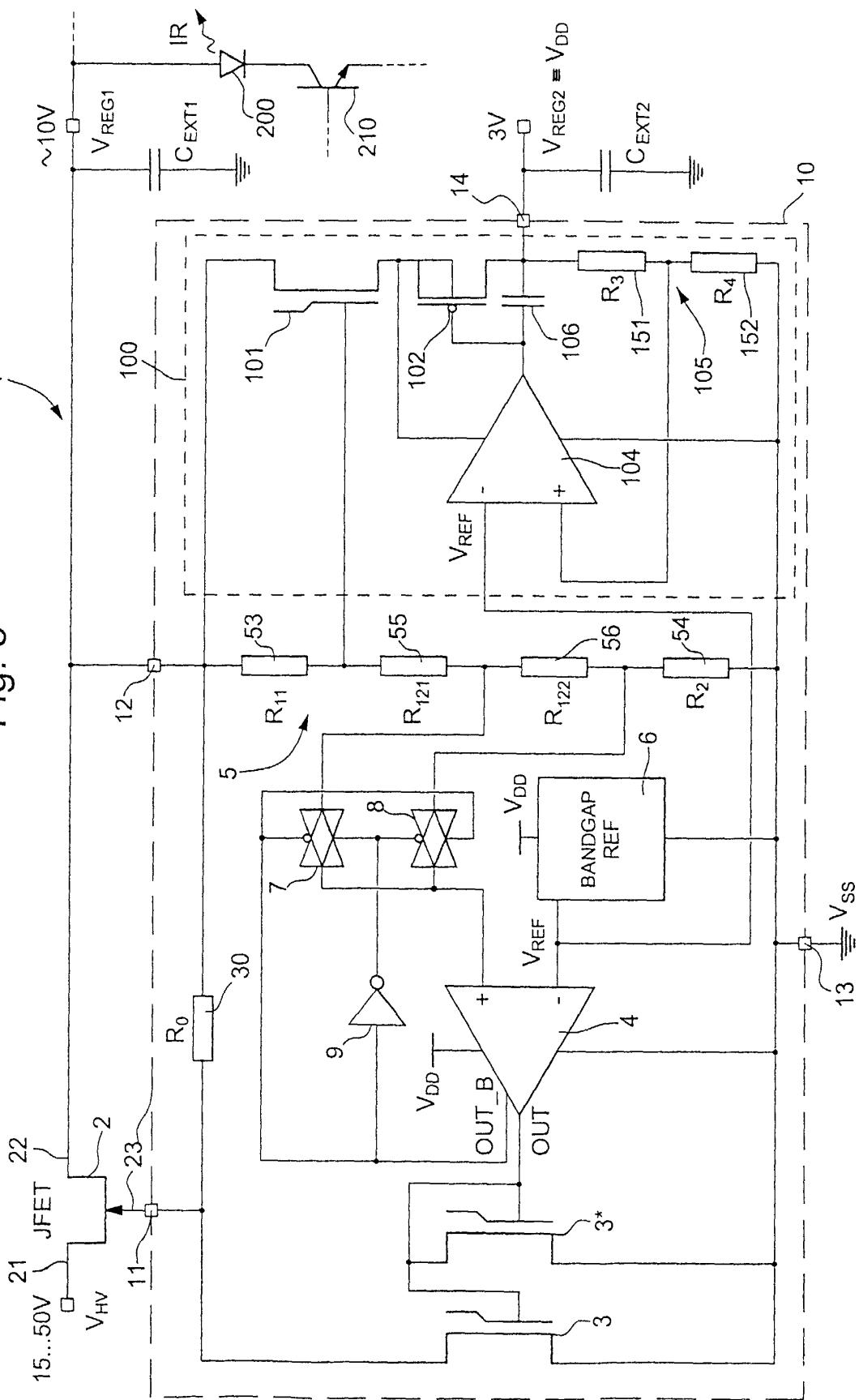

- la figure 5 montre une seconde variante de réalisation du circuit régulateur haute-tension selon l'invention dans laquelle l'amplificateur différentiel commandant le dispositif externe de régulation présente en outre une hystérèse ;

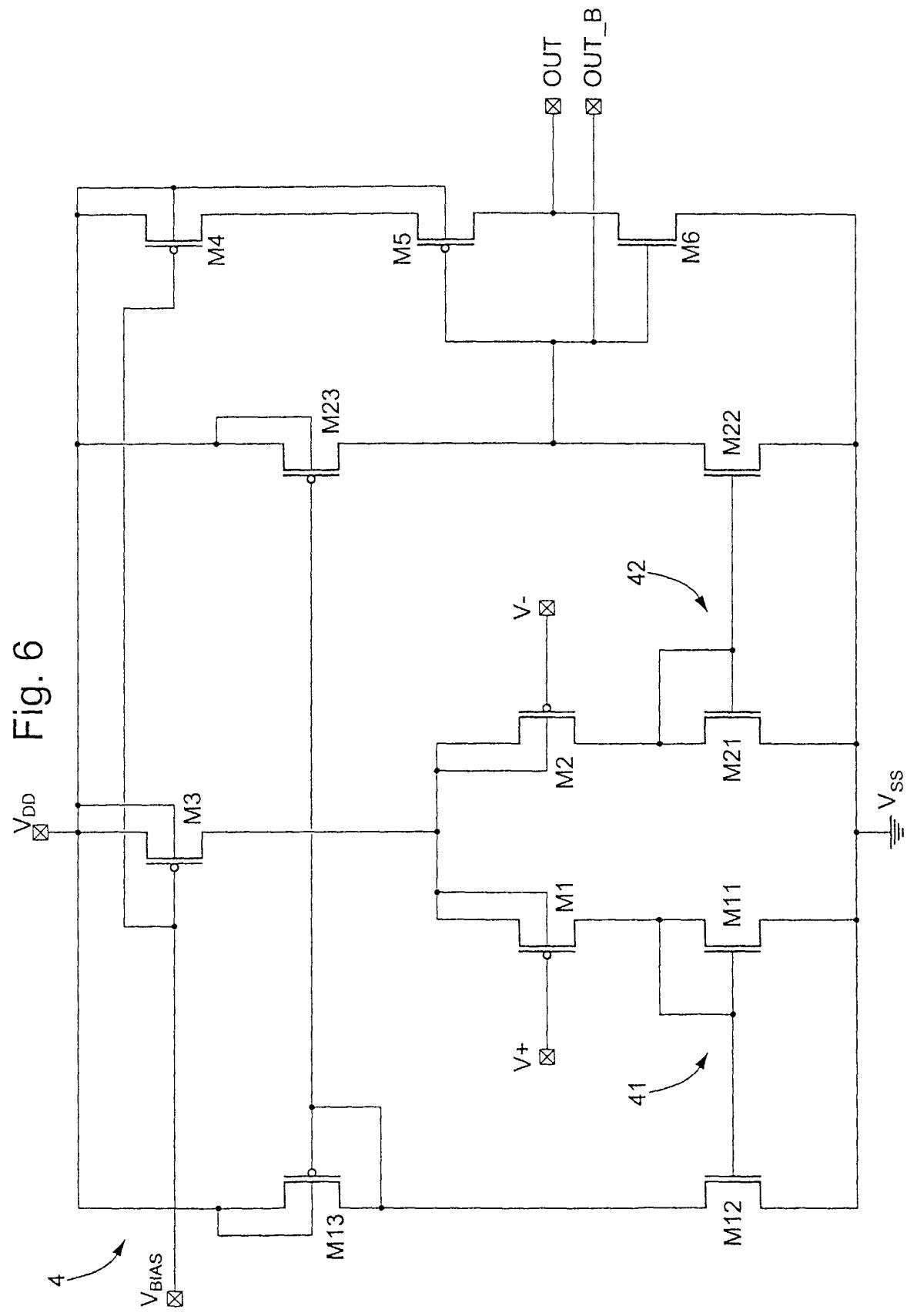

- la figure 6 est un schéma détaillé d'un exemple de réalisation de l'amplificateur différentiel commandant le dispositif externe de régulation ;

- la figure 7 est un schéma détaillé d'un exemple de réalisation de l'amplificateur différentiel du circuit régulateur des figures 4 et 5 utilisé pour produire la seconde tension de sortie régulée de niveau bas ; et

- la figure 8 est un schéma d'un dispositif externe de régulation susceptible de remplacer le transistor JFET utilisé comme dispositif externe de régulation dans les circuits régulateurs des figures 2, 4 et 5.

**[0019]** La figure 2 montre un schéma bloc général d'un circuit régulateur haute-tension selon la présente invention permettant de délivrer une tension de sortie régulée désignée  $V_{REG1}$ . Comme précédemment en référence à la figure 1, ce circuit régulateur est désigné globalement par la référence numérique 1 et comprend notamment un dispositif externe de régulation 2, constitué dans cet exemple d'un unique transistor JFET à canal n, ainsi qu'un circuit intégré de commande désigné globalement par la référence numérique 10, par exemple réalisé sous la forme d'un ASIC.

**[0020]** Dans le cadre de l'application spécifique comme régulateur de tension dans un dispositif de détection de fumée, la haute tension d'entrée  $V_{HV}$  peut varier dans cet exemple de 15 à 50 volts environ. La tension de sortie régulée  $V_{REG1}$  est dans cet exemple de l'ordre d'une dizaine de volts.

**[0021]** Le dispositif externe de régulation 2 comprend un terminal d'entrée 21 (le drain du transistor JFET) con-

necté à la tension d'entrée haute  $V_{HV}$ , un terminal de sortie 22 (la source du transistor JFET) sur lequel est délivrée la tension de sortie régulée  $V_{REG1}$ , et un terminal de commande 23 (la grille du transistor JFET) par le biais duquel l'état de conduction du dispositif externe de régulation 2 est commandé. Les terminaux de commande 23 et de sortie 22 sont respectivement reliés à des bornes 11 et 12 du circuit intégré 10. Une borne 13 du circuit intégré 10 est reliée à la masse  $V_{SS}$  du circuit. On notera déjà ici que d'autres dispositifs externe de régulation pourraient être utilisés en lieu et place du transistor JFET. La figure 8, qui sera discutée ultérieurement de manière détaillée, présente par exemple un autre dispositif externe de régulation comprenant un agencement de deux transistors bipolaires complémentaires et d'une résistance.

**[0022]** Le circuit intégré 10 comporte essentiellement un amplificateur différentiel 4, un circuit diviseur de tension 5, une cellule de référence 6, ainsi qu'un élément de commande haute-tension 3. Le circuit diviseur de tension 5 est formé dans cet exemple de deux résistances 51, 52 branchées en série entre la borne 12 du circuit intégré 10, à savoir le terminal de sortie du dispositif externe de régulation 2, et la masse  $V_{SS}$  du circuit. On comprendra bien évidemment que d'autres circuits diviseurs de tension pourraient être utilisés par l'homme du métier. Le circuit régulateur 1 comporte en outre typiquement un élément capacitif externe  $C_{EXT1}$  formant tampon branché sur le terminal de sortie 22.

**[0023]** Le noeud de connexion entre les deux résistances 51, 52 est relié à une première borne d'entrée de l'amplificateur différentiel 4. On aura aisément compris que la tension appliquée sur cette première borne d'entrée de l'amplificateur différentiel 4 ainsi que la tension régulée  $V_{REG1}$  sont proportionnelles dans un rapport déterminé par les valeurs R1 et R2 des résistances 51, 52. La seconde borne d'entrée de l'amplificateur différentiel 4 est reliée quant à elle à la cellule de référence 6 produisant une tension de référence désignée  $V_{REF}$ , cette cellule de référence 6 étant typiquement une cellule du type « bandgap » délivrant une tension de référence par exemple de l'ordre de 1.2 volts environ.

**[0024]** La sortie de l'amplificateur différentiel 4 est appliquée sur la grille d'un transistor MOSFET haute-tension 3 d'un type spécifique. Ce transistor MOSFET haute-tension 3, ici du type à canal-n, est déjà connu de l'homme du métier. La particularité de ce transistor haute-tension réside notamment dans la structure spécifique de l'oxyde de grille qui présente une épaisseur plus importante du côté drain que du côté source ainsi que dans la présence d'une zone tampon du côté drain constituée d'un caisson de type n (ou p pour un transistor MOSFET haute-tension à canal-p).

**[0025]** Les figures 3a et 3b montrent respectivement les schémas d'un transistor MOSFET à canal n haute-tension, ou HVNMOS, et d'un transistor MOSFET à canal p haute-tension, ou HVPMS. Les transistors HVNMOS présentent notamment l'avantage d'une tension

de claquage élevée typiquement supérieure à 30 volts. Un autre avantage de ce type de transistor réside dans le fait que leur fabrication est parfaitement compatible avec la technologie CMOS standard.

5 **[0026]** Pour de plus amples détails concernant ce type de transistors haute-tension, on pourra notamment se référer à l'article de MM. C. Bassin, H. Ballan et M. Declercq intitulé « High-Voltage Devices for 0.5- $\mu$ m Standard CMOS Technology », IEEE Electron Device Letters, vol. 21, No. 1, Janvier 2000, relatif à la fabrication de tels transistors haute-tension en technologie 0.5 microns. A titre d'exemple, il ressort de la Table 1 de ce document qu'un transistor MOSFET haute-tension à canal-n ayant une tension de claquage de l'ordre de 30 volts peut être réalisé en technologie CMOS standard sans que cela ne nécessite de masques ou d'implants additionnels.

10 **[0027]** En se référant à nouveau à la figure 2, on peut constater que le transistor MOSFET haute-tension 3 est connecté, du côté drain, au terminal de commande 23 du dispositif externe de régulation 2 via la borne 11, et, du côté source, à la masse  $V_{SS}$  via la borne 13. Afin d'assurer une polarisation adéquate du transistor JFET formant le dispositif externe de régulation 2, une résistance 30 de valeur  $R_0$  est connectée entre les bornes 11 et 12 du circuit intégré 10, à savoir entre les terminaux de commande 23 et de sortie 22 du dispositif externe de régulation 2. On notera que cette résistance 30 n'est nécessaire que dans le cas où le dispositif externe de régulation 2 est constitué d'un transistor JFET comme illustré. Dans l'éventualité où le dispositif externe de régulation était réalisé sous la forme d'un agencement de transistors bipolaires comme illustré en figure 8, cette résistance 30 n'est plus nécessaire.

15 **[0028]** Dans la figure 2, on notera que l'amplificateur différentiel 4 ainsi que la cellule de référence 6 sont alimentés par une tension d'alimentation  $V_{DD}$ , par exemple de l'ordre de 3 volts. Dans la suite de la présente description, selon une variante de la présente invention, cette tension d'alimentation  $V_{DD}$  est avantageusement également délivrée par le circuit régulateur 1 lui-même.

20 **[0029]** Selon l'invention, on notera que les seuls éléments devant supporter des tensions élevées à leurs bornes sont le transistor 3 et les résistances 30, 51 et 52, ces dernières étant avantageusement intégrées sous la forme de régions de diffusion de type n ou résistances « n-well ». L'amplificateur différentiel 4 est quant à lui un amplificateur différentiel conventionnel ne devant supporter que des tensions basses à ses bornes.

25 **[0030]** La figure 4 montre une variante avantageuse du circuit régulateur selon l'invention dans laquelle le circuit intégré 10 comporte en outre des moyens, désignés globalement par la référence numérique 100, pour délivrer une seconde tension de sortie régulée  $V_{REG2}$  permettant avantageusement d'alimenter divers composants électroniques du circuit régulateur, tels notamment l'amplificateur différentiel 4 et la cellule de référence 6, ou d'autres composants électroniques associés au

régulateur. Dans la figure 4, on notera que la tension de sortie régulée  $V_{REG2}$  est utilisée comme tension d'alimentation  $V_{DD}$  pour l'amplificateur différentiel 4 et la cellule de référence 6.

**[0031]** Les moyens 100 comprennent préféablement, comme illustré, un second transistor MOSFET haute-tension à canal n désigné par la référence numérique 101, un élément de régulation 102 constitué dans cet exemple d'un transistor p-MOS, un amplificateur différentiel 104 et un circuit diviseur de tension 105.

**[0032]** Le transistor MOSFET haute-tension 101 est analogue au transistor 3 et est branché par son terminal de drain au terminal de sortie 22 du dispositif externe de régulation 2, et, par son terminal de source au terminal de source du transistor p-MOS 102. La grille du transistor MOSFET haute-tension 101 est reliée au circuit diviseur de tension 5 au noeud de connexion entre des résistances 53 et 54. Ces résistances 53 et 54 en série remplacent la résistance 51 de la figure 2 et la somme des valeurs R11 et R12 de ces résistances 53 et 54 est équivalente à la valeur R1 de la résistance 51 de la figure 2. Le rapport de division du circuit diviseur de tension 5 reste ainsi inchangé en ce qui concerne la tension appliquée sur l'entrée de l'amplificateur différentiel 4.

**[0033]** Le rapport des résistances R11, R12 et R2 est choisi de sorte que la tension appliquée sur la grille du transistor haute-tension 101 provoque une chute de potentiel déterminée entre drain et source de ce transistor 101, la tension présente sur la source de ce transistor 101 étant alors représentative de la tension de sortie  $V_{REG1}$  moins la chute de potentiel déterminée présente aux bornes du transistor 101. On comprendra donc que le rôle essentiel du transistor haute-tension 101 est d'abaisser la tension de sortie  $V_{REG1}$  à un niveau tolérable pour les circuits situés en aval.

**[0034]** Le circuit diviseur de tension 105 est constitué dans cet exemple de l'agencement série, entre le terminal de drain du transistor p-MOS 102 et la masse  $V_{SS}$ , de deux résistances 151 et 152, le rapport de division de ce circuit diviseur 105 étant déterminé par les valeurs R3 et R4 de ces résistances. La seconde tension de sortie régulée  $V_{REG2}$  est délivrée à une borne 14 du circuit intégré 10 sur le terminal de drain du transistor p-MOS 102 aux bornes du circuit diviseur de tension 105, un second élément capacitif  $C_{EXT2}$  formant tampon étant typiquement branché à cette borne 14.

**[0035]** Le noeud de connexion entre les deux résistances 151 et 152 est relié à une première borne d'entrée de l'amplificateur différentiel 104. La tension appliquée sur cette première borne d'entrée de l'amplificateur différentiel 104 ainsi que la seconde tension de sortie régulée  $V_{REG2}$  sont proportionnelles dans un rapport déterminé par les valeurs R3 et R4 des résistances 151, 152. La seconde borne d'entrée de l'amplificateur différentiel 104 est reliée, de manière analogue à l'amplificateur différentiel 4, à la cellule de référence 6 produisant la tension de référence  $V_{REF}$ .

**[0036]** La sortie de l'amplificateur différentiel 104 est

appliquée sur la grille du transistor p-MOS 102. On comprendra à nouveau que l'agencement de l'amplificateur différentiel 104 illustré dans la figure 4 impose que la tension présente au noeud de sortie du circuit diviseur de tension 105, à savoir le noeud de connexion entre les résistances 151 et 152, soit sensiblement égale à la tension de référence  $V_{REF}$ , les valeurs R3 et R4 des résistances étant choisies de sorte que la seconde tension de sortie régulée  $V_{REG2}$  du circuit régulateur 1 ait une valeur déterminée, par exemple de l'ordre de 3 volts. Cette tension régulée  $V_{REG2}$  alimente notamment l'amplificateur différentiel 4 et la cellule de référence 6 du régulateur 1 comme déjà mentionné.

**[0037]** Contrairement à l'amplificateur différentiel 4, l'alimentation de l'amplificateur différentiel 104 est assurée, d'une part, par la masse  $V_{SS}$  et, d'autre part, par la tension présente au niveau du terminal de source du transistor p-MOS 102. Avantageusement, un élément capacitif 106 est disposé sur la sortie de l'amplificateur différentiel 104 entre les terminaux de grille et de drain du transistor p-MOS 102. Cet élément capacitif 106 assure une stabilité de la tension de sortie régulée  $V_{REG2}$ .

**[0038]** Dans le cadre spécifique d'une application dans un détecteur de fumée, le circuit régulateur selon l'invention permet le déplacement de la diode infrarouge du détecteur, nécessaire à la génération de l'impulsion infrarouge, de l'entrée vers la sortie du circuit régulateur sur la borne 12 du circuit où est délivrée la tension de sortie régulée  $V_{REG1}$ . La figure 4 montre schématiquement l'agencement de cette diode infrarouge indiquée par la référence numérique 200 et du moyen de commande 210 monté en série avec la diode 200, ici un transistor bipolaire, permettant le déclenchement de l'impulsion infrarouge.

**[0039]** Par rapport à la solution antérieure de la figure 1, la présente invention permet ainsi une réduction des pertes lors de la génération de l'impulsion infrarouge, notamment car la tension régulée utilisée pour cette génération est moindre que la tension d'entrée. Au moyen de la solution de la figure 1, on appellera à nouveau que la diode infrarouge et son moyen de commande sont placé à l'entrée haute-tension 21, la tension de sortie régulée n'étant pas suffisante pour alimenter cette diode infrarouge et permettre la génération de l'impulsion requise.

**[0040]** Comme déjà mentionné, l'amplificateur différentiel 4 utilisé dans le circuit régulateur de la figure 2 ou 4 est un amplificateur différentiel de type conventionnel dont un exemple de réalisation est illustré dans la figure 6. L'amplificateur différentiel 4 illustré dans la figure 6 comprend une paire différentielle de transistors M1, M2 (en l'occurrence deux transistors p-MOS identiques), les grilles desquels forment les entrées de l'amplificateur différentiel 4. Chaque transistor M1, M2 est branché en série dans la branche de référence d'un miroir de courant 41, 42, chaque miroir de courant 41, 42 comprenant de manière conventionnelle deux transistors n-MOS M11, M12 et M21, M22 branchés grille à

grille. Les transistors M12 et M22 des branches de sortie des miroirs de courant 41 et 42 sont eux-même branchés respectivement dans les branches de référence et de sortie d'un autre miroir de courant désigné globalement par la référence numérique 43 et comprenant deux transistors p-MOS M13 et M23. La sortie de l'amplificateur différentiel 4 est formée du noeud de connexion entre les transistors p-MOS M23 et n-MOS M22 de la branche de sortie du miroir de courant 43.

**[0041]** Un transistor p-MOS M3 connecté entre le terminal d'alimentation  $V_{DD}$  et le noeud de connexion des transistors p-MOS M1, M2 de la paire différentielle d'entrée assure une polarisation adéquate des transistors, une tension de polarisation déterminée  $V_{BIAS}$  étant appliquée sur la grille de ce transistor p-MOS M3.

**[0042]** Dans l'illustration de la figure 6, l'amplificateur différentiel 4 comporte en outre un étage de sortie additionnel comprenant des transistors p-MOS M5 et n-MOS M6 formant un agencement inverseur permettant de délivrer le signal de sortie désigné OUT et son inverse OUT\_B, un transistor p-MOS M4 commandé par la tension de polarisation  $V_{BIAS}$  étant branché en série avec ces transistors M5, M6 afin d'assurer une polarisation adéquate de ces derniers. De la sorte, l'amplificateur différentiel 4 forme un comparateur délivrant en sortie des signaux de niveaux logiques.

**[0043]** Il convient de mentionner que la structure de l'amplificateur différentiel 4 illustrée dans la figure 6 n'est donnée qu'à titre d'exemple uniquement et que d'autres configurations pourraient être envisagées par l'homme du métier.

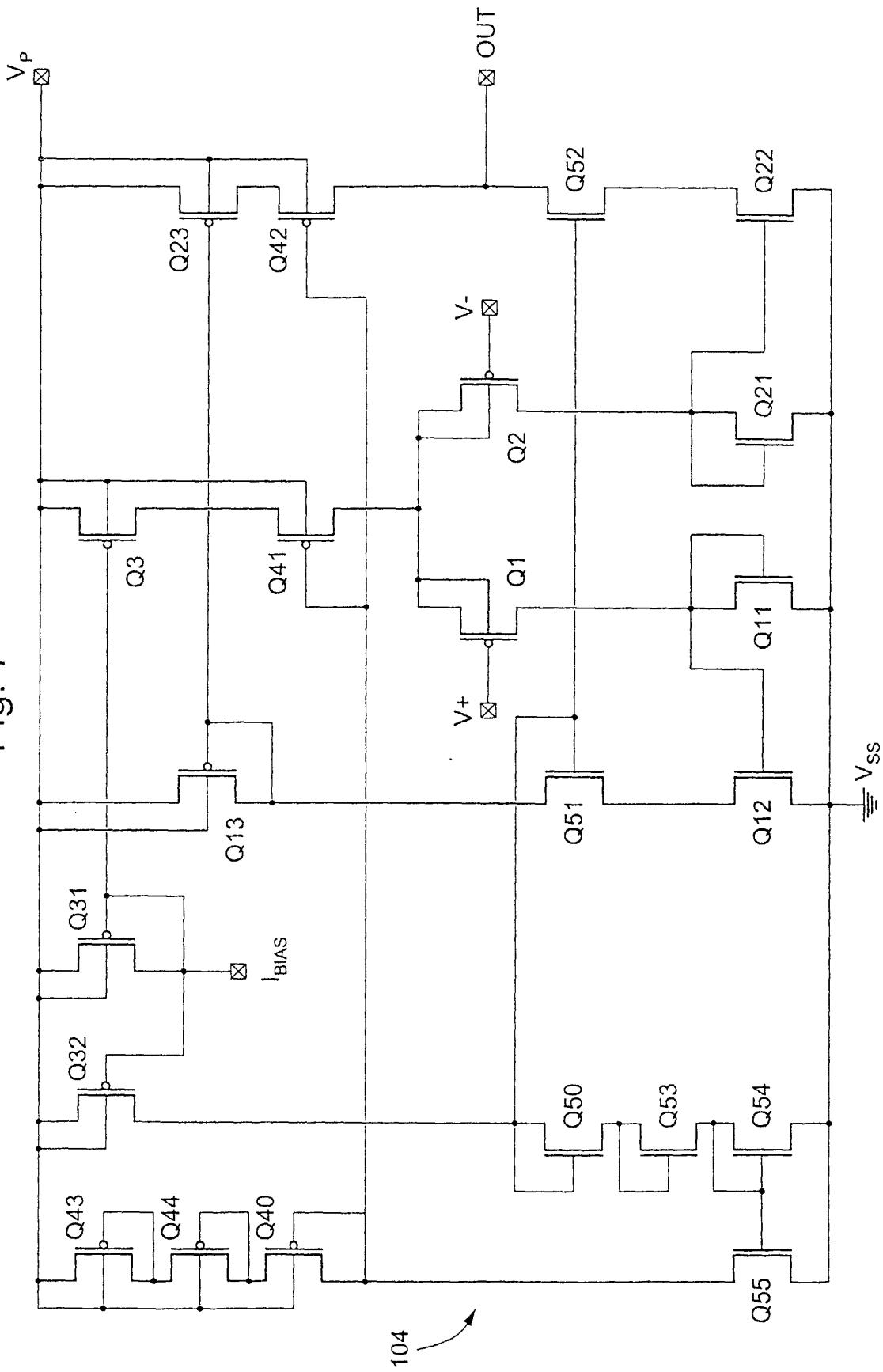

**[0044]** L'amplificateur différentiel 104 utilisé dans le circuit régulateur de la figure 4 doit être conçu pour tolérer des tensions plus élevées à ses bornes et peut être réalisé sur la base d'un schéma analogue à l'amplificateur différentiel 4 de la figure 6 en employant des montages cascodes bien connus de l'homme du métier, c'est-à-dire des montages de deux ou plusieurs transistors en série. La figure 7 montre un exemple de réalisation d'un tel amplificateur différentiel utilisant des techniques de montage cascode.

**[0045]** Les transistors Q1, Q2, Q11, Q12, Q21, Q22, Q13, Q23 et Q3 remplissent essentiellement les mêmes rôles que les transistors M1, M2, M11, M12, M21, M22, M13, M23 et M3 du circuit de la figure 6. Des montages cascodes sont utilisés afin de limiter les tensions susceptibles d'apparaître aux bornes des transistors de cet amplificateur différentiel 104, notamment les transistors branchés entre les tensions d'alimentation  $V_P$  et  $V_{SS}$ . On notera que la tension  $V_P$  est prélevée sur la source du transistor MOSFET haute-tension 101. Ainsi les transistors Q12 et Q22 sont chacun branchés en série respectivement avec un second transistor n-MOS Q51 disposé entre les transistors Q12 et Q13 et un second transistor n-MOS Q52 disposé entre les transistors Q22 et Q23. De même, les transistors Q3 et Q23 sont chacun branchés en série avec un second transistor p-MOS Q41 disposé entre le transistor Q3 et le noeud de con-

nexion de la paire différentielle et un second transistor p-MOS Q42 disposé entre les transistors Q22 et Q23. La borne de sortie de l'amplificateur différentiel 104 est formée du noeud de connexion entre les transistors Q42 et Q52.

**[0046]** Un transistor n-MOS additionnel Q50 forme de manière conventionnelle un miroir de courant avec les transistors Q51 et Q52. De même, un transistor p-MOS additionnel Q40 forme de manière conventionnelle un miroir de courant avec les transistors Q41 et Q42. Chacun de ces transistors Q40 et Q50 est branché en série avec un montage cascode de deux transistors respectivement p-MOS Q43, Q44 et n-MOS Q53, Q54. Le transistor n-MOS Q54 forme encore un miroir de courant avec un autre transistor n-MOS Q55 branché en série dans la branche comprenant les transistors p-MOS Q40, Q43 et Q44.

**[0047]** La polarisation des transistors est fixée par un courant de polarisation  $I_{BIAS}$  appliqué dans le chemin de courant d'un transistor p-MOS Q31 branché en miroir de courant avec le transistor Q3, ce courant de polarisation  $I_{BIAS}$  étant lui-même miroité dans la branche comprenant les transistors n-MOS Q50, Q53 et Q54 au moyen d'un transistor p-MOS Q32.

**[0048]** Le montage illustré dans la figure 7 assure qu'aucun des transistors de cet amplificateur différentiel 104 ne voit à ses bornes une tension trop élevée susceptible de causer un claquage de ce transistor.

**[0049]** Au même titre que l'amplificateur différentiel 4 de la figure 6, la configuration de la figure 7 n'est donnée qu'à titre d'exemple uniquement, l'homme du métier pouvant apporter de nombreuses modifications au schéma présenté, voire choisir une configuration alternative. On notera que l'amplificateur différentiel 104 doit essentiellement répondre à des contraintes plus élevées que l'amplificateur différentiel 4 étant donné que celui-ci est alimenté par une tension plus élevée, dans cet exemple typiquement de l'ordre de 4 à 7 volts.

**[0050]** La figure 5 montre une autre variante avantageuse du circuit régulateur selon l'invention sensiblement similaire à la variante de la figure 4. Outre les moyens permettant de délivrer la seconde tension de sortie régulée  $V_{REG2}$ , l'amplificateur différentiel 4 du circuit régulateur 1 est agencé pour présenter une hystérèse. Cette hystérèse a pour avantage de rendre moins critique la stabilité du régulateur et pour conséquence une variation périodique de la première tension régulée  $V_{REG1}$ . Le régulateur de la figure 5 forme de la sorte un régulateur de type « bang-bang » délivrant une tension régulée variant entre deux niveaux de tension déterminés. On notera en outre que l'amplificateur différentiel 4 forme dans cet exemple un comparateur, c'est-à-dire qu'il fournit des signaux de sortie OUT et OUT\_B de niveaux logiques.

**[0051]** L'hystérèse de l'amplificateur différentiel peut être générée de diverses manières. L'une d'entre elles est illustrée schématiquement dans la figure 5 et fait appel à deux portes de transmission 7, 8 branchées à l'en-

trée sur laquelle est appliquée la tension de sortie du circuit diviseur de tension 5, et un inverseur 9 branché sur la sortie de l'amplificateur différentiel 4. Par rapport, à la variante illustrée dans la figure 4, le circuit diviseur 5 est en outre légèrement modifié de sorte que la résistance 54 est subdivisée en deux résistances 55 et 56 dont la somme des valeurs R121 et R122 est équivalente à la valeur R12 de la résistance 54 de la figure 4. L'hystérèse est déterminée par le rapport des valeurs R11, R121, R122 et R2 des résistances 53, 55, 56 et 52.

**[0052]** Le noeud de connexion entre les résistances 55 et 56 est connecté à l'entrée de la première porte de transmission 7 et le noeud de connexion entre les résistances 56 et 52 est connecté à l'entrée de la seconde porte de transmission 8. L'état des portes de transmission 7 et 8 est contrôlé en fonction de la sortie de l'amplificateur différentiel 4, les portes de transmission 7 et 8 étant respectivement passante et non-passante lorsque le signal de sortie (non inversé) de l'amplificateur différentiel 4 est à l'état haut, et, à l'opposé, respectivement non passante et passante lorsque le signal de sortie de l'amplificateur différentiel 4 est à l'état bas. En l'occurrence, la sortie inversée OUT\_B de l'amplificateur différentiel 4 est connectée à la borne inverseuse de la porte 7 et la borne non-inverseuse de la porte 8, cette sortie inversée OUT\_B étant par ailleurs appliquée, via l'inverseur 9, sur la borne non-inverseuse de la porte 7 et la borne inverseuse de la porte 8.

**[0053]** Dans le cadre de la réalisation de la figure 5, il est par ailleurs avantageux de commander le dispositif externe de régulation 2 par l'intermédiaire d'un miroir de courant formé de deux transistors MOSFET haute-tension à canal n, à savoir le transistor 3 déjà mentionné et un transistor haute-tension analogue, désigné 3\*, dont la grille et le drain sont connectés ensemble à la sortie de l'amplificateur différentiel 4.

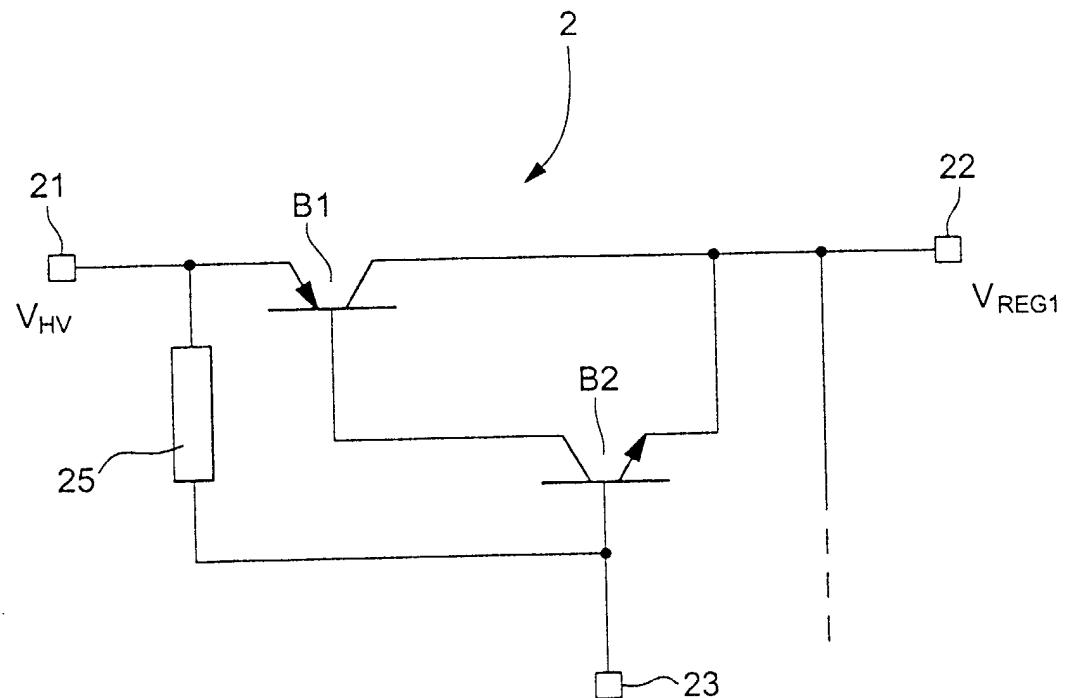

**[0054]** Finalement, comme déjà mentionné plus haut, le transistor JFET utilisé comme dispositif externe de régulation 2 dans les modes de réalisation décrits ci-dessus pourrait être remplacé par un autre dispositif adéquat. Par exemple, le transistor JFET peut avantageusement être remplacé par le dispositif illustré dans la figure 8 constitué d'un montage conventionnellement nommé « pseudo-Darlington » comprenant deux transistors bipolaires complémentaires, à savoir un transistor bipolaire de type pnp B1 et un transistor bipolaire de type npn B2. On notera qu'un montage Darlington comprenant deux transistors bipolaires de même type pourrait alternativement être utilisé en lieu et place du montage pseudo-Darlington de la figure 8.

**[0055]** Dans l'illustration de la figure 8, l'émetteur et le collecteur du transistor B1 forment respectivement l'entrée 21 sur laquelle est appliquée la haute tension d'entrée  $V_{HV}$  et la sortie 22 sur laquelle est délivrée la tension de sortie régulée  $V_{REG1}$ , la base de ce transistor B1 étant reliée au collecteur du transistor bipolaire B2, l'émetteur de ce transistor B2 étant connecté au collecteur du transistor B1. La base du transistor B2 forme le

terminal de commande 23 du dispositif externe de régulation. On notera que ce dispositif externe de régulation 2 comporte en outre une résistance 25 montée en parallèle entre le terminal d'entrée 21 et le terminal de commande 23.

**[0056]** Bien que le dispositif illustré dans la figure 8 comprenne un nombre plus élevé de composants, les coûts de ce dispositif sont néanmoins moindres que les coûts liés à l'utilisation d'un transistor JFET, ceci constituant donc un avantage dans l'optique d'une réduction des coûts de fabrication du circuit régulateur.

**[0057]** De nombreuses modifications et/ou améliorations de la présente invention peuvent être envisagées sans sortir du cadre de l'invention défini par les revendications annexées. En particulier, le circuit régulateur selon l'invention n'est nullement limité par le type de dispositif externe de régulation utilisé dans les modes de réalisation susmentionnés, à savoir un transistor JFET. Comme mentionné, d'autres agencements adéquats, tel l'agencement de la figure 8, peuvent être utilisés par l'homme du métier.

## Revendications

1. Circuit régulateur haute-tension (1) permettant de délivrer au moins une première tension de sortie régulée ( $V_{REG1}, V_{REG2}$ ) à partir d'une tension d'entrée haute ( $V_{HV}$ ), ce circuit régulateur comprenant un dispositif externe de régulation (2) comprenant un terminal d'entrée (21) sur lequel est appliquée ladite tension d'entrée haute, un terminal de sortie (22) sur lequel est délivrée ladite première tension de sortie régulée, et un terminal de commande (23) relié à un circuit de commande (10) dudit dispositif externe de régulation, ce circuit de commande (10) comprenant :

- un circuit diviseur de tension (5) connecté entre ledit terminal de sortie (22) et un potentiel de référence ou masse ( $V_{SS}$ ), et délivrant en sortie une première tension divisée proportionnelle, dans un rapport déterminé, à ladite première tension de sortie régulée ( $V_{REG1}$ ) ;

- une cellule de référence (6) délivrant en sortie une tension de référence déterminée ( $V_{REF}$ ) ; et

- un amplificateur différentiel (4) comprenant des première et seconde entrées sur lesquelles sont respectivement appliquées ladite première tension divisée délivrée par le circuit diviseur de tension (5) et ladite tension de référence ( $V_{REF}$ ) délivrée par la cellule de référence (6), la sortie de cet amplificateur différentiel commandant l'état de conduction dudit dispositif externe de régulation (2),

caractérisé en ce que ledit circuit de com-

- mande (10) comprend en outre un premier transistor MOSFET haute-tension (3) comprenant des terminaux de drain, de source et de grille respectivement connectés au terminal de commande (23) du dispositif externe de régulation (2), à la masse ( $V_{SS}$ ), et à la sortie dudit amplificateur différentiel (4).

2. Circuit régulateur selon la revendication 1, **caractérisé en ce que** ledit circuit de commande (10) comporte en outre des moyens (100) permettant de délivrer une seconde tension de sortie régulée ( $V_{REG2}$ ) assurant au moins l'alimentation dudit amplificateur différentiel (4) et de ladite cellule de référence (6).

3. Circuit régulateur selon la revendication 2, **caractérisé en ce que** lesdits moyens (100) comportent :

- un second transistor MOSFET haute-tension (101) comprenant des terminaux de drain, de source et de grille, les terminaux de drain et de grille de ce transistor MOSFET haute-tension (101) étant respectivement connectés au terminal de sortie (22) du dispositif externe de régulation (2) et à un seconde sortie du circuit diviseur de tension (5) délivrant une seconde tension divisée proportionnelle, dans un rapport déterminé, à ladite première tension de sortie régulée ( $V_{REG1}$ ) ;

- un transistor MOSFET à canal p (102) comprenant des terminaux de drain, de source et de grille, le terminal de source de ce transistor MOSFET à canal p (102) étant relié au terminal de source du second transistor MOSFET haute-tension (101), ladite seconde tension de sortie régulée ( $V_{REG2}$ ) étant délivrée sur le terminal de drain dudit transistor MOSFET à canal p ;

- un second circuit diviseur de tension (105) connecté entre le terminal de drain dudit transistor MOSFET à canal p (102) et la masse ( $V_{SS}$ ), et délivrant en sortie une tension divisée proportionnelle, dans un rapport déterminé, à ladite seconde tension de sortie régulée ( $V_{REG2}$ ) ; et

- un second amplificateur différentiel (104) comprenant des première et seconde entrées sur lesquelles sont respectivement appliquées ladite tension divisée délivrée par ledit second circuit diviseur de tension (105), et ladite tension de référence ( $V_{REF}$ ) délivrée par la cellule de référence (6), la sortie de ce second amplificateur différentiel (104) étant reliée au terminal de grille du transistor MOSFET à canal p (102), ce second amplificateur différentiel étant alimenté par la tension présente au noeud de connexion entre les terminaux de source dudit second transistor MOSFET haute-tension (101) et dudit transistor MOSFET à canal p (102).

4. Circuit régulateur selon la revendication 1, 2 ou 3, **caractérisé en ce que** ledit amplificateur différentiel (4) commandant l'état de conduction du dispositif externe de régulation (2) est agencé pour présenter une hystérèse de sorte que ladite première tension régulée ( $V_{REG1}$ ) varie entre des premier et second niveaux de tension déterminés.

5. Circuit régulateur selon la revendication 4, **caractérisé en ce que** ledit circuit de commande (10) comporte un transistor MOSFET haute-tension additionnel (3\*) comprenant des terminaux de drain, de source et de grille, ce transistor MOSFET haute-tension additionnel (3\*) formant, avec ledit premier transistor MOSFET haute-tension (3), un miroir de courant, les terminaux de drain et de grille du transistor MOSFET haute-tension additionnel (3\*) étant reliés ensemble au terminal de grille du premier transistor MOSFET haute-tension (3) et le terminal de source du transistor MOSFET haute-tension additionnel (3\*) étant relié à la masse ( $V_{SS}$ ).

6. Circuit régulateur selon l'une quelconque des revendications précédentes, **caractérisé en ce que** le ou lesdits transistors MOSFET haute-tension (3 ; 3\* ; 102) sont des transistors MOSFET à canal n comprenant un oxyde de grille présentant une épaisseur plus importante du côté drain que du côté source et une zone tampon du côté drain constituée d'un caisson de type n.

7. Circuit régulateur selon l'une quelconque des revendications précédentes, **caractérisé en ce que** le ou lesdits circuit diviseurs de tension (5, 105) sont des circuits diviseurs résistifs.

8. Circuit régulateur selon l'une quelconque des revendications 1 à 7, **caractérisé en ce que** ledit dispositif externe de régulation (2) est un transistor JFET comprenant des terminaux de drain, de source et de grille formant respectivement les terminaux d'entrée, de sortie et de commande dudit dispositif externe de régulation,

et **en ce que** ledit circuit de commande (10) comprend en outre un élément résistif (30) connecté entre les terminaux de commande (23) et de sortie (22) dudit dispositif externe de régulation (2).

9. Circuit régulateur selon l'une quelconque des revendications 1 à 7, **caractérisé en ce que** ledit dispositif externe de régulation (2) comporte un montage Darlington ou pseudo-Darlington de deux transistors bipolaires (B1, B2).

10. Circuit régulateur selon la revendication 9, **carac-**

**térisé en ce que** ledit dispositif externe de régulation (2) comporte un transistor bipolaire pnp (B1) et un transistor bipolaire npn (B2) agencé en montage pseudo-Darlington,

la base et le collecteur du transistor bipolaire pnp (B1) étant respectivement relié au collecteur et à l'émetteur du transistor bipolaire npn (B2),

l'émetteur du transistor bipolaire pnp (B1), le collecteur du transistor bipolaire pnp (B1) et la base du transistor bipolaire npn (B2) formant respectivement les terminaux d'entrée, de sortie et de commande dudit dispositif externe de régulation,

un résistance (25) étant en outre montée entre l'émetteur du transistor bipolaire pnp (B1) et la base du transistor bipolaire npn (B2).

5

10

15

20

25

30

35

40

45

50

55

**Fig.1**

(ART ANTERIEUR)

**Fig.2**

Fig.3a

Fig.3b

Fig. 4

Fig. 5

Fig. 6

Fig. 7

Fig.8

Office européen

des brevets

## RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande

EP 01 20 2429

| DOCUMENTS CONSIDERES COMME PERTINENTS                                                     |                                                                                                                                                                                                     |                            |                                              |  |  |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------|--|--|

| Catégorie                                                                                 | Citation du document avec indication, en cas de besoin,<br>des parties pertinentes                                                                                                                  | Revendication<br>concernée | CLASSEMENT DE LA<br>DEMANDE<br>(Int.Cl.7)    |  |  |

| A                                                                                         | US 3 913 082 A (HAMM JEFFREY E)<br>14 octobre 1975 (1975-10-14)<br>* colonne 1, ligne 5 - colonne 2, ligne 3<br>*<br>* colonne 4, ligne 42 - colonne 6, ligne<br>31; revendications 1-8; figure 5 * | 1-10                       | G08B17/10<br>G08B17/00<br>G01J1/42           |  |  |

| A                                                                                         | US 3 611 335 A (OGDEN WILBUR L ET AL)<br>5 octobre 1971 (1971-10-05)<br>* colonne 1, ligne 5-55 *<br>* colonne 4, ligne 56 - colonne 7, ligne<br>65; revendications 1-15; figures 2,3 *             | 1-10                       |                                              |  |  |

| A                                                                                         | PATENT ABSTRACTS OF JAPAN<br>vol. 013, no. 009 (P-811),<br>11 janvier 1989 (1989-01-11)<br>& JP 63 217231 A (NOHMI BOSAI KOGYO CO<br>LTD), 9 septembre 1988 (1988-09-09)<br>* abrégé *              | 1-10                       |                                              |  |  |

|                                                                                           |                                                                                                                                                                                                     |                            | DOMAINES TECHNIQUES<br>RECHERCHES (Int.Cl.7) |  |  |

|                                                                                           |                                                                                                                                                                                                     |                            | G08B<br>G01J                                 |  |  |

| Le présent rapport a été établi pour toutes les revendications                            |                                                                                                                                                                                                     |                            |                                              |  |  |

| Lieu de la recherche                                                                      | Date d'achèvement de la recherche                                                                                                                                                                   | Examinateur                |                                              |  |  |

| MUNICH                                                                                    | 11 janvier 2002                                                                                                                                                                                     | Pierron, P                 |                                              |  |  |

| CATEGORIE DES DOCUMENTS CITES                                                             |                                                                                                                                                                                                     |                            |                                              |  |  |

| X : particulièrement pertinent à lui seul                                                 | T : théorie ou principe à la base de l'invention                                                                                                                                                    |                            |                                              |  |  |

| Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie | E : document de brevet antérieur, mais publié à la date de dépôt ou après cette date                                                                                                                |                            |                                              |  |  |

| A : arrrière-plan technologique                                                           | D : cité dans la demande                                                                                                                                                                            |                            |                                              |  |  |

| O : divulgation non écrite                                                                | L : cité pour d'autres raisons                                                                                                                                                                      |                            |                                              |  |  |

| P : document intercalaire                                                                 | .....                                                                                                                                                                                               |                            |                                              |  |  |

| EPO FORM 1503.03.82 (P04C02)                                                              | & : membre de la même famille, document correspondant                                                                                                                                               |                            |                                              |  |  |

**ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE

RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.**

EP 01 20 2429

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Lesdits membres sont contenus au fichier informatique de l'Office européen des brevets à la date du

Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

11-01-2002

| Document brevet cité<br>au rapport de recherche |   | Date de<br>publication |                                                                | Membre(s) de la<br>famille de brevet(s)                                                                                                     | Date de<br>publication                                                                                                                                 |

|-------------------------------------------------|---|------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| US 3913082                                      | A | 14-10-1975             | CA<br>GB<br>JP                                                 | 1012261 A1<br>1450819 A<br>49107794 A                                                                                                       | 14-06-1977<br>29-09-1976<br>14-10-1974                                                                                                                 |

| US 3611335                                      | A | 05-10-1971             | BE<br>CA<br>CH<br>DE<br>DE<br>DK<br>FR<br>GB<br>JP<br>NL<br>NO | 741650 A<br>959976 A2<br>506147 A<br>1957172 A1<br>1966343 A1<br>131251 B<br>2023218 A5<br>1280297 A<br>52008158 B<br>6903185 A<br>124751 B | 16-04-1970<br>24-12-1974<br>15-04-1971<br>09-07-1970<br>25-05-1972<br>16-06-1975<br>07-08-1970<br>05-07-1972<br>07-03-1977<br>02-09-1969<br>29-05-1972 |

| JP 63217231                                     | A | 09-09-1988             | JP<br>JP                                                       | 1998537 C<br>7015410 B                                                                                                                      | 08-12-1995<br>22-02-1995                                                                                                                               |