# Europäisches Patentamt European Patent Office Office européen des brevets

EP 1 320 116 A1

(12)

# **EUROPEAN PATENT APPLICATION** published in accordance with Art. 158(3) EPC

(43) Date of publication: 18.06.2003 Bulletin 2003/25

(21) Application number: 02722726.3

(22) Date of filing: 24.04.2002

(51) Int Cl.7: **H01J 1/312**, H01J 9/02

(86) International application number: **PCT/JP02/04054**

(11)

(87) International publication number: WO 02/089166 (07.11.2002 Gazette 2002/45)

(84) Designated Contracting States:

AT BE CH DE DK ES FI FR GB IT LI NL SE

(30) Priority: 24.04.2001 JP 2001125156 24.04.2001 JP 2001125157 28.05.2001 JP 2001159625 26.10.2001 JP 2001329908

(71) Applicant: Matsushita Electric Works, Ltd. Kadoma-shi, Osaka 571-8686 (JP)

(72) Inventors:

KOMODA, Takuya, MATSUSHITA ELECTRIC WORKS, LTD. Kadoma-shi, Osaka 571-8686 (JP)

AIZAWA, Koichi, MATSUSHITA ELECTRIC WORKS, LTD. Kadoma-shi, Osaka 571-8686 (JP)

HONDA, Yoshiaki, MATSUSHITA ELECTRIC WORKS, LTD. Kadoma-shi, Osaka 571-8686 (JP)  ICHIHARA, Tsutomu, MATSUSHITA ELECTRIC WORKS, LTD. Kadoma-shi, Osaka 571-8686 (JP)

WATABE, Yoshifumi, MATSUSHITA ELECTRIC WORKS, LTD. Kadoma-shi, Osaka 571-8686 (JP)

HATAI, Takashi, MATSUSHITA ELECTRIC WORKS, LTD. Kadoma-shi, Osaka 571-8686 (JP)

BABA, Toru, MATSUSHITA ELECTRIC WORKS, LTD. Kadoma-shi, Osaka 571-8686 (JP)

TAKEGAWA, Yoshiyuki, MATSUSHITA ELECT. WORKS, LTD. Kadoma-shi, Osaka 571-8686 (JP)

(74) Representative: Dallmeyer, Georg, Dipl.-Ing. et al Patentanwälte von Kreisler-Selting-Werner Postfach 10 22 41 50462 Köln (DE)

# (54) FIELD EMISSION ELECTRON SOURCE AND PRODUCTION METHOD THEREOF

In a field emission-type electron source (10), a strong field drift layer (6) and a surface electrode (7) consisting of a gold thin film are provided on an n-type silicon substrate (1). An ohmic electrode (2) is provided on the back surface of the n-type silicon substrate (1). A direct current voltage is applied so that the surface electrode (7) becomes positive in potential relevant to the ohmic electrode (2). In this manner, electrons injected from the ohmic electrode (2) into the strong field drift layer (6) via the n-type silicon substrate (6) drift in the strong field drift layer (6), and is emitted to the outside via the surface electrode (7). The strong field drift layer (6) has: a number of semiconductor nanocrystals (63) of nano-meter order formed partly of a semiconductor layer configuring the strong field drift layer (6); and a number of insulating films (64) each of which is formed on the surface of each of the semiconductor nanocrystals (63) and each having film thickness to an extent such that an electron tunneling phenomenon occurs.

#### Description

#### **TECHNICAL FIELD**

**[0001]** The present invention relates to a field emission-type electron source which emits electron beams by means of electric field emission using semiconductor materials, and further to a manufacturing method thereof. More particularly, the present invention relates to a method and apparatus for forming insulating thin films on surfaces of semiconductor crystals when the field emission-type electron source is manufactured.

#### BACKGROUND OF THE INVENTION

[0002] Conventionally, as a field emission-type electron source (hereinafter, simply referred to as "electron source"), for example, there is known a Spindt type electrode disclosed in U.S. Patent No. 3,665,241 or the like. The Spindt type electrode includes a substrate having a number of fine triangular pyramid shaped emitter chips disposed thereon; and a gate layer which is insulated relevant to the emitter chips and has emission holes for exposing the tip ends of the emitter chips. The Spindt type electrode emits electron beams through the emission holes from the tip ends of the emitter chips by applying a high voltage so that the emitter chips are negative in polarity relevant to the gate layer.

[0003] However, the Spindt type electrode is complex in manufacturing process, and it is difficult to precisely fabricate a number of triangular pyramid shaped emitter chips. Thus, for example, in the case where this is applied to a planar light emitter or display, there is such a problem that it is difficult to make its surface area larger. In addition, in the Spindt type electrode, the electric field concentrates on the tip ends of the emitter chips. Thus, in the case where the degree of vacuum around the tip ends of the emitter chips is low so that the residual gas exists, the residual gas is ionized to positive ions by means of the emitted electrons. The positive ions collide to the tip ends of the emitter chips so that the tip ends of the emitter chips are subjected to damage (for example, damage due to ion shock). Thus, there occurs such a disadvantage that the current density or emission efficiency of the emitted electrons becomes unstable, and the service lives of the emitter chips are reduced. Therefore, in order to prevent the above-mentioned disadvantage, it is required to use the Spindt type electrode in a high vacuum (about 10<sup>-5</sup> Pa to about 10<sup>-6</sup> Pa) condition. As the result, there is a problem that higher cost or complicated handling may result.

[0004] In order to improve the above-mentioned disadvantage, there is proposed an electron source of an MIM (Metal Insulator Metal) type or MOS (Metal Oxide Semiconductor) type. The former is a planar type electron source having a deposited structure of metal - insulating film - metal, while the latter is a planar type electron source having a deposited structure of metal - oxide

film - semiconductor. In an electron source of such type, in order to improve the electron emission efficiency (that is, in order to emit much electrons), it is required to reduce the thickness of an insulating film or oxide film. However, if the thickness of the insulating film or oxide film is too small, there is a danger that insulation destruction occurs when a voltage is applied between the upper and lower electrodes of the deposited structures. Such insulation destruction must be prevented, and thus, there is a limitation in reduction of the thickness of the insulating film or oxide film. Thus, there is a problem that electron emission efficiency (lead-out efficiency) cannot be increased so much.

[0005] In recent years, there is proposed an electron source (semiconductor cool electron emission element) with its high electron emission efficiency so as to apply a voltage between a semiconductor substrate and a surface electrode, thereby emitting electrons. In the electron source, one surface of a single-crystalline semiconductor substrate such as silicon substrate is anodically oxidized, thereby forming a porous semiconductor layer (porous silicon layer). Then, on the porous semiconductor layer, a surface electrode consisting of a metal thin film (electrically conductive thin film) is formed.

**[0006]** However, in the electron source disclosed in Japanese Laid-open Patent Publication No. 8-250766, a popping phenomenon is likely to occur during electron emission, and non-uniformity is likely to occur in electron emission quantity. Thus, if this is applied to a planar light emitter or display device, there is a problem that non-uniform light emission is produced.

[0007] In order to solve the above-mentioned problems, for example in Japanese Patent Applications No. 10-272340 and No. 10-272342 etc., the present inventors proposed an electron source in which a strong field drift layer (hereinafter simply referred to as "drift layer") where electrons injected from the electrically conductive substrate drift is interposed between the electrically conductive substrate and the metal thin film (surface electrode).

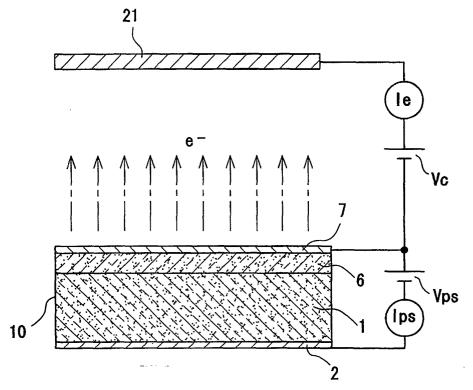

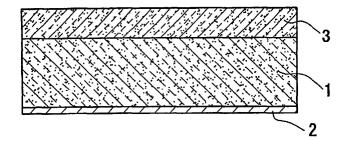

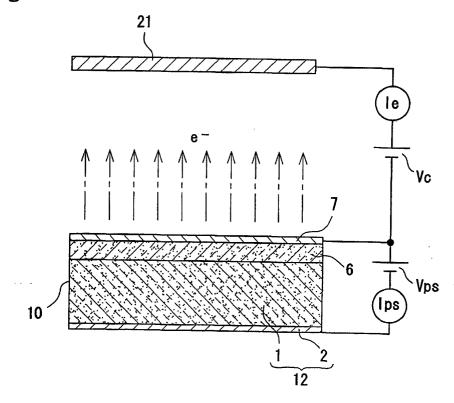

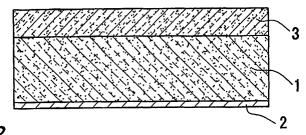

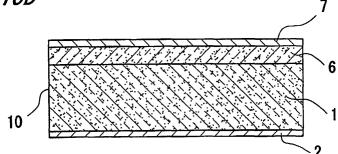

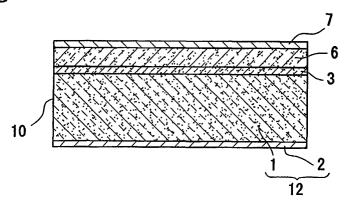

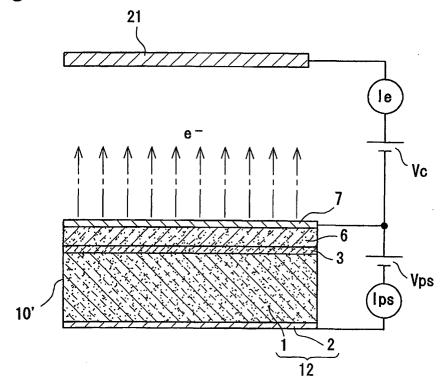

[8000] For example, as shown in Fig. 38, in an electron source 10' of such type, a drift layer 6 consisting of an oxidized porous polycrystalline silicon layer (porous polycrystalline silicon layer) on a main surface side of an n-type silicon substrate 1 that is an electrically conductive substrate. A surface electrode 7 consisting of a metal thin film (for example, metal film) is formed on the drift layer 6. In addition, an ohmic electrode 2 is formed on the back face of an n-type silicon substrate 1. A lower electrode 12 (electrically conductive substrate) is composed of the n-type silicon substrate 1 and ohmic electrode 2. In an example shown in Fig. 38, although a nondoped polycrystalline silicon layer 3 is interposed between the lower electrode 12 and the drift layer 6, there is proposed an electron source having the drift layer 6 formed on the lower electrode 12.

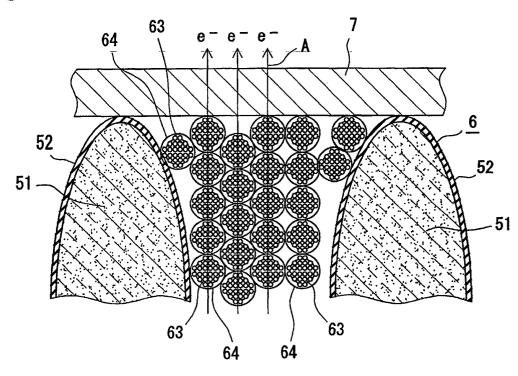

**[0009]** Then, a collector electrode 21 consisting of a transparent electrically conductive film (for example,

40

ITO film) is disposed in opposite to the surface electrode 7. In order to emit an electron from the electron source 10', while a vacuum is provided between the surface electrode 7 and the collector electrode 21, a direct current voltage Vps is applied between the surface electrode 7 and the lower electrode 12 so that the surface electrode 7 becomes high in potential relevant to the lower electrode 12. In addition, a direct current voltage Vc is applied between the collector electrode 21 and the surface electrode 7 so that the collector electrode 21 becomes high in potential relevant to the surface electrode 7. When direct current voltages Vps and Vc are properly set, electrons injected from the lower electrode 12 drift in the drift layer 6, and are emitted via the surface electrode 7 (the single dotted chain line in Fig. 38 indicates the flow of electrons "e-" emitted through the surface electrode 7). The thickness of the surface electrode 7 is set to about 3 nm to 15 nm.

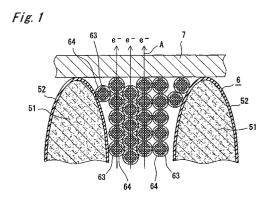

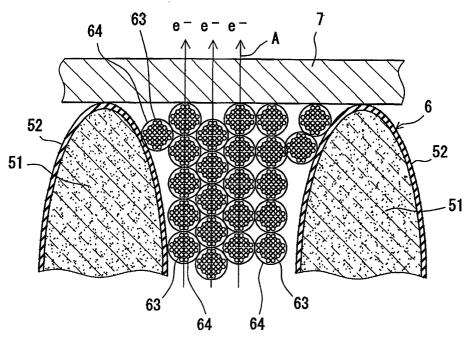

[0010] In the drift layer 6, after a non-doped polycrystalline silicon layer has been formed on the lower electrode 12, the polycrystalline silicon layer is made porous in accordance with anodic oxidization processing, thereby forming a porous polycrystalline silicon layer. Thus porous polycrystalline silicon layer is formed in accordance with a rapid thermal oxidizing technique for carrying out rapid thermal oxidization at 900°C, for example. **[0011]** As shown in Fig. 39, the drift layer 6 includes: at least columnar polycrystalline silicon grains 51; thin insulating films 52; a number of silicon nanocrystals 63 of nano-meter order; and a number of insulating films 64. The grains 51 are arranged on the main surface side of the n-type silicon substrate 1 (namely, the surface electrode 7 side in the lower electrode 12). The insulating films 52 are formed on the surfaces of the grains 51. The silicon nanocrystals 63 are interposed among the grains 51. The insulating films 64 are formed on the surfaces of the silicon nanocrystals 63, each of which has a film thickness smaller than the crystalline particle size of the silicon nanocrystal 63. In short, in the drift layer 6, the surface of each grain 51 in the polycrystalline silicon layer is made porous, and a crystalline state is maintained at the center portion of each grain 51. Each grain 51 extends in the thickness direction of the lower electrode 12. Insulating films 52 and 64 are composed of silicon oxide films.

**[0012]** In the electron source 10', it is believed that electron emission occurs in the following model. That is, during electron emission, a direct current voltage Vps having the surface electrode 7 provided as a high potential is applied between the surface electrode 7 and the lower electrode 12, and a direct current voltage Vc having the collector electrode 21 provided as a high potential is applied between the collector electrode 21 and the surface electrode 7. When the direct current voltage Vps reaches a predetermined value (critical value), the electrons "e-" are injected from the lower electrode into the drift layer 6 due to thermal excitation. On the other hand, a majority of the electron field applied to the

layer 6 is applied to the insulating films 64. Thus, the injected electrodes "e-" are accelerated by the strong electric field applied to the insulating films 64. Then, the electrons "e-" drift in the drift layer 6 in an orientation indicated by the arrow A in Fig. 39 from a region between the grains 51 toward the surface, tunnel the surface electrode 7, and are emitted into the vacuum.

[0013] In this manner, in the drift layer 6, the electrons injected from the lower electrode 12 are accelerated and drift in the electric field applied to the insulating films 64 without being hardly diffused at the silicon nanocrystals 63. Then, the electrons are emitted via the surface electrode 7 (ballistic type electron emission phenomenon). At this time, a heat generated in the drift layer 6 is radiated via the grains 51. Thus, popping phenomenon does not occur during electron emission, and the electrons can be constantly emitted. The electrons arrived at the surface of the drift layer 6 are believed to be hot electrons. The electrons easily tunnel the surface electrode 7, and are emitted into the vacuum.

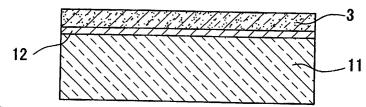

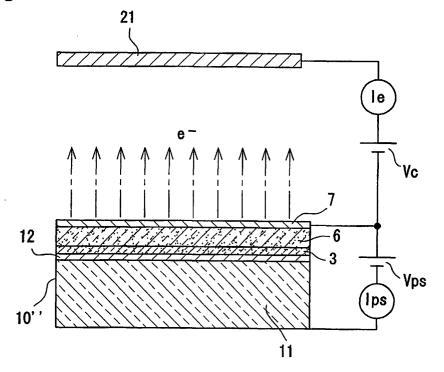

[0014] In the meantime, in the electron source 10', the lower electrode 12 is composed of the n-type silicon substrate 1 and ohmic electrode 2. However, as shown in Fig. 40, for example, there is proposed an electron source 10" in which the lower electrode 12 consisting of a metal material is formed on one surface of an insulating substrate 11 consisting of a glass substrate. In Fig. 40, constituent elements common to the electron source 10' shown in Fig. 38 are designated by like reference numbers. A description thereof is omitted here. In the electron source 10" shown in Fig. 40 as well, electrons can be emitted in a process similar to a case of the electron source 10' shown in Fig. 38.

[0015] In the electron sources 10' and 10", in general, a current flowing between the surface electrode 7 and the lower electrode 12 is referred to as a diode current lps, and a current flowing between the collector electrode 21 and the surface electrode 7 is referred to as an emission current (emission electron current) le. As a rate (le / lps) of the emission current le to the diode current lps increases, electron emission efficiency ((le / lps) x 100 [%]) increases. In the electron sources 10' and 10", even if the direct current voltage Vps applied between the surface electrode 7 and the lower electrode 12 is defined as a low voltage of about 10 V to 20 V, electrons can be emitted. In addition, as the direct current voltage Vps increases, the emission current le increases.

**[0016]** In the meantime, in a process for manufacturing the electron sources 10' and 10", the step of forming the drift layer 6 consists of the film forming step, anodic oxidization processing step, and oxidizing step. In the film forming step, a non-doped polycrystalline silicon layer is formed as a semiconductor layer on one surface of the lower electrode 12. In the anodic oxidization processing step, a polycrystalline silicon layer is made porous in accordance with anodic oxidization processing step, thereby forming a porous polycrystalline silicon

layer that contains the polycrystalline silicon grains 51 and silicon nanocrystals 63. In the anodic oxidization processing step, there is employed a mixture solution obtained by mixing a hydrogen fluoride water solution and ethanol at substantially 1:1 as an electrolytic solution employed for anodic oxidization. In the oxidizing step, the porous polycrystalline silicon layer is rapidly thermally oxidized in accordance with the rapid thermal oxidization technique that is a high temperature process, and thin insulating films (silicon oxide films) 52 and 64 are formed respectively on the surfaces of the grains 51 and silicon nanocrystals 63.

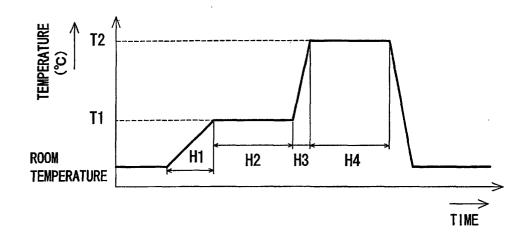

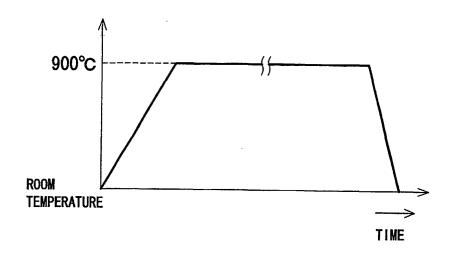

**[0017]** In addition, as shown in Fig. 41, in the oxidizing step, a substrate temperature is risen from room temperature to a heat treatment temperature (for example, 900°C) in dry oxygen by employing a lamp annealing device, for example. Then, the substrate temperature is held at this heat treatment temperature by a predetermined heat treatment time (for example, 1 hour), thereby oxidizing the porous polycrystalline silicon layer. Then, the substrate temperature is lowered to room temperature.

**[0018]** There is proposed an electron source formed of a nitride porous polycrystalline silicon layer instead of an oxidized porous polycrystalline silicon layer. Further, there is proposed an electron source formed of the oxidized or nitrided porous single-crystalline silicon layer as well.

**[0019]** In a conventional electron source comprising such a drift layer, it is possible to increase an area and to ensure cost reduction. In the case where an electron source of such type is applied as an electron source of a display, the surface electrode or lower electrode (electrically conductive substrate) may be properly patterned. However, in such a conventional electron source, the following problems occur.

### (Problem 1)

**[0020]** In the conventional electron source of such type, there is a problem that there increases a deviation in characteristics such as electron emission efficiency, dielectric strength, service life between manufactured lots. As a result of detailed study of such cause, it has been found that this deviation is caused by a deviation in thickness of the silicon oxide film that is an insulating film.

# (Problem 2)

**[0021]** As has been described previously, a rapid thermal oxidization technique is employed in the oxidizing step. However, in order to form the silicon oxide films 52 and 64 with their good film quality on the surface of all the grains 51 and silicon nanocrystals 63, there can be employed the oxidizing step for oxidizing a porous polycrystalline silicon layer in an electrolytic solution consisting of water solution such as sulfuric acid or nitric acid

in accordance with an electrochemical oxidization technique.

[0022] By employing the electrochemical oxidization technique, a process temperature can be reduced as compared with the case of employing the rapid thermal oxidization technique. Thus, a resistance on a substrate material is reduced. In the case of employing a glass substrate, a non-alkali glass substrate or low alkali glass substrate and the like with its low heat resistance temperature and modest price can be employed as compared with a quartz glass substrate. Therefore, there is an advantage that a larger area for the electron sources 10' and 10" and cost reduction can be achieved more efficiently.

[0023] However, in the conventional electron source manufactured by oxidizing the porous polycrystalline silicon layer in accordance with an electrochemical oxidization technique, there is a problem that the dielectric strength is low as compared with the electron source oxidized and manufactured in accordance with the rapid thermal oxidization technique. This is because an SiO<sub>2</sub> film formed in accordance with the electrochemical oxidization technique is much in water content or strain as compared with that formed in accordance with the rapid thermal oxidization technique. In the electron sources 10' and 10" manufactured by oxidizing the porous polycrystalline silicon layer in accordance with the rapid thermal oxidization technique as well, it is desired that the electron emission efficiency, dielectric strength, and service life be improved more remarkably. However, as the result of a variety of analytical evaluations (such as photo luminescence measurement, sectional TEM observation, or XPS composition analysis, for example) regarding the drift layer 6, the following findings were obtained. That is, the film thickness of the silicon oxide film 64 increases as the film is closer to the surface of the drift layer 6, the silicon nanocrystal 63 is destroyed, and the silicon nanocrystal 63 does not exist in the vicinity of the surface of the drift layer 6. Thus, in the conventional electron sources 10' and 10", there is a danger that a part of the electrons injected into the drift layer 6 are diffused or captured by the silicon oxide film 64 which is larger than the film thickness (degree of mean free path of electrons) to an extent such that an electron tunneling phenomenon occurs. In this case, there is a danger that the electron emission efficiency is lowered, and the dielectric strength and service life is reduced.

# (Problem 3)

**[0024]** In anodic oxidization processing, a mixture solution between hydrogen fluoride water solution and ethanol is utilized as an electrolytic solution. Thus, as shown in Fig. 42, the porous polycrystalline silicon layer formed in accordance with anodic oxidization processing is terminated by a hydrogen atom on its top surface. Further, it is believed that water is adsorbed on the surface of the porous polycrystalline silicon layer.

[0025] If the porous polycrystalline silicon layer formed in accordance with anodic oxidization processing is oxidized on a temperature profile as shown in Fig. 41, a hydrogen atom remains or Si-OH coupling occurs, as shown in Fig. 43. Thus, there is a problem that an oxide film with its fine structure consisting of SiO2 is hardly produced, and the dielectric strength is lowered. Further, there is a problem that a fluorine atom as well remains in the drift layer 6 other than the hydrogen atom. In addition, the content of hydrogen in the drift 6 is comparatively large in quantity. Thus, there is a danger that the distribution of hydrogen in the drift layer 6 changes with an elapse of time (for example, a hydrogen atom desorbs from the surface of the drift layer 6), and the stability of electron emission efficiency with an elapse of time is impaired.

#### (Problem 4)

[0026] When a comparatively inexpensive glass substrate (such as no-alkali glass substrate, a low alkali glass substrate, or soda lime glass substrate, for example) is employed as an insulating substrate 11 in the electron source 10", as compared with a quartz glass substrate, although a heat resistance temperature of the insulating substrate 11 is lowered, cost reduction can be achieved. Because of this, it is believed that the temperature of forming the porous silicon layer is lowered (for example, set to 600°C or less).

[0027] However, in the case of forming the polycrystalline silicon layer at a comparatively low temperature, the crystalline properties of the polycrystalline silicon layer is impaired as compared with the polycrystalline silicon layer formed at a comparatively high temperature, and a large number of defects occurs. As a result, there is a problem that a number of defects contained in the drift layer 6 increases, the electron emission characteristics are impaired, and the reliability is lowered. For example, if a defect exists in the silicon oxide films 52 and 64 each in the drift layer 6, the dielectric strength of the silicon oxide films 52 and 64 each is lowered, and the dielectric strength of the electron source is lowered. Alternatively, the electron emission efficiency is lowered because of electron diffusion.

### (Problem 5)

**[0028]** In the conventional electron sources 10' and 10", in the case where these sources are continuously driven for a long time, there is problem that the diode current lps decreases with an elapse of time, and concurrently, the emission current lc decreases as well. As a cause thereof, it is believed that an electron is captured by a trap in an insulating film 64, an electric field in the insulating film 64 is alleviated, and the tunneling probability of electrons is lowered.

**[0029]** Further, in the above-described manufacturing method, there is employed a process requiring a com-

paratively high heat treatment temperature (for example, 900°C) and a comparatively long heat treatment time (for example, 1 hour) in the oxidizing step. Thus, there is a problem that the process time is extended. Further, there is a problem that a non-alkali glass substrate or low alkali glass substrate with its low heat resistance temperature, which is comparatively inexpensive as compared with a quartz glass substrate, can not be employed as an insulating substrate 11.

# (Problem 6)

[0030] In the conventional electron sources 10' and 10", although an electron can be emitted constantly with high efficiency, it is desired to more remarkably improve the electron emission characteristics such as electron emission efficiency or the reliability such as dielectric strength. However, in the electron sources 10' and 10", it is believed that there exists a defect caused by a manufacturing process in the drift layer 6. For example, in the case where a defect exists in the silicon nanocrystal 63 or silicon oxide films 52 and 64 and the like, there is a problem that the lowering of electron emission efficiency due to electron diffusion or the lowering dielectric strength and the like is caused.

#### DISCLOSURE OF THE INVENTION

**[0031]** The present invention has been achieved to solve the above-mentioned problems. It is an object of the present invention to provide an electron source and a manufacturing method thereof with high efficiency and high reliability that can be employed for a flat panel display element, a planar light source, or a solid vacuum device and the like, and that can emit electron beams in accordance with preferable electric field emission.

**[0032]** It is another object of the present invention to provide an electron source and a manufacturing method thereof making it easy to design the dielectric strength and the service life.

**[0033]** It is a still another object of the present invention to provide a method and apparatus for forming insulation thin films capable of forming insulation thin films with high dielectric strength as compared with the prior art, or alternatively, to provide an electron source capable of extending the service life as compared with the prior art

**[0034]** It is a still another object of the present invention to provide a method of manufacturing the electron source capable of achieving cost reduction and capable of improving the electron emission characteristics and reliability such as electron emission efficiency.

**[0035]** The electron source (field emission-type electron source) according to the present invention includes: an electrically conductive substrate; a drift layer (strong field drift layer) formed on the electrically conductive substrate; and a surface electrode formed on the drift layer. The drift layer has a number of semiconductor na-

nocrystals of nano-meter order formed partly of a semiconductor layer configuring the drift layer, and has a number of insulating films each of which is formed on the surface of each of the semiconductor nanocrystals, the films having film thickness smaller than the crystalline particle size of the semiconductor nanocrystals. The insulating film formed on the surface of each of the semiconductor nanocrystal has film thickness (degree of mean free path of electrons) in which an electron tunneling phenomenon occurs when an electron field is applied. In this manner, a voltage is applied between the surface electrode and the electrically conductive substrate so that the surface electrode becomes high in potential, whereby the electrons injected from the electrically conductive substrate into the drift layer drift in the drift layer, and are emitted via the surface electrode.

**[0036]** In this electron source, it is possible to reduce diffusion of the electrons in each insulating film, and to reduce the difference of thickness of the insulating films in the drift layer. Thus, it is easy to design dielectric strength and lifetime in electron source.

[0037] In this electron source, it is preferable that the water contained in the insulating film formed on the surface of each of the semiconductor nanocrystals is substantially 0 (substantially free of water). In this case, a defect or strain and the like that adversely affects electrical characteristics of the electron source is alleviated, and thus, insulating films with high dielectric strength and extended service life can be formed.

**[0038]** In this electron source, it is preferable that a compound layer or alloy layer consisting of a semiconductor and metal is interposed on a critical surface between the semiconductor layer configuring the drift layer and the electrically conductive substrate. In addition, it is preferable that the semiconductor layer is substantially crystallized on the critical surface between the semiconductor layer configuring the drift layer and the electrically conductive substrate. In those cases, a barrier layer or high resistance layer between the semiconductor layer and electrically conductive substrate can be reduced, and thus, the electron emission efficiency and reliability are improved.

[0039] A method of manufacturing an electron source according to the present invention is a process for manufacturing the above electron source according to the present invention. This electron source manufacturing method to form the insulating films on the surfaces of the semiconductor nanocrystals is carried out by any one of the electrochemical method, rapid thermal oxidization technique, rapid thermal nitriding technique and rapid thermal oxidizing and nitriding technique or a combination thereof. By employing this manufacturing method, the film thickness of the insulating films can be obtained as thickness (degree of mean free path of electrons) if the electron tunneling phenomenon occurs.

[0040] In the method of manufacturing the electron source, after the insulating films have been formed on the surfaces of the semiconductor nanocrystals, it is

preferable that annealing processing at a temperature of 700°C or less be carried out in a vacuum, inert gas, foaming gas, or nitrogen gas. In this case, the water contained in the insulating film formed on the surface of each of the semiconductor nanocrystals can be set to substantially 0. Further, a barrier layer or high resistance layer between the semiconductor layer and the electrically conductive substrate can be reduced, and thus, the electron emission efficiency and reliability are improved. [0041] In the method of manufacturing this electron source, after the insulating films have been formed on the surfaces of the semiconductor nanocrystals, it is preferable that a heat treatment be carried out in accordance with a rapid heating technique at a temperature of 600°C in atmosphere containing oxide species or nitride species. In this case, a defect or strain and the like, which adversely affect electrical characteristics of the electron source can be alleviated, and insulating films with high dielectric strength and extended service life can be formed. Further, a barrier layer or high resistance layer between the semiconductor layer and the electrically conductive substrate can be reduced, and thus, the electron emission efficiency and reliability are improved. [0042] In this electron source manufacturing method, after the semiconductor nanocrystals have been formed, it is preferable that annealing processing be carried out in a vacuum or inert gas. In this case, a defect caused by impurities such as hydrogen or fluorine contained in a drift layer can be reduced as compared with a case of oxidizing a porous semiconductor layer while water or the like is adsorbed on the porous semiconductor layer immediately after anodic oxidization processing. In this manner, a fine oxide film can be formed, and there can be obtained an electron source with its small change of electron emission efficiency with an elapse of time, high dielectric strength, and high reliability. Further, a barrier layer or high resistance layer between the semiconductor layer and the electrically conductive substrate can be reduced, and thus, the electron emission efficiency and reliability are improved.

[0043] In this electron source manufacturing method, after the semiconductor layer has been formed on the electrically conductive substrate, it is preferable that annealing processing be carried out in a vacuum or inert gas. In this case, a compound layer or alloy layer consisting of a semiconductor and a metal can be interposed on a critical surface between the semiconductor layer and the electrically conductive substrate. Alternatively, the semiconductor layer can be almost crystallized on a critical surface between the semiconductor layer and the electrically conductive substrate. In this manner, a barrier layer or high resistance layer between the semiconductor layer and the electrically conductive substrate can be reduced, and thus, the electron emission efficiency and reliability can be improved.

**[0044]** In this electron source manufacturing method, after the insulating films have been formed on the surfaces of the semiconductor nanocrystals, there may be

carried out one or plural times at least two steps of (a) the above step of carrying out the annealing processing at the temperature of  $700^{\circ}\text{C}$  or less in a vacuum, inert gas, foaming gas, or nitride gas; (b) the above step of carrying out the heat treatment in accordance with the rapid heating technique at the temperature of  $600^{\circ}\text{C}$  or more in atmosphere containing oxide species or nitride species; and (c) the above step of carrying out the annealing processing in accordance with the rapid heating technique at the temperature of  $600^{\circ}\text{C}$  or more in the inert gas atmosphere, respectively (for example, (a) $\rightarrow$  (b), (a) $\rightarrow$ (c), (a) $\rightarrow$ (b) $\rightarrow$ (b), (a) $\rightarrow$ (c), (a) $\rightarrow$ (b) $\rightarrow$ (c), (a) $\rightarrow$ (c) $\rightarrow$ (b) or the like).

[0045] In this electron source manufacturing method, it is preferable to carry out the annealing processing in hydrogen, hydrogen radical emission processing or hydrogen radical emission annealing processing at least at one period after forming the semiconductor layers, after forming the semiconductor nanocrystals, and after forming the insulating films on the surfaces of the semiconductor nanocrystals. In this case, hydrogen radicals are emitted to the top surface on one surface side of the electrically conductive substrate, and thus, a defect existing in the drift layer can be made passive or reduced, and the electron emission characteristics and reliability of the electron source can be improved. Further, the barrier or high resistance layer between the semiconductor layer and the electrically conductive substrate can be reduced, and thus, the electron emission efficiency and reliability are improved.

# BRIEF DESCRIPTION OF THE DRAWINGS

**[0046]** The present invention will be fully understood by the following detailed description and accompanying drawings. In the accompanying drawings, common constituent elements are designated by like reference numerals.

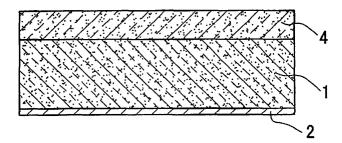

Fig. 1 is a schematic cross section showing essential portions of an electron source according to Embodiment 1 of the present invention.

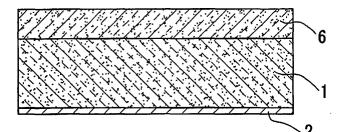

Fig. 2 is a view showing an operation of the electron source shown in Fig. 1.

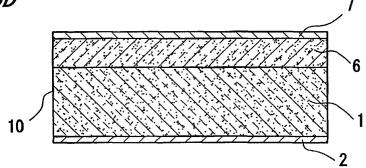

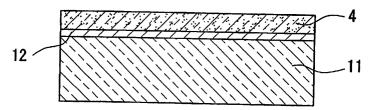

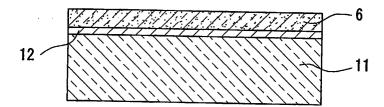

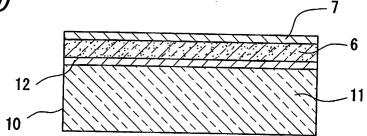

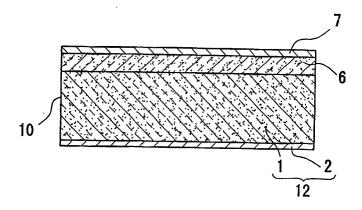

Fig. 3A to Fig. 3D are schematic cross sections each showing the electron source shown in Fig. 1 or an intermediate body in the middle of the manufacture, and show a method of manufacturing the electron source.

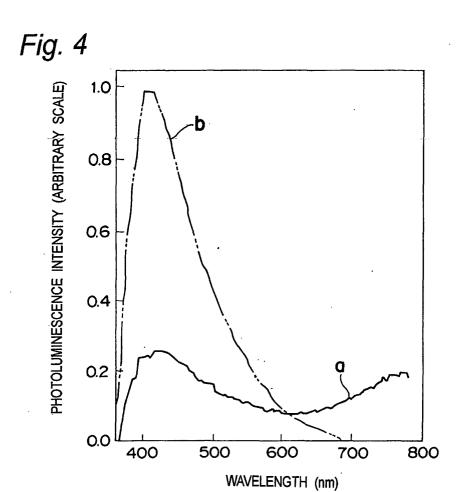

Fig. 4 is a light emission spectrum using the photoluminescence intensity of the electron source shown in Fig. 1 and Comparative Examples, and shows characteristics of the photoluminescence measurement relevant to the wavelength.

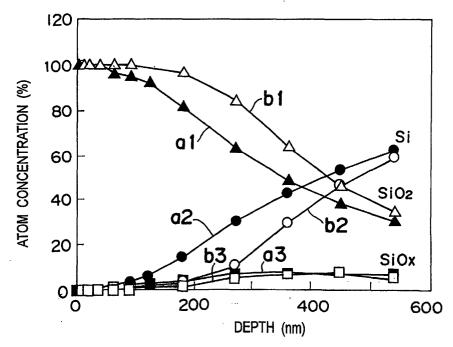

Fig. 5 is a graph showing a direction in the depth direction of constituent elements using the X-ray photo-electronic spectroscopy of the electron source shown in Fig. 1 and Comparative Examples,

and shows characteristics of the atom concentration relevant to the depth.

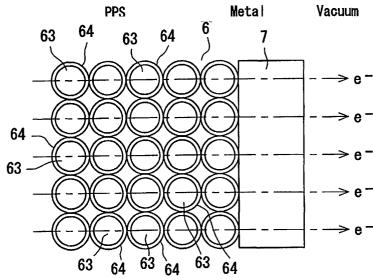

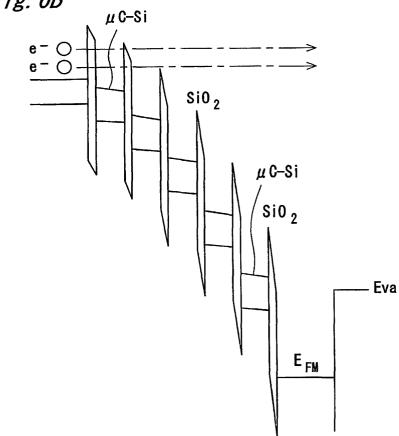

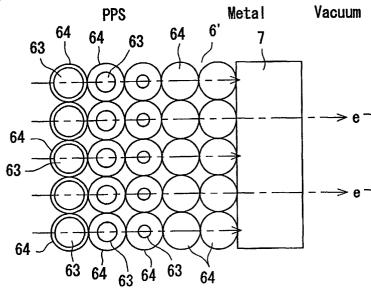

Fig. 6A and Fig. 6B are views each showing an electron emission principle of the electron source shown in Fig. 1.

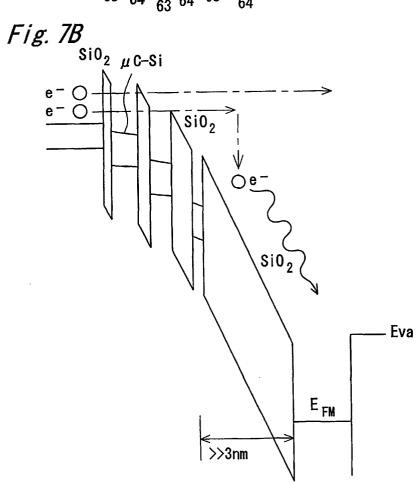

Fig. 7A and Fig. 7B are views each showing an electron emission principle of an electron source according to Comparative Examples.

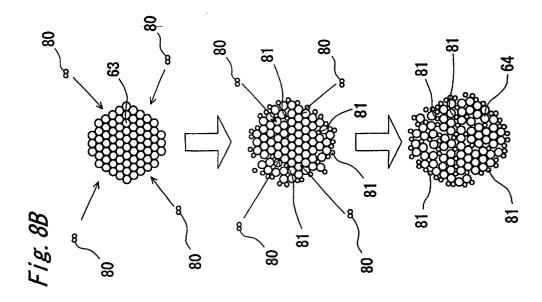

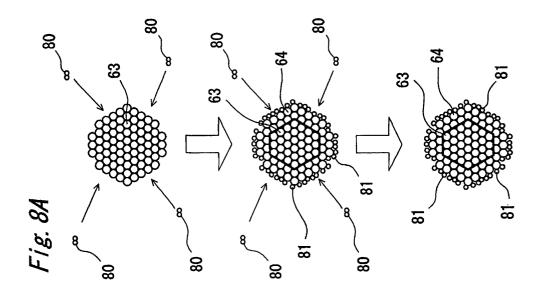

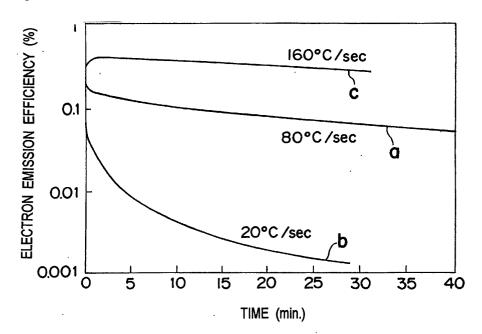

Fig. 8A and Fig. 8B are views each showing an oxidization process in the electron source shown in Fig. 1 and that according to Comparative Examples. Fig. 9 is a graph showing a change with an elapse of time, of electron emission efficiency in the electron source shown in Fig. 1 and that according to Comparative Examples.

Fig. 10 is a view showing electron emission characteristics of the electron source shown in Fig. 1 and that according to Comparative Example.

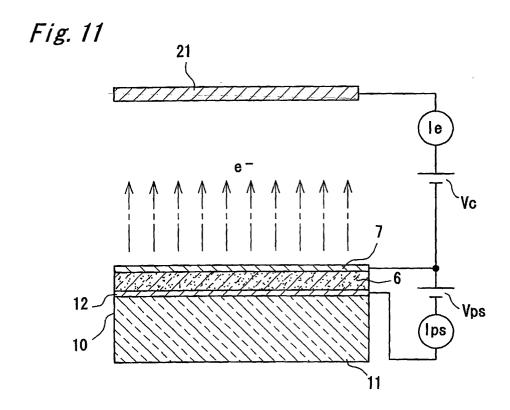

Fig. 11 is a view showing an operation of an electron source according to Embodiment 2 of the present invention.

Fig. 12A to Fig. 12D are schematic sectional views each showing an electron source shown in Fig. 11 or an intermediate body in the middle of the manufacture, and show a method of manufacturing the electron source.

Fig. 13 is a schematic cross section showing an electron source according to Embodiment 3 of the present invention.

Fig. 14 is a view showing an operation of an electron source shown in Fig. 13.

Fig. 15A to Fig. 15D are schematic cross sections each showing the electron source shown in Fig. 13 or an intermediate body in the middle of its manufacture, and show a method of manufacturing the electron source.

Fig. 16 is a view showing a technique of forming insulation thin films in the electron source according to Embodiment 3 of the present invention, and shows a change with an elapse of time, of a heat treatment temperature.

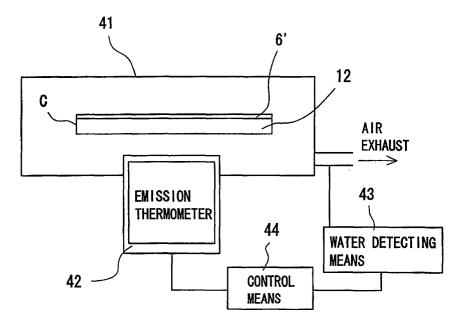

Fig. 17 is a schematic configuration of a heat treatment device employed for forming the insulation thin film shown in Fig. 13.

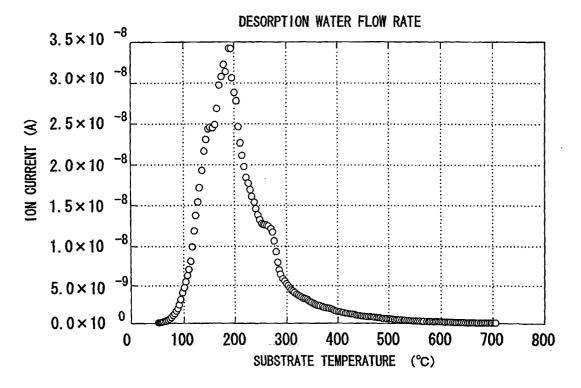

Fig. 18 is a graph showing a measurement result of temperature rise desorbing gas mass spectroscopic analysis, and shows change characteristics of an ionic current relevant to a heating temperature.

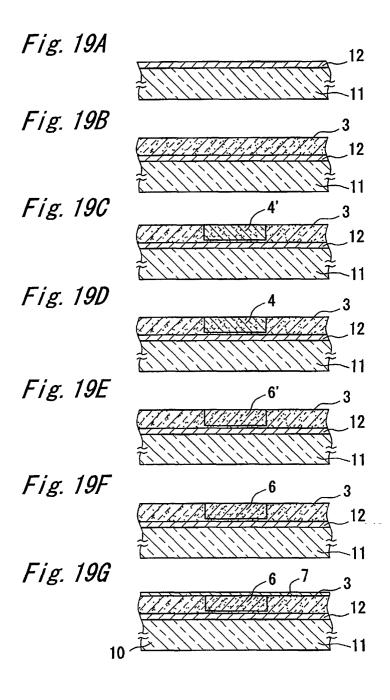

Fig. 19A to Fig. 19G are schematic sectional views each showing an electron source according to Embodiment 4 of the present invention or an intermediate body in the middle of the manufacture, and show a method of manufacturing the electron source.

Fig. 20 is a view showing a termination aspect of a top surface of a porous polycrystalline silicon layer after the annealing processing.

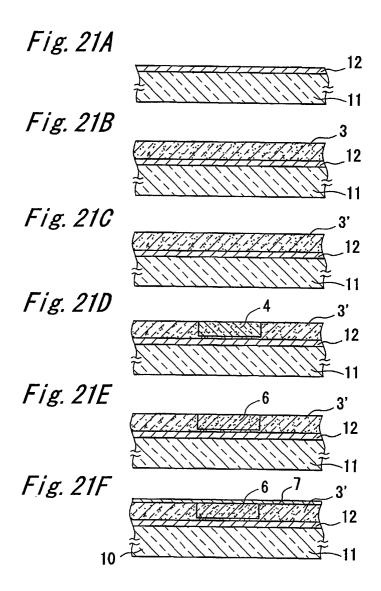

Fig. 21A to Fig. 21F are schematic cross sections

15

20

each showing an electron source according to Embodiment 5 of the present invention or an intermediate body in the middle of its manufacture, and show a method of manufacturing the electron source.

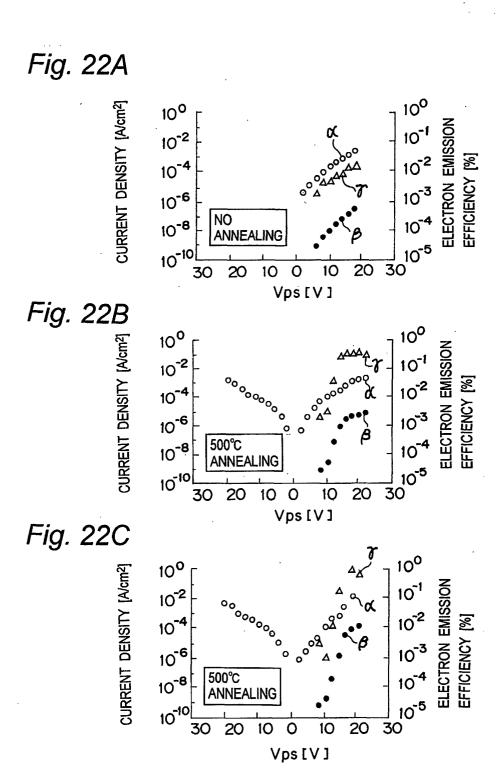

Fig. 22A to Fig. 22C are graphs depicting change characteristics of a current density of an electron source relevant to the direct current voltage Vps when the annealing processing is not carried out, when the annealing processing is carried out at 500°C, and when the annealing processing is carried out at 550°C, respectively.

Fig. 23 is a schematic cross section showing an electron source according to Embodiment 6 of the present invention.

Fig. 24 is a view showing an operation of the electron source shown in Fig. 23.

Fig. 25A to Fig. 25D are schematic cross sections each showing the electron source according to Embodiment 6 of the present invention or an intermediate body in the manufacture, and show a method of manufacturing the electron source.

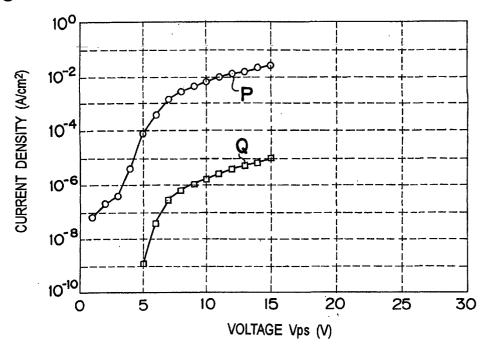

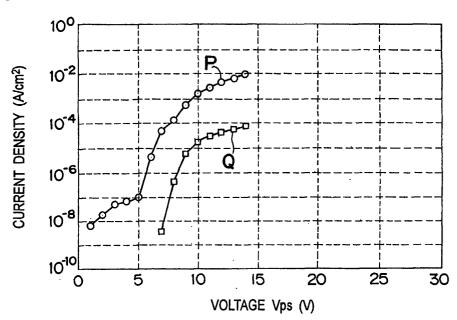

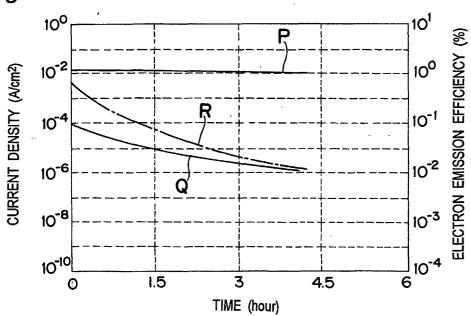

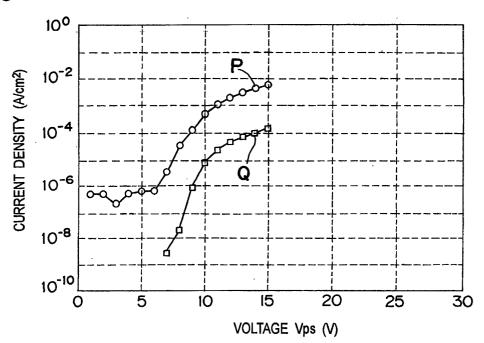

Fig. 26 is a graph depicting change characteristics of the current density relevant to the direct current voltage Vps in the electron source shown in Fig. 23. Fig. 27 is a graph depicting change characteristics of the current density relevant to a time in the electron source shown in Fig. 23.

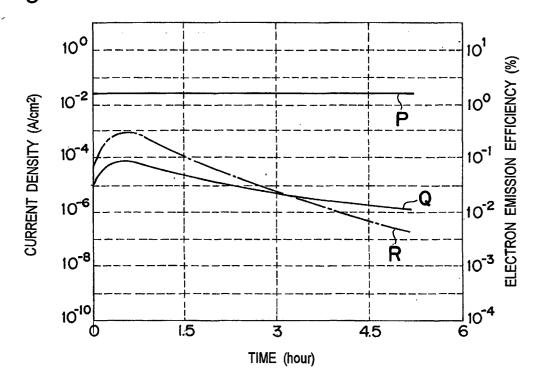

Fig. 28 is a graph depicting change characteristics of the current density relevant to the direct current voltage Vps in an electron source according Comparative Example.

Fig. 29 is a graph depicting change characteristics of the current density relevant to a time in an electron source according to Comparative Example identical to the case of Fig. 28.

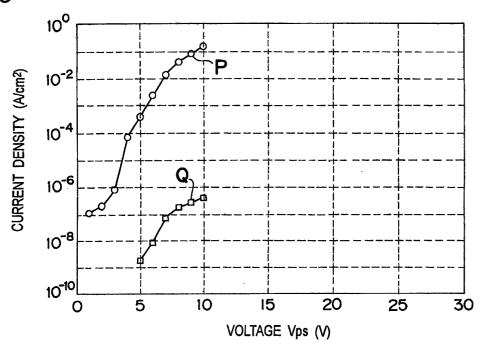

Fig. 30 is a graph depicting change characteristics of the current density relevant to the direct current voltage Vps in an electron source according another Comparative Example.

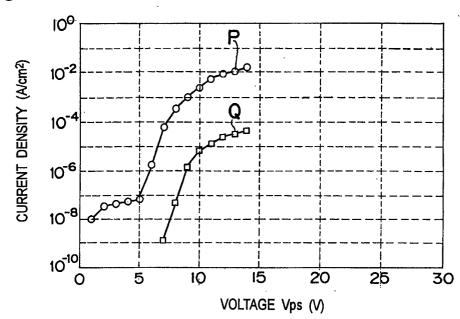

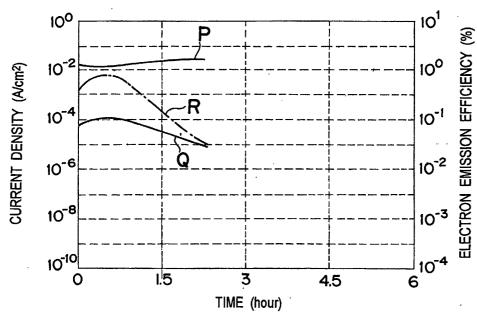

Fig. 31 is a graph depicting change characteristics of the current density relevant to a time in an electron source according to Comparative Example identical to the case of Fig. 30.

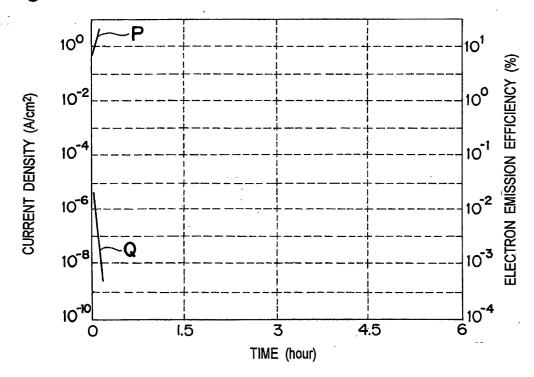

Fig. 32 is a graph depicting change characteristics of the current density relevant to the direct current voltage Vps in an electron source according to Embodiment 7 of the present invention.

Fig. 33 is a graph depicting change characteristics of the current density relevant to a time in the electron source according to Embodiment 7 of the present invention.

Fig. 34 is a graph depicting change characteristics of the current density relevant to the direct current voltage Vps in an electron source according to Embodiment 10 of the present invention.

Fig. 35 is a graph depicting change characteristics of the current density relevant to a time in the elec-

tron source according to Embodiment 10 of the present invention.

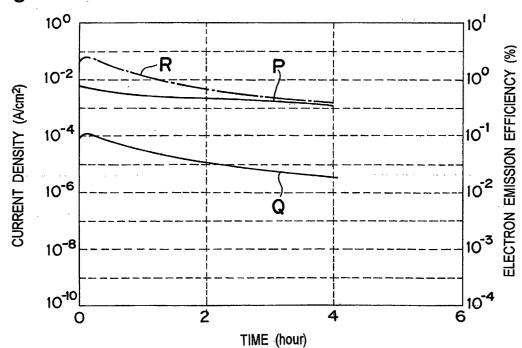

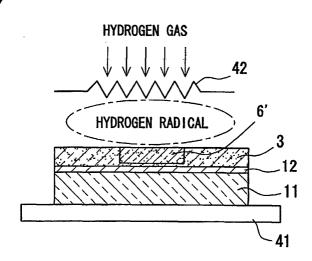

Fig. 36A to Fig. 36F are schematic cross sections each showing an electron source according to Embodiment 13 of the present invention or an intermediate body in the middle of the manufacture, and show a method of manufacturing the electron source.

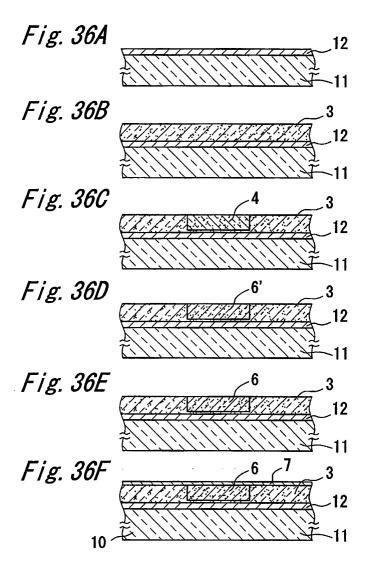

Fig. 37 is a view showing a processing technique in a hydrogen radical emission step in a method of manufacturing the electron source according to Embodiment 13 of the present invention.

Fig. 38 is a view showing an operation of a conventional electron source.

Fig. 39 is a schematic cross section showing the conventional electron source.

Fig. 40 is a view showing an operation of another conventional electron source.

Fig. 41 is a graph depicting a change with an elapse of time, of a heat treatment temperature in a rapid heating technique.

Fig. 42 is a view showing a termination aspect of a top surface of a porous polycrystalline silicon layer after the anodic oxidization processing.

Fig. 43 is a view showing a termination aspect of the top surface of the porous polycrystalline silicon layer after the rapid heating processing.

# DESCRIPTIONS OF THE PREFERRED EMBODIMENTS

**[0047]** The present application is based on Japanese Patent Application No. 2001-125156, Japanese Patent Application No. 2001-125157, Japanese Patent Application No. 2001-159625, and Japanese Patent Application No. 2001-329908, the contents of which are fully incorporated therein.

[0048] Hereinafter some embodiments of the present invention will be specifically described. Elements common to the embodiments, that is, elements whose configuration and function are substantially identical to each other, are designated by common reference numerals. A duplicate description thereof is principally omitted here.

### (Embodiment 1)

[0049] Hereinafter, Embodiment 1 of the present invention will be described. In Embodiment 1, as an electrically conductive substrate (lower electrode), there is employed a single-crystalline n-type silicon substrate whose resistivity is comparatively close to a resistivity of a conductor (for example, a (100) substrate whose resistivity is 0.01  $\Omega$  cm to 0.02  $\Omega$  cm).

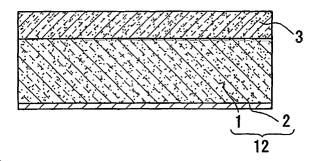

**[0050]** As shown in Fig. 2, in an electron source 10 (field emission-type electron source) according to Embodiment 1, a drift layer 6 (strong field drift layer) consisting of an oxidized porous polycrystalline silicon layer

is formed on a main surface side of an n-type silicon substrate 1 that is an electrically conductive substrate. A surface electrode 7 is formed on the drift layer 6. An ohmic electrode 2 is formed on the back surface of the n-type silicon substrate 1. In Embodiment 1, the n-type silicon substrate 1 configures an electrically conductive substrate.

**[0051]** A material with its small work function is employed for a material for the surface electrode 7. The thickness of the surface electrode 7 is set to 10 nm. However, the thickness thereof is not limited to this value, and may be thickness such that an electron passing through the drift layer 6 can be tunneled. The thickness of the surface electrode 7 may be set to about 3 nm to 15 nm

[0052] The surface electrode 7 is composed of a first thin film layer consisting of a metal film formed on the drift layer 6 and a second thin film layer consisting of a metal film deposited on the first thin film layer. As a material for the first thin film later on the drift layer 6, for example, there may be employed a material having intimacy with the drift layer 6, the material being capable of preventing diffusion between the second thin film layer and the drift layer 6 such as chrome, nickel, platinum, titanium, iridium. As a material for the second thin film layer, there may be employed gold with its low resistance and high stability with an elapse of time. In Embodiment 1, chrome (Cr) is employed as a material for the first thin film layer. The film thickness of the first thin film layer is set to 2 nm. As a material for the second thin film layer, gold (Au) is employed. The film thickness of the second thin film layer is set to 8 nm. In Embodiment 1, although the surface electrode 7 is composed of a two-layered metal film, this electrode may be composed of one or three or more layered metal film instead of this film.

[0053] In the electron source 10, the surface electrode 7 is disposed in a vacuum, and a collector electrode 21 is disposed in opposite to the surface electrode 7. Then, a direct current voltage Vps is applied so that the surface electrode 7 becomes positive in polarity relevant to the n-type silicon substrate 1 (ohmic electrode 2), and a direct current voltage Vvc is applied so that the collector electrode 21 becomes positive in polarity relevant to the surface electrode 7. In this manner, electrons injected from the n-type silicon substrate 1 drift in the drift layer 6, and are emitted via the surface electrode 7 (the single dotted chain line in Fig. 2 indicates the flow of electrons "e-" emitted through the surface electrode 7). As a ratio of the emission current (emission electron current) le flowing between the collector electrode 21 and the surface electrode 7 to the diode current lps flowing between the surface electrode 7 and the n-type silicon substrate 1 (ohmic electrode 2) is greater, the electron emission efficiency increases.

**[0054]** As shown in Fig. 1, the drift layer 6 according to Embodiment 1 is composed of: at least, columnar polycrystalline silicon grains 51; thin silicon oxide films

52 formed on the surfaces of the grains 51; a number of silicon nanocrystals 63 of nano-meter order interposed between the grains 51; and a number of silicon oxide films 64 formed on the surfaces of the silicon nanocrystals 63, each of which is an insulating film with film thickness that is smaller than the crystalline particle size of the silicon nanocrystal 63. In short, the surface of each grain 51 is made porous in the drift layer 6, and the crystalline state is maintained at the center portion of each grain. It is desirable that the thickness of the silicon oxide film 64 formed on the surface of the silicon nanocrystal 63 is set at the film thickness to an extent such that an electron tunneling phenomenon occurs (degree of mean free path of electrons: the degree of mean free path of electrons in SiO<sub>2</sub> is about 3 nm), for example, about 1 nm to 3 nm.

[0055] In the electron source 10 according to Embodiment 1, it is believed that electron emission occurs in the following model. That is, the surface electrode 7 is disposed in a vacuum. Then, between the surface electrode 7 and the n-type silicon substrate 1 (ohmic electrode 2), with the surface electrode 7 being positive in polarity, the direct current voltage Vc is applied. In addition, at the same time, between the collector electrode 21 and the surface electrode 7, with the collector electrode 21 being positive in polarity, the direct current voltage Vps is applied. When the direct current voltage Vps reaches a predetermined value (critical value), electrons "e-" are injected due to thermal excitation from the n-type silicon substrate 1 serving as an electrically conductive substrate to the drift layer 6. On the other hand, a majority of the electron field applied to the drift layer 6 is applied to the silicon oxide films 64. Thus, the injected electrons "e-" are accelerated by the strong electric field applied to the silicon oxide film 64. Then, the electrons drift in a region between the grains 51 in the drift layer 6 toward the surface in an orientation indicated by the arrow A in Fig. 1, tunnel the surface electrode 7, and are emitted into the vacuum. In this manner, in the drift layer 6, the electrons injected from the n-type silicon substrate 1 are accelerated and drift in the strong electric field applied to the silicon oxide film 64 without being diffusing in the silicon nanocrystal 63, and are emitted via the surface electrode 7 (ballistic type electron emission phenomenon). A heat generated in the drift layer 6 is emitted via the grains 51. Thus, a popping phenomenon does not occur during electron emission, and electrons can be constantly emitted. The electrons arrived at the surface of the drift layer 6 are believed as hot electrons, easily tunnel the surface electrode 7, and are emitted in the vacuum.

**[0056]** Hereinafter, a method of manufacturing the electron source 10 according to Embodiment 1 will be described with reference to Fig. 3A to Fig. 3D.

**[0057]** First, after an ohmic electrode 2 has been formed on the back surface of an n-type silicon substrate 1, a non-doped polycrystalline silicon layer 3 is formed as a semiconductor layer on a main surface of the n-

type silicon substrate 1, and a structure shown in Fig. 3A is obtained. As a method of film forming the polycrystalline silicon layer 3, for example, there may be employed a CVD technique (such as LPCVD technique, plasma CVD technique, or catalytic CVD technique, for example), a sputtering technique, or a CGS (Continuous Grain Silicon) technique and the like.

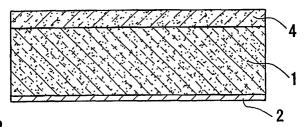

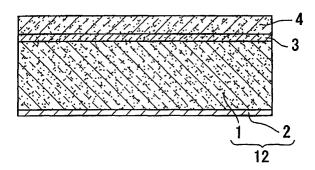

[0058] After the non-doped polycrystalline silicon layer 3 has been formed, the polycrystalline silicon layer 3 is made porous in accordance with the anodic oxidization processing step, whereby a porous polycrystalline silicon layer 4 that is a porous semiconductor layer is formed, and a structure shown in Fig. 3B is obtained. In the anodic oxidization processing step, there is employed an anodic oxidization processing vessel that contains an electrolytic solution consisting of a mixture solution obtained by mixing 55 wt.% of hydrogen fluoride water solution and ethanol at substantially 1:1. Then, with a platinum electrode (not shown) being negative in polarity and the n-type silicon substrate 1 (ohmic electrode 2) being positive in polarity, while light emission is carried out for the polycrystalline silicon layer 3, anodic oxidization is carried out at a constant current. In this manner, the porous polycrystalline silicon layer 4 is formed. The thus formed porous polycrystalline silicon layer 4 contains polycrystalline silicon grains and silicon nanocrystals. In Embodiment 1, although all of the polycrystalline silicon layer 3 is made porous, the layer may be partially made porous.

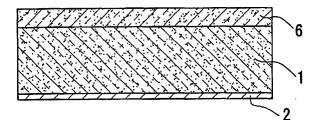

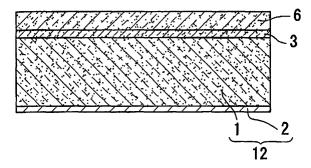

[0059] After the anodic oxidization processing step has terminated, the porous polycrystalline silicon layer 4 is oxidized in accordance with the oxidizing step, whereby the drift layer 6 consisting of the oxidized porous polycrystalline silicon layer is formed, and a structure shown in Fig. 3C is obtained. In the oxidizing step, the porous polycrystalline silicon layer 4 is oxidized in a rapid heating technique, whereby a drift layer 6 is formed, the drift layer containing the grains 51, silicon nanocrystals 63, and silicon oxide films 52 and 64. A lamp annealing device is employed in the oxidizing step using the rapid heating technique. In this case, while O<sub>2</sub> gas atmosphere is produced in a furnace, the substrate temperature is risen from the room temperature to a predetermined oxidization temperature (for example, 900°C) at a predetermined temperature rise velocity (for example, 80°C / sec). Then, the substrate temperature is maintained by a predetermined oxidization time (for example, 1 hour), and rapid thermal oxidization (RTO) is carried out. Then, the substrate temperature is lowered to the room temperature. In Embodiment 1, although the temperature rise velocity is set to 80°C / sec, the temperature rise velocity may be set to 80°C / sec or more, and it is preferable that the velocity be set to 150°C / sec or more. A reason for thus setting the temperature rise velocity will be described later. In Embodiment 1, the oxidization step is provided as the insulating film forming step of forming the silicon oxide films 64, which are insulating films, on the surfaces of the silicon

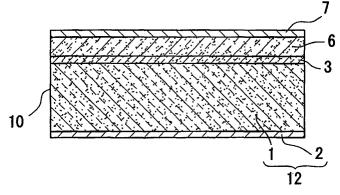

nanocrystals 63 that are semiconductor nanocrystals. [0060] After the drift layer 6 has been formed, a first thin film layer consisting of a metal film (chrome film in Embodiment 1) is deposited on the drift layer 6 in accordance with an electron beam vapor deposition technique. Further, a second thin film layer consisting of a metal film (gold film in Embodiment 1) is deposited on the first thin film layer in accordance with the electron beam vapor deposition technique. In this manner, a surface electrode 7 consisting of the first thin film layer and the second thin film layer is formed, and an electron source 10 with its structure shown in Fig. 3D is obtained. In Embodiment 1, although the surface electrode 7 is formed in accordance with the electron beam vapor deposition technique, a method of forming the surface electrode 7 is not limited to the electron beam vapor deposition technique, and a sputtering technique may be employed, for example.

[0061] In the meantime, the present inventors have

obtained a finding that, as a result of search, a condition for the oxidizing step using the rapid heating technique, in particular, a temperature rise velocity affects a deviation between lots of characteristics such as electron emission efficiency, dielectric strength, or service life. [0062] Then, the present inventors carried out analytical evaluation of the drift layer 6 of the electron source 10 by setting the temperature rise velocity in the rapid heating technique to 80°C / sec. Specifically, there were carried out: a structural evaluation in the vicinity of the surface of the drift layer 6 in accordance with a photoluminescence technique (PL technique); observation and element analysis of a structure of a drift layer surface vicinity portion using a sectional TEM (Transmission type Emission Microscope); and dimensional measurement of the existing quantity of the drift layer constituent element relevant to the depth direction by using X-ray photo-electron spectroscopy (XPS technique). Further, similar analytical evaluation was carried out for an electron source (drift layer) according to Comparative Example as well. The electron source according Comparative Example was manufactured by setting the temperature rise velocity in the rapid heating technique to 20°C / sec which is lower than 80°C / sec. As a result, in Comparative Example in which the temperature velocity was set to 20°C / sec, in the drift layer, an SiO<sub>2</sub> film was formed from the surface (critical surface with surface electrode 7) to a depth of about 100 nm, and the presence of silicon nanocrystal was not verified. In contrast, in the drift layer in the electron source 10 in which the temperature rise velocity was set to 80°C / sec, which is comparatively high, it was found that the silicon nanocrystals 63 exist in a region to the depth of about 100 nm from the surface as well.

**[0063]** Hereinafter, a result f each analytical evaluation will be described. First, a result obtained by observation and element analysis caused to a sectional TEM for a structure in the vicinity of a surface, respectively, will be described with respect to the drift layer 6 of the

electron source 10 according to Embodiment 1 and the drift layer according to Comparative Example. By evaluation caused by the sectional TEM, in the drift layer 6 of the electron source 10, the columnar grains of the polycrystalline silicon and the silicon nanocrystals of nano-meter order were verified. In contrast, in the drift layer according to Comparative Example, SiO<sub>2</sub> films were formed over the whole region from the surface to a depth of about 100 mm, and the columnar grains of the polycrystalline silicon were verified only in a region deeper than 100 nm.

[0064] Now, a result of structural evaluation in the vicinity of the surface of the drift layer in accordance with the PL technique will be described with reference to Fig. 4. Fig. 4 shows light emission spectra measured by emitting light of 325 nm in wavelength from a He-Cd laser. "a" in Fig. 4 indicates the light emission spectra of the drift layer 6 according to Embodiment 1, and "b" indicates the light emission spectra of the drift layer according to Comparative Example. An invasion length of the light emitted from the He-Cd laser into the drift layer 6 is within the range of 100 nm in the depth direction from the surface of the drift layer 6. Therefore, the light emission spectra of each of "a" and "b" in Fig. 4 indicates light emission spectra from a shallow region in the vicinity of the surface. In general, the light emission from the silicon oxide films is referred to as an F band, and is known to have a peak in the proximity of 430 nm to 540 nm. In addition, the light emission from the silicon nanocrystals is referred to as an S band, and is known to have a peak in the vicinity of 650 nm to 800 nm. As is evident from Fig. 4, in the drift layer 6 according to Embodiment 1, the peak believed to be light emission from the silicon nanocrystals 63 and the peak believed to be light emission from the silicon oxide films are observed. In contrast, in the drift layer according to Comparative Example, only the peak believed to be light emission from the silicon oxide films is observed. That is, in the region from the surface of the drift layer 6 according to Comparative Example to the depth of about 100 nm, silicon nanocrystals hardly exist, a majority or all of which are believed to be silicon oxide films. This result coincides with the analysis result caused by the sectional TEM.

**[0065]** Now, a result of distribution measurement in the depth direction concerning an existence quantity of drift layer constituent elements in accordance with the XPS technique will be described with reference to Fig. 5. The horizontal axis of Fig. 5 indicates the depth from the surface of the drift layer 6. The vertical axis of Fig. 5 indicates the atom concentration. "a1", "a2", and "a3" in Fig. 5 indicate the measurement result relevant to the drift layer 6 according to Embodiment 1. In addition, "b1", "b2", and "b3" indicate the measurement result relevant to the drift layer according to Comparative Example. Here, "a1" and "b1" indicate the distribution in the depth direction of SiO<sub>2</sub>, "a2" and "b2" indicate the distribution in the depth direction of Si, and "a3" and "b3"

indicate the distribution in the depth direction SiOx. As is evident from Fig. 5, in the drift layer 6 according to Embodiment 1, Si and SiO<sub>2</sub> are observed in the region in which the depth from the surface is shallower than 100 nm. In contrast, in the drift layer according to Comparative Example, Si is not observed in the region which is shallower than 100 nm from the surface, and only SiO<sub>2</sub> is observed. This result coincides with the analysis result caused by the sectional TEM.

[0066] From the above analysis result, as shown in Fig. 6A and Fig. 6B, in the drift layer 6 according to Embodiment 1, it is believed that the silicon nanocrystals 63 having the silicon oxide films 64 formed on the surface thereof are contained in the vicinity of the surface of the drift layer 6 as well. Then, it is believed that the electrons "e-" injected into the drift layer 6 are accelerated by the strong electric field applied to the silicon oxide films 64, drift in the orientation (right side) indicated by the arrow in Fig. 6A with hardly colliding with the silicon nanocrystals 63, reach the surface of the drift layer 6, tunnel the surface electrode 7, and are emitted into the vacuum (the single dotted chain light in Fig. 6A indicates the flow of electrons "e-"). "PPS" described at the upper part of Fig. 6A indicates the drift layer 6, "Metal" indicates the surface electrode 7, and "Vacuum" indicates a vacuum. In addition, Fig. 6B is an energy band chart illustrating a principle of electron emission. "SiO<sub>2</sub>" in Fig. 6B indicates silicon oxide films 64, "uc-Si" indicates silicon nanocrystals 63 of nano-meter order, "EFM" indicates the Fermi level of the surface electrode 7, and "Eva" indicates the vacuum level.

[0067] On the other hand, as shown in Fig. 7, in the drift layer according to Comparative Example (hereinafter, referred to as "drift layer 6'"), the film thickness of each of the silicon oxide films 64 increases as the film is close to the surface of the drift layer 6', and the silicon nanocrystals 63 are destroyed. In the vicinity of the surface, any silicon nanocrystals 63 do not exist. Thus, a part of the electrons "e-" injected in the drift layer 6' are diffused or absorbed by the silicon oxide films 64 each of which has a film thickness (degree of mean free pass of electrons) larger than the film thickness to an extent such that an electron tunneling phenomenon occurs. Thus, it is believed that the electron emission efficiency is lowered, and the dielectric strength and service life are lowered.

[0068] In the drift layer 6 according to Embodiment 1, the silicon nanocrystals 63 exist in the vicinity of the surface as well. In contrast, in the drift layer 6' according to Comparative Example, the following model is believed to be responsible for destruction of the silicon nanocrystals 63 in the vicinity of the surface. That is, in Embodiment 1, in the oxidizing step after the anodic oxidization processing step, as shown in Fig. 8A, an oxygen molecule 80 reaches the periphery of the silicon nanocrystal 63. At this time, a temperature rise velocity is comparatively high (80°C / sec), and thus, the silicon oxide films 64 are formed within a short time on the surfaces of the

silicon nanocrystals 63 formed in accordance with anodic oxidization. Thus, diffusion of an oxygen atom 81 into the center portion of the silicon nanocrystal 63 is inhibited. In this manner, it is believed that the silicon oxide film 64 having film thickness (degree of mean free path of electrons) in which an electron tunneling phenomenon occurs is formed only on the surface of the silicon nanocrystal 63. On the other hand, in Comparative Example as well, in the oxidizing step after anodic oxidization processing step, as shown in Fig. 8B, the oxygen molecule 80 reaches the periphery of the silicon nanocrystal 63. However, the temperature rise velocity is comparatively low (20°C / sec), and thus, the oxygen atom 81 diffuses to the center portion of the silicon nanocrystal 63 formed in accordance with anodic oxidization, and the entirety of the silicon nanocrystal 63 is oxidized. This is because the silicon nanocrystal 63 is destroyed.

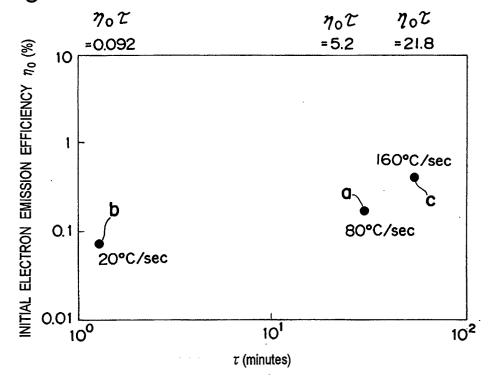

[0069] Fig. 9 shows a change with en elapse of time, of a respective electron emission efficiency when the temperature rise velocity is set to 80°C / sec, 160°C / sec, and 20°C / sec. The vertical axis of Fig. 9 indicates electron emission efficiency, and the horizontal axis indicates an elapsed time. "a" in Fig. 9 indicates a case in which the temperature rise velocity is set to 80°C / sec, "b" indicates a case in which the velocity is set to20°C / sec, and "c" indicates a case in which the velocity is set to 160°C/sec. As is evident from Fig. 9, in Embodiment 1, the electron emission efficiency is high and a change with an elapse of time of the electron emission efficiency is reduced as compared with Comparative Example. In this manner, the service life is extended. In addition the temperature rise velocity is increased from 80°C / sec to 160°C / sec, whereby the electron emission efficiency is increased more remarkably.

**[0070]** A change with an elapse of time, of the electron emission efficiency shown in Fig. 9 can be fitted by a function (hereinafter, referred to as "damping function") that damps relevant to an elapsed time in an exponential function manner. That is, an initial value of the electron emission efficiency (hereinafter, referred to as "initial electron emission efficiency") is defined as  $\eta$ 0, a time constant is defined as  $\tau$ , a proportional coefficient (linear filter) is defined as  $\gamma$ , and an elapsed time is defined as  $\tau$ , the electron emission efficiency in an arbitrarily elapsed time "t" can be approximated in the following formula 1. As a value of time constant  $\tau$  increases, the service life of the electron source increases.

$η = η0 \cdot exp((-t / τ) \cdot γ)$  Formula 1

[0071] Fig. 10 shows a relationship between the initial electron emission efficiency  $\eta 0$  and the time constant  $\tau$  obtained by being fitted by the damping function. The vertical axis of Fig. 10 indicates the initial electron emission efficiency  $\eta 0$ , and the horizontal axis indicates the time constant  $\tau$ . "a" in Fig. 10 indicates a case in which the temperature rise velocity is set to  $80^{\circ}\text{C}$  / sec, "b"

indicates a case in which the temperature rise velocity is set to 20°C / sec, and "c" indicates a case in which the temperature rise velocity is set to 160°C / sec. According to Fig. 10, as the temperature rise velocity increases, it is found that the initial electron emission efficiency  $\eta 0$  and the time constant  $\tau$  increase. Namely, as the temperature rise velocity increases, the electron emission efficiency can be improved, and the service life can be extended. Here, assuming that the characteristic evaluation of the electron source is carried out by a multiple  $\eta 0.\tau$  between the initial electron emission efficiency  $\eta 0$  and the time constant  $\tau$ , it is believed that the characteristics of the electron source is more excellent as the value of  $\eta 0.\tau$  increases. The value of  $\eta 0.\tau$  is 0.092 in "b", 5.2 in "a", and 21.8 in "c". The temperature rise velocity is increased from 20°C / sec to 80°C / sec, it is found that the value of  $\eta 0.\tau$  is larger by 50 times as compared with a case of 20°C / sec. Therefore, the temperature rise velocity is set to 80°C / sec or more, whereby the electron emission efficiency can be improved, and the service life can be extended as compared with a case of 20°C / sec. Further, the temperature rise velocity is set to 150°C or more, whereby the electron emission efficiency can be improved more remarkably, and the service life can be extended more significantly. Although the temperature rise velocity is restricted by performance of a manufacturing apparatus (for example, lamp annealing device) employed in the rapid heating technique, it is currently known that the temperature rise velocity can be increased to about 400°C / sec.

[0072] With the method of manufacturing the electron source 10 according to Embodiment 1, the thickness of the silicon oxide films 64 that are insulating films in the drift layer 6 can be set at the film thickness to an extent such that an electron tunneling phenomenon occurs. Thus, electron diffusion in the silicon oxide films 64 can be reduced, and a deviation of thickness of the silicon oxide films 64 in the drift layer 6 can be reduced. In this manner, the design of the dielectric strength and service life is made easy, the dielectric strength can be improved, and the service life can be extended. Further, the electron emission efficiency can be improved.

(Embodiment 2)

**[0073]** Hereinafter, Embodiment 2 of the present invention will be described. In Embodiment 2, as an electrically conductive substrate, there is employed a substrate on which an electrically conductive layer consisting of a metal film (for example, tungsten film) is provided on one surface of an insulating substrate consisting of a glass substrate (for example, quartz glass substrate).

**[0074]** As shown in Fig. 11, in an electron source 10 according to Embodiment 2, a drift layer 6 consisting of an oxide porous polycrystalline silicon layer is formed on an electrically conductive layer 12 on an insulating substrate 11. A surface electrode 7 is formed on the drift

layer 6. A configuration of the surface electrode 7 is similar to that of Embodiment 1.

[0075] In order to emit electrons from the electron source 10, a collector electrode 21 is arranged so as to be opposite to the surface electrode 7, and a vacuum state is established between the surface electrode 7 and the collector electrode 21. Then, a direct current voltage Vps is applied between the surface electrode 7 and the electrically conductive layer 21 so that the surface electrode 7 becomes positive in polarity (high potential) relevant to the collector electrode 21, and a direct current voltage Vc is applied between the collector electrode 21 and the surface electrode 7 so that the collector electrode 21 becomes positive in polarity relevant to the surface electrode 7. When the direct current voltages Vps and Vc are properly set, the electrons injected from the electrically conductive layer 12 drift in the drift layer 6, and are emitted via the surface electrode 7 (the single dotted chain line in Fig. 11 indicates the flow of electrons "e-" emitted through the surface electrode 7). The electrons arrived on the surface of the drift layer 6 are believed to be hot electrons, easily tunnel the surface electrode 7, and are emitted into the vacuum. In the electron source 10 according to Embodiment 2 as well, as in the electrode 10 according to Embodiment 1, as a ratio of the emission current le to the diode current lps (= le / lps) increases, the electron emission efficiency increas-

[0076] The configuration and function of the drift layer 6 is similar to those of Embodiment 1. That is, the drift layer 6 is composed of, at least, grains 51, silicon oxide films 52, a number of silicon nanocrystals 63, and a number of silicon oxide films 64 (refer to Fig. 1). In addition, in the drift layer 6, the surface of each grain is made porous, and a crystalline state is maintained at the center portion of each grain. The thickness of each of the silicon oxide films 64 is set at the film thickness to an extent such that an electron tunneling phenomenon occurs (degree of mean free path of electrons), for example, about 1 nm to 3 nm.

[0077] In the electron source 10 according to Embodiment 2 as well, it is believed that the electron emission occurs in a model similar to the case of the electron source 10 according to Embodiment 1. That is, the direct current voltage Vps is applied between the surface electrode 7 and the electrically conductive later 12 with the surface electrode 7 being positive in polarity, and the direct current voltage Vc is applied between the collector electrode 21 and the surface electrode 7 with the collector electrode 21 being positive in polarity, whereby the electrons "e-" injected from the electrically conductive layer 12 into the drift layer 6 by thermal excitation drift, tunnel the surface electrode 7, and are emitted into the vacuum.

**[0078]** In the case where the electron source 10 according to Embodiment 2 is utilized as an electron source of a display, the lower electrode (electrically conductive substrate) or surface electrode 7 and the like

may be properly patterned.

**[0079]** A method of manufacturing the electron source 10 according to Embodiment 2 will be described with reference to Fig. 12A to Fig. 12D.

[0080] First, on one surface side of an insulating substrate 11, an electrically conductive layer 12 consisting of a metal layer (for example, tungsten film) is formed, and an electrically conductive substrate is fabricated in accordance with a sputtering technique or the like. Then, on a main surface side of the electrically conductive substrate (on the electrically conductive layer 12), a non-doped polycrystalline silicon layer 3 is formed as a semiconductor layer, and a structure shown in Fig. 12A is obtained. As a method of film forming the polycrystalline silicon layer 3, for example, there may be employed a CVD technique (such as LPCVD technique, plasma CVD technique, or catalytic CVD technique, for example), a sputtering technique, or a CGS (Continuous Grain Silicon) technique.

[0081] After the non-doped polycrystalline silicon layer 3 has been formed, the polycrystalline silicon layer 3 is made porous in accordance with the anodic oxidization processing step, whereby a porous polycrystalline silicon layer 4 that is a porous semiconductor layer is formed, and a structure shown in Fig. 12B is obtained. In the anodic oxidization processing step, there is employed an anodic oxidization processing vessel that contains an electrolytic solution consisting of a mixture solution obtained by mixing 55 wt.% of hydrogen fluoride water solution and ethanol at substantially 1:1. Then, with a platinum electrode (not shown) being negative in polarity and the electrically conductive layer 12 being a positive layer, while light emission is carried out for the porous polycrystalline silicon layer 3, anodic oxidization processing is carried out at a constant current. In this manner, a porous polycrystalline silicon layer 4 is formed. The porous polycrystalline silicon layer 4 contains polycrystalline silicon grains and silicon nanocrystals. In Embodiment 2, although entire polycrystalline silicon layer 3 is made porous, the layer may be partially made porous.

[0082] After the anodic oxidization processing step has terminated, the porous polycrystalline silicon layer 4 is oxidized, whereby a drift layer 6 consisting of an oxidized porous polycrystalline silicon layer is formed, and a structure shown in Fig. 12C is obtained. In the oxidizing step, the porous polycrystalline silicon layer 4 is oxidized in accordance with the rapid heating technique, whereby a drift layer 6 containing the grains 51, the silicon nanocrystals 63 and silicon oxide films 52 and 64 is formed. In the oxidizing step using the rapid heating technique, as is the case of Embodiment 1, O<sub>2</sub> gas atmosphere is produced inside of a furnace by employing a lamp annealing device, and the substrate temperature is risen from the room temperature to a predetermined oxidization temperature (for example, 900°C) by a predetermined temperature rise velocity (for example, 80°C / sec). Then, the substrate temperature is main-

tained for a predetermined oxidization time (for example, 1 hour), and rapid thermal oxidization (RTO) is applied. Then, the substrate temperature is lowered to the room temperature. In Embodiment 2, although the temperature rise velocity is set to  $80^{\circ}$ C / sec, the temperature rise velocity may be set to  $80^{\circ}$ C / sec or more, as is the case of Embodiment 1, it is preferable that the velocity be set to  $150^{\circ}$ C / sec or more. In Embodiment 2 as well, as is the case of Embodiment 1, the oxidizing step is provided as the insulating film forming step of forming the silicon oxide films 64 that are insulating films on the surfaces of the silicon nanocrystals 63 that are semiconductor nanocrystal.

[0083] After the drift layer 6 has been formed, a first thin film layer consisting of a metal film (chrome film in Embodiment 2) is deposited on the drift layer 6 in accordance with the electron beam vapor deposition technique. Further, a second thin film layer consisting of a metal layer (gold layer in Embodiment 2) is deposited on the first thin film layer in accordance with the electron beam vapor deposition technique. In this manner, the surface electrode 7 consisting of the first thin film layer and the second thin film layer is formed, and the electron source 10 with its structure shown in Fig. 12D is obtained. In Embodiment 2, although the surface electrode 7 is formed in accordance with the electron beam vapor deposition technique, a method of forming the surface electrode 7 is not limited to the electron beam vapor deposition technique, and a sputtering technique may be employed, for example.

[0084] In this manner, with the method of manufacturing the electron source 10 according to Embodiment 2, the thickness of the silicon oxide film 64 that is an insulating film in the drift layer 6 can be provided as the film thickness to an extent such that an electron tunneling phenomenon occurs (degree of mean free path of electrons). Thus, electron diffusion in the silicon oxide films 64 each can be reduced, and a deviation of the thickness of the silicon oxide films 64 in the drift layer 6 can be reduced. In this manner, the design of the dielectric strength and service life is made easy. Therefore, the dielectric strength can be improved, and the service life can be extended. Further, the electron emission efficiency can be improved.

[0085] In the meantime, in Embodiments 1 and 2, the drift layer 6 is composed of the oxidized porous polycrystalline silicon layer. However, the drift layer 6 may be composed of a nitrided porous polycrystalline silicon layer or an oxi-nitrided porous polycrystalline silicon layer. Alternatively, this layer may be composed of the other oxide, nitride, or oxi-nitride porous semiconductor layer. [0086] In the case where the drift layer 6 is formed of the nitrided porous polycrystalline silicon layer, there may be employed a nitriding step (insulating film forming step) of nitriding the porous polycrystalline silicon layer 4 in accordance with the rapid heating technique in which the temperature rise velocity is set as in the embodiments by employing NH<sub>3</sub> gas, for example, instead

of the oxidizing step (insulating firm forming step) of carrying out oxidization in accordance with the rapid heating technique employing  ${\rm O_2}$  gas. In this case, the silicon oxide films 52 and 64 each in Fig. 1 are provided as silicon nitride films.