(19)

---

Europäisches Patentamt

European Patent Office

## Office européen des brevets

(11)

EP 1 324 170 A1

(12)

## DEMANDE DE BREVET EUROPEEN

(43) Date de publication:

**02.07.2003 Bulletin 2003/27**

(51) Int Cl.<sup>7</sup>: **G05F 1/56**, G05F 3/26

(21) Numéro de dépôt: **02080252.6**

(22) Date de dépôt: **11.12.2002**

(84) Etats contractants désignés:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR

IE IT LI LU MC NL PT SE SI SK TR

### Etats d'extension désignés:

**AL LT LV MK RO**

(30) Priorité: 20.12.2001 FR 0116577

(71) Demandeur: Koninklijke Philips Electronics N.V.

5621 BA Eindhoven (NL)

(72) Inventeur: **Marie, Hervé, c/o Société Civile S.P.I.D.**

**75008 Paris (FR)**

(74) Mandataire: Chaffraix, Jean

Société Civile S.P.I.D.

156, Boulevard Haussmann

75008 Paris (FR)

#### (54) Circuit à transconductance sensiblement constante

(57) Il s'agit d'un circuit à transconductance avec au moins une cellule à transconductance (100) montée entre deux bornes d'alimentation (20, 21) incluant au moins un transistor MOS (M1, M1'). Il comporte des moyens (200) pour polariser le transistor MOS (M1, M1') de la cellule (100) avec un courant de polarisation dont

la variation en fonction de la température compense sensiblement celle de la mobilité des porteurs majoritaires dans le canal du transistor MOS ( $M_1, M_1'$ ) de la cellule (100) de manière à rendre sa transconductance sensiblement indépendante de la température. Application notamment dans les circuits intégrés analogiques.

FIG. 1

**Description****DOMAINE TECHNIQUE**

5 [0001] La présente invention est relative à un circuit en technologie MOS à transconductance sensiblement constante, en particulier, un circuit à transconductance avec au moins une cellule à transconductance montée entre deux bornes d'alimentation incluant un transistor MOS. Ces circuits à transconductance souvent appelés convertisseur tension-courant sont largement employés dans les circuits intégrés analogiques notamment dans des montages intégrateurs pour réaliser par exemple des filtres, des oscillateurs, des circuits retardateurs.

**ETAT DE LA TECHNIQUE ANTERIEURE**

10 [0002] De tels circuits à transconductance peuvent comporter des circuits actifs et des résistances R en polysilicium ou diffusées et leur transconductance  $G_m$  est fonction du rapport  $1/R$ . Mais la valeur de la résistance R varie avec la température, ce qui rend la valeur de la transconductance instable. De plus la valeur de la résistance dépend du procédé de fabrication. La tolérance sur la valeur de la résistance est de l'ordre de plus ou moins 15 à 20% et cela se répercute sur la transconductance.

15 [0003] Les circuits à transconductance réalisés en technologie bipolaire ou MOS ont une transconductance  $G_m$  qui est proportionnelle à  $I/V_T$  ou à  $I/2V_{gt}$  respectivement, I étant le courant délivré par le circuit à transconductance,  $V_T$  la tension de seuil et  $V_{gt}$  la tension grille de saturation ('GATE OVERDRIVE VOLTAGE', en anglais) d'un transistor MOS. La transconductance  $G_m$  varie notamment comme le courant et celui-ci n'est pas constant et dépend d'une part de la température et d'autre part du procédé de fabrication.

20 [0004] Pourtant, notamment dans les circuits intégrateurs à transconductance, on cherche à ce que cette transconductance  $G_m$  soit sensiblement constante, car de sa valeur dépend la constante de temps du circuit. En effet, ces circuits intégrateurs comportent au moins un circuit à transconductance  $G_m$  et au moins un condensateur d'intégration C connecté à la sortie du circuit à transconductance et leur constante de temps T est proportionnelle au rapport C/ $G_m$ . Il est important que la constante de temps T soit la plus constante possible dans un grand nombre d'applications. On cherche également à ce que cette constante de temps soit connue avec précision et soit donc la plus insensible possible au procédé de fabrication du circuit intégrateur.

25 [0005] Pour rendre la constante de temps sensiblement constante, on est amené à l'asservir. On mesure la valeur de la constante de temps et l'on corrige cette valeur si la valeur mesurée est différente d'une valeur souhaitée. Le circuit d'asservissement nécessite une horloge de référence, des compteurs, un circuit de détection de phase ou un circuit à boucle de verrouillage de phase pour réaliser la mesure et un réseau de résistances et de condensateurs pour la correction. Ce circuit d'asservissement augmente de façon non négligeable le coût du circuit intégrateur, sa consommation en énergie ainsi que sa taille.

**EXPOSÉ DE L'INVENTION**

30 [0006] La présente invention vise justement à réaliser simplement un circuit à transconductance en technologie MOS dont la transconductance est sensiblement constante.

40 [0007] Dans ce type de circuit, on s'aperçoit que la transconductance dépend entre autre de la mobilité  $\mu$  des porteurs majoritaires (électrons ou trous selon le type de transistor MOS) dans le canal du transistor MOS et cette grandeur varie fortement avec la température. L'idée pour rendre la transconductance sensiblement constante est de compenser les variations thermiques de la mobilité  $\mu$  des porteurs majoritaires.

45 [0008] Pour y parvenir la présente invention propose un circuit à transconductance avec au moins une cellule à transconductance montée entre deux bornes d'alimentation incluant au moins un transistor MOS. Il comporte des moyens pour polariser le transistor MOS de la cellule avec un courant de polarisation dont la variation en fonction de la température compense sensiblement celle de la mobilité des porteurs majoritaires dans le canal du transistor MOS de la cellule de manière à rendre sa transconductance sensiblement indépendante de la température.

50 [0009] Les moyens de polarisation peuvent comporter un miroir de courant relié au transistor MOS de la cellule, ce miroir de courant coopérant avec un circuit d'accord lui-même relié à un générateur de tension de référence, le circuit d'accord comportant un transistor MOS d'accord traversé par le courant de polarisation que le miroir de courant recopie et la tension grille de saturation du transistor MOS d'accord possédant une pente en température sensiblement égale et opposée à celle de la mobilité des porteurs majoritaires dans le canal du transistor MOS de la cellule, cette tension grille de saturation étant obtenue à partir du générateur de tension de référence.

55 [0010] Le circuit d'accord peut comporter, de plus, un transistor bipolaire dont l'émetteur est relié à l'une des bornes d'alimentation à travers une résistance, dont la base est reliée au générateur de tension de référence et dont le collecteur est relié d'une part à l'autre borne d'alimentation à travers un montage série avec une diode et une résistance

et d'autre part à la grille du transistor MOS d'accord qui est monté entre l'autre borne d'alimentation et le miroir de courant.

[0011] Le générateur de tension de référence est destiné à délivrer au circuit d'accord une tension de référence permettant d'obtenir une pente en température telle que celle de la tension grille de saturation du transistor MOS d'accord compense sensiblement celle de la mobilité des porteurs majoritaires dans le transistor MOS de la cellule.

[0012] Un générateur de tension de référence classique quelconque, par exemple un générateur classique de tension de référence fondée sur la bande d'énergie interdite d'un matériau semi-conducteur, peut être utilisé pour obtenir un générateur de tension de référence présentant les caractéristiques ci-dessus. La tension fournie par un tel générateur classique possède une dépendance en température donnée, en général comprise entre 0 et 1. Cependant la dépendance en température de la tension grille de saturation du transistor MOS d'accord peut être modifiée selon l'invention pour compenser sensiblement celle de la mobilité des porteurs majoritaires dans le transistor MOS de la cellule.

[0013] Pour cela, le générateur classique est connecté à un pont diviseur incluant par exemple deux résistances, une des deux étant reliée à la sortie du générateur classique et l'autre à une masse, le point milieu entre ces deux résistances étant relié à l'entrée du circuit d'accord, c'est-à-dire à la base du transistor d'accord. En modifiant les valeurs relatives des résistances et par conséquent la valeur de la tension sur le point milieu, la pente en température dans l'émetteur du transistor d'accord peut être modifiée. Ainsi la combinaison entre un générateur de tension de référence classique et un pont diviseur de tension permet d'obtenir que la pente en température de la tension grille de saturation du transistor MOS d'accord compense sensiblement celle de la mobilité des porteurs majoritaires dans le transistor MOS de la cellule.

[0014] Il est aussi possible d'utiliser directement un générateur de tension de référence fournissant une tension permettant une dépendance en température voulue et contrôlée dans le transistor d'accord. Un exemple d'un tel générateur sera présenté.

[0015] La cellule à transconductance peut comporter une paire différentielle de transistors MOS dont les grilles forment les entrées du circuit à transconductance et les drains les sorties.

[0016] Dans un souci de linéarisation, la paire différentielle de transistors MOS peut coopérer avec une résistance de dégénérescence montée entre les sources des transistors MOS de la paire.

[0017] La résistance de dégénérescence peut être réalisée par une paire de transistors MOS, chacun d'entre eux ayant sa grille reliée à la grille de l'un des transistors MOS respectif de la paire différentielle.

[0018] La cellule à transconductance peut être montée entre les deux bornes d'alimentation à travers d'un côté les moyens de polarisation et de l'autre un circuit de charge.

[0019] Le circuit de charge peut être passif.

[0020] Dans un autre mode de réalisation, le circuit de charge peut être formé à base de source de courant coopérant avec système d'asservissement de mode commun des sorties du circuit à transconductance.

[0021] Un autre but de l'invention est de réaliser un circuit intégrateur à partir du circuit précédent et de rendre sa constante de temps sensiblement indépendante de la température et du procédé de fabrication. Un tel circuit intégrateur n'a pas besoin de circuit d'asservissement de la constante de temps. Un tel circuit intégrateur comporte au moins un circuit à transconductance ainsi défini, dont la sortie est connectée à un condensateur d'intégration réalisé à partir de transistor MOS.

[0022] La présente invention concerne également un filtre qui comporte au moins un tel circuit intégrateur.

[0023] La présente invention concerne également un circuit retardateur ou un oscillateur qui comportent au moins un tel circuit intégrateur. L'invention peut ainsi être mise en oeuvre dans un appareil destiné à la réception et à la transmission de signaux de radiotélécommunications incluant un circuit de transconductance selon l'invention. Un tel appareil peut par exemple être un téléphone.

#### 45 BRÈVE DESCRIPTION DES DESSINS

[0024] La présente invention sera mieux comprise à la lecture de la description d'exemples de réalisation donnés, à titre purement indicatif et nullement limitatif, en faisant référence aux dessins annexés sur lesquels :

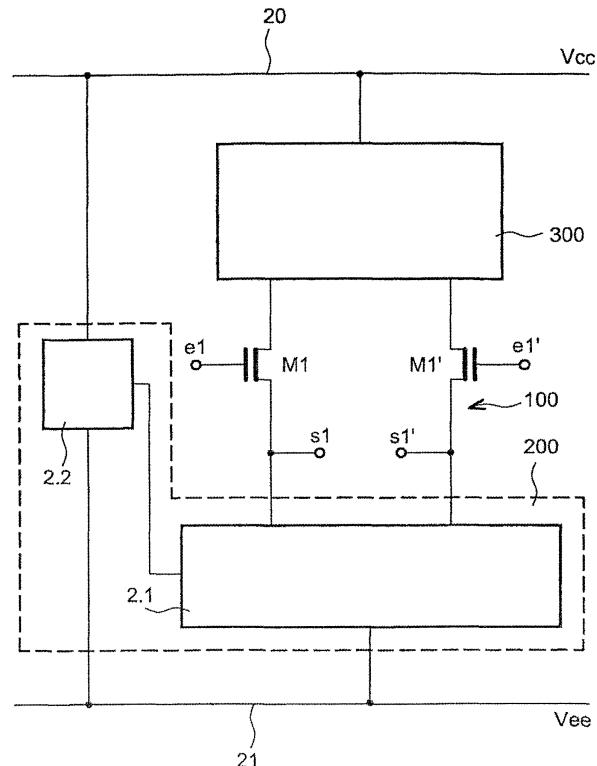

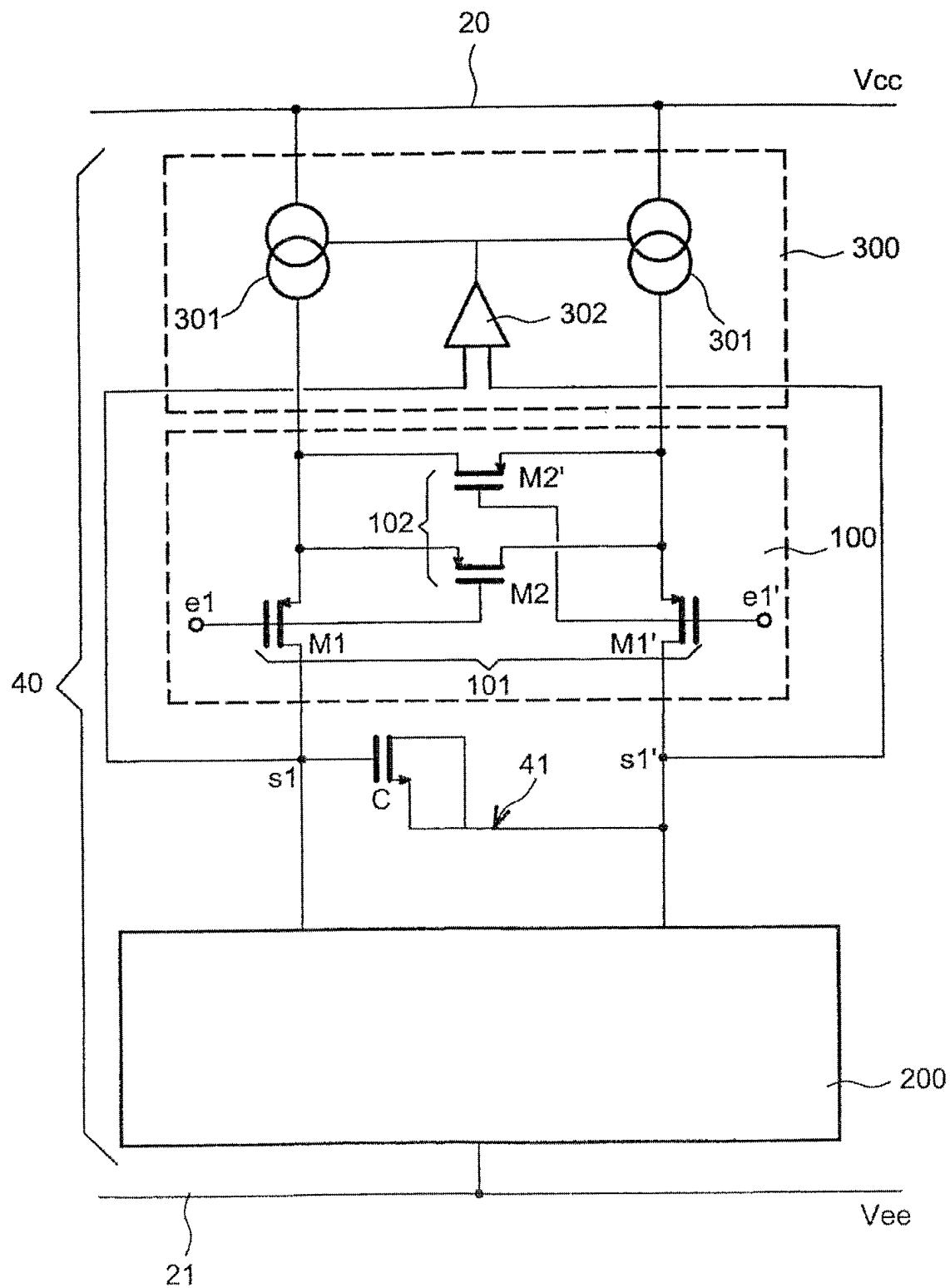

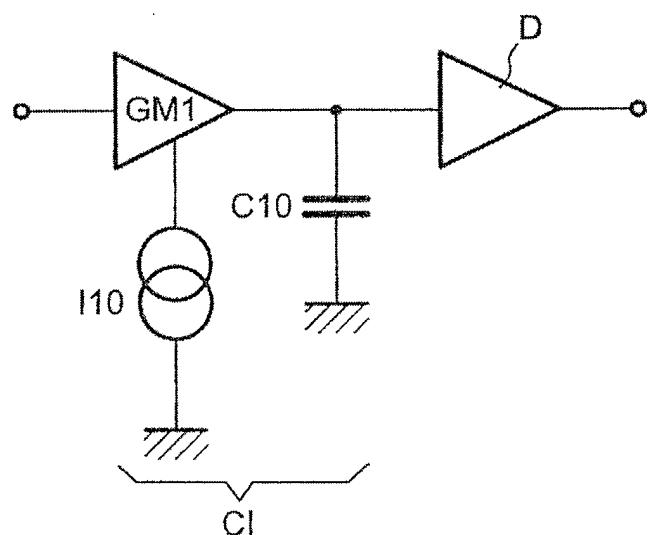

- 50 la figure 1 montre schématiquement un circuit à transconductance en technologie MOS conforme à l'invention ;

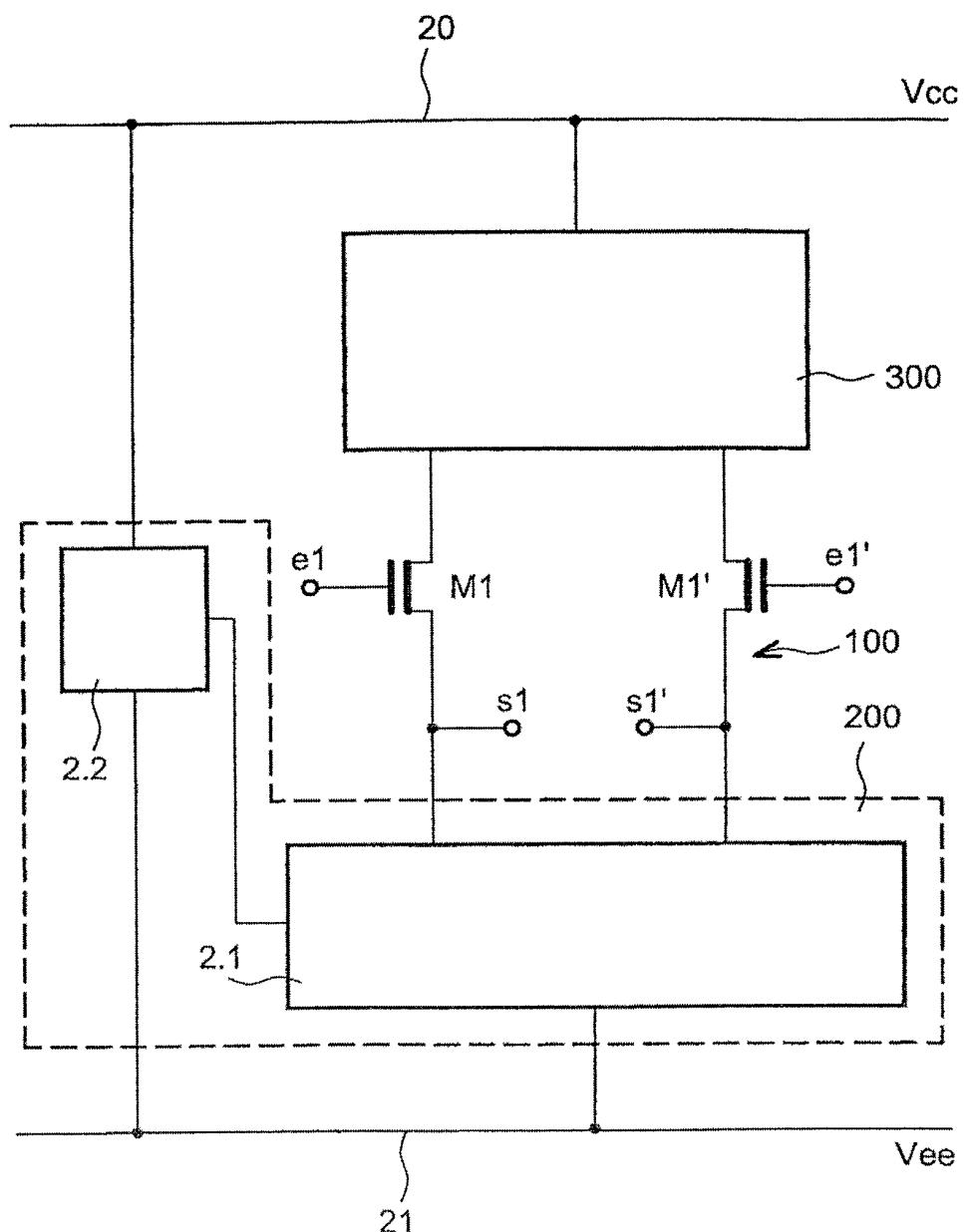

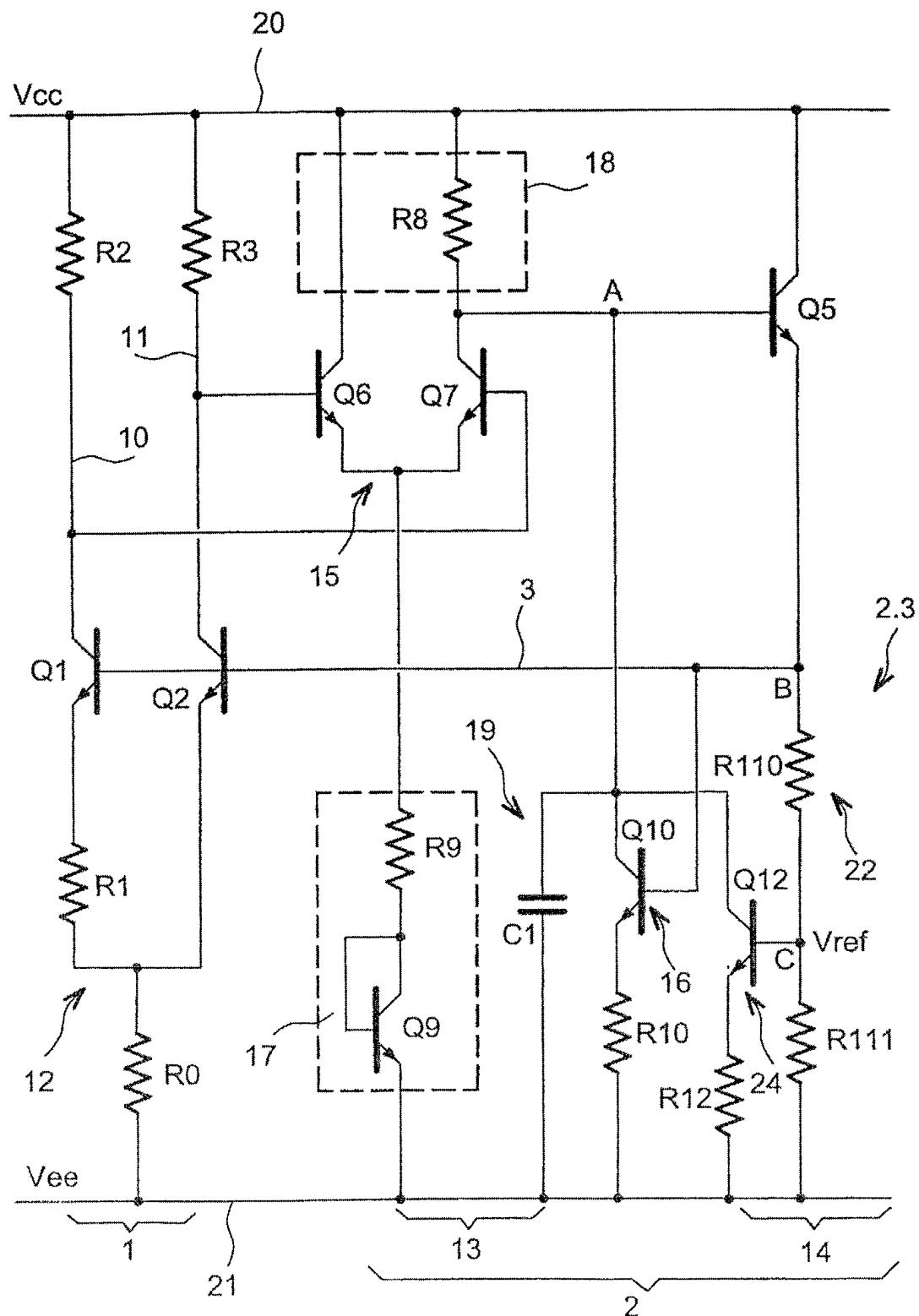

la figure 2 montre un schéma d'un circuit à transconductance en technologie MOS conforme à l'invention avec un circuit de charge passif et dans lequel les moyens de polarisation sont détaillés ;

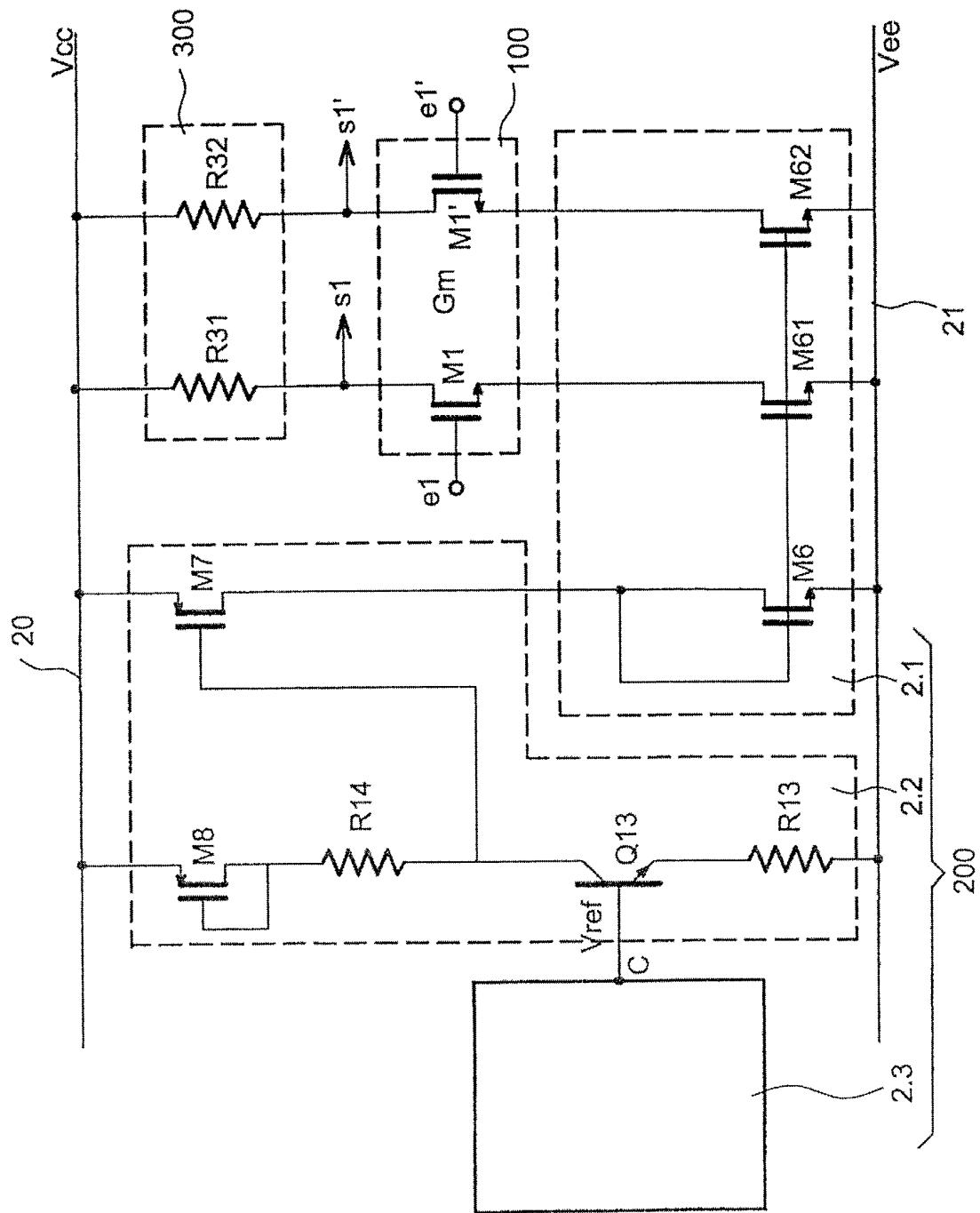

la figure 3 montre un exemple du générateur de tension de référence inclus dans les moyens de polarisation ;

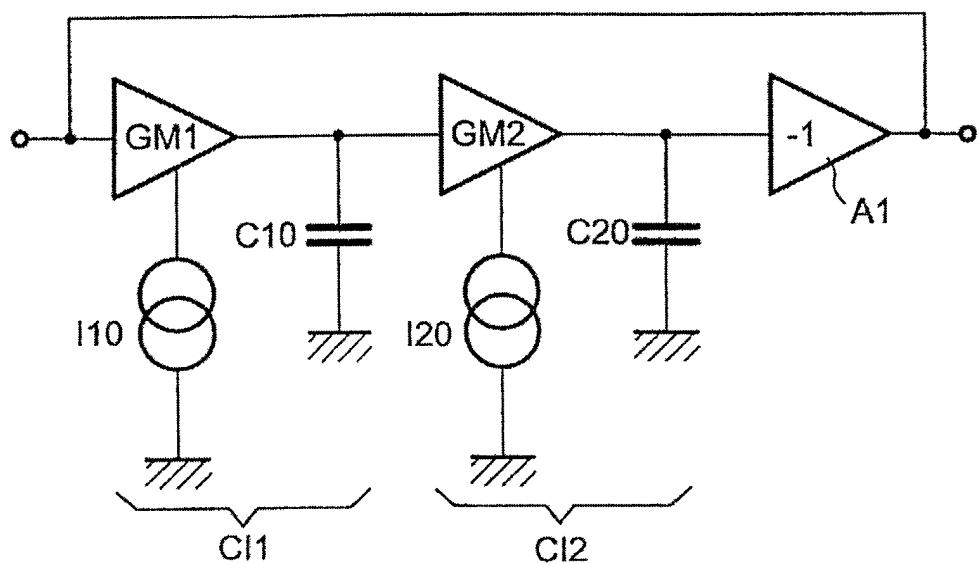

la figure 4 illustre un circuit intégrateur selon l'invention réalisé à partir d'un circuit à transconductance à circuit de charge actif ;

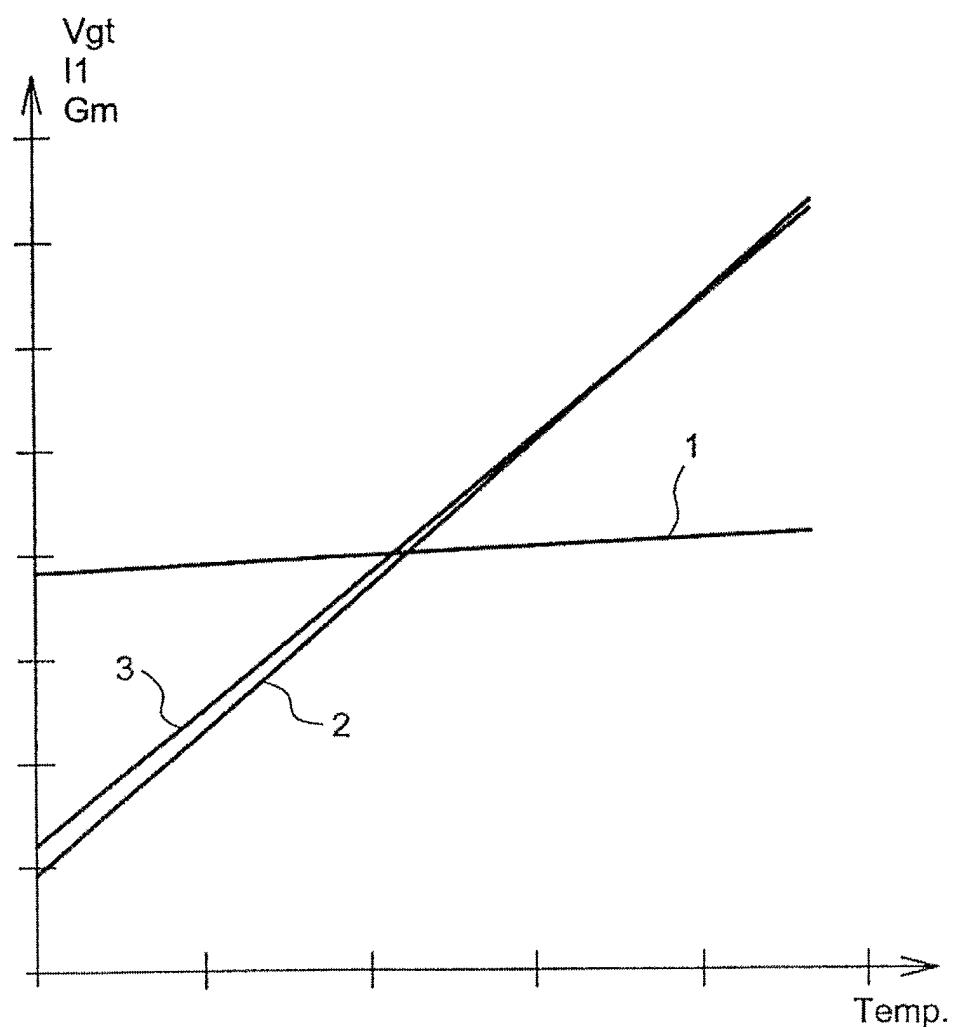

la figure 5 montre la variation de la tension grille de saturation, du courant de polarisation et de la transconductance en fonction de la température dans le circuit intégrateur de la figure 4 ;

les figures 6A, 6B montrent des schémas d'un oscillateur et d'un circuit retardateur réalisés à partir d'un circuit

intégrateur selon l'invention.

[0025] Les éléments identiques sont désignés par les mêmes caractères de référence.

## 5 EXPOSÉ DÉTAILLÉ DE MODES DE RÉALISATION PARTICULIERS

[0026] On va maintenant s'intéresser à un exemple de circuit à transconductance en technologie MOS selon l'invention. La figure 1 représente de manière très schématique un circuit à transconductance en technologie MOS conforme à l'invention. Ce circuit à transconductance comporte entre une première borne d'alimentation 20 portée à un potentiel haut Vcc et une seconde borne d'alimentation 21 portée à un potentiel bas Vee, généralement la masse, au moins une cellule à transconductance 100 avec au moins un transistor MOS. Dans l'exemple la cellule à transconductance 100 est représentée sous la forme d'une paire différentielle de transistors MOS M1, M1' et elle est reliée à l'une des bornes d'alimentation 21 par l'intermédiaire de moyens de polarisation 200 et à l'autre borne d'alimentation 20 par l'intermédiaire d'un circuit de charge 300. Le circuit de charge 300 peut être passif ou actif comme on le verra ultérieurement. D'autres configurations de la cellule à transconductance sont possibles comme par exemple celle illustrée sur la figure 4, la paire différentielle de transistors MOS est une configuration des plus simples.

[0027] Selon une caractéristique de l'invention les moyens de polarisation 200 délivrent aux transistors MOS de la cellule à transconductance 100 un courant de polarisation dont la variation avec la température compense sensiblement celle de la mobilité des porteurs majoritaires dans le canal des transistors MOS de la cellule 100 de manière à ce que la transconductance Gm du circuit soit sensiblement constante et indépendante de la température.

[0028] Le courant de polarisation circulant dans les transistors MOS de la cellule à transconductance 100 qui fonctionnent en régime de saturation est de la forme  $Id = \frac{1}{2}(\mu C_{ox} W/L)(Vgs - V_T)^2$  avec  $\mu$  mobilité des porteurs majoritaires,  $C_{ox}$  capacité par unité de surface de la couche d'oxyde des transistors MOS,  $W/L$  rapport de la largeur  $W$  du canal sur sa longueur  $L$ ,  $Vgs$  tension grille-source et  $V_T$  tension de seuil du transistor. La transconductance s'exprime par :

$$Gm = dId/dVgs \text{ à saturation soit}$$

$Gm = (\mu C_{ox} W/L)(Vgs - V_T)$ , la différence  $Vgs - V_T$  correspondant à  $Vgt$  ou tension grille de saturation des transistors MOS M1, M1'.

[0029] Dans cette expression la valeur de la mobilité  $\mu$  des porteurs majoritaires varie fortement avec la température, par contre elle est sensiblement indépendante du procédé de fabrication. En compensant cette variation à l'aide de la tension grille de saturation  $Vgt$ , on arrive à rendre la transconductance sensiblement indépendante de la température.

[0030] Les dimensions géométriques du canal des transistors MOS sont parfaitement maîtrisées lors de la fabrication. La valeur de la capacité  $C_{ox}$  de l'épaisseur d'oxyde par contre dépend du procédé de fabrication et pourra varier pour des circuits à transconductance appartenant à des lots différents.

[0031] On va voir maintenant comment réaliser les moyens de polarisation 200. Ils peuvent être réalisés par un miroir de courant 2.1 qui coopère avec un circuit d'accord 2.2, lui-même relié à un générateur de tension de référence 2.3, le circuit d'accord 2.2 comportant un transistor MOS M7 d'accord traversé par le courant de polarisation que le miroir de courant recopie et dont la tension grille de saturation possède une pente en température sensiblement égale et opposée à celle de la mobilité des porteurs majoritaires dans le canal des transistors MOS de la cellule à transconductance 100, cette tension grille de saturation étant obtenue à partir du générateur de tension de référence.

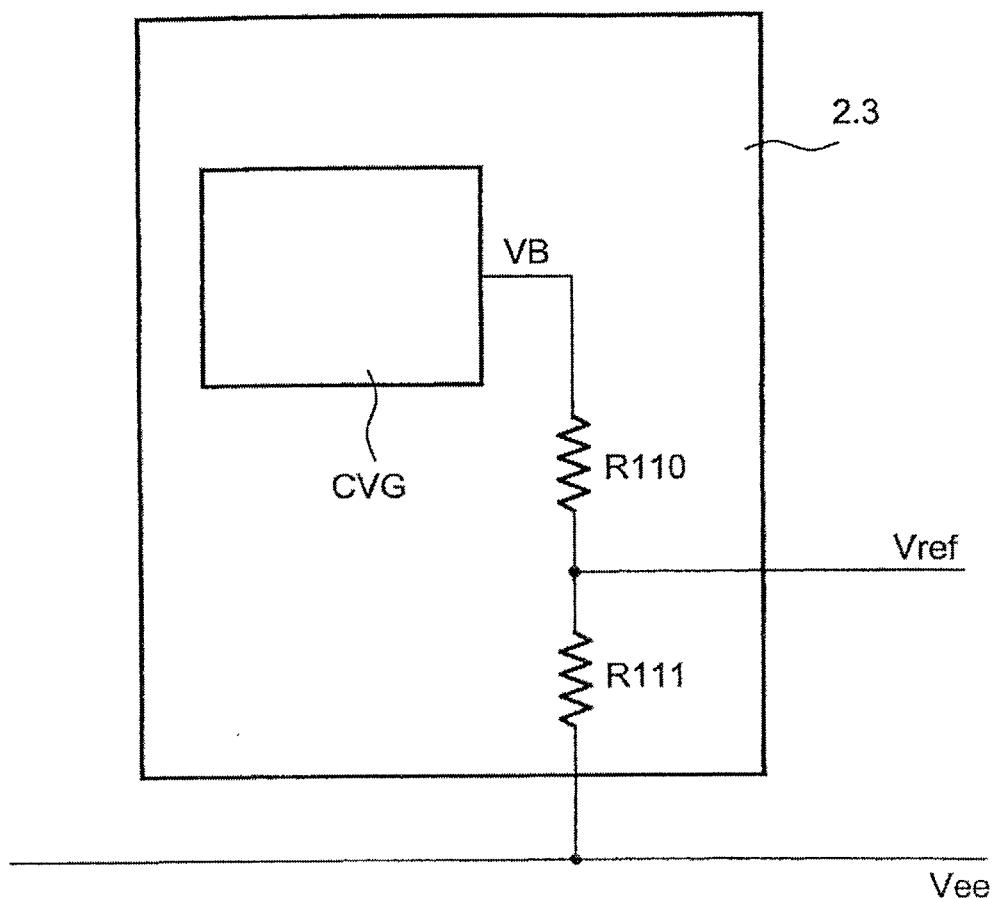

[0032] On peut se référer à la figure 2 qui montre en détails le miroir de courant 2.1 et le circuit d'accord 2.2. Deux exemples de modes de réalisation du générateur de tension 2.3 de référence sont montrés sur les figures 3a et 3b. Le générateur de la figure 3b est décrit en détails dans la demande de brevet français No. 01 16573 déposée le 20 Décembre 2001 au nom de la Demanderesse.

[0033] On remarquera que, sur cette figure 2, le circuit de charge 300 est passif et est formé d'une résistance R31, R32 reliée respectivement entre l'une des bornes d'alimentation 20 et les drains des transistors M1, M1' de la paire différentielle 100. Dans l'exemple, les transistors M1, M1' de la paire différentielle 100 sont des transistors MOS à canal N mais ils pourraient être à canal P moyennant les inversions appropriées.

[0034] Les sources des transistors M1, M1' de la paire différentielle 100 sont reliées aux moyens de polarisation 200. Les grilles des transistors M1, M1' de la paire différentielle forment l'entrée e1, e1' du circuit à transconductance tandis que la sortie s1, s1' se fait sur les drains des transistors M1, M1' de la paire différentielle 100 qui sont eux reliés au circuit de charge 300.

[0035] Le miroir de courant 2.1 comporte un transistor MOS asservi M61, M62 relié à chacun des transistors MOS M1, M1' de la paire différentielle de transistors 100 et un transistor MOS maître M6 relié au transistor MOS M7 d'accord du circuit d'accord 2.2.

[0036] On va voir maintenant plus en détails le circuit d'accord 2.2. Il comporte un transistor bipolaire Q13 dont l'émetteur est relié à l'une des bornes d'alimentation 21 à travers une résistance R13, dont la base est reliée au générateur de tension de référence 2.3 et dont le collecteur est relié à la grille du transistor MOS M7 d'accord d'une part et d'autre part à l'autre borne d'alimentation 20 à travers un montage série formé d'une résistance R14 et d'une diode,

représentée par un transistor MOS M8 monté en diode, c'est à dire dont la grille est reliée au drain. Plus précisément, la source du transistor MOS M8 est reliée à l'autre borne d'alimentation 20, son drain étant relié à la résistance R14 et à sa grille.

**[0037]** Le générateur de tension de référence 2.3 impose sur la base du transistor bipolaire Q13 une tension  $V_{ref}$  dont la variation avec la température est choisie pour que la tension grille de saturation  $V_{gt}$  du transistor MOS M7 d'accord relié au miroir de courant 2.1 ait la pente en température appropriée pour contrecarrer celle de la mobilité des porteurs majoritaires dans le canal des transistors MOS M1, M1' de la cellule à transconductance 100. De par leur fabrication le point d'opération de tous les transistors est dans la région de forte inversion, c'est-à-dire que la tension grille de saturation est égale à  $V_{gt} < V_{DS}$ .

**[0038]** On va voir comment s'exprime la tension grille de saturation  $V_{gt}$  du transistor MOS M7 d'accord relié au miroir de courant 2.1.

**[0039]**  $V_{gt}(M7) = V_{gs}(M7) - V_T$  avec  $V_{gs}(M7)$  tension grille source du transistor MOS M7 d'accord et  $V_T$  tension de seuil du transistor MOS M7 d'accord.

**[0040]** On peut encore exprimer  $V_{gt}(M7)$  de la manière suivante :

**15**  $V_{gs}(M7) = V(R14) + V_{gs}(M8)$  avec  $V(R14)$  tension aux bornes de la résistance R14 et  $V_{gs}(M8)$  tension grille source du transistor MOS M8 monté en diode.

**[0041]** Or  $V_{gs}(M8) \approx V_T$  car la tension grille à saturation du transistor MOS M8 est très petite. On peut alors simplifier et assimiler la tension grille à saturation  $V_{gt}(M7)$  du transistor MOS M7 d'accord à la tension  $V(R14)$  aux bornes de la résistance R14 :

$$20 \quad V_{gt}(M7) \approx V(R14).$$

**[0042]** En ajustant la valeur et la pente en température de la tension  $V_{ref}$  délivrée par le générateur de tension de référence 2.3 et les valeurs des résistances R13 et R14, il est aisément d'obtenir pour la tension  $V_{gt}(M7)$  une valeur et une pente souhaitées pour rendre la transconductance du circuit à transconductance sensiblement indépendante de la température.

**25** **[0043]** Nous allons maintenant présenter une manière extrêmement simple et homogène de comparer les pentes en température des différents composants électroniques qui nous intéressent. Plusieurs unités sont fréquemment employées pour désigner des pentes en température, s'il s'agit de résistances, on l'exprime en  $ppm/\text{ }^{\circ}\text{C}$  alors que pour la tension base émetteur  $V_{be}$  d'un transistor bipolaire, elle vaut environ  $-2 \text{ mV}/\text{ }^{\circ}\text{C}$  et pour la mobilité des porteurs majoritaires elle varie en  $T^{-1.5}$ .

**30** **[0044]** Posons la grandeur sans dimension  $t$  telle que :

$T = (T - T_0)/T_0$ , avec  $T$  température considérée et  $T_0$  température de référence par exemple égale à  $25^{\circ}\text{C}$ . Les valeurs de  $t$  suivantes sont obtenues par rapport aux températures  $T$  courantes :

$$35 \quad T = -1 \text{ pour } T = -273^{\circ}\text{C} \text{ ou } 0^{\circ}\text{K}$$

$$T = -1/4 \text{ pour } T = -50^{\circ}\text{C}$$

$$T = 0 \text{ pour } T = 25^{\circ}\text{C}$$

$$T = +1/4 \text{ pour } T = 100^{\circ}\text{C}$$

**[0045]** Une tension peut s'exprimer de la manière suivante en fonction de la grandeur  $t$  :

**40**  $V = V_0(a + bt + ct^2)$  avec  $V_0$  valeur de la tension à la température de référence  $T_0$  et  $a$ ,  $b$ ,  $c$  des coefficients. La pente en température au premier ordre est donnée par :

$$\alpha_1 = b/a \text{ et la pente en température au second ordre est donnée par } \alpha_2 = c/a.$$

**[0046]** Pour une tension proportionnelle à la température absolue (connue sous la dénomination de tension PTAT, PTAT étant l'abréviation anglo-saxonne pour Proportionnal To Absolute Temperature) on peut écrire :

$$45 \quad V_{PTAT} = V_{PTAT0}(1 + t) \text{ et pour une tension base-émetteur d'un transistor bipolaire :}$$

$V_{BE} = V_{BE0}(1 - t/2)$  avec  $V_{PTAT0}$  et  $V_{BE0}$  tensions à la température de référence. Pour un transistor bipolaire  $V_{BE0} = 0,8\text{V}$ .

**[0047]** On en déduit que la pente en température d'un circuit dont la tension est proportionnelle à la température absolue est de 1 tandis que la pente en température de la tension base-émetteur d'un transistor bipolaire est de  $-0,5$ .

**50** **[0048]** Quant aux résistances selon leurs valeurs, avec cette notation, leurs pentes peuvent varier négativement ou positivement et prendre la valeur 0. La mobilité  $\mu$  des porteurs majoritaires a une pente de  $-1,5$ .

**[0049]** Dans la majorité des cas le terme  $\alpha_2$  peut être considéré comme négligeable sauf pour le gain en courant  $\beta$  des transistors bipolaires.

**55** **[0050]** Avec ce qui précède, on cherche à ce que la pente de la tension grille de saturation  $V_{gt}(M7)$  du transistor MOS M7 d'accord soit sensiblement égale à  $+1,5$  pour compenser celle de la mobilité  $\mu$  des porteurs majoritaires qui est de  $-1,5$ .

**[0051]** On va maintenant décrire en référence à la figure 3 deux exemples de générateur de tension de référence 2.3 qui va fournir sur la base du transistor bipolaire Q13 du circuit d'accord 2.2 une tension de référence  $V_{ref}$  dont la

pente en température est ajustée pour obtenir la pente en température voulue au niveau de la tension grille de saturation  $V_{gt}(M7)$  du transistor MOS M7 d'accord.

**[0052]** Le générateur de tension de référence  $V_{ref}$  2.3 de la figure 3A se compose d'un générateur de tension de référence classique CVG et fournissant une tension  $V_B$  ayant une dépendance en température qui peut être quelconque. Souvent, cette dépendance est nulle mais elle peut être modifiée selon l'invention. De plus, avantageusement, le générateur classique CVG délivre une tension de référence fondée sur la bande d'énergie interdite d'un matériau semi-conducteur. Un pont diviseur incluant par exemple deux résistances  $R_{110}$  et  $R_{111}$  est connecté à la sortie du générateur de référence CVG. Une des deux résistances  $R_{110}$  a une de ses bornes reliée à la sortie du générateur classique CVG qui délivre la tension  $V_B$  et l'autre résistance a une de ces bornes reliée à un potentiel bas  $V_{ee}$ , généralement la masse. Les deux résistances  $R_{110}$  et  $R_{111}$  ont un point commun au niveau duquel se fait la sortie du générateur de tension de référence 2.3. En modifiant les valeurs relatives des résistances, la tension  $V_{ref}$  en sortie du générateur 2.3 par cette combinaison d'un générateur classique CVG et d'un pont diviseur  $R_{110}$ ,  $R_{111}$  peut être choisie de manière à ce que la pente en température dans le transistor d'accord compense celle de la mobilité  $\mu$  des porteurs majoritaires qui est de -1,5. En effet, lorsque la pente en température de la tension  $V_B$  est nulle,  $R_{110}=R_{111}/8$  permet d'obtenir une pente en température de 1,5 qui, nous le verrons est particulièrement avantageuse.

**[0053]** La figure 3B propose un exemple détaillé d'un générateur de tension de référence amélioré permettant la délivrance d'une tension dont la dépendance en température est contrôlée. Le générateur de tension de référence  $V_{ref}$  2.3 de la figure 3B se compose d'un étage d'entrée 1 à deux branches 10, 11 montées entre les deux bornes d'alimentation 20, 21. Dans chacune des branches 10, 11 se trouve au moins transistor bipolaire Q1, Q2 et ces transistors n'ont pas la même taille d'émetteur. Ce circuit d'entrée 1 combine une tension base émetteur d'un des transistors bipolaires Q2 avec une tension proportionnelle à la température absolue. Plus précisément, les deux transistors Q1, Q2 ont leur base commune, leurs collecteurs reliés à la borne d'alimentation 20 portée au potentiel  $V_{cc}$  par l'intermédiaire d'une résistance R2, R3 respectivement. L'émetteur du premier transistor Q1 est relié à l'autre borne d'alimentation 21 via un montage série 12 de deux résistances R1, R0. L'émetteur du second transistor Q2 est relié à l'autre borne d'alimentation 21 via l'une R0 des résistances du montage série 12. On suppose que la surface d'émetteur du premier transistor Q1 est égale à  $n$  ( $n$  entier supérieur à un) fois celle du second transistor Q2. Par exemple,  $n$  peut être égal à 8.

**[0054]** Cet étage d'entrée 1 coopère avec un amplificateur opérationnel 2 qui comporte un étage amplificateur différentiel 13, un étage de sortie 14, un circuit de compensation 16.

**[0055]** L'étage de sortie 14 délivre la tension de référence  $V_{ref}$ , il est relié par une boucle 3 à l'étage d'entrée 1 au niveau de la base commune des deux transistors Q1, Q2 de l'étage d'entrée 1.

**[0056]** L'étage amplificateur différentiel 13 comporte une paire de transistors Q6, Q7 différentielle 15 reliée à l'étage d'entrée 1 et montée entre les deux bornes d'alimentation 20, 21 par l'intermédiaire d'un circuit de source 17 et d'un circuit de charge 18. Plus précisément, les bases des deux transistors Q6, Q7 forment les deux entrées différentielles de l'étage 13. La base du transistor Q6 est reliée à la branche 11 au niveau du collecteur du transistor Q2, la base du transistor Q7 est reliée à la branche 10 au niveau du collecteur du transistor Q1. Les émetteurs des transistors Q6, Q7 sont reliés entre eux. Ils sont reliés à la borne d'alimentation 21 portée au potentiel  $V_{ee}$  par le circuit de source 17 qui est un circuit actif. Les circuits de source 17 et de charge 18 comportent des moyens de régulation R8, R9 pour, même lorsque la boucle 3 est ouverte, réguler la tension de référence  $V_{ref}$ , cette dernière étant ajustée de manière sensiblement indépendante du procédé de fabrication, des variations de la tension d'alimentation  $V_{cc}$ - $V_{ee}$  et avec une pente en température prédéterminée.

**[0057]** Le circuit de source 17 comporte en série une diode, représentée par un transistor Q9 branché en diode, et une résistance R9 faisant partie des moyens de régulation. La résistance R9 est reliée aux émetteurs communs des transistors Q6, Q7 de la paire différentielle 15. Les collecteurs des deux transistors Q6, Q7 sont reliés chacun à la borne d'alimentation 20 portée au potentiel  $V_{cc}$  par l'intermédiaire du circuit de charge 18. Ce circuit de charge 18 comporte une résistance R8, faisant partie des moyens de régulation, montée entre le collecteur du transistor Q7 de la paire différentielle et la borne d'alimentation 20. Le collecteur de l'autre transistor Q6 de la paire différentielle 15 est directement relié à la borne d'alimentation 20. L'étage de sortie 14 est relié en un premier noeud A au circuit de charge 18, au niveau du collecteur du transistor Q7. Les moyens de régulation des circuits de source 17 et de charge 18 de par leur configuration imposent que la tension apparaissant au premier noeud A soit pratiquement indépendante de variations de la tension d'alimentation  $V_{cc}$ - $V_{ee}$ .

**[0058]** En effet, le rapport des résistances R9 et R8 des moyens de régulation est choisi de telle manière qu'une variation  $\delta(V_{cc}-V_{ee})$  de la tension d'alimentation entraîne sensiblement la même variation  $\delta(V_{cc}-V_{ee})$  sur le circuit de source 17 et sur le circuit de charge 18 aux bornes de la résistance de charge R8 et ce quelle que soit la température.

En conséquence, le premier noeud A ne varie pas en tension lors d'une variation de la tension d'alimentation. Le rapport des résistances R8/R9 des moyens de régulation est choisi de telle manière que le gain en mode commun des résistances R2, R3 soit ajusté à la valeur -1. Ceci est réalisé lorsque le rapport des valeurs des résistances R8/R9 vaut approximativement 2, le courant dans la résistance R9 étant sensiblement égal à deux fois celui traversant la

résistance de charge R8. De plus, le circuit de source 17 est configuré pour générer un courant sensiblement indépendant de la température, ce qui revient à dire que la résistance R9 est ajustée pour que la tension à ses bornes soit sensiblement indépendante de la température. Cela est vérifié pour toutes les températures si l'ajustement suivant est réalisé au niveau de l'étage d'entrée 1.

5 [0059] La tension  $V_{R9}$  aux bornes de la résistance R9 s'exprime par :

$$V_{R9} = (V_{cc} - V_{ee}) - (V_{R3} + V_{BE}(Q6) + V_{BE}(Q9))$$

10  $V_{R9} = (V_{cc} - V_{ee}) - (V_{R3} + 2V_{BE})$

15 [0060] Le terme  $(V_{R3} + 2V_{BE})$  doit alors être sensiblement indépendant de la température, cela arrive s'il est égal à deux fois la tension présente à la liaison entre la boucle 3 et l'étage de sortie 14, par exemple et si la pente en température de la résistance de sommet R3 compense celles des deux tensions base-émetteur des transistors Q6 et Q9. Cela permet de rendre le générateur de tension de référence sensiblement insensible au procédé de fabrication. Avec la notation expliquée antérieurement, la pente en température de la résistance R3 est sensiblement égale à un et celle de la tension aux bornes de la résistance R9 sensiblement égale à zéro. Les deux résistances R2, R3 de collecteur de l'étage d'entrée 1 sont identiques.

20 [0061] L'étage de sortie 14 comporte un circuit suiveur 22 avec un transistor Q5 dont l'émetteur est relié à la borne d'alimentation 21 à travers un pont de résistances R110, R111. La base du transistor Q5 est reliée au premier noeud A tandis que l'émetteur du transistor Q5 est relié à la boucle 3 lorsqu'elle est fermée au niveau d'un second noeud B. La résistance R110 est reliée à l'émetteur du transistor Q5, la résistance R111 est reliée à la borne d'alimentation 21. Les deux résistances R110 et R111 ont un point commun C au niveau duquel se fait la sortie du générateur de tension de référence 2.3. On retrouve ici sous une forme plus élaborée l'utilisation d'un pont diviseur.

25 [0062] L'étage de sortie 14 comporte de plus un circuit de réglage 24 qui génère un courant dont la pente en température est sensiblement égale à +1,5 et cette pente est ajustée par les valeurs des résistances R110, R111 du pont diviseur et plus particulièrement par le rapport  $(R110 + R111)/R111$ . En donnant à ce rapport sensiblement la valeur 8/9, le courant traversant la résistance R12 possède sensiblement une pente de +1,5. Ce circuit de réglage 24 comporte un transistor Q12 dont l'émetteur est relié à la borne d'alimentation 21 à travers une résistance R12, dont le collecteur est relié au premier noeud A et au collecteur du circuit de compensation 16 et dont la base est reliée au circuit suiveur 22. La base du transistor Q12 est reliée au point commun C et c'est au niveau de la base du transistor Q12 que se fait la sortie du générateur de tension de référence.

30 [0063] Le courant qui circule dans le circuit de réglage 24 va être recopié dans l'ensemble Q13, R13 du circuit d'accord 2.2 décrit sur la figure 2. En effet cet ensemble Q13, R13 forme un miroir de courant avec le circuit de réglage 24. Les résistances R13 et R12 sont les mêmes.

35 [0064] Avec un tel circuit de réglage 24, la pente en température au niveau du point commun C qui correspond à la sortie du générateur de tension de référence 2.3 doit être sensiblement égale à zéro. Pour y parvenir, on va voir maintenant l'action du circuit de compensation 16 et du circuit de réglage 24 sur la pente en température au premier noeud A.

40 [0065] La pente en température de la tension au premier noeud A doit être sensiblement égale et opposée à celle apportée par le transistor Q5 de l'étage de sortie 14 pour obtenir la compensation en pente au point commun C. Il en résulte que la pente en température de la tension au premier noeud A doit être égale sensiblement à 0,5 puisque la pente en température d'une tension base émetteur d'un transistor bipolaire est de -0,5. Cette pente est conditionnée par celle du circuit de source 17 et par celle du circuit de compensation 16 associé au circuit de réglage 24. Ces trois circuits comportent chacun un transistor bipolaire Q9, Q10, Q12 dont la pente en température est imposée et égale à sensiblement -0,5 et une résistance R9, R10, R12 qu'il suffit d'ajuster pour imposer celle du circuit de charge 18. La pente en température du circuit de compensation 16 coopérant avec le circuit de réglage 24 prend ainsi sensiblement une valeur légèrement supérieure à un dans l'exemple décrit et celle du circuit de source 17 sensiblement la valeur 0.

45 [0066] Les courants générés par le circuit de compensation 16 et par le circuit de réglage 24 se combinent au niveau du circuit de charge 18 et le courant résultant dans le circuit de charge a une pente en température qui dépend des poids relatifs des courants des deux circuits, c'est-à-dire des valeurs des résistances R10, R12. Dans l'exemple décrit, il est préférable que la pente due aux circuits de compensation 16 et de réglage 24 soit légèrement supérieure à un pour s'affranchir d'inévitables parasites du second ordre qui ont une action de réduction de la valeur de la pente.

50 [0067] Il est préférable de prévoir, dans l'amplificateur opérationnel 2, un circuit de stabilisation 19 de l'amplificateur différentiel 13. Il peut être réalisé par un condensateur C1 connecté entre le noeud A et la borne d'alimentation 21.

55 [0068] Le tableau suivant regroupe les caractéristiques en valeur, pente et tension affectées à chacun des composants du générateur de tension de référence Vref de la figure 3.

| NOM                                        | VALEUR  | PENTE | CHUTE DE TENSION |

|--------------------------------------------|---------|-------|------------------|

| Vcc-Vee                                    | 2,8     | 0     | -                |

| R2, R3                                     | 16,8 kΩ | 1     | 0,8 V            |

| Vbe(Q1, Q2, Q6, Q7, Q5, Q9, Q10, Q12, Q13) |         | -0,5  | 0,8 V            |

| R1                                         | 1 kΩ    | 1     | 0,05 V           |

| R0                                         | 4,2 kΩ  | 1     | 0,4 V            |

| R8                                         | 10 kΩ   | 0,5   | 0,8 V            |

| R9                                         | 4,1 kΩ  | 0     | 0,4 V            |

| R10                                        | 40 kΩ   | 1     | 0,4 V            |

| R12, R13                                   | 15 kΩ   | 1,5   | 0,27 V           |

| R110                                       | 1 kΩ    | -     | -                |

| R111                                       | 8 kΩ    | -     | -                |

**[0069]** Tous les transistors bipolaires ont été représentés par des transistors NPN, mais il est possible de les remplacer par des transistors bipolaires PNP en effectuant toutes les inversions appropriées notamment au niveau du circuit de charge et de source.

**[0070]** La figure 4. montre un exemple de circuit intégrateur réalisé à partir d'un circuit à transconductance selon l'invention. Ce circuit intégrateur comporte un circuit à transconductance 40 sensiblement constante et un condensateur d'intégration 41 branché en sortie du circuit à transconductance. En réalisant le condensateur 41 à base de transistor MOS, la constante de temps T de ce circuit intégrateur est indépendante de la température et du procédé de fabrication du circuit. Dans l'exemple, la grille du transistor MOS réalisant le condensateur C est reliée à la sortie s1, le drain, le canal et la source du transistor MOS à la sortie s1'.

**[0071]** Dans cet exemple, le circuit à transconductance 40 comporte toujours la cellule à transconductance 100 montée entre un circuit de polarisation 200 et un circuit de charge 300. Mais le circuit à transconductance 40 n'est pas de même type que celui de la figure 2.

**[0072]** La cellule à transconductance 100 comporte toujours une paire différentielle 101 de transistors MOS M1, M1'. Cette paire différentielle 101 de transistors coopère maintenant avec une résistance de dégénérescence 102 représentée dans cet exemple sous la forme d'une paire de transistors MOS de dégénérescence M2, M2', chacun des transistors MOS de la paire différentielle M1, M1' est associé à l'un des transistors MOS de dégénérescence M2, M2' respectivement. Une telle résistance de dégénérescence 102 réalisée avec des transistors MOS amène une meilleure linéarité qu'une résistance de dégénérescence en silicium polycristallin. La linéarité optimale est obtenue lorsque le rapport W1/L1 de la largeur sur la longueur du canal des transistors MOS de la paire différentielle 101 est sensiblement égal à sept fois le rapport W2/L2 de la largeur sur la longueur du canal des transistors MOS de la résistance de dégénérescence 102.

**[0073]** Plus précisément les deux transistors MOS M1, M1' de la paire différentielle 101 ont leurs grilles qui forment les entrées e1, e1' du circuit intégrateur. Leurs sources sont reliées à la borne d'alimentation 20 portée au potentiel Vcc à travers le circuit de charge 300 et leurs drains à la borne d'alimentation 21 portée au potentiel Vee à travers le circuit de polarisation 200. On suppose que le circuit de polarisation 200 est similaire à celui représenté sur les figures 2 et 3.

**[0074]** La sortie s1, s1' du circuit à transconductance 40 se fait au niveau des drains des transistors MOS M1, M1' de la paire différentielle 101. Le condensateur d'intégration C est monté entre les deux sorties s1, S1' du circuit à transconductance.

**[0075]** Les transistors MOS M1, M1' de la paire différentielle 101 sont reliés aux transistors MOS M2, M2' de dégénérescence 102 de la manière suivante : chacune des sources des transistors MOS M1, M1' est reliée d'une part à la source de l'un des transistors MOS de dégénérescence M2, M2' respectivement et au drain de l'autre transistor MOS de dégénérescence M2', M2 respectivement. La grille de chacun des transistors MOS M2, M2' de dégénérescence est reliée à la grille du transistor MOS M1, M1' de la paire différentielle 101 avec lequel il est associé.

**[0076]** Le circuit de charge 300 est maintenant représenté comme un circuit actif sous la forme de deux sources de courant 301 équipées d'un système d'asservissement de mode commun 302 des sorties s1, s1' du circuit à transconductance 40 de manière à stabiliser la tension de sortie de mode commun. Les tensions présentes au niveau des sorties s1, s1' sont comparées dans un comparateur 302 et en fonction du résultat de la comparaison, les courants

## EP 1 324 170 A1

des sources de courant 301 sont ajustés. Le circuit de charge peut également être un simple circuit de charge tel que connu de l'homme du métier et incluant simplement des résistances. Le système d'asservissement de mode commun est un mode de réalisation amélioré.

**[0077]** On va maintenant exprimer la transconductance  $G_m$  du circuit à transconductance 40 de la figure 4.

**[0078]** Les transistors MOS M1, M1' de la paire différentielle 101 fonctionnent en mode saturé, le courant  $I_1$  qui les parcourt s'exprime par :

$I_1 = \frac{1}{2}(\mu C_{ox} W_1 / L_1) V_{gt}^2$  avec  $\mu$  mobilité des porteurs majoritaires dans le canal des transistors MOS M1, M1',  $C_{ox}$  capacité par unité de surface de la couche d'oxyde des transistors MOS,  $W_1 / L_1$  rapport de la largeur  $W_1$  sur la longueur  $L_1$  du canal des transistors MOS,  $V_{gt}$  tension grille de saturation des transistors MOS. La transconductance  $gm_1$  de la paire différentielle est donnée par :

$$gm_1 = \beta_1 V_{gt} \text{ avec } \beta_1 = \mu C_{ox} W_1 / L_1$$

**[0079]** Les transistors MOS M2, M2' de dégénérescence 102 fonctionnent en mode linéaire. Ils sont de même type que les transistors MOS M1, M1' de la paire différentielle et donc possèdent la même mobilité des porteurs majoritaires  $\mu$  et la même tension grille de saturation  $V_{gt}$  que les transistors MOS M1, M1' de la paire différentielle 101.

**[0080]** Le courant  $I_2$  qui les parcourt s'exprime par :

$I_2 = (\mu C_{ox} W_2 / L_2) V_{gt} \cdot V_{ds}$  avec  $\mu$  mobilité des porteurs majoritaires dans le canal des transistors MOS M2, M2',  $C_{ox}$  capacité par unité de surface de la couche d'oxyde des transistors MOS,  $W_2 / L_2$  rapport de la largeur  $W_2$  sur la longueur  $L_2$  du canal des transistors MOS,  $V_{gt}$  tension grille de saturation des transistors MOS et  $V_{ds}$  tension drain-source des transistors MOS.

**[0080]** La résistance  $R$  des transistors MOS de dégénérescence 102 est donnée par  $R = 1/\beta_2 \cdot V_{gt}$  avec

$$\beta_2 = \mu C_{ox} W_2 / L_2$$

**[0081]** La transconductance  $G_m$  du circuit à transconductance 40 s'exprime par

$$G_m = \frac{gm_1}{1 + gm_1 \frac{R}{4}}$$

30

$$G_m = \frac{1}{1 + \frac{7}{4}} \beta_1 \cdot V_{gt}$$

35

$$G_m = \beta_1 \cdot V_{gt} / 2,75$$

40

$$G_m = \frac{\sqrt{2} \beta_1 I_1}{2,75}$$

**[0082]** La constante de temps  $T$  du circuit intégrateur s'exprime par :

$$T = G_m / C \text{ avec } C \text{ capacité du condensateur } C.$$

45

$$T = \frac{\frac{1}{2,75} \mu C_{ox} \cdot \frac{W_1}{L_1} \cdot V_{gt}}{C_{ox} W_c \cdot L_c}$$

**[0083]** Le produit  $W_c L_c$  correspond au produit de la largeur  $W_c$  par la longueur  $L_c$  du canal du transistors MOS réalisant le condensateur  $C$ .

55

$$T = \frac{1}{2,75} \cdot \frac{W_1}{L_1 \cdot W_c \cdot L_c} \cdot \mu \cdot V_{gt}$$

**[0084]** En réalisant le condensateur  $C$  à base de transistor MOS, par exemple avec un transistor MOS fonctionnant en mode linéaire dont la grille forme l'une des électrodes du condensateur et dont la source, le drain et le canal forment

l'autre électrode, la constante de temps  $T$  ne dépend plus du procédé de fabrication car la capacité  $C_{ox}$  s'élimine dans son expression.

5

$$T = F \cdot \mu \cdot V_{gt}$$

**[0085]** La constante de temps ne dépend plus que d'un facteur géométrique  $F$  fonction de  $W_1/L_1$  et de  $W_c/L_c$  des transistors MOS, de la mobilité des porteurs majoritaires  $\mu$  et de  $V_{gt}$ . En ajustant la pente de la tension  $V_{gt}$  pour compenser celle de la mobilité  $\mu$ , on rend la constante de temps  $T$  d'un tel circuit intégrateur pratiquement insensible à la température et au procédé de fabrication.

**[0086]** Un tel circuit intégrateur peut fonctionner avec des amplitudes de signaux d'entrée plus importantes que celles d'un circuit intégrateur de l'art antérieur avec une cellule à transconductance ayant seulement une paire différentielle de transistors MOS.

**[0087]** La figure 5 montre les variations de différentes grandeurs en fonction de la température dans un circuit intégrateur tel que celui de la figure 4. La courbe référencée 1 représente les variations de la transconductance  $G_m$  du circuit à transconductance 40, la courbe référencée 2 représente le courant  $I_1$  et la courbe 3 représente la tension grille de saturation  $V_{gt}$  des transistors MOS de la cellule à transconductance. On voit bien que la transconductance  $G_m$  est sensiblement indépendante de la température, et que  $I_1$  et  $V_{gt}$  ont sensiblement la même pente en température de valeur +1,5.

**[0088]** Un tel circuit intégrateur possède une précision bien meilleure que ceux de l'art antérieur.

**[0089]** Le courant de polarisation des transistors MOS de la cellule à transconductance dépendant de l'adaptation de résistances critiques ou des transistors du générateur de tension de référence et du miroir de courant, la taille de ces composants doit être adaptée avec soin pour obtenir la précision recherchée.

**[0090]** Après analyse statistique, la constante de temps obtenue avec le circuit intégrateur de la figure 4 possède une précision d'environ 3% due aux variations de la température de la tension d'alimentation, d'environ 1,3% due à l'apéage entre composants et d'environ 1,6% due au procédé de fabrication.

**[0091]** Cela correspond environ à un décalage en fréquence d'environ  $\pm 12\%$ .

**[0092]** Un tel circuit intégrateur peut être employé comme filtre. Il peut servir de bloc de base dans un circuit oscillateur comme l'illustre la figure 6A ou dans un circuit retardateur comme l'illustre la figure 6B. Sur la figure 6A, on retrouve deux circuits intégrateurs conformes à l'invention montés en série CI1, CI2, la sortie du second circuit intégrateur CI2 étant reliée à un amplificateur A1 de gain -1. La sortie de l'amplificateur A1 est bouclée sur l'entrée du premier circuit intégrateur CI1. Chacun des circuits intégrateurs est schématisé par un amplificateur à transconductance GM1, GM2 polarisé par une source de courant  $I_{10}$ ,  $I_{20}$ . La sortie des amplificateurs GM1, GM2 est reliée à une électrode d'un condensateur d'intégration C10, C20 dont l'autre électrode est portée à la masse. Une meilleure précision sur la fréquence d'oscillation est obtenue en utilisant les circuits intégrateurs de l'invention.

**[0093]** Sur la figure 6B, le circuit retardateur comporte un circuit intégrateur CI selon l'invention dont la sortie est reliée à une cellule à retard D. La sortie du circuit retardateur se fait au niveau de la sortie de la cellule à retard D tandis que l'entrée se fait au niveau de l'entrée du circuit intégrateur CI. Le circuit intégrateur CI est schématisé comme sur la figure 6A avec un amplificateur à transconductance GM1 des moyens de polarisation  $I_{10}$  et un condensateur d'intégration C10.

**[0094]** Une meilleure précision sur le temps de propagation dans le circuit retardateur est obtenue en utilisant un circuit intégrateur selon l'invention.

**[0095]** Les circuits décrits dans ces dernières figures peuvent avantageusement être utilisés au sein d'un appareil destiné à la réception et/ou à la transmission de signaux de radiotélécommunication incluant un circuit de transconductance à performances améliorées selon l'invention. L'insertion de tels circuits de transconductance dans de tels appareils est connu de l'homme du métier.

**[0096]** Bien que certains modes de réalisation de la présente invention aient été représentés et décrits de façon détaillée, on comprendra que différents changements et modifications puissent être apportés sans sortir du cadre de l'invention.

50

## Revendications

- 55 1. Circuit à transconductance avec au moins une cellule à transconductance (100) montée entre deux bornes d'alimentation (20, 21) incluant au moins un transistor MOS (M1, M1'), **caractérisé en ce qu'il** comporte des moyens (200) pour polariser le transistor MOS (M1, M1') de la cellule (100) avec un courant de polarisation dont la variation en fonction de la température compense sensiblement celle de la mobilité des porteurs majoritaires dans le canal du transistor MOS (M1, M1') de la cellule (100) de manière à rendre sa transconductance sensiblement indépen-

dante de la température.

2. Circuit à transconductance selon la revendication 1, **caractérisé en ce que** les moyens de polarisation (200) comportent un miroir de courant (2.1) relié au transistor MOS (M1, M1') de la cellule (100), ce miroir de courant (2.1) coopérant avec un circuit d'accord (2.2) lui-même relié à un générateur de tension de référence (2.3), le circuit d'accord (2.2) comportant un transistor MOS (M7) d'accord traversé par le courant de polarisation que le miroir de courant (2.1) recopie, la tension grille de saturation (Vgt) du transistor MOS (M7) d'accord possédant une pente en température sensiblement égale et opposée à celle de la mobilité des porteurs majoritaires dans le canal du transistor MOS (M1, M1') de la cellule (100), cette tension grille de saturation étant obtenue à partir du générateur de tension de référence (2.3).

- 5

3. Circuit à transconductance selon la revendication 2, **caractérisé en ce que** le circuit d'accord (2.2) comporte de plus un transistor bipolaire (Q13) dont l'émetteur est relié à l'une des bornes d'alimentation (21) à travers une résistance (R13), dont la base est reliée au générateur de tension de référence (2.3) et dont le collecteur est relié d'une part à l'autre borne d'alimentation (20) à travers un montage série avec une diode ((M8) et une résistance (R14) et d'autre part à la grille du transistor MOS (M7) d'accord qui est monté entre l'autre borne d'alimentation (20) et le miroir de courant (2.1).

- 10

4. Circuit à transconductance selon l'une des revendications 2 ou 3, **caractérisé en ce que** le générateur de tension de référence (2.3) délivre au circuit d'accord (2.2) une tension de référence (Vref) dont la pente en température et la valeur sont choisies pour que la pente en température de la tension grille de saturation du transistor MOS (M7) d'accord compense sensiblement celle de la mobilité des porteurs majoritaires dans le transistor MOS (M1, M1') de la cellule (100).

- 15

5. Circuit à transconductance selon l'une des revendications 1 à 4, **caractérisé en ce que** la cellule à transconductance (100) comporte une paire différentielle de transistors MOS (M1, M1') dont les grilles forment les entrées (e1, e1') du circuit à transconductance et les drains les sorties (s1, s1').

- 20

6. Circuit à transconductance selon la revendication 5, **caractérisé en ce que** la paire différentielle de transistors MOS (M1, M1') coopère avec une résistance de dégénérescence (M2, M2') montée entre les sources des transistors MOS (M1, M1') de la paire.

- 25

7. Circuit à transconductance selon la revendication 6, **caractérisé en ce que** la résistance de dégénérescence est réalisée par une paire de transistors MOS (M2, M2'), chacun d'entre eux ayant sa grille reliée à la grille de l'un des transistors MOS (M1, M1') respectif de la paire différentielle.

- 30

8. Circuit à transconductance selon l'une des revendications 1 à 7, **caractérisé en ce que** la cellule à transconductance (100) est montée entre les deux bornes d'alimentation (20, 21) à travers d'un côté les moyens de polarisation (200) et de l'autre un circuit de charge (300).

- 35

9. Circuit intégrateur **caractérisé en ce qu'il** comporte un circuit à transconductance selon l'une des revendications 1 à 8 dont la sortie est connectée à un condensateur d'intégration (C) réalisé à partir de transistor MOS.

- 40

10. Filtre **caractérisé en ce qu'il** comporte au moins un circuit intégrateur selon la revendication 9.

- 45

11. Oscillateur **caractérisé en ce qu'il** comporte au moins un circuit intégrateur selon la revendication 9.

12. Circuit retardateur **caractérisé en ce qu'il** comporte au moins un circuit intégrateur selon la revendication 9.

- 50

13. Appareil destiné à la réception et/ou à la transmission de signaux de radiotélécommunication incluant un circuit de transconductance selon l'une des revendications 1 à 8.

FIG.1

FIG.2

FIG.3A

FIG.3B

FIG.4

FIG.5

FIG.6A

FIG.6B

Office européen

des brevets

## RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande

EP 02 08 0252

| DOCUMENTS CONSIDERES COMME PERTINENTS                                                     |                                                                                      |                         |                                              |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------|----------------------------------------------|

| Catégorie                                                                                 | Citation du document avec indication, en cas de besoin, des parties pertinentes      | Revendication concernée | CLASSEMENT DE LA DEMANDE (Int.Cl.7)          |

| X                                                                                         | EP 0 543 056 A (DELCO ELECTRONICS CORP)<br>26 mai 1993 (1993-05-26)                  | 1                       | G05F1/56<br>G05F3/26                         |

| Y                                                                                         | * abrégé *                                                                           | 2-8                     |                                              |

|                                                                                           | ---                                                                                  |                         |                                              |

| Y                                                                                         | US 5 986 910 A (NAKATSUKA JUNJI)<br>16 novembre 1999 (1999-11-16)                    | 2-8                     |                                              |

| A                                                                                         | * le document en entier *                                                            | 9-13                    |                                              |

|                                                                                           | ---                                                                                  |                         |                                              |

| A                                                                                         | EP 0 740 243 A (SAMSUNG ELECTRONICS CO LTD)<br>30 octobre 1996 (1996-10-30)          | 1-13                    |                                              |

|                                                                                           | * abrégé *                                                                           |                         |                                              |

|                                                                                           | ---                                                                                  |                         |                                              |

| A                                                                                         | US 5 748 030 A (AFEK YACHIN ET AL)<br>5 mai 1998 (1998-05-05)                        | 1-13                    |                                              |

|                                                                                           | * abrégé *                                                                           |                         |                                              |

|                                                                                           | ---                                                                                  |                         |                                              |

| A                                                                                         | US 6 265 929 B1 (HAUSER MAX WOLFF)<br>24 juillet 2001 (2001-07-24)                   | 1-13                    |                                              |

|                                                                                           | * abrégé *                                                                           |                         |                                              |

|                                                                                           | ---                                                                                  |                         |                                              |

| A                                                                                         | EP 0 911 978 A (ST MICROELECTRONICS SRL)<br>28 avril 1999 (1999-04-28)               | 1-13                    | DOMAINES TECHNIQUES<br>RECHERCHES (Int.Cl.7) |

|                                                                                           | * abrégé *                                                                           |                         |                                              |

|                                                                                           | ---                                                                                  |                         |                                              |

| A                                                                                         | US 5 978 240 A (NICOLLINI GERMANO)<br>2 novembre 1999 (1999-11-02)                   | 1-13                    | G05F                                         |

|                                                                                           | * abrégé *                                                                           |                         |                                              |

|                                                                                           | -----                                                                                |                         |                                              |

| Le présent rapport a été établi pour toutes les revendications                            |                                                                                      |                         |                                              |

| Lieu de la recherche                                                                      | Date d'achèvement de la recherche                                                    | Examinateur             |                                              |

| LA HAYE                                                                                   | 20 mars 2003                                                                         | Schobert, D             |                                              |

| CATEGORIE DES DOCUMENTS CITES                                                             |                                                                                      |                         |                                              |

| X : particulièrement pertinent à lui seul                                                 | T : théorie ou principe à la base de l'invention                                     |                         |                                              |

| Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie | E : document de brevet antérieur, mais publié à la date de dépôt ou après cette date |                         |                                              |

| A : arrrière-plan technologique                                                           | D : cité dans la demande                                                             |                         |                                              |

| O : divulgation non-écrite                                                                | L : cité pour d'autres raisons                                                       |                         |                                              |

| P : document intercalaire                                                                 | & : membre de la même famille, document correspondant                                |                         |                                              |

**ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE

RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.**

EP 02 08 0252

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Lesdits membres sont contenus au fichier informatique de l'Office européen des brevets à la date du

Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

20-03-2003

| Document brevet cité<br>au rapport de recherche |    | Date de<br>publication |       | Membre(s) de la<br>famille de brevet(s) | Date de<br>publication |

|-------------------------------------------------|----|------------------------|-------|-----------------------------------------|------------------------|

| EP 0543056                                      | A  | 26-05-1993             | US    | 5068595 A                               | 26-11-1991             |

|                                                 |    |                        | EP    | 0543056 A1                              | 26-05-1993             |

| US 5986910                                      | A  | 16-11-1999             | JP    | 11154833 A                              | 08-06-1999             |

| EP 0740243                                      | A  | 30-10-1996             | KR    | 134661 B1                               | 25-04-1998             |

|                                                 |    |                        | DE    | 740243 T1                               | 06-05-1999             |

|                                                 |    |                        | EP    | 0740243 A2                              | 30-10-1996             |

|                                                 |    |                        | JP    | 8307165 A                               | 22-11-1996             |

|                                                 |    |                        | US    | 5629614 A                               | 13-05-1997             |

| US 5748030                                      | A  | 05-05-1998             | AUCUN |                                         |                        |

| US 6265929                                      | B1 | 24-07-2001             | US    | 6188269 B1                              | 13-02-2001             |

| EP 0911978                                      | A  | 28-04-1999             | EP    | 0911978 A1                              | 28-04-1999             |

|                                                 |    |                        | DE    | 69710467 D1                             | 21-03-2002             |

|                                                 |    |                        | DE    | 69710467 T2                             | 07-11-2002             |

|                                                 |    |                        | JP    | 11194839 A                              | 21-07-1999             |

|                                                 |    |                        | US    | 5929621 A                               | 27-07-1999             |

| US 5978240                                      | A  | 02-11-1999             | IT    | 1295291 B1                              | 04-05-1999             |