(11) EP 1 324 304 A1

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

02.07.2003 Bulletin 2003/27

(51) Int Cl.<sup>7</sup>: **G09G 3/36**

(21) Application number: 01830810.6

(22) Date of filing: 27.12.2001

(84) Designated Contracting States:

AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE TR

**Designated Extension States:**

AL LT LV MK RO SI

(71) Applicants:

STMicroelectronics S.r.l.

20041 Agrate Brianza (Milano) (IT)

Dora S.p.A.

11024 Chatillon (AO) (IT)

(72) Inventors:

- Sala, Leonardo 11026 Pont Saint Martin (AO) (IT)

- Pulvirenti, Francesco

95024 Acireale (CT) (IT)

- Gariboldi, Roberto

20084 Lacchiarella (MI) (IT)

- (74) Representative: Mittler, Enrico c/o Mittler & C. s.r.l.,

Viale Lombardia, 20

20131 Milano (IT)

# (54) "Supply system of the driving voltage generator of the rows and of the columns of a liquid crystal display"

(57) The present invention refers to a supply system of the driving voltage generator of the rows and of the columns of a liquid crystal display. The supply system comprises first and second generator circuits (D3,D4) which output respective prefixed voltages (V3,V4). Each generator circuit receives two supply voltages. The first generator receives, via one voltage supply terminal, a

first voltage (VLCD). The second generator receives, via one voltage supply terminal, a second voltage (GND). The other supply terminals of the generators are each connected to a charge storage device (CTNK), e.g. a capacitor, which acts as a charging tank. Charge stored in the capacitor is shared by both generators, and a control circuit (CONT) causes the voltage across the capacitor to lie within a predefined range.

Fig.2

20

40

50

#### Description

**[0001]** The present invention refers to a supply system of the driving voltage generator of the rows and of the columns of a liquid crystals display.

[0002] Five voltage levels and the reference of ground GND are necessary for driving a liquid crystal display (LCD) according to the technique denominated Improved Halt & Pleshko (IA& P). The first voltage level is called Vlcd and it is directly proportional to the lighting threshold of the liquid crystal and to the square root of the number of the driven rows. The other four voltage levels V2, V3, V4 and V5 are distributed between the Vlcd and GND voltages according to a law that depends on the square root of the number of the driven rows. Particularly, on the increasing of the number of rows, the voltages V2, V3, V4 and V5 tend to gather at the extreme supply values, that is the voltages V2 and V3 towards the voltage Vlcd while the voltages V4 and V5 towards the ground voltage GND.

**[0003]** The different voltage levels are applied to the rows and columns with alternate phase in order to cancel the direct component of the voltage applied to the display, harmful for the liquid crystal. More particularly, in a frame period, or part of it, the rows are driven between the voltages V5 and Vlcd, while in the following period the rows are driven between the voltages GND and V2, in the same way the columns are driven between the voltages GND and V4 and between the voltages V3 and Vlcd.

[0004] Normally, the voltage Vlcd is generated by a charging pump starting from the supply voltage Vdd, while the other four voltage levels V2, V3, V4 and V5 are obtained by intermediary dividers of Vlcd, and applied to voltage followers that work as buffer circuits, normally supplied between the voltages Vlcd and GND. [0005] For driving a liquid crystal display (LCD) according to the technique denominated Multi Row Addressing (MLA) a number of driving voltages that grow linearly with the number of rows simultaneously driven are requested, while the voltage generation techniques are similar to what previously described.

[0006] The US patent 6,201,522 describes a method for driving a liquid cristal display that includes a series of multiplexers coupled to the columns of the display. The multiplexers couple selectively each of the columns to a capacity for a fraction of the driving period to discharge each of the pixel placed in the column. In the fraction of the remaining driving period the multiplexer couples to the column the driving voltage generators. This solution requires that all the controller outputs coupled to the display, equal in number to the sum of the totality of the rows and the totality of the columns, have an additional capacitor, according to a "distributed" approach.

**[0007]** In view of the state of the art described, it is an object of the present invention to provide a supply system of the driving voltage generator of the rows and of

the columns of a liquid crystals display with greater efficiency and simpler as regards the known art.

[0008] According to the present invention, this and other objects are achieved by means of a supply system of the driving voltage generator of the rows and of the columns of a liquid crystals display comprising: a first terminal of a first supply voltage; a second terminal of a second supply voltage; a first generator circuit of a first prefixed voltage having a third terminal of a third supply voltage and a fourth terminal of a fourth supply voltage; a second generator circuit of a second prefixed voltage having a fifth terminal of a fifth supply voltage and a sixth terminal of a sixth supply voltage; characterized by further comprising an energy storage device coupled to said fourth and to said fifth terminal.

**[0009]** Thanks to the present invention it is possible to provide the driving voltage generators with a charge reserve, so as to reduce the need to draw, where the supply of a current is requested, directly from the power supply. Preferably, such charging tanks, are equipped with a control circuit that assures the correct working of the generators towards the voltage variations of the charging tank. According to the present invention it is possible to apply a charging tank for each couple of driving voltages. Advantageously an hysteresis has been introduced into such a control circuit.

**[0010]** The solution according to the present invention is applicable both to the driving method according to the technique denominated Improved Halt & Pleshko (IA& P), and according to the denominated technique Multi Row Addressing (MLA), but the application of other techniques is not excluded.

**[0011]** The features and the advantages of the present invention will be made more evident by the following detailed description of a particular embodiment, illustrated as a non-limiting example in the annexed drawings, wherein:

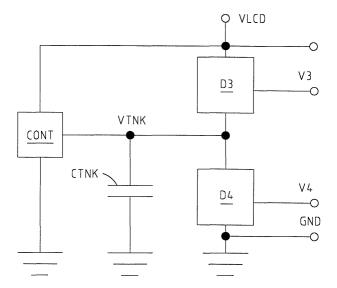

figure 1 represents an example of a supply system of the driving voltage generation of the rows and of the columns of a liquid crystals display according to the known art IA&P;

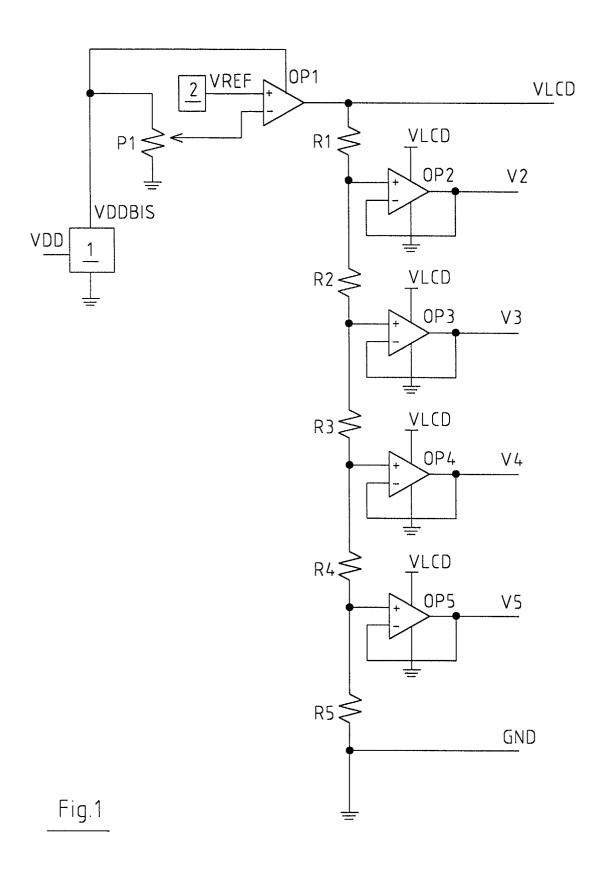

figure 2 represents in a schematic way one part of a supply system of the driving voltage generator of the rows and of the columns of a liquid crystals display according to the present invention;

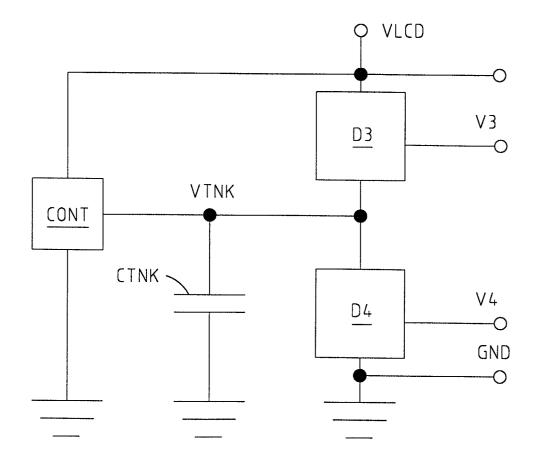

figure 3 represents in a schematic way a supply system of the driving voltage generator of the rows and of the columns of a liquid crystals display according to the present invention;

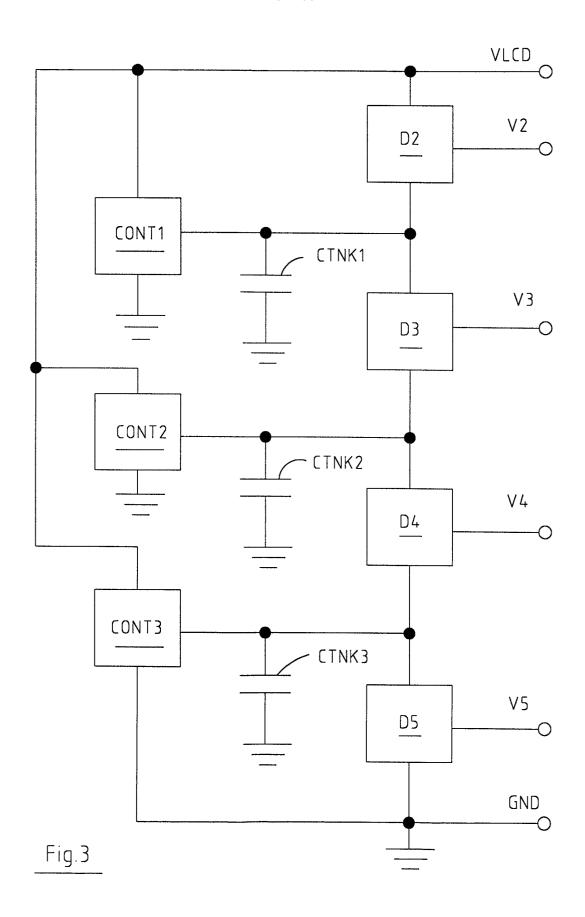

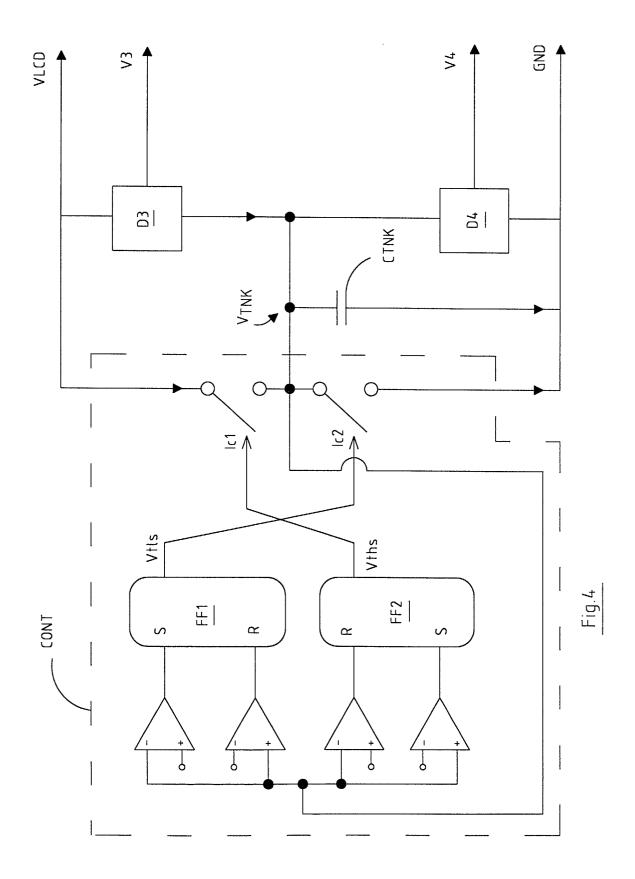

figure 4 represents a first embodiment of a supply system of the driving voltage generator of the rows and of the columns of a liquid crystals display according to the present invention;

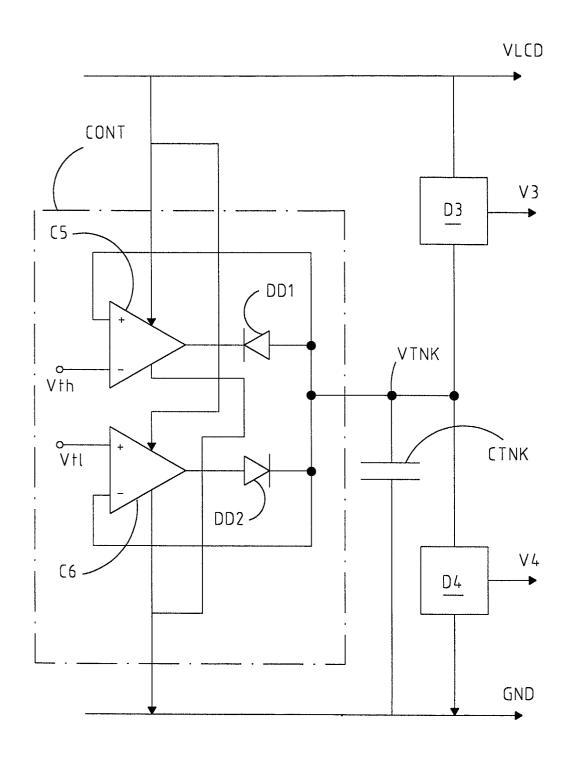

figure 5 represents a second embodiment of a supply system of the driving voltage generator of the rows and of the columns of a liquid crystals display according to the present invention. [0012] Referring now to figure 1, that represents a system according to the known art, the supplying voltage Vdd supplies a positive charging pump 1, that provides in output the voltage Vddbis. The voltage Vddbis supplies an operational amplifier OP1 that supplies a voltage Vlcd in output. The voltage Vlcd is applied to a terminal of a variable resistance P1, the other terminal of P1 is connected to ground GND. The cursor of the variable resistance P1 is connected to the negative terminal of the operational amplifier OP1. A reference voltage Vref produced by a voltage generator 2 is connected to the positive terminal of the operational amplifier OP1. The operational amplifier OP 1 produces a voltage VIcd in output. This voltage Vlcd is applied to a resistance divider R1-R5 in turn connected to ground GND. The positive inputs of the operational amplifiers denominated respectively OP2-OP5 are applied at the junction nodes between a resistance and another. The negative terminals of the operational amplifiers OP2-OP5 are connected to the respective outputs of the operational amplifiers OP2-OP5, so as to constitute voltage followers. The operational amplifiers OP2-OP5 produces respectively the voltages V2-V5 at their outputs.

**[0013]** The operational amplifiers OP2-OP5, in the embodiment of figure 1, are supplied between the voltages Vlcd and GND, alternatively they can be supplied by any suitable voltage.

**[0014]** The voltage generator 2 is designed so that it compensates the thermal variations and eventually other factors of the liquid crystal display.

**[0015]** We refer now to figure 2 that represents in a schematic way one part of a supply system of the driving voltage generator of the rows and of the columns of a liquid crystals display according to the present invention.

[0016] The supply voltage VIcd and the ground voltage GND supply two circuits D3 and D4, that are schematic of one part of the circuits reported in figure 1, that produce respectively the driving voltages V3 and V4 in output. Particularly the voltage VIcd is applied to a supplying terminal of the circuit D3, the voltage GND is applied to a supplying terminal of the circuit D4; the other two supplying terminals of the circuits D3 and D4, connected in the known art of figure 1 respectively to ground and VIcd, in this case are connected together and a capacitor Ctnk is connected to them too, with the function of storage energy device.

**[0017]** Preferably, a control circuit CONT is connected to the capacitor Ctnk too, preferably, but not necessarily, supplied by the voltages Vlcd and GND.

**[0018]** In the example of figure 2 only the two circuits D3 and D4 are reported for descriptive simplicity but it is possible to generalize this solution for each couple of driving voltages.

**[0019]** The charge transfer from the generator of the driving voltage D3, or upper, to D4, or lower, happens as shown here inafter.

[0020] In the case of voltage switching (of column)

from a voltage V smaller than V3 to the voltage V3, there is a charge inflow in the circuit D3 from the supply Vlcd. **[0021]** In the case of voltage switching (of column) from a voltage V greater than V3 to the voltage V3, there is a charge outflow in the capacitor Ctnk, without charge inflow toward ground, as otherwise required by the known solution.

**[0022]** Preferably, if the voltage of the capacitor Ctnk goes up beyond a prefixed upper activation threshold, it is brought again to an suitable value to the correct working of D3 by the control circuit Cont.

**[0023]** In the case of voltage switching (of column) from a voltage V greater than V4 to the voltage V4, there is a charge outflow toward the voltage GND.

**[0024]** In the case of voltage switching (of column) from a voltage V smaller than V4 to the voltage V4, there is a charge inflow from the capacitor Ctnk toward the circuit D4, without requiring charges from the supply VI-cd, as otherwise required by the known solution.

**[0025]** Preferably, if the voltage of the capacitor Ctnk goes down beyond a prefixed lower activation threshold, it is brought again by the control circuit Cont to a suitable value for the correct working of D4.

**[0026]** In the particular case of the Improved Halt & Pleshko driving method, the characteristic distribution of the voltage levels of the rows and of the columns allows therefore to synthesize the following optimizations in the charge transfer.

**[0027]** Accumulation of the discharging current from the voltage Vlcd to V3 for the following re-use (in the period with dual polarity) as charge current from the voltage GND to the voltage V4. Each transition of the column waveform toward greater voltages will determine a contribution of current that, added to those associates to the other columns, will fix the general amount of charge transferred in the charging tank Ctnk during of the frame period.

[0028] Accumulation of the discharging current from the voltage Vlcd to V2 for the following re-use (in the period with duel polarity) as charge current from the voltage GND to V5. The type of useful transition to such charge accumulation comes true, in the case of Improved Halt & Pleshko driving, only in correspondence of the last row, before the beginning of the new period with inverted polarity.

**[0029]** The control circuit Cont keeps the voltage to the terminals of the capacitor Ctnk within an prefixed voltages range. In the example of figure 2 the prefixed voltages range is for instance comprised between the voltages V3-0,5V and V4+0,5V, and however must be so as to guarantee the right working of D3 and D4.

**[0030]** Besides it is possible to share the same charging tank by the generators of the driving voltages of row and of column, as it is possible to see in figure 3, so as to make the charge accumulated by the rows available for the columns and vice versa. In this case, a charging tank or a capacitor Ctnk1-Ctnk3 are applied between each couple of adjoining voltages, so that the charge

transfer happens where possible between the capacitors Ctnk1-Ctnk3.

**[0031]** Particularly, a terminal of the capacitors Ctnk1-Ctnk3 is connected respectively to the common terminals of D2-D3, D3-D4 and D4-D5, while the other terminal of the capacitors Ctnk1-Ctnk3 is preferably, but not necessarily, connected to ground GND, or any other supply terminal.

**[0032]** The control circuits Cont1-Cont4 check the voltages to the terminals of the capacitors Ctnk1-Ctnk3 respectively.

[0033] In figure 2 and 3 it is represented a solution according to the present invention for the Improved Halt & Pleshko driving method but this solution is also extendable in the case of the Multi Row Addressing method. In such a case the used voltages for driving are not only 6 but, normally, they are in greater number as they linearly grow with the row number simultaneously driven. In fact showing the number of rows simultaneously driven with p, the number of voltage levels requested is in general, taking into account both the row voltages and the column voltages, equal to p+3, while, excluding the upper supply Vlcd and the lower one GND, the number of driving voltage generators results to be p+1. Admitting therefore the use of N = (p+1) - 1 = p capacitors, the reduction of the current consumption will be equal up to 1/(p+1) times.

**[0034]** In the examples reported in this description the upper supply voltage is the Vlcd, but they can be supplied with any other suitable voltage.

**[0035]** We refer now to figure 4 that represents a first embodiment of a supply system of the driving voltage generator of the rows and of the columns of a liquid crystals display according to the present invention.

**[0036]** It is necessary to note the possibility that the capacitor Ctnk is undersized, or that particular driving patterns of the display break the symmetry between two couples of driving voltages. Therefore it is necessary to foresee a recovery system of the optimal operation condition maintaining the voltage to the terminals of the capacitor Ctnk within a prefixed voltage range and in the example of figure 4 to a voltage value centred in the neighbourhood of the intermediary value between the voltage V3 and the voltage V4.

**[0037]** Besides, in this case, it has been decided of introduce an hysteresis for avoiding the repeated intervention of the control circuit.

**[0038]** Particularly, in figure 4, the same elements of figure 2 are noticed, where however a possible embodiment of the circuit Cont is represented.

[0039] The voltage Vtnk available on the capacitor Ctnk is applied to the negative input of the comparators C1 and C3 and to the positive input of the comparators C2 and C4. The reference voltage Vth2 is applied to the positive input of the comparator C1, the reference voltage Vth1 is applied to the negative input of the comparator C2, the reference voltage Vtl1 is applied to the positive input of the comparator C3, the reference voltage

Vtl2 is applied to the negative input of the comparator C4. The outputs of the comparators C1-C4 are applied respectively to the inputs S and R of the flip-flop FF1 and FF2. The output of the flip-flop FF1 controls a controlled switch IC2 connected between the terminal of the capacitor Ctnk and ground GND. The output of the flip-flop FF2 controls a controlled switch IC1 connected between the terminal of the capacitor Ctnk and the voltage Vlcd.

**[0040]** Supposing of being in the period in which the voltages V3 and Vlcd are activated, if the voltage Vtnk at the terminals of the capacitor Ctnk overcomes the voltage Vth2, then the flip-flop FF1 closes the switch IC2 and the voltage Vtnk is reduced up to the achievement of a lower voltage value Vth1, at this point the flip-flop FF1 reopens the switch IC2, preventing the ulterior discharge of the capacitor Ctnk.

**[0041]** Supposing now of being in the period in which the voltages V4 and GND are activated, if the voltage Vtnk at the terminals of the capacitor Ctnk goes down under the voltage Vtl2, then the flip-flop FF2 closes the switch IC 1 and the voltage Vtnk increases up to the achievement of an upper voltage value Vtl1, at this point the flip-flop FF2 reopens the switch IC1, preventing the further charging of the capacitor Ctnk.

[0042] Supposing that the row number is Nr = 64 and the upper voltage used for driving the display is shown with Vlcd, than the sizing of the capacitor Ctnk can be effected as described in the following. Supposing of wishing to supply the display with an average current of 500  $\mu$ A, that the voltage is Vth= 1,5V, that the period is equal to 20 ms, that the voltages Vtl2 and Vth2 are respectively V4+0,5V and V3-0,5V, and being Kv the multiplier factor that guarantees the correct effective voltage applied, we have

$$K_{\rm V} = (1 + \sqrt{(Nr+1)}) / \sqrt{(2^*(1 - (\frac{1}{\sqrt{(Nr+1)}})))} = 6,75$$

B= $\sqrt{Nr}$  + 1 = 9 Vlcd= Kv\* Vth= 6,75\* Vth= 10.5 Q=I\*T=500\*20=10 μC C = Q/V = 10/(5\*(1/B)\*Vlcd - 2 \* 0,5) = 2 μF

**[0043]** Where Q is the charge that the charging tank supplies in the frame period, V is the voltage difference we can have between the start and the stop of the frame, compatibly with the correct working of the control circuits, B is the bias that shows the spacing of the voltage levels of a given row number.

**[0044]** This sizing of the capacitor Ctnk, that makes the function of charging tank in the particular embodiment of figure 4, allows of excluding, in absence of sudden display changes that can determine asymmetries in the capacitor charging and discharging, the intervention of the recovery circuit of the optimal situation that is the circuit Cont.

20

35

**[0045]** We refer now to figure 5 that represents a second embodiment of a supply system of the driving voltage generator of the rows and of the columns of a liquid crystals display according to the present invention.

[0046] In this case a further possible embodiment of the circuit Cont is represented. The voltage Vtnk available at the capacitor Ctnk is applied to the positive input of the comparator C5 and to the negative input of the comparator C6; it is also applied to the anode of the diode DD1 whose cathode is applied to the output of the comparator C5, and to the cathode of the diode DD2 whose anode is applied to the output of the comparator C6. The reference voltage Vth is applied to the negative input of the comparator C5, and the reference voltage Vtl is applied to the positive input of the comparator C6. Both the comparators C5 and C6 are supplied between Vlcd and ground GND.

[0047] If the voltage Vtnk of the capacitor Ctnk is within the reference voltages Vth and Vtl, both the diodes DD1 and DD2 are inversely biased and there is neither a contribution nor a subtraction of charge from the capacitor Ctnk. If instead the voltage Vtnk overcomes the reference voltage Vth the comparator C5 tries to reduce the output voltage, lowering the voltage of the cathode of the diode DD1 and carrying the diode DD1 in forward bias, which subtracts charges from the capacitor Ctnk and reducing the voltage on its terminals. If instead the voltage Vtnk is smaller than the reference voltage Vtl the comparator C6 tries to increase the output voltage, increasing the voltage of the anode of the diode DD2 and carrying the diode DD2 in direct biasing, that brings charge to the capacitor Ctnk and increasing the voltage at its terminals.

#### **Claims**

- 1. Supply system of the driving voltage generator of the rows and of the columns of a liquid crystals display comprising: a first terminal of a first supply voltage (Vlcd); a second terminal of a second supply voltage (GND); a first generator circuit (D3) of a first prefixed voltage (V3) having a third terminal of a third supply voltage and a fourth terminal of a fourth supply voltage; a second generator circuit (D4) of a second prefixed voltage (V4) having a fifth terminal of a fifth supply voltage and a sixth terminal of a sixth supply voltage; characterized by further comprising an energy storage device (Ctnk) coupled to said fourth and to said fifth terminal.

- Supply system according to claim 1 characterized in that said third terminal is coupled to said first terminal and said sixth terminal is coupled to said second terminal.

- Supply system according to claim 1 characterized in that said energy storage device (Ctnk) is charged

in a first phase and is discharged in a second phase.

- **4.** Supply system according to claim 1 **characterized by** comprising a control circuit (Cont) that maintains the voltage at the terminals of said energy storage device (Ctnk) within a prefixed voltage range.

- 5. Supply system according to claim 4 characterized in that said control circuit (Cont) comprises two controlled switchs (IC1, IC2) that allow said energy storage device (Ctnk) to be selectively coupled to said first terminal of a first supply voltage (Vlcd) and to said second terminal of a second supply voltage (GND).

- 6. Supply system according to claim 5 characterized in that said control circuit (Cont) controls said two controlled switches (IC1, IC2) in response to the voltage (Vtnk) available at the terminals of said energy storage device (Ctnk).

- Supply system according to claim 6 characterized in that said control circuit (Cont) introduces a hysteresis.

- 8. Supply system according to claim 4 **characterized** in **that** said control circuit (Cont) receives in input two reference voltages (Vth, Vtl) corresponding to said prefixed voltage range.

- Supply system according to claim 4 characterized in that said control circuit (Cont) receives in input four reference voltages(Vth1, Vth2, Vtl1, Vtl2) proportional to said prefixed voltage range.

- 10. Supply system according to claim 4 characterized in that said control circuit (Cont) comprises a first circuit (C3, C4, FF2, IC1, C6, DD2) able to charge said energy storage device (Ctnk) in the case in which the voltage (Vtnk) available at the terminals of said energy storage device (Ctnk) is smaller than said prefixed voltage range.

- 11. Supply system according to claim 4 characterized in that said control circuit (Cont) comprises a second circuit (C1, C2, FF1, IC2, C5, DD1) able to discharge said energy storage device (Ctnk) in the case in which the voltage (Vtnk) available at the terminals of said energy storage device (Ctnk) is greater than said prefixed voltage range.

- 12. Supply system according to claim 1 characterized by comprising a plurality of generator circuits (D2-D5) of prefixed voltages having terminals of supply voltages connected in series between them and that energy storage devices (Ctnk1-Ctnk3) are coupled to the connection of said terminals of supply voltages.

50

Fig.2

Fig.5

# **EUROPEAN SEARCH REPORT**

Application Number EP 01 83 0810

| Category                       | Citation of document with indic<br>of relevant passage                                                                                                |                                                                                     | Relevant<br>to claim                                    | CLASSIFICATION OF THE APPLICATION (int.Cl.7) |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------|

| X                              | EP 0 772 182 A (SHARP<br>7 May 1997 (1997-05-0<br>* abstract *<br>* page 7, line 37 - p<br>* page 9, line 45 - p<br>figure 5 *                        | 7)<br>age 8, line 4 *                                                               | 1-6,<br>10-12                                           | G09G3/36                                     |

| Υ                              | * page 13, line 17 - figure 8 *                                                                                                                       | page 13, line 35;                                                                   | 8                                                       |                                              |

| X                              | EP 0 756 190 A (SEIKO<br>29 January 1997 (1997<br>* abstract *<br>* column 8, line 31 -                                                               | -01-29)                                                                             | 1-4,<br>10-12                                           |                                              |

| Y                              | figure 1 *                                                                                                                                            | - column 16, line 54;                                                               | 8                                                       |                                              |

| Y                              | PATENT ABSTRACTS OF J<br>vol. 016, no. 050 (P-<br>7 February 1992 (1992<br>-& JP 03 251817 A (HI                                                      | 1308),<br>-02-07)<br>TACHI LTD;OTHERS:                                              | 8                                                       | TECHNICAL FIELDS SEARCHED (Int.Cl.7) G09G    |

| A                              | 01), 11 November 1991<br>* abstract *<br>* figure 1 *                                                                                                 |                                                                                     | 1-6,8,<br>10-12                                         | H03K                                         |

| X                              | EP 0 391 655 A (SHARP KK)<br>10 October 1990 (1990-10-10)<br>* page 10, line 52 - page 11, line 5;<br>figure 15 *                                     |                                                                                     | 1-3,12                                                  |                                              |

| X                              | US 5 751 278 A (ODA K<br>12 May 1998 (1998-05-<br>* column 21, line 4 -<br>figure 20 *                                                                | y 1998 (1998-05-12)<br>umn 21, line 4 - column 22, line 16;                         |                                                         |                                              |

|                                | The present search report has bee                                                                                                                     |                                                                                     |                                                         |                                              |

|                                | Place of search MUNICH                                                                                                                                | Date of completion of the search 28 March 2002                                      | Mor                                                     | ris, D                                       |

| X : parti<br>Y : parti<br>docu | ATEGORY OF CITED DOCUMENTS  cularly relevant if taken alone cularly relevant if combined with another ument of the same category nological background | T : theory or principle E : earlier patent document cited in L : document cited for | cument, but publice nother application or other reasons | nvention<br>shed on, or                      |

# **EUROPEAN SEARCH REPORT**

Application Number EP 01 83 0810

|                                                        | DOCUMENTS CONSID                                                                                                                                                                       | ERED TO BE RELEVANT                                                                        | ······································                                                             |                                              |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------|

| Category                                               | Citation of document with in<br>of relevant pass                                                                                                                                       | ndication, where appropriate,<br>ages                                                      | Relevant<br>to claim                                                                               | CLASSIFICATION OF THE APPLICATION (Int.Cl.7) |

| Α                                                      | ;SGS THOMSON MICROE<br>2 October 1996 (199<br>* abstract *                                                                                                                             |                                                                                            | 1-11                                                                                               |                                              |

| A                                                      | US 4 983 931 A (NAK<br>8 January 1991 (199<br>* column 3, line 28<br>figures 3,4 *                                                                                                     |                                                                                            | 9-11                                                                                               |                                              |

|                                                        |                                                                                                                                                                                        |                                                                                            |                                                                                                    | TECHNICAL FIELDS<br>SEARCHED (Int.Cl.7)      |

|                                                        |                                                                                                                                                                                        |                                                                                            |                                                                                                    |                                              |

|                                                        |                                                                                                                                                                                        | •                                                                                          |                                                                                                    | ·                                            |

|                                                        |                                                                                                                                                                                        |                                                                                            |                                                                                                    |                                              |

|                                                        | The present search report has t                                                                                                                                                        | peen drawn up for all claims                                                               | -                                                                                                  |                                              |

| _                                                      | Place of search                                                                                                                                                                        | Date of completion of the search                                                           |                                                                                                    | Examiner                                     |

|                                                        | MUNICH                                                                                                                                                                                 | 28 March 2002                                                                              | Mor                                                                                                | ris, D                                       |

| X : parti<br>Y : parti<br>docu<br>A : tech<br>O : non- | ATEGORY OF CITED DOCUMENTS cularly relevant if taken alone cularly relevant if combined with anoth ment of the same category nological background -written disclosure mediate document | E : earlier patent d<br>after the filing o<br>ner D : document cited<br>L : document cited | ple underlying the i<br>ocument, but publis<br>late<br>d in the application<br>of or other reasons | nvention<br>shed on, or                      |

EPO FORM 1503 03.82 (P04C01)

### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 01 83 0810

This annex lists the patent family members relating to the patent documents cited in the above–mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

28-03-2002

| A<br>A<br>A | 07-05-1997<br>29-01-1997<br>11-11-1991<br>10-10-1990 | JP<br>EP<br>US<br>CN<br>WO<br>NONE           | 9101496<br>0772182<br>5781001<br>0756190<br>6188395<br>1145668<br>9621879<br>2264296<br>2520169 | A2<br>A<br>A1<br>B1<br>A<br>A1                                                                                                                                                                                           | 15-04-1997<br>07-05-1997<br>14-07-1998<br>29-01-1997<br>13-02-2001<br>19-03-1997<br>18-07-1996                                                                                                                                                                     |

|-------------|------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α           | 11-11-1991                                           | US<br>CN<br>WO<br>NONE<br>JP<br>JP           | 6188395<br>1145668<br>9621879<br>                                                               | B1<br>A<br>A1<br>                                                                                                                                                                                                        | 13-02-2001<br>19-03-1997<br>18-07-1996<br>                                                                                                                                                                                                                         |

| <b>-</b>    |                                                      | JP<br>JP                                     |                                                                                                 |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                    |

| A           | 10-10-1990                                           | JP                                           |                                                                                                 |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                    |

|             |                                                      | JP<br>JP<br>JP<br>JP<br>DE<br>EP<br>KR<br>US |                                                                                                 | B2<br>A<br>B2<br>A<br>B2<br>A<br>D1<br>A2<br>B1                                                                                                                                                                          | 31-07-1996<br>03-02-1999<br>15-04-1991<br>03-02-1999<br>15-04-1991<br>03-12-1997<br>01-08-1991<br>20-07-1995<br>10-10-1990<br>12-01-1994<br>09-05-1995                                                                                                             |

| A           | 12-05-1998                                           | JP<br>JP<br>JP<br>JP<br>JP<br>JP<br>JP<br>JP | 2708945<br>4097281<br>2708946<br>4097283<br>2708947<br>4097285<br>2634688<br>4097218            | B2<br>A<br>B2<br>A<br>B2<br>A<br>B2<br>A                                                                                                                                                                                 | 30-03-1992<br>04-02-1998<br>30-03-1992<br>04-02-1998<br>30-03-1992<br>04-02-1998<br>30-03-1992<br>30-07-1997<br>30-03-1992<br>11-03-1997                                                                                                                           |

| A           | 02-10-1996                                           | EP<br>DE<br>DE<br>JP<br>US                   | 69514090<br>69514090<br>9069760                                                                 | D1<br>T2<br>A                                                                                                                                                                                                            | 02-10-1996<br>27-01-2000<br>25-05-2000<br>11-03-1997<br>16-09-1997                                                                                                                                                                                                 |

| Α           | 08-01-1991                                           | JP                                           | 3034619                                                                                         | Α                                                                                                                                                                                                                        | 14-02-1991                                                                                                                                                                                                                                                         |

|             | A                                                    | A 02-10-1996                                 | A 12-05-1998 JP JP JP JP JP JP JP JP US  A 02-10-1996 EP DE DE JP US                            | KR 9400254 US 5414443  A 12-05-1998 JP 4097279 JP 2708945 JP 4097281 JP 2708946 JP 4097283 JP 2708947 JP 4097285 JP 2634688 JP 4097218 US 5610627  A 02-10-1996 EP 0735677 DE 69514090 DE 69514090 JP 9069760 US 5668508 | KR 9400254 B1 US 5414443 A  A 12-05-1998 JP 4097279 A JP 2708945 B2 JP 4097281 A JP 2708946 B2 JP 4097283 A JP 2708947 B2 JP 4097285 A JP 2634688 B2 JP 4097218 A US 5610627 A  A 02-10-1996 EP 0735677 A1 DE 69514090 D1 DE 69514090 T2 JP 9069760 A US 5668508 A |

FORM P0459

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82