(19)

Europäisches Patentamt

European Patent Office

Office européen des brevets

(11)

EP 1 475 895 A8

(12)

## DEMANDE DE BREVET EUROPEEN CORRIGEE

Avis: La bibliographie est mise à jour

(15) Information de correction:

**Version corrigée no 1 (W1 A1)**

**code(s) INID 71**

(51) Int Cl.7: **H03M 13/41**

(48) Corrigendum publié le:

**26.01.2005 Bulletin 2005/04**

(43) Date de publication:

**10.11.2004 Bulletin 2004/46**

(21) Numéro de dépôt: **04354020.2**

(22) Date de dépôt: **10.05.2004**

(84) Etats contractants désignés:

**AT BE BG CH CY CZ DE DK EE ES FI FR GB GR**

**HU IE IT LI LU MC NL PL PT RO SE SI SK TR**

Etats d'extension désignés:

**AL HR LT LV MK**

(30) Priorité: **09.05.2003 FR 0305648**

(71) Demandeur: **STMicroelectronics SA**

**F-92120 Montrouge (FR)**

(72) Inventeurs:

- Urard, Pascal**

38570 Theys (FR)

- Paumier, Laurent**

38000 Grenoble (FR)

- Lantreibecq, Etienne**

73190 Challes les Eaux (FR)

(74) Mandataire: **de Beaumont, Michel**

**Cabinet Michel de Beaumont**

1, rue Champollion

38000 Grenoble (FR)

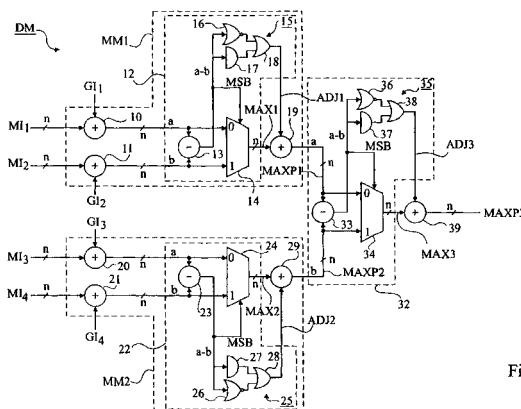

### (54) Dispositif et procédé d'addition-comparaison-sélection-ajustement dans un décodeur

(57) L'invention concerne un dispositif (MM1) d'addition-comparaison-sélection-ajustement comprenant :

des premier et deuxième additionneurs (10, 11) pour produire des valeurs a et b respectivement égales à la somme de premières métriques d'état précédent ( $MI_1$ ) et de branche ( $GI_1$ ) et à la somme de deuxièmes métriques d'état précédent ( $MI_2$ ) et de branche ( $GI_2$ ) ;

un bloc de calcul (12) pour fournir la plus grande des valeurs a et b sur une première sortie, et produire une valeur d'ajustement sur une deuxième sortie ; et

un troisième additionneur (19) pour produire une métrique d'état courant égale à la somme des sorties du bloc de calcul ;

dans lequel les additionneurs (10, 11, 19) effectuent des additions sans conservation de la retenue de telle manière que la métrique d'état courant et les valeurs intermédiaires a et b comportent le même nombre de bits que les première et deuxième métriques d'état précédent ( $MI_1$ ,  $MI_2$ ).

Fig 3