(11) EP 1 508 901 A1

(12)

## **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication:

23.02.2005 Bulletin 2005/08

(51) Int Cl.7: **G11C 16/22**

(21) Numéro de dépôt: 04291653.6

(22) Date de dépôt: 30.06.2004

(84) Etats contractants désignés:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IT LI LU MC NL PL PT RO SE SI SK TR Etats d'extension désignés:

AL HR LT LV MK

(30) Priorité: 18.08.2003 FR 0309987

(71) Demandeur: STMicroelectronics S.A. 92120 Montrouge (FR)

(72) Inventeur: **Devin, Jean 13100 Le Tholonet (FR)**

(74) Mandataire: Bentz, Jean-Paul CABINET BALLOT Groupe NOVAGRAAF 122, rue Edouard Vaillant 92593 Levallois Perret Cedex (FR)

## (54) Circuit mémoire à mémoire non volatile d'identification et procédé associé

- (57) L'invention a pour objet un circuit mémoire (1), comprenant :

- une zone mémoire utile (2);

- une zone mémoire non volatile de stockage (3) d'au moins un code d'identification;

- une broche de fixation d'état (4) de la zone mémoire de stockage de code d'identification;

- un registre (5) dont l'état ne peut être fixé qu'une unique fois, stockant un état indiquant si l'état de la zone mémoire de stockage de code d'identification

- a été fixé;

- un module (6) bloquant la fixation d'état de la zone mémoire de stockage de code d'identification lorsque le registre (5) indique que l'état de la zone mémoire de stockage de code d'identification a été fixé.

L'invention sert notamment à éviter la reprogrammation frauduleuse de la zone contenant le code d'identification.

L'invention porte également sur un procédé associé.

Fig. 1

### **Description**

**[0001]** L'invention concerne les circuits mémoires comprenant une zone de mémoire non volatile d'inscription de codes d'identification.

[0002] Des mémoires non volatiles présentant une zone mémoire de stockage d'un code d'identification sont connues. La zone mémoire est typiquement programmée à la fin d'un test de la mémoire pour l'identifier de façon unique ou pour mémoriser des données de fabrication. Cette zone mémoire est typiquement programmable par une broche de programmation. Le circuit de la mémoire non volatile est conçu pour ne transmettre qu'une unique commande de programmation à la zone mémoire, de sorte que le code stocké n'est normalement pas modifié.

**[0003]** Une telle mémoire et son procédé de fonctionnement présentent des inconvénients. En effet, la zone mémoire de stockage de code d'identification peut frauduleusement être reprogrammée relativement facilement.

**[0004]** Il existe donc un besoin pour un circuit mémoire ou un procédé qui résolve un ou plusieurs de ces inconvénients.

**[0005]** L'invention a ainsi pour objet un circuit mémoire, comprenant :

- une zone mémoire utile;

- une zone mémoire non volatile de stockage d'au moins un code d'identification;

- une broche de fixation d'état de la zone mémoire de stockage de code d'identification;

- un registre dont l'état ne peut être fixé qu'une unique fois, stockant un état indiquant si l'état de la zone mémoire de stockage de code d'identification a été fixé;

- un module bloquant la fixation d'état de la zone mémoire de stockage de code d'identification lorsque le registre indique que l'état de la zone mémoire de stockage de code d'identification a été fixé.

[0006] Selon une variante, la broche est une broche de programmation, le registre est programmable une unique fois, l'état du registre indique si la zone mémoire de stockage de code d'identification est programmée, le module bloque la programmation de la zone mémoire de stockage lorsque le registre indique que la zone mémoire est programmée.

**[0007]** Selon une variante, la zone mémoire utile est non volatile.

**[0008]** Selon encore une variante, la zone mémoire utile, la zone de stockage de code d'identification et le registre sont des cellules de mémoire EEPROM.

**[0009]** Selon encore une autre variante, le registre est programmable une unique fois et est constitué d'un transistor à grille flottante dont le drain et la source ne sont pas alimentés par une tension d'effacement.

[0010] Selon encore une autre variante, le registre est

programmable une unique fois et est constitué d'un transistor à grille flottante dont la grille n'est pas alimentée par une tension d'effacement.

**[0011]** On peut également prévoir que le circuit comprend en outre un circuit logique ET, dont deux entrées sont connectées respectivement au registre et à la broche de fixation d'état, et dont la sortie est connectée à une borne de fixation d'état de la zone mémoire de stockage de code d'identification.

**[0012]** L'invention a également pour objet un circuit mémoire comprenant une zone mémoire utile, une zone mémoire de stockage d'au moins un code d'identification et un registre dont l'état peut être fixé une unique fois, comprenant les étapes de:

- inscription d'un code d'identification dans la zone mémoire d'identification;

- inscription d'un marqueur d'état fixé dans le registre:

- blocage de la fixation d'état de la zone mémoire d'identification.

**[0013]** Selon une variante, le registre est programmable une unique fois, le marqueur inscrit est un marqueur d'état programmé.

**[0014]** Selon une autre variante, le procédé comprend en outre une étape de test de la zone mémoire utile préalable à l'inscription du code d'identification.

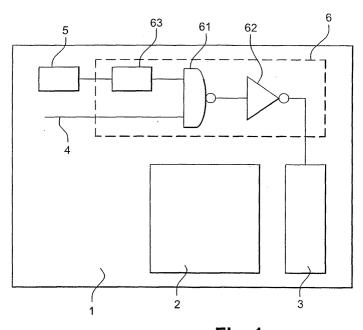

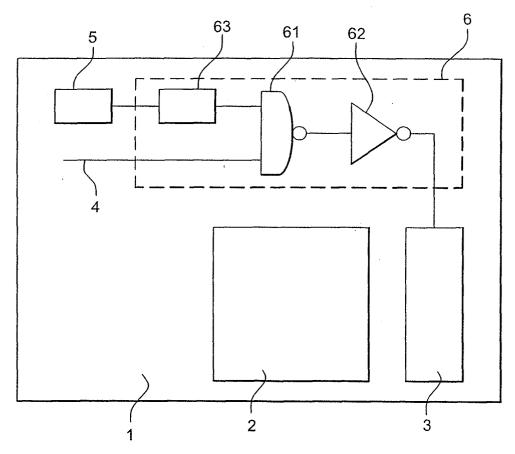

**[0015]** L'invention sera mieux comprise à partir de la figure annexée, fournie à titre d'exemple, et qui représente une représentation schématique d'un exemple de circuit mémoire selon l'invention.

**[0016]** L'invention propose d'utiliser un registre dont l'état ne peut être fixé qu'une unique fois pour mémoriser la fixation d'état de la zone mémoire de code d'identification et bloquer d'ultérieures tentatives defixation d'état.

[0017] L'invention va être décrite par la suite dans le cas le plus général de la fixation d'état. Le texte placé entre parenthèse correspond au cas particulier illustré où la fixation d'état comprend la programmation sélective de cellules mémoires. Selon une alternative, la fixation d'état utilisée peut bien entendu être un effacement sélectif de cellules mémoires.

**[0018]** La figure 1 représente schématiquement un exemple de circuit mémoire 1 selon l'invention. le circuit mémoire 1 comprend une zone mémoire utile 2 destinée au stockage des données utiles. Le circuit mémoire 1 comprend également une zone mémoire non volatile de stockage d'au moins un code d'identification 3.

**[0019]** Le code d'identification peut par exemple être un code inscrit après une étape de test du circuit mémoire 1, à la fin du processus de fabrication. Ce code d'identification peut notamment être un code identifiant de façon unique le circuit, un code identifiant les conditions de production du circuit ou un code utilisable pour des opérations de cryptage des données utiles du circuit mémoire.

50

25

40

50

**[0020]** Le circuit mémoire 1 comprend également une broche de fixation d'état 4 (en l'occurrence une broche de programmation) de la zone mémoire de stockage de code d'identification 3. Cette broche 4 est prévue pour permettre au moins une étape de fixation d'état (en l'occurrence une étape de programmation) de la zone mémoire de stockage 3.

[0021] Le circuit mémoire 1 comprend en outre un registre dont l'état ne peut être fixé qu'une unique fois 5 (programmable une unique fois), stockant un état indiquant si l'état de la zone mémoire de stockage de code d'identification 3 a été fixé (cet état indique si la zone mémoire 3 a été programmée). Le registre présente typiquement un état correspondant à une zone mémoire 3 dont l'état n'a pas été fixé (la zone mémoire 3 n'a pas été programmée) et un autre état correspondant à une zone mémoire 3 dont l'état a été fixé (la zone mémoire 3 a été programmée). Une taille de 1 bit peut ainsi être suffisante pour mémoriser si l'état de la zone mémoire 3 a été fixé.

**[0022]** Le circuit mémoire 1 comprend en outre un module 6 bloquant la fixation d'état (en l'occurrence la programmation) de la zone mémoire 3 lorsque le registre 5 indique que l'état de cette zone mémoire 3 a été fixé (en l'occurrence lorsque cette zone mémoire 3 a été programmée).

[0023] Une fois que l'état de la zone mémoire 3 a été fixé (lorsque la zone mémoire a été programmée), le registre 5 l'est également. Du fait que le l'état du registre 5 ne peut être fixé (programmé) qu'une seule fois, toute tentative de fixation d'état (programmation) ultérieure de la zone mémoire 3 est bloquée. Une tentative erronée ou frauduleuse de fixation d'état (programmation) de la zone mémoire 3 est alors efficacement évitée.

[0024] L'invention s'applique avantageusement à un circuit mémoire dans lequel la zone mémoire utile 2 est non volatile. La zone mémoire 3 protégée permet alors de certifier le contenu de la zone mémoire utile 2. La zone mémoire 2 peut notamment être constituée de mémoire EEPROM, de mémoire Flash ou de mémoire ferro-électrique.

[0025] Avantageusement, la zone mémoire utile 2, la zone mémoire de stockage 3 et le registre programmable 5 sont des cellules d'une mémoire EEPROM ou d'une mémoire Flash. Il s'avère en effet relativement aisé de réaliser ces différentes zones mémoires dans les cellules d'une unique mémoire d'un tel type. En effet, à partir de légères modifications de masques utilisés pour la réalisation de telles mémoires, on peut obtenir un circuit mémoire 1 selon l'invention.

[0026] Le registre programmable est préférablement constitué d'un transistor à grille flottante dont le drain et la source ne présentent pas les connexions permettant de recevoir des tensions d'effacement. On peut ainsi prévoir que la source et le drain soient uniquement connectés à une source de tension de programmation et de lecture. Dans l'exemple d'une mémoire Flash, on peut prévoir que le drain, le substrat et la source ne soient

pas connectés à une pompe d'extraction des électrons de la grille flottante. Le registre programmable 5 peut aussi être constitué d'un transistor à grille flottante dont la grille ne présente pas les connexions permettant de recevoir une tension d'effacement. Le transistor peut alors être programmé mais ne peut être effacé pour être reprogrammé. Pour une fixation d'état par effacement, l'homme de métier saura également prévoir des connexions adéquates du transistor à grille flottante pour empêcher sa programmation. Ces modes de réalisations sont particulièrement adaptés à la variante dans laquelle les différentes zones mémoires sont des cellules mémoire EEPROM ou Flash : de simples modifications de masques de fabrication permettent de supprimer des connexions entre une électrode d'un transistor à grille flottante et une pompe de charge. Ces modes de réalisation sont particulièrement avantageux car il est extrêmement difficile de modifier frauduleusement un tel circuit mémoire pour alimenter les électrodes des transistors et permettre le cas échéant leur programmation ou leur effacement.

**[0027]** Plus généralement, il suffit de réaliser des connexions des électrodes d'un transistor à grille flottante telles qu'il soit possible :

- soit d'ajouter mais pas de retrancher des électrons de la grille flottante;

- soit de retrancher mais pas d'ajouter des électrons dans la grille flotte.

[0028] Selon une variante préférée, le module de blocage 6 est réalisé de la façon suivante: le module 6 comprend un circuit logique ET, dont deux entrées sont connectées respectivement au registre 5 et à la broche 4. La sortie du circuit ET est connectée à une borne de programmation de la zone mémoire 3. On réduit avantageusement un circuit ET présentant un nombre de transistors réduit en plaçant en série une porte logique NON-ET 61 et un circuit NON 62, comme illustré à la figure 1.

**[0029]** Dans le circuit mémoire 1, représenté, un circuit de lecture du registre 5 est interposé entre le registre 5 et le circuit ET.

[0030] Dans l'exemple représenté, on peut prévoir que le circuit 63 fournisse un signal logique à 1 lorsque le registre 5 est vierge, ce qui correspond à une zone mémoire 3 non programmée. Ainsi, lorsqu'une requête de fixation d'état (programmation) est appliquée sur la broche 4, elle est validée par le circuit ET. Après la fixation d'état (programmation) de la zone mémoire 3, l'état du registre 5 a également été fixé (le registre est programmé). Le circuit 63 fournit alors un signal logique à 0. Ainsi, lorsqu'une requête fixation d'état (programmation) est appliquée sur la broche 4, elle est invalidée par le circuit ET.

**[0031]** Le procédé d'utilisation du circuit mémoire 1 peut ainsi être le suivant:

[0032] On inscrit un code d'identification dans la zone

15

20

25

35

40

45

mémoire d'identification, puis on inscrit un marqueur d'état fixé (programmé) dans le registre 4, puis on bloque la fixation d'état (programmation) de la zone mémoire d'identification.

**[0033]** L'inscription du code d'identification peut être précédée d'une étape de test de la zone mémoire utile, par exemple à la fin du processus de fabrication de la mémoire. Le code d'identification peut alors contenir des données provenant du résultat des tests.

**[0034]** L'invention n'est bien entendu pas limitée aux exemples et modes de réalisation décrits et représentés, mais est susceptible de nombreuses variantes accessibles à l'homme de l'art.

#### Revendications

- 1. Circuit mémoire (1), comprenant :

- une zone mémoire utile (2);

- une zone mémoire non volatile de stockage (3) d'au moins un code d'identification;

- une broche de fixation d'état (4) de la zone mémoire de stockage de code d'identification;

- caractérisé en ce qu'il comprend en outre :

- un registre (5) dont l'état ne peut être fixé qu'une unique fois, stockant un état indiquant si l'état de la zone mémoire de stockage de code d'identification a été fixé;

- un module (6) bloquant la fixation d'état de la zone mémoire de stockage de code d'identification lorsque le registre (5) indique que l'état de la zone mémoire de stockage de code d'identification a été fixé.

- Circuit selon la revendication 1, caractérisé en ce que :

- la broche (4) est une broche de programmation;

- le registre (5) est programmable une unique fois;

- l'état du registre indique si la zone mémoire de stockage de code d'identification est programmée;

- le module bloque la programmation de la zone mémoire de stockage lorsque le registre indique que la zone mémoire est programmée.

- 3. Circuit selon la revendication 1 ou 2, caractérisé en ce que la zone mémoire utile (2) est non volatile.

- 4. Circuit selon la revendication 3, caractérisé en ce que la zone mémoire utile (2), la zone de stockage de code d'identification (3) et le registre (5) sont des cellules de mémoire EEPROM.

- 5. Circuit selon l'une quelconque des revendications

précédentes, **caractérisé en ce que** le registre (5) est programmable une unique fois et est constitué d'un transistor à grille flottante dont le drain et la source ne sont pas alimentés par une tension d'effacement.

- 6. Circuit selon l'une quelconque des revendications 1 à 4, caractérisé en ce que le registre (5) est programmable une unique fois et est constitué d'un transistor à grille flottante dont la grille n'est pas alimentée par une tension d'effacement.

- 7. Circuit selon l'une quelconque des revendications précédentes, caractérisé en ce qu'il comprend en outre un circuit logique ET (61), dont deux entrées sont connectées respectivement au registre et à la broche de fixation d'état, et dont la sortie est connectée à une borne de fixation d'état de la zone mémoire de stockage de code d'identification (3).

- 8. Procédé d'utilisation d'un circuit mémoire (1) comprenant une zone mémoire utile (2), une zone mémoire de stockage (3) d'au moins un code d'identification et un registre dont l'état peut être fixé une unique fois, comprenant les étapes de:

- inscription d'un code d'identification dans la zone mémoire d'identification;

- inscription d'un marqueur d'état fixé dans le registre;

- blocage de la fixation d'état de la zone mémoire d'identification.

- 9. Procédé selon la revendication 8, caractérisé en ce que :

- le registre (5) est programmable une unique fois:

- le marqueur inscrit est un marqueur d'état programmé;

- 10. Procédé selon la revendication 8 ou 9, caractérisé en ce qu'il comprend en outre une étape de test de la zone mémoire utile préalable à l'inscription du code d'identification.

4

Fig. 1

# RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande EP 04 29 1653

| Revendication concernée  1-4,7  10  1-4,8,9  10  1-6,8,9 | DOMAINES TECHNIQUES RECHERCHES (Int.Cl.7) G11C |

|----------------------------------------------------------|------------------------------------------------|

| 10<br>1-4,8,9<br>10                                      | DOMAINES TECHNIQUES<br>RECHERCHES (Int.Cl.7)   |

| 1-4,8,9                                                  | RECHERCHES (Int.Cl.7)                          |

| 10                                                       | RECHERCHES (Int.Cl.7)                          |

|                                                          | RECHERCHES (Int.Cl.7)                          |

| 1-6,8,9                                                  | RECHERCHES (Int.Cl.7)                          |

|                                                          | RECHERCHES (Int.Cl.7)                          |

|                                                          | RECHERCHES (Int.Cl.7)                          |

|                                                          | G11C                                           |

|                                                          |                                                |

|                                                          | i .                                            |

|                                                          |                                                |

|                                                          |                                                |

|                                                          |                                                |

|                                                          |                                                |

|                                                          |                                                |

|                                                          |                                                |

|                                                          |                                                |

|                                                          |                                                |

| ll and                                                   | Examinateur                                    |

|                                                          | rms, J                                         |

|                                                          | vention<br>is publié à la                      |

| 4                                                        | à la base de l'ir                              |

EPO FORM 1503 03.82 (P04C02)

# ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

EP 04 29 1653

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Lesdits members sont contenus au fichier informatique de l'Office européen des brevets à la date du

Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

05-08-2004

| DE 4340027 A | 03-09-1996<br>01-06-1995<br>10-10-2001 | AUCUN  DE 4340027 A1  JP 2001283594 A  EP 1143455 A2  TW 497103 B  US 2001036105 A1 | 01-06-199<br>12-10-200<br>10-10-200<br>01-08-200<br>01-11-200 |

|--------------|----------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------|

|              |                                        | JP 2001283594 A<br>EP 1143455 A2<br>TW 497103 B                                     | 12-10-200<br>10-10-200<br>01-08-200                           |

| EP 1143455 A | 10-10-2001                             | EP 1143455 A2<br>TW 497103 B                                                        | 10-10-200<br>01-08-200                                        |

|              |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

| ,            |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

|              |                                        |                                                                                     |                                                               |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82

EPO FORM P0460