(11) EP 1 656 001 A1

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

10.05.2006 Bulletin 2006/19

(51) Int Cl.:

H05B 33/08<sup>(2006.01)</sup> H05B 37/02<sup>(2006.01)</sup> F21V 23/04 (2006.01)

(21) Application number: 04026001.0

(22) Date of filing: 03.11.2004

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LU MC NL PL PT RO SE SI SK TR Designated Extension States:

AL HR LT LV MK YU

(71) Applicant: High Tech Computer Corp.

Taoyuan City,

Taoyuan Hsien (TW)

(72) Inventors:

Tsai, Jung-Yuan

Taoyuan City

Taoyuan Hsien (TW)

Chen, Kuo-Feng Taoyuan City Taoyuan Hsien (TW)

Chien, Chung-An Taoyuan City Taoyuan Hsien (TW)

Chen, Wei-Shao Taoyuan City Taoyuan Hsien (TW)

(74) Representative: Schwabe - Sandmair - Marx Stuntzstrasse 16 81677 München (DE)

Remarks:

Amended claims in accordance with Rule 86 (2) EPC.

## (54) Flashing lights control apparatus and method thereof

(57) The present invention describes a flashing light apparatus and method for operating the same. A pulse signal generated by a pulse signal generator (202) and

the states of the general purpose Input/Output pins (306,308,310) of a CPU (200) are used to control the lights (324,326,328) to flash.

FIG. 2

EP 1 656 001 A1

20

25

30

45

#### Field of the Invention

**[0001]** The present invention relates to a light control method, specifically relates to a flashing light control method and apparatus thereof.

1

#### **Background of the Invention**

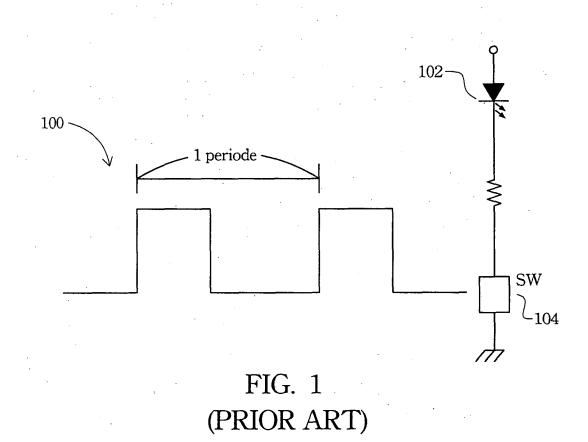

**[0002]** In electrical products, it is necessary to use different flashing lights to represent different operation situations. In figure 1, a low pulse signal 100 controls a switching device 104 that makes a light emitting diode 102 flash.

**[0003]** Typically, there are two methods of generating the low pulse signal 100. One is to use a program to control a counter in a CPU to output the pulse signals from the general purpose input/output pins. The pulse signals make the switching devices switch the light emitting diodes on/off. However, the CPU has to keep working in this method, which increase the power consumption of the electrical products. Additionally, the working efficiency of the CPU is reduced because the partial calculation period is used to generate the pulse signals.

**[0004]** Another method is to use an oscillation circuit to generate pulse signals with a fixed period to make the switching device switch the light emitting diodes on/off. However, an additional oscillation circuit is required in this method, which increase the cost and the volume of the electrical products. Moreover, the oscillation circuit can only generate a pulse signal with a fixed period. Therefore, the flashing period is also fixed, which limits the application range thereof.

[0005] A pulse signal generator inside a CPU is typically used to resolve the problem of fixed period resulting from use of the oscillation circuit. This pulse signal generator is used to provide a pulse signal whose period is modulated by the CPU. However, although this method can resolve the fixed period problem, a pulse signal generator can only provide a pulse signal. In other words, the number of flashing lights is related to the number of pulse signal generators inside a CPU. If the number of pulse signal generators built in a CPU is not enough, an additional pulse signal generator must be attached to the CPU, which increase the manufacturing cost and the volume of a electrical product.

## **Summary of the Invention**

**[0006]** Therefore, the main purpose of the present invention is to provide a flashing light control method and apparatus thereof to make many lights flash but not increase the power consumption and volume of a electrical product.

**[0007]** Another purpose of the present invention is to provide a flashing light control method and apparatus thereof by using a pulse signal generator to make many

lights flash.

**[0008]** A further purpose of the present invention is to provide a flashing light control method and apparatus thereof to control the flashing light period without reducing CPU efficiency.

**[0009]** Accordingly, the states of the general purpose Input/Output pins of a CPU can determine whether or not a light is triggered by a pulse signal generated by a pulse signal generator. The method not only can use a pulse signal generator built in a CPU but also can use a pulse signal generator independent from a CPU.

#### **Brief Description of the Drawings**

**[0010]** The foregoing aspects and many of the attendant advantages of this invention will become more readily appreciated and better understood by referencing the following detailed description, when taken in conjunction with the accompanying drawings, wherein:

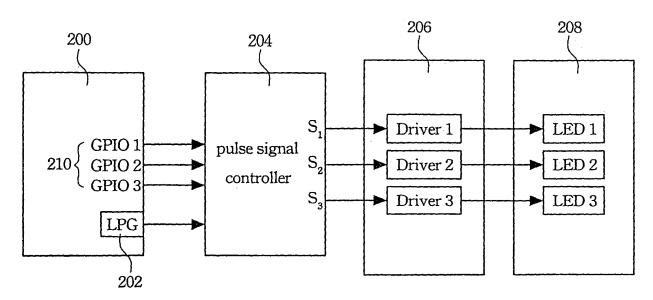

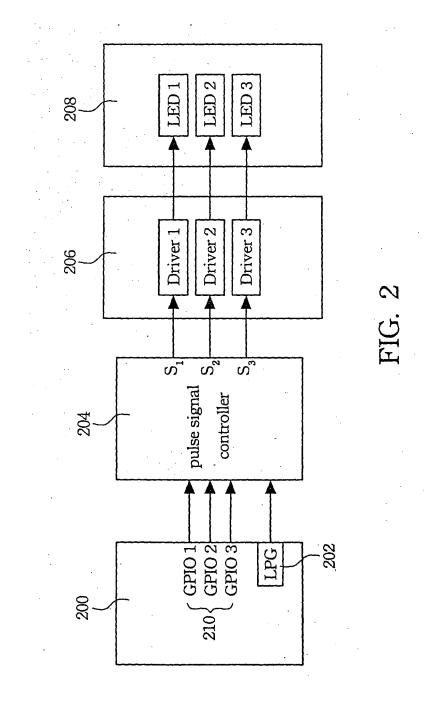

Figure 1 is a typical pulse signal for flashing lights; Figure 2 is a block diagram of a control circuit according to the first embodiment;

Figure 3 is a control circuit diagram according to the block diagram illustrated in figure 2;

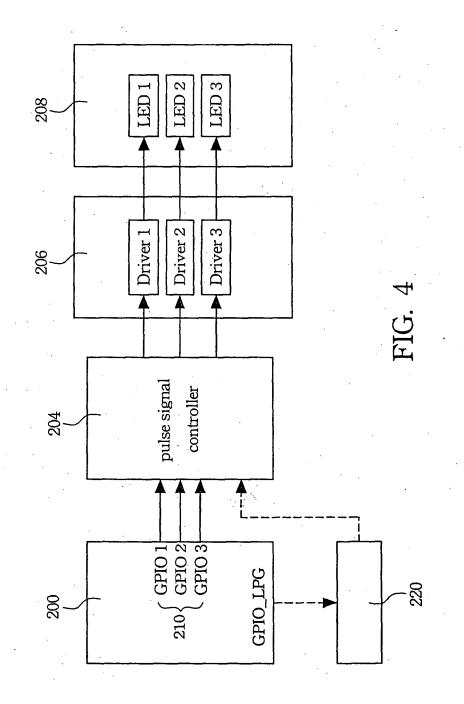

Figure 4 is a block diagram of a control circuit according to the second embodiment;

Figure 5 is a control conditions table for making lights flash; and

Figure 6 is a control conditions table for keeping lights on or off.

#### **Detailed Description of the Preferred Embodiment**

[0011] Figure 2 is a block diagram of a control circuit according to the first embodiment. According to the first embodiment, a CPU 200 with a low pulse generator (LPG) 202 makes lights flash by controling the states of the general purpose Input/Output (GPIO) pins 210 and thereby selecting which light flahses. The pulse signal generated by the low pulse generator 202 makes the selected light flash. A pulse signal controller 204 triggers a specific driving circuit in the driving circuitdriving circuit module 206 according to the states of the general purpose Input/Output (GPIO) pins 210 of the CPU 200. Then, the pulse signal received by the pulse signal controller 204 can make a specific light in the light module 208 flash through the triggered driving circuit. The light module is composed of light emitting diodes respectively connected to corresponding driving circuits.

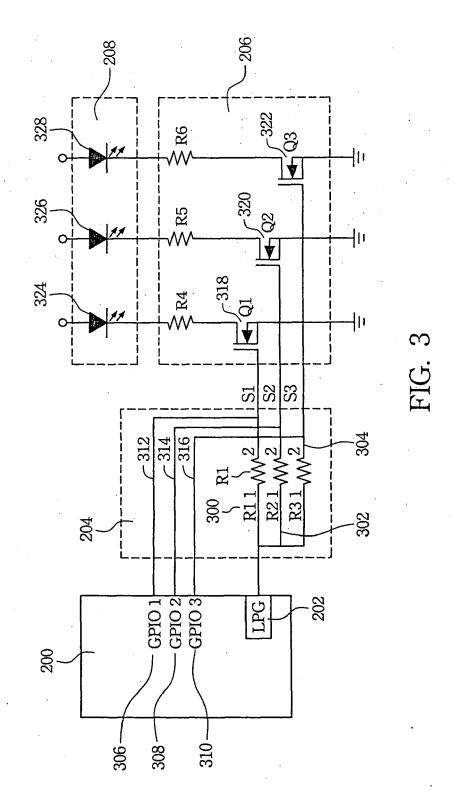

[0012] Figure 3 is a control circuit diagram according to the block diagram illustrated in the figure 2. Reference is made to figure 2 and figure 3. A low pulse generator (LPG) 202 is built in a CPU 200. According to the embodiment, the conductive line 300, 302 and 304 connected with the low pulse generator 202 and the conductive lines 312, 314 and 316 connected with the CPU 200 are respectively connected together to form three intersec-

20

40

tions that serve as the three output points  $S_1$ ,  $S_2$  and  $S_3$  of the pulse signal controller 204.

[0013] When the state of a general purpose Input/Output pin 210 is set in an Input mode, this pin has a "high" input impedance. When the state of a general purpose Input/Output pin 210 is set in an output mode, this pin is grounded. For example, when the general purpose Input/ Output pin 306 is set in an Input mode, this pin has a "high" input impedance. Therefore, the output signal of the output point S<sub>1</sub> of the pulse signal controller 204 is the pulse signal transmitted by the conductive line 300. Conversely, when the general purpose Input/Output pin 306 is set in an output mode, this pin is grounded. The output point S<sub>1</sub> of the pulse signal controller 204 is also grounded. Therefore, the pulse signal transmitted by the conductive line 300 is reduced to a "zero" level state through the resistance R1. In other words, the output signals of the three output points  $S_1$ ,  $S_2$  and  $S_3$  can be determined by controlling the states of the corresponding general purpose Input/Output pins.

[0014] There are three switching devices 318, 320 and 322 in the driving circuit module 206. The three switching devices 318, 320 and 322 are transistors. These switching devices 318, 320 and 322 are respectively controlled by the three output points S<sub>1</sub>, S<sub>2</sub> and S<sub>3</sub>. For example, when the output point S<sub>1</sub> is grounded because the corresponding GPIO pin 306 is set in an output mode, the switching device 318 is in an "off' state because the pulse signal transmitted by the conductive line 300 is reduced to a "zero" level state through the resistance R1. Conversely, when the corresponding GPIO pin 306 is set in an "input" mode, this pin has a "high" input impedance. Through the conductive line 312, this "high" input impedance makes the output point S<sub>1</sub> output the pulse signal transmitted by the conductive line 300 to switch the switching device 318. At this time, the corresponding light emitting diode 324 in the light module 208 flashes according to the switching of the switching device 318.

**[0015]** When both the GPIO pins 308 and 310 are set in the input mode and the GPIO pin 306 is set in the output mode, the output point  $S_1$  is grounded to turn of the switching device 318, and the output points  $S_2$  and  $S_3$  respectively output the pulse signal transmitted from the conductive lines 302 and 302 to switch the switching devices 320 and 322. At this time, the light emitting diode 324 is turned off because the switching device is in an "off" state. The light emitting diodes 326 and 328 flash according to the switching of the switching devices 320 and 322.

**[0016]** On the other hand, the light emitting diodes can be kept on in the present invention. In such situation, the LPG 202 is turned off to stop providing the pulse signal. Therefore, the three output points  $S_1$ ,  $S_2$  and  $S_3$  of the pulse signal controller 204 are only controlled by the GPIO pins. For example, when the GPIO pin 306 outputs a "high" level such that the output point  $S_1$  is also in a "high" level, the switching device 318 is kept in an "on" state, thereby making the LED 324 continuously on.

**[0017]** Figure 4 is a block diagram of a control circuit according to the second embodiment. The main difference between the first and second embodiment is that an independent LPG 220 controlled by a GPIO pin of the CPU 200 is used in the second embodiment to generate the pulse signal. However, the operation method of the first and second embodiment is the same.

[0018] Figure 5 is a control conditions table for making light emitting diodes (LEDs) flash. Reference is made to figure 3 and figure 5 together. For example, the situation described in number 3 is that the LED 328 flashes and the LEDs 324 and 326 are off. In such situation, the GPIO pin 310 is set in the input mode and the GPIO pins 306 and 308 are set in the output mode. According to the setting of the pins, the output point S<sub>1</sub> and S<sub>2</sub> are grounded. Therefore, the switching devices 318 and 320 are turned off. The LED 324 and 326 are turned off. The output point S<sub>3</sub> outputs the pulse signal transmitted by the conductive line 304 to switch the switching device 322. The LED 328 flahs according to the switch of the switching device 322. On the other hand, the situation described in number 8 is that the LEDs 324, 326 and 328 are all turned off. In such situation, all of the GPIO pins 306, 308 and 310 of the CPU 200 are set in the output mode. It is noted that the control condictions described in figure 5 also can be used in the circuit structure illustrated in figure 4.

[0019] The present invention also can maintain the light emitting diodes in on/off states. Figure 6 illustrates a control conditions table. For example, the situation described in number 13 is that the LEDs 326 and 328 are continually on and the LEDs 324 is off. In this situation, the LPG 202 is turned off to stop the flashing function. The GPIO pins 308 and 310 are set in the output mode with a high level and the GPIO pin 306 is set in the output mode with a low level. According to the setting of the pins, the output point S<sub>1</sub> is grounded to turn off the switching device 318. Therefore, the LED 324 is turned off. The output points S2 and S3 output the high level signal to turn on the switching devices 320 and 322. Therefore, the LEDs 326 and 328 are continually turned on. On the other hand, the situation described in number 16 is that the LEDs 324, 326 and 328 are all turned off. In this situation, all GPIO pins 306, 308 and 310 of the CPU 200 are set in the output mode with a low level. It is noted that the control conditions described in the figure 6 also can be used in the circuit structure illustrated in the figure 4.

[0020] Accordingly, the states of the general purpose Input/Output pins of a CPU are used to make a pulse signal controller generate an output signal. This output signal selects a specific driving circuit. A pulse signal generated by a pulse signal generator triggers this selected driving circuit, which then makes the corresponding light flash. The pulse signal generator not only can be a pulse signal generator built in a CPU but also can be a pulse signal generator located outside a CPU and controlled by a GPIO pin of a CPU.

15

20

25

30

35

40

45

[0021] As is understood by a person skilled in the art, the foregoing descriptions of the preferred embodiment of the present invention are an illustration of the present invention rather than a limitation thereof. Various modifications and similar arrangements are included within the spirit and scope of the appended claims. The scope of the claims should be accorded to the broadest interpretation so as to encompass all such modifications and similar structures. While a preferred embodiment of the invention has been illustrated and described, it will be appreciated that various changes can be made therein without departing from the spirit and scope of the invention.

**Claims**

1. A flashing light control apparatus, comprising:

a central processing unit with a plurality of general purpose input/output pins, wherein each pin has a specific impedance state; a pulse signal generator connecting to said central processing unit for generating a pulse signal; a driving circuit module with a plurality of driving circuit, wherein said driving circuit module is connected to said pulse signal generator; and a light module with a plurality of lights respectively connected to said driving circuits, wherein said pulse signal triggers said driving circuits to turn on corresponding lights according to said impedance states of said pins.

- **2.** The apparatus of claim 1, wherein said driving circuits comprises transistors.

- 3. A flashing light control apparatus, comprising:

eral purpose input/output pins and a pulse signal pin, wherein each of said general purpose input/output pins has a specific impedance state and said pulse signal pin outputs a pulse signal; a pulse signal generator connecting to said general purpose input/output pins and said pulse signal pin; a driving circuit module with a plurality of driving circuits, wherein said driving circuit module is connected to said pulse signal generator; and a light module with a plurality of lights respectively connected to said driving circuits, wherein said pulse signal triggers said driving circuits to turn on corresponding lights according to said impedance states of said pins.

a central processing unit with a plurality of gen-

**4.** The apparatus of claim 3, wherein said driving circuits comprise transistors.

5. A flashing light control method for a system, wherein said system comprises a central processing unit with a plurality of general purpose input/output pins, a pulse signal pin and a plurality of lights, comprising:

> setting the states of said general purpose input/ output pins; and sending pulse signals to trigger lights.

#### Amended claims in accordance with Rule 86(2) EPC.

1. A flashing light control apparatus, comprising:

a central processing unit (200) with a plurality of general purpose input/output pins (201), wherein each pin has a specific state; a pulse signal generator connecting to said central processing unit for generating a pulse signal; a pulse signal control unit (204) connecting to said general purpose input/output pins (210) and said pulse signal generator, said pulse signal control unit has a plurality of output ends (S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>) controlled by said general purpose input/ output pins (210) respectively, wherein said pins (210) control said output ends (S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>) to output the special states of pins or said pulse a driving circuit module (206) with a plurality of driving circuit respectively connected to corresponding said output ends  $(S_1, S_2, S_3)$ ; and a light module (208) with a plurality of lights respectively connected to said driving circuits, wherein said pulse signal triggers said driving

- circuits to turn on corresponding lights according to said states of said pins (210).

2. The apparatus of claim 1, wherein said driving circuit comprises a transistor (318, 320, 322) con-

- 3. The apparatus of claim 1, wherein said special state is an Input mode with high impedance, an output mode with a low voltage level or an output mode with a high voltage level.

trolled by said corresponding output end  $(S_1, S_2, S_3)$ .

55

| No | LED R | LED G | LED B | LPG | GPIO 1     | GPIO 2     | GPIO 3     |

|----|-------|-------|-------|-----|------------|------------|------------|

| 1  | Flash | OFF   | OFF   | ON  | Input      | Output (L) | Output (L) |

| 2  | OFF   | Flash | OFF   | ON  | Output (L) | Input      | Output (L) |

| 3  | OFF   | OFF   | Flash | ON  | Output (L) | Output (L) | Input      |

| 4  | Flash | Flash | OFF   | ON  | Input      | Input      | Output (L) |

| 5  | OFF   | Flash | Flash | ON  | Output (L) | Input      | Input      |

| 6  | Flash | OFF   | Flash | ON  | Input      | Output (L) | Input      |

| .7 | Flash | Flash | Flash | ON  | Input      | Input      | Input      |

| 8  | OFF   | OFF   | OFF   | OFF | Output (L) | Output (L) | Output (L) |

FIG. 5

| No | LED R | LED G | LED B | LPG | GPIO 1     | GPIO 2     | GPIO 3     |

|----|-------|-------|-------|-----|------------|------------|------------|

| 9  | ON    | OFF   | OFF   | OFF | Output (H) | Output (L) | Output (L) |

| 10 | OFF   | ON    | OFF   | OFF | Output (L) | Output (H) | Output (L) |

| 11 | OFF   | OFF   | ON    | OFF | Output (L) | Output (L) | Output (H) |

| 12 | ON    | ON    | OFF   | OFF | Output (H) | Output (H) | Output (L) |

| 13 | OFF   | ON    | ON    | OFF | Output (L) | Output (H) | Output (H) |

| 14 | ON    | OFF   | ON    | OFF | Output (H) | Output (L) | Output (H) |

| 15 | ON    | ON    | ON    | OFF | Output (H) | Output (H) | Output (H) |

| 16 | OFF   | OFF   | OFF   | OFF | Output (L) | Output (L) | Output (L) |

FIG. 6

# **EUROPEAN SEARCH REPORT**

Application Number EP 04 02 6001

|                                                                                                                                                                                                                      |                                                                                                                                                       | ERED TO BE RELEVANT                                                                                              | Relevant                                                                                                                                                                                                                                                                          | CLASSIEICATION OF THE                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| Category                                                                                                                                                                                                             | ategory Citation of document with indication, where appropriate, of relevant passages                                                                 |                                                                                                                  |                                                                                                                                                                                                                                                                                   | CLASSIFICATION OF THE APPLICATION (Int.CI.7) |  |

| X                                                                                                                                                                                                                    | US 2003/174496 A1 (<br>18 September 2003 (<br>* page 4, paragraph<br>52; figure 6 *                                                                   | 1-5                                                                                                              | H05B33/08<br>F21V23/04<br>H05B37/02                                                                                                                                                                                                                                               |                                              |  |

| X                                                                                                                                                                                                                    | US 5 969 479 A (WON<br>19 October 1999 (19<br>* column 3, line 39<br>figures 3,5,6 *                                                                  |                                                                                                                  | 1-5                                                                                                                                                                                                                                                                               |                                              |  |

| А                                                                                                                                                                                                                    | BOOGAARDS: "AN264<br>DISPLAY CONTROL"<br>PHILIPS SEMICONDUCT<br>[Online] 22 July 20<br>1-27, XP002319313<br>Retrieved from the<br>URL:http://www.semi | conductors.philips.com/plicationnotes/AN264.pd 05-02-24]                                                         | 1-5                                                                                                                                                                                                                                                                               | TECHNICAL FIELDS<br>SEARCHED (Int.Cl.7)      |  |

| А                                                                                                                                                                                                                    | US 5 903 103 A (GAR<br>11 May 1999 (1999-6<br>* column 8, line 13<br>figure 6A *                                                                      |                                                                                                                  | 1-5                                                                                                                                                                                                                                                                               | H05B<br>F21V                                 |  |

|                                                                                                                                                                                                                      | The prepart agareh report has l                                                                                                                       | poon drawn up for all alaima                                                                                     |                                                                                                                                                                                                                                                                                   |                                              |  |

|                                                                                                                                                                                                                      | The present search report has be a place of search                                                                                                    | Date of completion of the search                                                                                 |                                                                                                                                                                                                                                                                                   | Examiner                                     |  |

|                                                                                                                                                                                                                      |                                                                                                                                                       | 25 February 2005                                                                                                 | Dv                                                                                                                                                                                                                                                                                |                                              |  |

| Munich 2  CATEGORY OF CITED DOCUMENTS  X: particularly relevant if taken alone Y: particularly relevant if combined with another document of the same category A: technological background O: non-written disclosure |                                                                                                                                                       | T : theory or principle E : earlier patent doc after the filing date D : document cited in L : document cited fo | February 2005  Burchielli, M  T: theory or principle underlying the invention E: earlier patent document, but published on, or after the filing date D: document cited in the application L: document cited for other reasons  &: member of the same patent family, corresponding |                                              |  |

EPO FORM 1503 03.82 (P04C01)

### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 04 02 6001

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

25-02-2005

| Patent document<br>cited in search report |    | Publication date |                      | Patent family<br>member(s)               |          | Publication date                             |

|-------------------------------------------|----|------------------|----------------------|------------------------------------------|----------|----------------------------------------------|

| US 2003174496                             | A1 | 18-09-2003       | AU<br>WO             | 2003209567<br>03078178                   |          | 29-09-20<br>25-09-20                         |

| US 5969479                                | Α  | 19-10-1999       | US                   | 5894201                                  | Α        | 13-04-19                                     |

| US 5903103                                | A  | 11-05-1999       | AU<br>CA<br>EP<br>WO | 6698898<br>2294073<br>0999762<br>9839983 | A1<br>A2 | 29-09-19<br>17-09-19<br>17-05-20<br>17-09-19 |

|                                           |    |                  |                      |                                          |          |                                              |

|                                           |    |                  |                      |                                          |          |                                              |

FORM P0459

$\stackrel{\circ}{\mathbb{L}}$  For more details about this annex : see Official Journal of the European Patent Office, No. 12/82