(11) EP 1 662 663 A1

(12)

#### **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

31.05.2006 Bulletin 2006/22

(51) Int Cl.:

H03L 7/095 (2006.01)

(21) Application number: 05025229.5

(22) Date of filing: 18.11.2005

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI SK TR

**Designated Extension States:**

AL BA HR MK YU

(30) Priority: 30.11.2004 JP 2004346660

(71) Applicant: NEC Electronics Corporation Kawasaki, Kanagawa 211-8668 (JP)

(72) Inventors:

Kaneko, Makoto, c/o NEC Electronics Corp. Kawasaki, Kanagawa 211-8668 (JP)

Nakamura, Satoshi, c/o NEC Electronics Corp. Kawasaki,

Kanagawa 211-8668 (JP)

(74) Representative: Glawe, Delfs, Moll

Patentanwälte Postfach 26 01 62 80058 München (DE)

#### (54) PLL circuit

(57) Disclosed is a PLL circuit including a deadlock detection circuit (20) includes a counter circuit (22) for counting a clock signal. In a deadlock state, the deadlock detection circuit (20) outputs a deadlock detection signal responsive to an output signal (TRIG) from the counter

circuit (22) when the counter circuit (22) has counted a preset number of the clock signal. The deadlock detection signal serves to release the PLL circuit from the dead lock. During the normal operation, the counter circuit (22) does not impart noise to the PLL circuit.

### FIG. 2

20

#### FIELD OF THE INVENTION

[0001] This invention relates to a PLL circuit and, more particularly, to a PLL circuit having a deadlock removing circuit.

1

#### BACKGROUND OF THE INVENTION

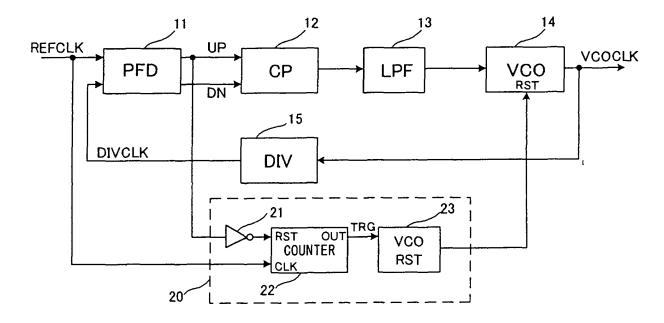

[0002] Fig.1 shows an illustrative configuration of a conventional PLL (Phase Locked Loop) circuit disclosed in Patent Publication 1. This conventional PLL circuit, shown in Fig.1, includes a phase frequency detector (PFD) 11, a charge pump circuit (CP) 12, a low-pass filter (LPF) 13, a voltage-controlled oscillator (VCO) 14, and a divider circuit (DIV) 15. The phase frequency detector 11 compares the phase of rising of a reference clock signal (REFCLK) with that of a divided clock signal (DI-VCLK), output from the divider circuit 15 and, if the divided clock signal lags or leads the reference clock signal, the phase frequency detector 11 outputs an up (UP) signal or a down (DN) signal, each being of a pulse width corresponding to the phase difference, respectively.

[0003] The charge pump circuit 12 receives UP and DN signals output from the phase frequency detector 11 and causes the current having a value corresponding to the pulse width of the UP signal to flow from a power supply to an output terminal thereof, thereby charging the output terminal, while causing the current having a value corresponding to the pulse width of the DN signal to flow from the output terminal to the ground, thereby discharging the output terminal. The charge pump circuit 12 outputs from the output terminal thereof an error signal corresponding to the phase/frequency difference detected by the phase frequency detector 11. The low-pass filter 13 receives the error signal output from the charge pump circuit 12 and generates a control voltage which is obtained by smoothing the error signal. The voltage-controlled oscillator 14 receives the control voltage output from the low-pass filter 13 and generates an output clock signal, the frequency of which is subjected to change to a higher value or to a lower value depending on a higher or lower value of the control voltage, respectively. The divider circuit 15 receives the output clock signal (VCO-CLK) output from the voltage-controlled oscillator 14 and divides the output clock signal (VCOCLK) by a preset frequency division ratio to output the divided clock signal (DIVCLK). In this manner, the PLL circuit performs feedback control so that the reference clock signal (REFCLK) and the divided clock signal (DIVCLK) becomes coincident in phase and frequency with each other and hence the frequency of the output clock signal (VCOCLK) of the voltage-controlled oscillator 14 becomes a preset multiple of the frequency of the reference clock signal (REF-CLK).

[0004] In unstable states, such as on power up, the oscillation frequency of the voltage-controlled oscillator 14 may become unusually high to exceed the limit of the toggle frequency of the divider circuit 15. In case the frequency of the output clock signal (VCOCLK) fed to the divider circuit 15 exceeds the maximum toggle frequency of the divider circuit 15, the divider circuit 15 continues to output a fixed level, as a result of which the phase frequency detector 11 continues to output the UP signal. This leads to a deadlock state in which the PLL circuit is unable to act as a negative feedback loop. In order to take a measure to meet the situation, the PLL circuit shown in Fig.1 includes a deadlock detection circuit made up by a power-on reset circuit 25, a flip-flop 26, and an NMOS transistor 3. This deadlock detection circuit operates as follows:

First, until such time that the power supply voltage on power up reaches a preset value, an output signal of the power-on reset circuit 25 is activated to reset the divider circuit 15 as well as to set the flip-flop 26. An output of the flip-flop 26 turns the transistor 3 on to discharge an output of the low-pass filter 13.

[0005] Consequently, the voltage-controlled oscillator 14 oscillates at a low frequency without oscillating at an unusually high frequency. When the power supply voltage then reaches a preset value, an output signal of the power-on reset circuit 25 is inactivated to release the reset state of the divider circuit 15. The divider circuit 15 divides the frequency of the output of the voltage-controlled oscillator 14 to output the divided clock signal (DI-VCLK). By the divided clock signal, the flip-flop 15 is reset to turn off the NMOS transistor 3. As from this time, the PLL circuit commences its normal operation.

#### [Patent Document 1]

[0006] JP Patent Kokai Publication No. JP-A-11-103249

#### SUMMARY OF THE DISCLOSURE

[0007] With the above-described conventional PLL circuit, it is possible to prevent the circuit from falling into a deadlock state in an unstable state prevailing at the time of power up. However, if, in the course of subsequent operation, the oscillation frequency of the voltage controlled oscillator becomes unusually high by some reason or other, or the oscillation of the voltage controlled oscillator is halted, such that the PLL circuit has fallen into a deadlock state, the PLL circuit cannot be restored to its normal state except if the power-on resetting circuit is again set into operation. It is therefore desirable that, when the PLL circuit has fallen into a deadlock state, the deadlock state can be automatically detected such that the PLL circuit can be automatically reverted to its normal operation.

[0008] In view of the above depicted status of the art, the present invention provides a PLL circuit comprising

20

40

a phase frequency detector for comparing the phase or the frequency of a reference clock signal with the phase or the frequency of a divided clock signal to output an UP signal or a DN signal depending on whether the phase of the divided clock signal leads or lags the phase of the reference clock signal, respectively, or on whether the frequency of the divided clock signal is lower or higher than the frequency of the reference clock signal, respectively, a charge pump circuit for causing current to flow out to an output thereof and to flow in from the output thereof, responsive to the UP signal and to the DN signal, respectively, for generating an error signal associated with phase or frequency difference detected by said phase frequency detector, a low-pass filter for smoothing the error signal to output a control voltage, a voltage controlled oscillator for generating an output clock signal, the frequency of which is changed to a higher or lower value depending on the higher or lower value of the control voltage, a divider circuit for dividing the frequency of the output clock signal by a preset frequency division ratio to output the divided clock signal, and a deadlock detection circuit for detecting a deadlock state of the PLL circuit to output a deadlock detection signal. The deadlock detection circuit includes a counter circuit for counting a clock signal. The deadlock detection circuit outputs the deadlock detection signal responsive to a signal output when the counter circuit has counted a preset number of the clock signal in the deadlock state. The deadlock state is removed by the deadlock detection signal.

**[0009]** According to the present invention, a deadlock detection signal is output responsive to an output signal output when a preset number of clocks has been counted in a deadlock state by a counter circuit, and the deadlock state is removed by the deadlock detection signal, as a result of which, the deadlock state can be detected reliably to render it possible to release the PLL circuit automatically from the deadlock.

**[0010]** The meritorious effects of the present invention are summarized as follows.

The present invention provides a PLL circuit including a deadlock detection circuit enabling the PLL circuit to be freed automatically from the deadlock and which does not operate as a noise source otherwise affecting the PLL circuit during the normal operation.

#### BRIEF DESCRIPTION OF THE DRAWINGS

#### [0011]

Fig.1 is a diagram showing the configuration of a conventional PLL circuit.

Fig. 2 is a diagram showing the configuration of a PLL circuit of the first embodiment of the present invention.

Figs.3A, 3B, 3C and 3D are timing charts showing the operation of the PLL circuit.

Fig.4 is a diagram showing the configuration of a counter circuit in the PLL circuit of the present inven-

tion.

Fig.5 is a diagram showing the configuration of a VCO resetting circuit in the PLL circuit of the present invention.

Fig.6 is a timing chart at the time of deadlock in the PLL circuit of the present invention.

Fig.7 is a diagram showing the configuration of a deadlock detection circuit of a second embodiment of the present invention.

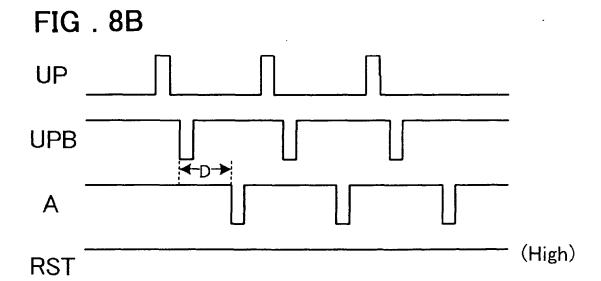

Figs.8A and 8B are diagrams showing the configurations and the operations of a pulse cutting circuit in the second embodiment of the present invention.

#### PREFERRED EMBODIMENTS OF THE INVENTION

**[0012]** Referring to the drawings, preferred embodiments of the PLL circuit of the present invention will be described in detail.

#### [First Embodiment]

**[0013]** Fig.2 is a block diagram showing the configuration of a PLL circuit according to an embodiment of the present invention. Referring to Fig.2, the PLL circuit according to the present embodiment comprises a phase frequency detector (PFD) 11, a charge pump circuit (CP) 12, a low-pass filter (LPF) 13, a voltage-controlled oscillator (VCO) 14, a divider circuit (DIV) 15 and a deadlock detection circuit 20. Of these, the phase frequency detector 11, the charge pump circuit 12, the low-pass filter 13, the voltage-controlled oscillator 14 and the divider circuit 15 are similar to the corresponding components of the conventional PLL circuit shown in Fig.1.

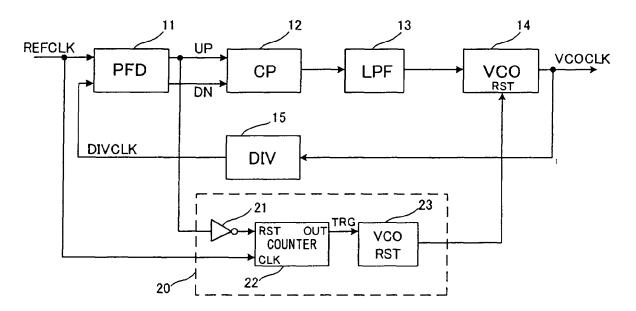

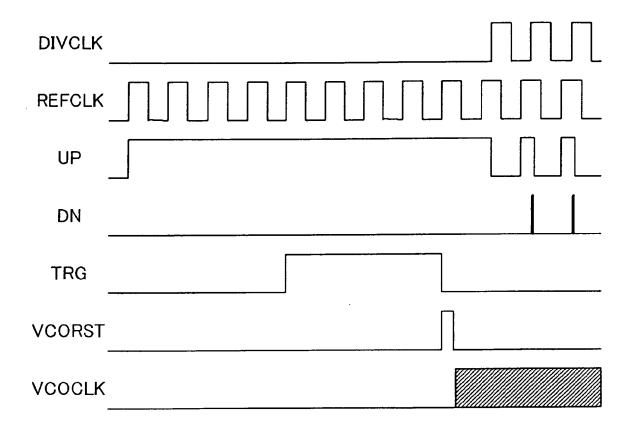

[0014] The phase frequency detector 11 compares the phase of a rising edge of a reference clock signal (REF-CLK) with that of a divided clock signal (DIVCLK) output from the divider circuit 15. If the divided clock signal lags the reference clock signal, or is lower in frequency than the reference clock signal, the phase frequency detector 11 outputs an UP signal, which is a positive going pulse of a pulse width conforming to the phase difference, as shown in Fig.3A. At this time, the DN signal is output as a positive going pulse of a minimum pulse width of the phase frequency detector 11. If the divided clock signal leads the reference clock signal, or is higher in frequency than the reference clock signal, the phase frequency detector 11 outputs a DN signal, which is a positive going pulse of a pulse width conforming to the phase difference, as shown in Fig.3B. At this time, the UP signal is output as a positive going pulse of a minimum pulse width of the phase frequency detector 11.

**[0015]** The charge pump circuit 12 causes the current of a current value corresponding to the pulse width of the UP signal to flow from a power supply to an output terminal, as an output error signal, while causing the current of a current value corresponding to the pulse width of the DN signal to flow from the output terminal to the ground, again as an output error signal. Thus, the output terminal

35

40

45

50

voltage of the charge pump circuit 12 corresponds to the phase difference detected by the phase frequency detector. The low-pass filter 13 receives the error signal output from the charge pump circuit 12 and carries out smoothing of the error signal received to generate a control signal. The voltage-controlled oscillator 14 receives the control signal to generate an output clock signal, the frequency of which is varied to a higher or a lower value in dependence upon the higher or lower value of the control voltage, respectively. The divider circuit 15 receives the output clock signal from the voltage-controlled oscillator 14 and divides the output clock signal by a preset frequency division ratio to output the divided clock signal. In this manner, the PLL circuit performs feedback control to bring the reference clock signal and the divided clock signal into coincidence with each other in phase and frequency, so that the reference clock signal will be synchronized as to the phase with the divided clock signal. At this time, the DN signal and the UP signal are output as positive going pulses of the minimum pulse width of the phase frequency detector 11, as shown in Fig.3C.

[0016] If the PLL circuit falls into a deadlock state by some or other reason, such as by cessation of oscillation of the voltage-controlled oscillator 14 or by unusual increase of the oscillation frequency, the divided clock signal output from the divider circuit 15 becomes fixed at a high or low level, while the UP signal and the DN signal are fixed at a high level and a low level, respectively, as shown in Fig.3D.

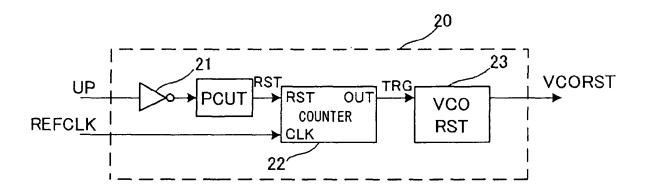

[0017] The deadlock detection circuit 20 in the present embodiment comprises an inverter 21 which receives the UP signal from the phase frequency detector 11, a counter circuit 22 which receives the reference clock signal (REFCLK) and an output signal of the inverter 21 at its clock input terminal and at its reset terminal, respectively, to output a trigger output signal (TRIG), and a VCO resetting circuit 23 which receives the trigger output signal (TRIG) output from the counter circuit 22 and supplies a VCO resetting signal to an reset terminal of the voltage controlled oscillator 14.

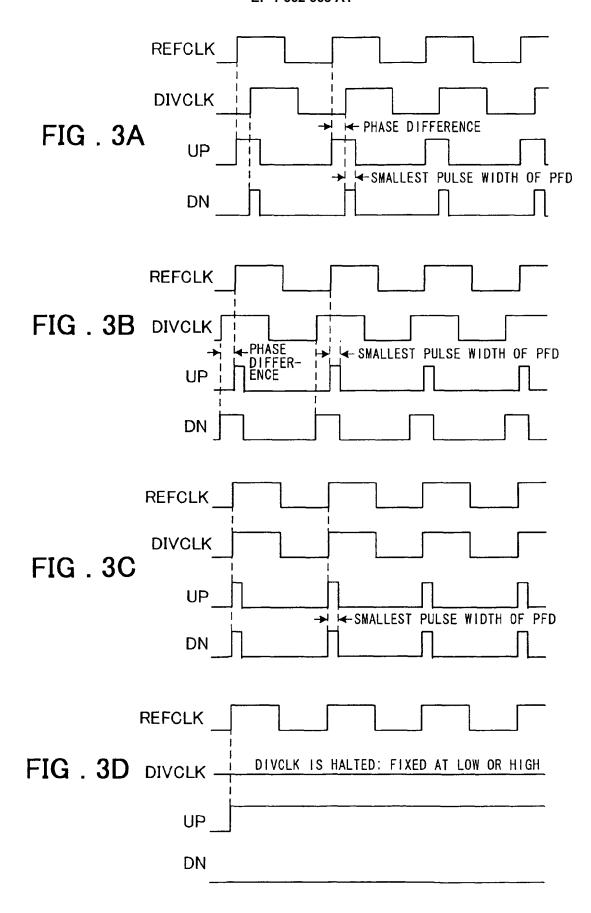

[0018] Fig.4 shows an illustrative configuration of the counter circuit 22. Referring to Fig.4, the counter circuit 22 is configured as a 23 counter, composed by three Dflip-flops 30, 31 and 32. To D-input terminals of the Dflip-flops 30, 31 and 32 are connected to respective inverting output terminals (QB). To each of the reset input terminals (RST) of the D-flip-flops 30, 31 and 32 is supplied an inverted version of the UP signal from the inverter 21. The clock terminal of the D-flip-flop 30 is supplied with the reference clock (REFCLK). The inverting output (QB) of the D-flip-flop 30 is connected to the clock terminal of the D-flip-flop 31. The inverting output (QB) of the D-flip-flop 31 is connected to the clock terminal of the Dflip-flop 32. An output signal from the non-inverting output terminal (Q) of the D-flip-flop 32 is supplied, as the trigger output signal (TRG), to the VCO resetting circuit 23.

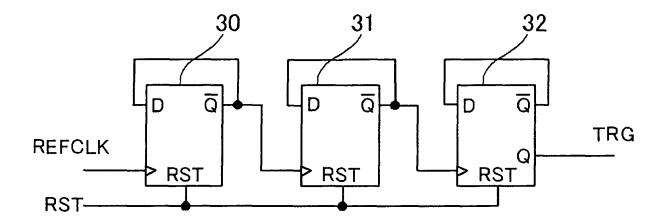

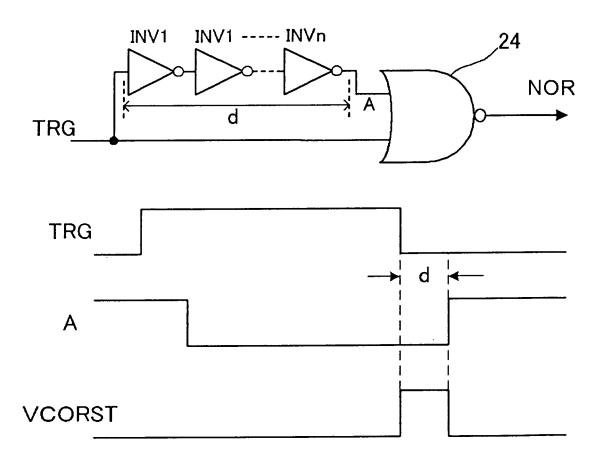

**[0019]** Fig.5 shows an illustrative configuration of the VCO resetting circuit 23. Referring to Fig.5, the VCO re-

setting circuit 23 comprises a delay circuit composed of an odd number of inverters (INV1 to INVn) and a NOR circuit 24. The NOR circuit 24 outputs an inverted logical sum of the trigger output (TRG) and a signal (A) corresponding to the trigger output (TRG) delayed by the delay circuit. The VCO resetting circuit 23 outputs a one shot pulse signal of a pulse width corresponding to the delay time (d) of the delay circuit, at the falling edge of the trigger output signal (TRG). A VCO resetting signal (VCORST) which is one shot pulse signal output from the VCO resetting circuit 23 is supplied as a deadlock detection signal, to a reset terminal of the voltage-controlled oscillator 14.

[0020] Fig.6 is a timing chart showing the operation of the PLL circuit when the PLL circuit has fallen into the deadlock state. If, after phase synchronization of the reference clock signal with the divided clock signal, the PLL circuit falls into deadlock by some reason or other, the divided clock signal (DIVCLK) is at a fixed level. In Fig. 6, the divided clock signal (DIVCLK) is fixed at a low level. [0021] When the divided clock signal (DIVCLK) has become fixed at a low level, the UP signal and the DN signal become fixed at a high level and in at a low level, respectively. The counter circuit 22, which has so far been reset every period of the divided clock signal (DI-VCLK), by a signal (RST) which is obtained by inverting the UP signal by the inverter 21, commences to count the reference clock signal (REDCLK). When the count value of the reference clock signal (REDCLK) by the counter circuit 22 becomes 22, the trigger output signal (TRIG) goes to a high level and when the count value of the reference clock signal (REDCLK) by the counter circuit 22 becomes 23, the trigger output signal (TRIG) undergoes a transition from a high level to a low level. A VCO resetting signal (VCORST) is output from the VCO resetting circuit 23 at a falling edge of the trigger output signal (TRIG) output from the counter circuit 22 which has counted a preset number, herein 23, of the reference clock signal (REFCLK). The voltage-controlled oscillator 14, reset by the VCO resetting signal (VCORST), begins oscillation, and hence the PLL circuit is synchronized after a preset time interval.

#### [Second Embodiment]

**[0022]** Fig.7 shows the configuration of the deadlock detection circuit 20 in the PLL circuit of a second embodiment of the present invention. The configuration of the deadlock detection circuit 20 according to the present second embodiment is equivalent to that of the deadlock detection circuit 20 of the first embodiment, except that, in the configuration of the second embodiment, there is newly added a pulse cutting circuit 24. The configuration of the present second embodiment is otherwise the same as that of the first embodiment described above.

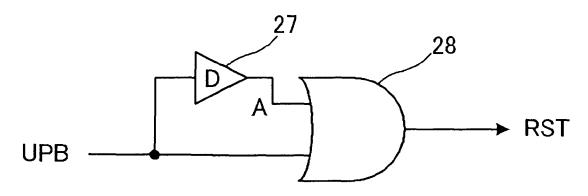

**[0023]** Fig.8A shows the configuration of the pulse cutting circuit 24. This pulse cutting circuit 24 is supplied with an inverted version of the UP signal by the inverter

20

25

35

40

45

50

55

21 (UPB) to output a resetting signal (RST) to the counter circuit 22. The pulse cutting circuit 24 is made up by a delay circuit 27 and an OR circuit 28. The OR circuit 28 is supplied with a signal (UPB), which is an inverted version of the UP signal inverted by the inverter 21, and with a signal (A), which is obtained by delaying the UPB by the delay circuit 27 a preset delay time (D), to output a signal corresponding to the logical sum of these two signals.

**[0024]** As will be apparent from the timing chart shown in Fig.8B, the pulse cutting circuit 24 cuts a pulse having a pulse width not larger than D to output the resetting signal (RST) which is of a high level at all times. In the present second embodiment, the UP signal of the smallest pulse width, output from the phase frequency detector 11 during the normal operation of the PLL circuit, is cut by the pulse cutting circuit.

**[0025]** Thus, the counter circuit 22 is not reset every period of the reference clock signal (REFCLK) by the UP signal of the minimum pulse width, and is supplied at all times with the reset signal which then operates to halt the operation of the counter circuit 22. Thus, with the present second embodiment, there may be achieved such a meritorious effect that the operation noise of the counter circuit 22 is prevented from affecting the PLL circuit to affect in turn jitter of the output clock signal of the PLL circuit.

[0026] In the above-described first and second embodiments, the inverted version of the UP signal which is fixed at a high level at the time of deadlock, is used as the resetting signal (RST) for the counter circuit 22. Hence, during the normal operation, the counter circuit 22 is reset every period of the reference clock signal (RE-FCLK). However, comparable results may be obtained with use of the DN signal which becomes fixed at a low level at the time of deadlock. In this case, the counter circuit 22 is reset every period of a divided clock signal (DIVCLK). A logical sum signal of the above two signals also may be used as the resetting signal (RST). Although the counter circuit 22 is configured to count the reference clock signal (REFCLK), it is also possible to count such a signal, obtained on frequency division of the reference clock signal at a preset ratio. It is to be noted that any clock signal other than the reference clock signal may be used provided that the clock signal used are independent of output clocks of the PLL circuit, it being sufficient if the counter used is able to count during the time sufficiently allowing for deadlock decision in conjunction with the number of stages of the counter circuit.

#### Claims

#### 1. A PLL circuit comprising:

a phase frequency detector (11), receiving a reference clock signal and a divided clock signal, for comparing phase or frequency of the reference clock signal with phase or frequency of the divided clock signal to output an up signal or a down signal depending on whether the phase of the divided clock signal leads or lags the phase of the reference clock signal, respectively, or on whether the frequency of the divided clock signal is lower or higher than the frequency of the reference clock signal, respectively; a charge pump circuit (12), receiving the up and down signals, for causing current to flow out to

a charge pump circuit (12), receiving the up and down signals, for causing current to flow out to an output thereof and to flow in from the output thereof, responsive to said up signal and to said down signal, respectively, for outputting an error signal associated with phase or frequency difference detected by said phase frequency detector;

a low-pass filter (13), receiving the error signal, for smoothing the error signal to output a control voltage:

a voltage controlled oscillator (14), receiving the control voltage for generating an output clock signal, the frequency of which is controlled to vary to a higher or lower value in accordance with higher or lower level of said control signal, respectively; and

a divider circuit (15), receiving the output clock signal, for dividing the frequency of the output clock signal by a preset frequency division ratio to output said divided clock signal, **characterized in that** the PLL circuit further comprises a deadlock detection circuit (20) for detecting the falling of the PLL circuit into a deadlock state to output a deadlock detection signal;

wherein said deadlock detection circuit includes a counter circuit for counting a clock signal, said deadlock detection circuit outputting the deadlock detection signal responsive to a signal output from said counter circuit when said counter circuit has counted a preset number of said clock signal in the deadlock state, said deadlock state being removed by said deadlock detection signal.

- The PLL circuit as claimed in claim 1, wherein said counter circuit is reset responsive to said up signal or said down signal.

- 3. The PLL circuit as claimed in claim 2, wherein said PLL circuit further comprises

- a pulse cutting circuit for cutting said up signal or said down signal having a pulse width not larger than a preset width;

- said counter circuit being reset responsive to an output signal of said pulse cutting circuit.

- 4. The PLL circuit as claimed in any one of claims 1 to 3, wherein said clock signal that said counter circuit counts is the reference clock signal or a signal ob-

20

40

45

tained on frequency division of said reference clock signal by a preset frequency division ratio.

- 5. The PLL circuit as claimed in any one of claims 1 to 3, wherein said voltage controlled oscillator has a reset terminal for receiving said deadlock detection signal output from said deadlock detection circuit, said voltage controlled oscillator, on receipt of said deadlock detection signal from said deadlock detection circuit, being reset to commence oscillation.

- 6. The PLL circuit as claimed in any one of claims 1 to 3, wherein said counter circuit has a reset terminal for receiving a signal for resetting said counter circuit, said signal being one selected among an inverted version of said up signal, said down signal, and the result of logical operation of said up signal and said down signal.

#### 7. A PLL circuit comprising:

a phase frequency detector (11), receiving a reference clock signal and a divided clock signal for comparing phase or frequency of the reference clock signal with phase or frequency of the divided clock signal to output an up signal and a down signal depending on whether the phase of the divided clock signal leads and lags the phase of the reference clock signal, respectively, or on whether the frequency of the divided clock signal is lower and higher than the frequency of the reference clock signal, respectively; a charge pump circuit (12), receiving the up and down signals, for causing current to flow out to an output thereof and to flow in from the output thereof, responsive to said up signal and to said down signal, respectively, for outputting an error signal associated with phase or frequency difference detected by said phase frequency de-

a low-pass filter (13), receiving the error signal, for smoothing the error signal to output a control voltage:

a voltage controlled oscillator (14), receiving the control voltage for generating an output clock signal, the frequency of which is controlled to vary to a higher or lower value in accordance with higher or lower level of said control signal, respectively; and

a divider circuit (15), receiving the output clock signal, for dividing the frequency of the output clock signal by a preset frequency division ratio to output said divided clock signal, **characterized in that** the PLL circuit further comprises a deadlock detection circuit (20) for detecting falling of the PLL circuit into a deadlock state to output a deadlock detection signal;

wherein said deadlock detection circuit (20) in-

cludes a counter circuit (22) for counting a clock signal, said counter circuit (22) being supplied with an inverted version of said up signal or said down signal as a resetting signal, said deadlock state being removed responsive to a signal output from said counter circuit (22) when said counter circuit (22) has counted a preset number of said clock signal.

- **8.** The PLL circuit as claimed in claim 7, wherein said PLL circuit further comprises

- a pulse cutting circuit for cutting said up signal or said down signal having a pulse width not larger than a preset width:

- said counter circuit being reset responsive to an output signal of said pulse cutting circuit.

- 9. The PLL circuit as claimed in claim 7, wherein said clock signal which said counter circuit counts is said reference clock signal or a signal obtained on frequency division of said reference clock signal by a preset frequency division ratio.

6

#### FIG. 1 **PRIOR ART** UP REFCLK VCOCLK PFD CP LPF VCO DN DIVCLK POWER-ON RESET Q CLK 4 FF DIV s 25 26

FIG.2

FIG . 4

# FIG . 5

## FIG . 6

FIG . 7

FIG.8A

### **EUROPEAN SEARCH REPORT**

Application Number EP 05 02 5229

| Category                                 | Citation of document with indica<br>of relevant passages                                                                                                                    | ation, where appropriate,                                                                            | Relevant<br>to claim                         | CLASSIFICATION OF THE APPLICATION (IPC) |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------|

| Х                                        | US 5 864 572 A (BHAGW<br>26 January 1999 (1999                                                                                                                              |                                                                                                      | 1,4,5                                        | H03L7/095                               |

| Υ                                        | * column 4, line 48 - figure 3 *                                                                                                                                            | column 6, line 34;                                                                                   | 2,6,7,9                                      |                                         |

| Х                                        | US 5 389 898 A (TAKET<br>14 February 1995 (199                                                                                                                              | TOSHI ET AL)<br>95-02-14)                                                                            | 1                                            |                                         |

| Υ                                        | * abstract; figure 1                                                                                                                                                        | *<br>                                                                                                | 2,6,7,9                                      |                                         |

| Υ                                        | PATENT ABSTRACTS OF J<br>vol. 010, no. 113 (E-<br>26 April 1986 (1986-0<br>& JP 60 247330 A (MIT<br>7 December 1985 (1985<br>* abstract; figure 2                           | 399),<br>4-26)<br>SUBISHI DENKI KK),<br>-12-07)                                                      | 2,6,7,9                                      |                                         |

|                                          |                                                                                                                                                                             |                                                                                                      |                                              | TECHNICAL FIELDS<br>SEARCHED (IPC)      |

|                                          |                                                                                                                                                                             |                                                                                                      |                                              | H03L                                    |

|                                          |                                                                                                                                                                             |                                                                                                      |                                              |                                         |

|                                          | The present search report has been                                                                                                                                          | n drawn up for all claims  Date of completion of the search                                          |                                              | Examiner                                |

| Munich                                   |                                                                                                                                                                             | 25 January 200                                                                                       |                                              | ters, D                                 |

| X : part<br>Y : part<br>docu<br>A : tech | ATEGORY OF CITED DOCUMENTS icularly relevant if taken alone icularly relevant if combined with another iment of the same category inological background -written disclosure | T : theory or prin<br>E : earlier patent<br>after the filing<br>D : document cit<br>L : document cit | iple underlying the i<br>document, but publi | nvention<br>shed on, or                 |

#### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 05 02 5229

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

25-01-2006

| Patent docume cited in search re | nt<br>port | Publication<br>date | Patent family member(s) |                        | Publication date       |

|----------------------------------|------------|---------------------|-------------------------|------------------------|------------------------|

| US 5864572                       | Α          | 26-01-1999          | NONE                    |                        | ı                      |

| US 5389898                       | Α          | 14-02-1995          | NONE                    |                        |                        |

| JP 60247330                      | A          | 07-12-1985          | JP<br>JP                | 1718585 C<br>2050655 B | 14-12-199<br>05-11-199 |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

|                                  |            |                     |                         |                        |                        |

FORM P0459

$\stackrel{

m O}{

m ii}$  For more details about this annex : see Official Journal of the European Patent Office, No. 12/82