## (11) **EP 1 703 398 A8**

## (12) CORRECTED EUROPEAN PATENT APPLICATION

(15) Correction information:

Corrected version no 1 (W1 A2)

Corrections, see

Bibliography INID code(s) 22

(48) Corrigendum issued on:

15.09.2010 Bulletin 2010/37

(43) Date of publication:

20.09.2006 Bulletin 2006/38

(21) Application number: 05254873.2

(22) Date of filing: 04.08.2005

(84) Designated Contracting States: **DE FR GB**

(30) Priority: 17.03.2005 JP 2005078010

(71) Applicant: FUJITSU LIMITED Kawasaki-shi,

Kanagawa 211-8588 (JP)

(72) Inventors:

Suzuki, Kenji, c/o Fujitsu Limited Kawasaki-shi

Kanagawa 211-8588 (JP)

(51) Int Cl.: **G06F 11/10** (2006.01)

- Honda, Yasufumi, c/o Fujitsu Limited Kawasaki-shi Kanagawa 211-8588 (JP)

- Koguchi, Takashi, c/o Fujitsu Limited Kawasaki-shi Kanagawa 211-8588 (JP)

- (74) Representative: Fenlon, Christine Lesley et al Haseltine Lake LLP Lincoln House, 5th Floor 300 High Holborn London WC1V 7JH (GB)

## (54) Techniques for soft error correction

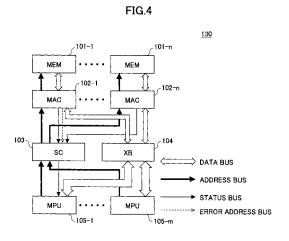

(57) A soft error correction method is described for a memory system having memory access controllers accessing memories for storing bytesliced data in cycle synchronism, and a system controller receiving a memory access from an arbitrary one of MPUs and issuing a memory address to the memory access controllers. When a correctable error is detected in data read from one memory, an error address where the error was detected is held within a memory access controller, and an error notification is made to the system controller from the memory access controller. In response to the error notification, the memory access controller without intervention from the MPUs, and reads, corrects and rewrites the data to the error address.

Printed by Jouve, 75001 PARIS (FR)