(12)

# **EUROPÄISCHE PATENTANMELDUNG**

(43) Veröffentlichungstag:

22.11.2006 Patentblatt 2006/47

(51) Int Cl.:

H01L 21/768 (2006.01)

(21) Anmeldenummer: 06113643.8

(22) Anmeldetag: 08.05.2006

(84) Benannte Vertragsstaaten:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI SK TR

Benannte Erstreckungsstaaten:

AL BA HR MK YU

(30) Priorität: 19.05.2005 DE 102005023122

- (71) Anmelder: Infineon Technologies AG 81669 München (DE)

- (72) Erfinder: Körner, Heinrich 83052, Bruckmühl (DE)

- (74) Vertreter: Kindermann, Peter et al Kindermann Patentanwälte Postfach 10 02 34 85593 Baldham (DE)

#### (54)Integrierte Schaltungsanordnung mit Schichtstapel und Verfahren

(57)Erläutert wird unter anderem eine integrierte Schaltungsanordnung (10), die eine elektrisch leitfähige Leitstruktur (16,22) aus Kupfer oder einer Kupferlegierung enthält. An einer Seitenwand der Leitstruktur (16,22) befindet sich ein Schichtstapel (26), der mindestens drei Schichten enthält. Trotz sehr dünner Schichten in dem Schichtstapel (32) lässt sich eine hohe Barrierewirkung gegen Kupferdiffusion verbunden mit einer hohen elektrischen Leitfähigkeit erreichen, wie sie z.B. für eine elektrolytische Kupferabscheidung mit Außenstrom benötigt wird.

35

#### **Beschreibung**

**[0001]** Die Erfindung betrifft eine integrierte Schaltungsanordnung mit einer elektrisch leitfähigen Leitstruktur und mit einem zwischen der Leitstruktur und einem Dielektrikum an einer Seitenwand der Leitstruktur angeordneten Schichtstapel.

[0002] Die Leitstruktur ist beispielsweise eine Leitbahn zum lateralen Stromtransport oder ein Via zum vertikalen Stromtransport. Lateral bedeutet dabei parallel zu einer Hauptfläche eines Substrats der Schaltungsanordnung, wobei in der Hauptfläche eine Vielzahl integrierter Halbleiterbauelemente angeordnet sind. Vertikal bedeutet in Normalenrichtung oder entgegen der Normalenrichtung der Hauptfläche. Die Leitstruktur besteht beispielsweise aus Kupfer oder aus einer Kupferlegierung. Im Zusammenhang mit Kupfer-Leitstrukturen wird das sogenannte einfache Damaszener-Verfahren oder das sogenannte duale Damaszener-Verfahren verwendet. Die Leitstrukturen werden in ein Dielektrikum eingebettet, beispielsweise in Siliziumdioxid oder ein Dielektrikum mit einer kleinen relativen Dielektrizitätskonstante von beispielsweise kleiner als 3,9 bzw. kleiner als 3.

[0003] Um eine Diffusion des Kupfers in das Dielektrikum und anschließend in ein einkristallines Halbleitersubstrat zu verhindern, werden Schichtstapel verwendet, die auch eine gute mechanische Haftung zwischen dem Dielektrikum und der Leitstruktur gewährleisten sollen. Im Rahmen eines Damaszener-Verfahrens wird die Kupfer-Leitstruktur mit einem elektrolytischen Verfahren erzeugt, beispielsweise mit einer Schichtdicke größer als 100 nm. Das elektrolytische Verfahren wird mit Außenstrom durchgeführt, wobei der Schichtstapel zur Stromleitung verwendet wird, beispielsweise weil am Waferrand ein festes Potential angelegt wird, das das Gegenpotential zu einer als Anode geschalteten Gegenelektrode ist.

[0004] Es ist Aufgabe der Erfindung, eine integrierte Schaltungsanordnung mit einem Schichtstapel anzugeben, der eine kleine Gesamtschichthöhe hat und dennoch als Diffusionsbarriere gegen Kupferdiffusion sowie als sogenannte Seed-Layer in einem elektrolytischen Kupfer-Abscheideverfahren verwendet werden kann. Außerdem soll ein Verfahren zur Kupferabscheidung angegeben werden.

[0005] Die auf die Schaltungsanordnung bezogene Aufgabe wird durch eine Schaltungsanordnung mit den im Patentanspruch 1 angegebenen Merkmalen gelöst. Weiterbildungen sind in den Unteransprüchen angegeben.

[0006] Die Erfindung betrifft Verfahren zur Herstellung dünnster Mehrschichtstapel sowie solche Mehrschichtstapel, die als Ganzes sowohl als zuverlässige Haftschichten, als Diffusionsbarrieren und auch als Schichten für homogene und spontane Bekeimungen von nachfolgenden CVD- (Chemical Vapor Deposition) oder ECD-Metallabscheidungen (Electro Chemical Deposition) dienen und welche die Dicken-Forderungen der

ITRS (International Technology Roadmap for Semiconductors) 2003, Update 2004, für zukünftige Technologien erfüllen. Die Mehrschichtstapel ermöglichen selbst bei größten Waferdurchmessern (z.B. 300 mm und größer) homogene und lunkerfrei füllende Abscheidungen in Single- oder Dual Damascene-Strukturen mit hohem Aspektverhältnis z.B. von größer als Eins. Insbesondere wird eine Abscheidung von Cu oder Wolfram durch elektrolytische, außenstromlose oder (MO)CVD-Prozesse (Metall Organisches CVD) möglich. Ein sich eventuell bildendes Oberflächenoxid soll - im Gegensatz zu Cu Seedlayern - nicht stören und nicht zu lunkerhaltigen Auffüllungen führen. Die erfindungsgemäßen Schichten zeigen deutlich geringere mechanische Stress-Werte als z.B. reine Ruthenium-Schichten und damit geringere Neigungen zur Delamination oder Riss- bzw. Crack-Bildung. Die Schichtstapel weisen bei gleicher Gesamtdikke wesentlich bessere Eigenschaften als Haft-, Barriereund Nukleationsschicht auf als dicke Einzelschichten. Zum Erzielen vergleichbarer Ergebnisse wie bisher genügen somit geringere Gesamtschichtdicken.

[0007] Überraschenderweise zeigen dünnste Schichtkombinationen des Typs A/B/A, A/B/A/B/A, A/B/A/B/A, oder A/B/A', A/B/A'/B/A bzw. A' etc. die genannten Eigenschaften, wobei:

- Leitschichtmaterialien A beispielsweise Ruthenium (Ru), Wolfram (W), Rhodium (Rh), Rhenium (Re), Molybdän (Mo) oder Legierungen hieraus oder ähnliche Materialien darstellen, und

- Leitschichtmaterialien A' beispielsweise Ruthenium (Ru), Wolfram (W), Rhodium (Rh), Rhenium (Re), Molybdän (Mo), Kupfer (Cu), Silber (Ag), Gold (Au), Palladium (Pd), Platin (Pt) oder Legierungen hieraus oder ähnliche Materialien darstellen. Als A' Materialien kommen bspw. auch Nickel (Ni), Chrom (Cr) oder Kobalt (Co) in Frage, insbesondere wenn das darunter angeordnete Material B elementar ist, d.h. nur eine Atomart enthält.

- 40 Zwischenschichtmaterialien B beispielsweise

Ta, TaN, eine Doppelschicht TaN/Ta, TaC, TaCN, TaSiN,

WN, WC, WCN, WSiN,

45 TiN, TiC, TiCN, TiSiN,

Al, Cr, Ni, Co, Pd, Pt, C oder Legierungen hieraus oder ähnliche Materialien darstellen.

[0008] Die Schichtstapel enthalten somit mindestens drei Schichten, wobei Leitschichten mit Zwischenschichten abwechseln und der Schichtstapel bspw. mit einer Leitschicht beginnt. Mehrere Zwischenschichten bestehen jeweils bspw. aus dem gleichen Material oder aus voneinander verschiedenen Materialien. Ebenso bestehen die Leitschichten jeweils aus dem gleichen Material oder aus voneinander verschiedenen Materialien.

**[0009]** Während z.B. reine Ruthenium-Schichten von 20, 30 oder 40 nm Dicke aufgrund ihrer kolumnaren Struktur keine ausreichende Cu-Diffusionsbarrieren sind

50

40

und somit noch zusätzliche Barrierenschichten benötigen, ist z.B. die A/B/A/B/A - Schichtkombination mit A  $\leq$  5 nm Ru und B  $\leq$  2 nm TaN sehr wohl eine ausreichende Cu-Diffusionsbarriere.

[0010] Bei den Materialien der Gruppe A handelt es sich typischerweise um niederohmige Refraktärmetalle, d.h. um Metalle mit Schmelztemperatur größer als 1600 °C oder sogar größer als 2000 °C. Die Gruppe A' ist im Vergleich zur Gruppe A erweitert um niederohmige Halbedelmetalle, z.B. Cu, oder niederohmige Edelmetalle. Niederohmig bedeutet, dass der spezifische Widerstand  $\rho \le 50 \ \mu\Omega$ cm oder  $\rho \le 20 \ \mu\Omega$ cm ist, gemessen bspw. an einem Volumenmaterial (bulk), bspw. einer Schicht mit einer Dicke von 200 nm oder größer. Die Materialien der Gruppe A bzw. A' sind häufig mit Cu oder anderen Leitbahnmaterialien weder legierbar noch mischbar. Die minimale benötigte Dicke der A-Materialien bzw. A'-Materialien wird durch den noch zulässigen Schicht-Widerstand bei der nachfolgenden elektrolytischen Cu-Abscheidung sowie durch die Anzahl der A-Schichten bzw. bzw. A'-Schichten bestimmt. Um gleichzeitig wirkungsvolle Diffusionsbarrieren zu erzeugen, erwies es sich als besonders vorteilhaft, den Abscheideprozess für die A-Komponente bzw. A'-Komponente ein- oder mehrmals zu unterbrechen und mindestens einmal extrem dünne (< 2nm) Schichten oder Prozesse der B-Komponenten einzubringen.

[0011] Bei den Materialien der Gruppe B handelt es sich typischerweise um leitfähige Schichten mit Cu-Diffusionssperrwirkung. Aufgrund ihrer eigenen Leitfähigkeit tragen sie auch zur Leitfähigkeit des Schichtstapels und damit zu dessen Funktion als Bekeimungsschicht für nachfolgende Abscheideprozesse bei, die eine gewisse Mindestleitfähigkeit benötigen. Noch wichtiger aber ist der Beitrag der B-Komponenten zur Barrierenwirkung. Sie wirken nicht nur selbst diffusionshemmend, sondern modifizieren überraschenderweise auch das Wachstum der nachfolgenden A-Komponente bzw. bzw. A'-Komponente. Während diese in dickeren Einzelschichten bevorzugt kolumnar wachsen, bewirken zwischengelagerte dünne und somit oft amorph ausgestaltete B-Komponenten ein zunächst ebenfalls amorph einsetzendes Wachstum der A-Komponenten bzw. A'-Komponenten. Im Gegensatz zu den kolumnar ausgeprägten A-Komponenten bzw. A'-Komponenten tragen die entsprechenden amorphen oder röntgenamorphen A-Spezies bzw. A'-Spezies ebenfalls zur Barrierenwirkung bei. [0012] Neben der Abscheidung von dünnen B-Komponenten erfüllen bei einer Weiterbildung auch folgende Schritte eine analoge Wirkung:

- Unterbrechung der A-Abscheidung bzw. der A'-Abscheidung und Temperung bei bis zu 400°C in Gasgemischen, die eine oder mehrere der Komponenten N<sub>2</sub>, Ar, O<sub>2</sub>, NH<sub>3</sub>, Kohlenwasserstoffe oder H<sub>2</sub> enthalten.

- Unterbrechung der A-Abscheidung bzw. der A'-Abscheidung und Plasma-Flash oder kurzer Sputter-

schritt mit Gasgemischen, die eine oder mehrere der Komponenten  $N_2$ , Ar,  $O_2$ ,  $NH_3$ , Kohlenwasserstoffe oder  $H_2$  enthalten.

[0013] In Summe wird damit erreicht, dass im Vergleich zum Zwei- bzw. Dreischichtschichtsystem des Typs B/A bzw. B/B'/A (z.B. TaN/Ta/Cu) geringere Gesamtdicken an Barrierekomponente B benötigt werden, um die gleiche Barrierewirkung zu erreichen. Gleichzeitig werden keine dickeren Schichten der A-Komponente bzw. A'-Komponente für die "seed-layer"-Funktion als im Vergleichsfall benötigt.

[0014] Bei einer nächsten Weiterbildung wird ausgenutzt, dass beispielsweise Ruthenium ein Oxid (RuO<sub>2</sub>) bildet, das eine zum reinen Metall vergleichbare Leitfähigkeit von etwa 20  $\mu\Omega$ cm besitzt. Somit wird es möglich, eine beispielsweise A/B/A/B/A-Schichtenfolge zunächst mit einer dünnen A-OxidSchicht zu beginnen, welche dann kontinuierlich oder abrupt in eine reine A-Schicht übergeht. Dieses A-Oxid zeigt eine sehr gute Haftung zu den typischen IMD-Materialien (InterMetallDielektrikum) wie z.B. SiO<sub>2</sub> bzw. SiCOH und macht zusätzliche Haftschichten überflüssig, wie sie bei Cu-Seedlayern bzw. Cu-Wachstumskeimbildungsschichten benötigt werden. Aufgrund der hohen Leitfähigkeit von RuO2 stört eine oberflächlich ausgebildete Oxidschicht nachfolgende Prozesse wie z.B. elektrolytische Cu-Abscheidung nicht und diese Abscheidungen können reproduzierbarer, sicherer, gleichmäßiger und lunkerfrei erfolgen.

[0015] Geeignete Abscheidemethoden für A-Komponenten bzw. A'-Komponenten sind PVD (Physical Vapor Deposition, insbesondere Verfahren mit einer hohen Plasmadichte und/oder hohem Ionisierungsgrad des abzuscheidenden Materials, z. B. IPVD (Ionized PVD) oder SIP (Self Ionized Plasma). Andere Abscheidemethoden sind CVD (Chemical Vapor Deposition), ALD (Atomic Layer Deposition), galvanische oder stromlose Verfahren oder auch SFD (Supercritical Fluid Deposition) mit z.B. superkritischem CO<sub>2</sub> Für B-Komponenten eignen sich prinzipiell die gleichen Methoden. Bevorzugterweise werden die Multischichten in Mehrkammeranlagen erzeugt, wie z.B. einer "Endura" von Applied Materials. Diese bieten die Möglichkeit, die Schichten mit allen notwendigen Vor- und Nachbehandlungen mit oder ohne Vakuum-Unterbrechung unter Einsatz verschiedener Parameter (wie Temperatur, Druck, Gasflüsse) oder verschiedener Medien in einer oder mehreren Abscheidekammern unmittelbar hintereinander zu erzeugen und damit schnell, gut kontrolliert und kostengünstig.

50 [0016] Optional kann vor der Erzeugung des Schichtstapels:

- ein Reinigungsschritt z.B. zur Entfernung von Oberflächen-oxiden auf bereits vorhandenen Metall-Lagen

- die Abscheidung einer separaten, dünnen Haft- oder Nukleationsschicht,

- ein Schritt zum Versiegeln von Poren in porösen low-

40

k Materialien.

oder ähnliches ausgeführt werden.

[0017] Optional kann sich an die Erzeugung des Schichtstapels:

- die Abscheidung einer sehr dünnen Cu-Schicht, z.B. dünner als 1 nm oder dünner als 3 nm,

- ein Reinigungsschritt zur Generierung definierter Oberflächen,

- ein Anneal- oder Temperschritt,

- die Abscheidung eines Materials, welches als Leitbahnmaterial fungiert,

oder ähnliches anschließen.

**[0018]** Die Vorteile der erfindungsgemäßen multifunktionalen Schichtstapel lassen sich wie folgt zusammenfassen:

- großer effektiver Bahnquerschnitt der Kupferleitstruktur und damit verbundene hohe Stromtragfähigkeit, insbesondere nimmt der Schichtstapel auch bei minimalen lateralen Abmessungen der Leitstruktur von kleiner als 100 nm nur weniger als 10 Prozent des Gesamtbahnquerschnitts ein,

- exzellente Eigenschaften als diffusionshemmende Barriere- und niederohmige Bekeimungsschichten bei geringsten Schichtdicken für Einzelkomponenten und Schichtstapel,

- zuverlässige, spontane und gleichmäßige Bekeimung bei nachfolgenden Prozessen wie z.B. Cu-ECD (Electro Chemical Deposition) oder -(MO)CVD sowohl lateral über den gesamten Wafer als auch in Strukturen mit anspruchsvollsten Aspektverhältnissen z.B. größer als 1 oder größer als 2) und Geometrien (z.B. minimale Abmessungen kleiner als 100 nm),

- geringste Rauhigkeit des Schichtstapels und des nachfolgend abgeschiedenen "Leitbahnmaterials",

- ermöglicht lunkerfreie Füllung von Damascene-Strukturen und damit Erzeugung hochstromtragender Leitbahnen,

- skalierbar,

- wenig sensitiv bezüglich Bildung von Oberflächen-Oxiden,

- Minimierung oder gezielte Einstellung von z.B. bestimmten Schicht-Stresswerten über die Schichtkombination möglich und somit geringste Gefahr für Delaminationen, Crackbildung etc.,

- Materialien und Methoden in großem Umfang wählund kombinierbar,

- Kombinierbar mit Vor- und Nachbehandlungsschritten.

- Kostengünstig,

- Geeignet für Damascene als auch für subtraktive Architekturen.

[0019] Die Erfindung betrifft außerdem ein Verfahren

zur Herstellung der erfindungsgemäßen Schaltungsanordnung oder einer ihrer Weiterbildungen. Bei einer Weiterbildung des Verfahrens wird eine elektrolytische Kupferabscheidung mit Außenstrom ohne Verwendung einer Kupferkeimbildungsschicht direkt auf dem Schichtstapel aufgebracht.

[0020] Es werden also Verfahren zur Erzeugung von ultradünnen niederohmigen Schichtstapeln sowie solche Schichtstapel angegeben, die sowohl als Haft-, Barriereund Bekeimungsschicht in Mehrlagenmetallisierungen von integrierten Schaltkreisen dienen. Die Schichtstapel bestehen aus mindestens zwei unterschiedlichen Schichtmaterialien, von denen mindestens ein Material (B) amorph oder teilweise amorph ist und welches das andere Material (A) bzw. die anderen Materialien (A, A') mindestens einmal unterbricht.

**[0021]** Im folgenden werden Ausführungsbeispiele der Erfindung an Hand der beiliegenden Zeichnungen erläutert. Darin zeigen:

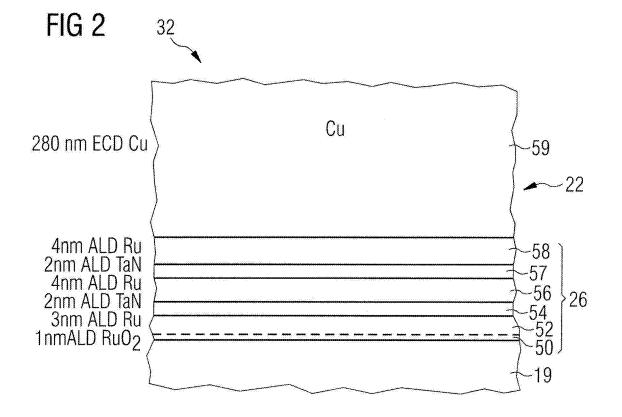

- Figur 1 einen Querschnitt durch die Metallisierung einer integrierten Schaltungsanordnung entlang der Normalenrichtung zur Oberfläche eines nicht dargestellten Halbleitersubstrats,

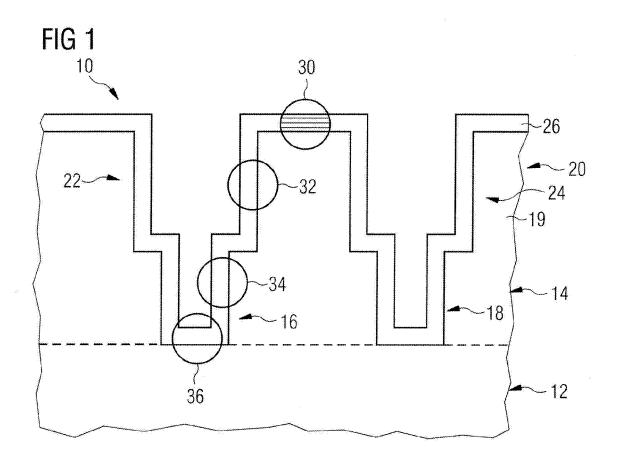

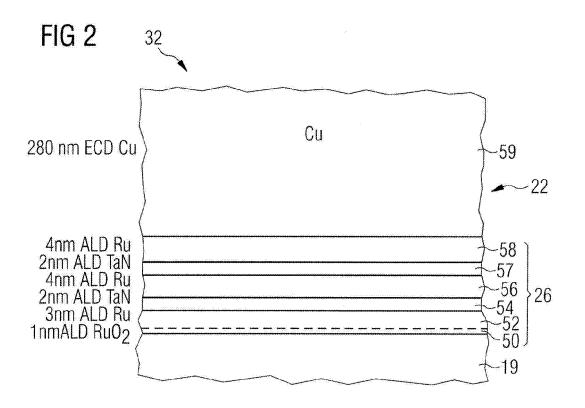

- 25 Figur 2 einen Schichtstapel mit zwei Zwischenschichten.

- Figur 3 einen Schichtstapel mit einer Zwischenschicht, und

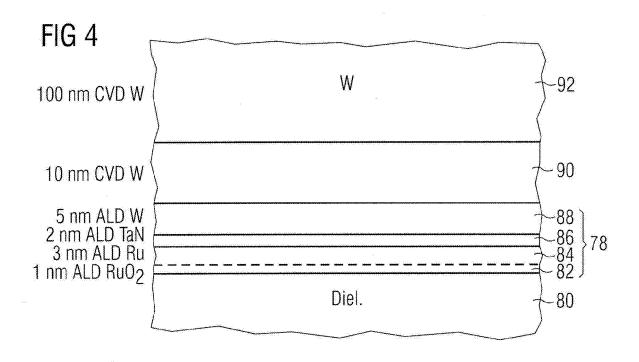

- Figur 4 einen Schichtstapel für einen Wolframkontakt.

[0022] Figur 1 zeigt einen Querschnitt durch die Metallisierung einer integrierten Schaltungsanordnung 10 entlang der Normalenrichtung zur Oberfläche eines nicht dargestellten Halbleitersubstrats, z.B. eines einkristallinen Siliziumsubstrats. Die Schaltungsanordnung 10 enthält eine untere Metallisierungslage 12. An die untere Metallisierungslage 12 schließt sich nach oben hin eine Vialage 14 an, die Kupfervias 16 und 18 enthält. Die Vialage 14 befindet sich in einer Isolierschicht 19, in der auch eine Leitbahnlage 20 angeordnet ist, die Leitbahnen 22 und 24 enthält. Im Ausführungsbeispiel werden die Vialage 12 und die Leitbahnlage 20 mit Hilfe eines dualen Damaszener-Verfahrens hergestellt, wobei nach dem Erzeugen der Aussparungen für die Vias 16, 18 und für die Leitbahnen 22, 24 ganzflächig und konform ein Schichtstapel 26 abgeschieden wird, dessen Aufbau weiter unten noch näher erläutert wird.

**[0023]** Auf Grund der konformen Abscheidung sind die folgenden Ausschnitte des Schichtstapels 26 im wesentlichen identisch:

- ein Ausschnitt 30 an der Oberfläche der Isolierschicht zwischen zwei Leitbahnen 22, 24, wobei der den Ausschnitt 30 enthaltende Teil des Schichtstapels 26 bei einem anschließenden Planarisierungsschritt wieder entfernt wird,

- ein Ausschnitt 32 an der Seitenwand der Leitbahn

20

- 22, insbesondere auf halber Höhe der Seitenwand,

ein Ausschnitt 34 an der Seitenwand des Vias 16, insbesondere auf halber Höhe der Seitenwand, und

- ein Ausschnitt 36 am Boden des Vias 16, wobei bei diesem Ausschnitt 36 der Schichtstapel 26 nicht am Dielektrikum 19 sondern auf dem Metall der unteren Metallisierungslage angeordnet ist.

[0024] An Stelle der unteren Metallisierungslage wird auch eine polykristalline Leitstruktur, z.B. aus Silizium, verwendet. Schichtstapel, die in ihrem Aufbau dem Schichtstapel 26 entsprechen, sind bei anderen Ausführungsbeispielen auch in höheren Metallisierungslagen angeordnet, insbesondere in allen höheren Kupfermetallisierungslagen. alternativ werden solche Schichtstapel nur in einer oder in zwei Metallisierungslagen erzeugt, während in anderen KupferMetallisierungslagen der Schaltungsanordnung andere Barriereschichten oder andere Barriereschichtstapel verwendet werden.

[0025] Figur 2 zeigt den Ausschnitt 32 des Schichtstapels 26 mit zwei Zwischenschichten 54 und 57. Vorhergehende Prozessschritte zur Herstellung mikroelektronischer Bauelemente auf entsprechenden Substraten sind bekannt und werden deshalb nicht näher erläutert. Das Substrat ist bspw. ein einkristalliner Siliziumwafer oder ein SOI-Wafer (Silicon On Insulator). Der Wafer hat bspw. einen Durchmesser größer oder gleich 200 Millimeter oder größer oder gleich 300 Millimeter.

**[0026]** Es wird eine erste Isolationsschicht abgeschieden und es werden Durchkontaktierungen erzeugt, z.B. durch Füllung mit Wolfram per CVD (chemical Vapor Deposition) und CMP (chemical Mechanical Polishing) gemäß dem Stand der Technik.

[0027] Danach erfolgt bspw. die Abscheidung einer dielektrischen Barriere, z.B. von 30 nm PECVD-SiN (Plasma Enhanced CVD Siliziumnitrid) oder PECVD-SiCN (Siliziumcarbonitrid). Anschließend wird die elektrisch isolierende Schicht 19 erzeugt, bspw. durch Abscheidung von mindestens 100 nm dielektrischem Material, wie PECVD SiO<sub>2</sub> (Siliziumdioxid), SiCOH (Hydrogenated Oxidized Silicon Carbon), oder anderen low-k Materialien als IMD (Intermetalldielektrikum) sowie optionaler Hartmasken und Hilfsschichten mittels bekannter Techniken der Halbleiterherstellung.

[0028] Danach werden in der Schicht 19 Gräben und/ oder Vias durch bekannte Abfolgen von Belackung, lithographischer Belichtung und Erzeugung von Lackmasken, plasmaunterstützter Ätzschritte und Lackstripp-Verfahren mittels bekannter Techniken der Halbleiterherstellung erzeugt. Die minimalen lateralen Strukturbreiten des Grabens für die Leitbahn 22 sind dabei bspw. kleiner als 100 Nanometer.

[0029] Dann wird die dielektrische Barriere geöffnet, bspw. durch plasmaunterstützte Ätzschritte mittels bekannter Techniken der Halbleiterherstellung. Der Wafer wird danach in eine Multikammeranlage zur Abscheidung von metallischen Schichten eingebracht, bspw. in eine Multikammeranlage mit einem Grundvakuumdruck

kleiner als 10 mTorr bzw. 1,3 Pa. Es wird ein optionaler Degas- und Reinigungsschritt mittels bekannter Techniken der Halbleiterherstellung durchgeführt, bspw. physikalisch oder nasschemisch.

[0030] Nachdem der Wafer in eine ALD-Kammer (Atomic layer Deposition) eingebracht worden ist, werden bspw. 1 nm (Nanometer) ALD RuO<sub>2</sub> einer Haftschicht 50 und 3 nm Ru einer ersten Leitschicht 52 bei bspw. T = 280 °C (Grad Celsius) abgeschieden, bspw. unter Verwendung von abwechselnden Pulsen von Ru  $(C_2H_5C_5H_4)_2$  [Bis (ethylcyclopentadienyl) ruthenium (II)] sowie sauerstoffhaltigen Gasgemischen, zwischen denen jeweils ein kurzer Spülschritt mit Inertgas erfolgt, z.B. mit molekularem Stickstoff N2. Um zu Beginn bspw. eine ein Nanometer dicke Haftschicht 50 aus RuO2 abzuscheiden, wird anfänglich als Reaktionspartner ein Sauerstoff-Argon-Gasgemisch mit 85 Prozent Sauerstoff O<sub>2</sub> bezogen auf die Gesamtgasmenge des Sauerstoff-Argon-Gasgemisches verwendet. Nach Abscheidung von ca. 1 nm RuO<sub>2</sub> wird mit einem Sauerstoff-Argon-Gasgemisch von 42 Prozent Sauerstoff bezogen auf die Gesamtgasmenge des Sauerstoff-Argon-Gasgemisches reines Ruthenium Ru für die erste Leitschicht 52 mit einem spezifischen elektrischen Widerstand p = 17  $\mu\Omega$ cm (Mikroohmzentimeter) abgeschieden. Die Abscheiderate liegt bspw. bei 0,16 nm/Zyklus bzw. bei 1,6 Angström je Zyklus.

[0031] Der Wafer wird dann in eine zweite ALD-Kammer transportiert, z.B. in eine Kammer der selben Anlage, insbesondere in eine der zuvor benutzten ALD-Kammer benachbarte ALD-Kammer. Hier werden bspw. 2 nm ALD TaN (Tantalnitrid) einer ersten Zwischenschicht 54 direkt auf der ersten Leitschicht 52 abgeschieden, bspw. unter Verwendung von abwechselnden Pulsen von Tantal-Tris(diethylamino)-t-butylimid sowie Ammoniak NH<sub>3</sub>, zwischen denen jeweils ein kurzer Spülschritt bspw. mit Inertgas (N<sub>2</sub>/Ar) erfolgt. Die Temperatur in der Kammer beträgt bspw. T = 260°C. Die Abscheiderate liegt bspw. bei 0,4 Angström/Zyklus.

40 [0032] Danach wird der Wafer bspw. wieder in die zuerst benutzte ALD-Kammer eingebracht, wo bspw. 4 nm ALD Ru einer zweiten Leitschicht 56 bei den gleichen Prozessbedingungen wie beim Abscheiden der ersten Leitschicht 52 abgeschieden werden. Die zweite Leitschicht 56 wird unmittelbar auf der Zwischenschicht 54 erzeugt, so dass die Zwischenschicht 54 und die zweite Leitschicht 56 aneinander grenzen.

[0033] Anschließend wird der Wafer wieder in die zweite ALD-Kammer transportiert, wo bspw. 2 nm ALD TaN einer zweiten Zwischenschicht 57 auf der zweiten Leitschicht 56 unter den gleichen Prozessbedingungen wie beim Erzeugen der ersten Zwischenschicht 54 abgeschieden werden.

[0034] Danach wird der Wafer nochmals in die zuerst benutzte ALD-Kammer eingebracht. In der zuerst benutzten Kammer wird auf der zweiten Zwischenschicht 57 eine dritte Leitschicht 58 erzeugt, die bspw. eine Schichtdicke von 4 nm hat und die eine ALD Ruthenium-

schicht ist. Beim Abscheiden der dritten Leitschicht 58 werden wieder die gleichen Abscheidebedingungen verwendet, wie beim Abscheiden der ersten Leitschicht 52. [0035] Es entsteht ein Schichtstapel 26 der in der folgenden Reihenfolge enthält:

- eine untere Haftschicht 50, die einen spezifischen elektrischen Widerstand von etwa 20 Mikroohmzentimetern hat,

- eine erste Leitschicht 52 aus Ruthenium mit einen spezifischen elektrischen Widerstand von etwa 10 Mikroohmzentimetern,

- eine erste Zwischenschicht 54 mit einen spezifischen elektrischen Widerstand von etwa 200 Mikroohmzentimetern.

- eine zweite Leitschicht 56 aus Ruthenium mit einen spezifischen elektrischen Widerstand von etwa 10 Mikroohmzentimetern,

- einer zweite Zwischenschicht 57 mit einen spezifischen elektrischen Widerstand von etwa 200 Mikroohmzentimetern.

- eine dritte Leitschicht 52 aus Ruthenium mit einen spezifischen elektrischen Widerstand von etwa 10 Mikroohmzentimetern.

[0036] Obwohl die Leitschichten 52, 56 und 58 vorrangig dem Stromtransport beim elektrolytischen Abscheiden des Kupfers dienen, d.h. die klassische Funktion einer Seedlayer haben, erbringen sie auch Funktionen einer Kupferdiffusionsbarriere, insbesondere auf Grund amorpher Teilschichten an den Grenzen zur jeweils darunter angeordneten Zwischenschicht 54 bzw. 57. Ebenso dienen zwar die Zwischenschichten 54 und 57 vorrangig als Kupfer-Diffusionsbarriere. Jedoch fließt durch die Zwischenschichten bei der elektrolytischen Kupferabscheidung auch ein Strom, insbesondere quer zur Zwischenschicht und in lateraler Richtung der Zwischenschicht.

[0037] Dann wird das Substrat bzw. der Wafer aus der Multikammeranlage zur Prozess-Station für elektrolytische Cu-Abscheidungen gebracht. Hier erfolgt die Abscheidung einer Bulk-Leitstrukturschicht 59 aus Kupfer mit einer Schichtdicke von mehr als 100 Nanometern, bspw. mit einer Schichtdicke von 280 nm. Es werden bekannte elektrolytische Verfahren benutzt, bspw. bei Raumtemperatur mit abschließender Reinigung des Substrates durch Spülung mit DI-Wasser (Delonisiertes Wasser) und i-Propanol (Isopropanol).

[0038] Danach wird eine Temperung des beschichteten Substrates bei einer Temperatur größer als 100 °C für bspw. mehr als 10 Minuten durchgeführt, bspw. bei 150°C für 15 min. Bspw. wird in Formiergas mit 95 Prozent molekularer Stickstoff und 5 Prozent molekularer Wasserstoff getempert. Die Tempertemperatur ist jedoch kleiner als 450 °C oder kleiner als 350 °C.

[0039] Nach dem Tempern werden über den Graben bzw. das Via hinausragende Kupferbereiche, Mehrschichtbarrierebereiche sowie Dielektrikumsanteile

durch mindestens einen CMP-Schritt mit nachfolgender Reinigung mittels bekannter Techniken der Halbleiterherstellung entfernt. Die weitere Prozessführung und Fertigstellung erfolgt gemäß dem Stand der Technik, wobei die oben genannte Prozessführung zur Bildung von Mehrlagenmetallisierungen auch wiederholt durchgeführt wird.

**[0040]** Bei einem alternativen Ausführungsbeispiel werden die Schichten 50 bis 58 mit einem CVD-verfahren oder einige Schichten mit ALD-Verfahren und andere Schichten mit einem CVD-Verfahren erzeugt.

[0041] Bei einem nächsten Ausführungsbeispiel enthält der Schichtstapel 26 zusätzlich noch eine obere dritte Zwischenschicht, die wie die erste Zwischenschicht 54 aufgebaut ist, sowie eine obere vierte Leitschicht, die wie die erste Leitschicht 52 aufgebaut ist. In diesem Fall werden die Leitschichten und die Zwischenschichten jedoch dünner als an Hand der Figur 2 erläutert ausgeführt. Bei anderen Ausführungsbeispielen werden weitere Zwischenschichten und Leitschichten hinzugefügt, wobei die Schichtdicken der einzelnen Schichten weiter verringert werden. Die letzte Schicht des Schichtstapel ist eine Leitschicht, die an die Leitstruktur grenzt.

[0042] Figur 3 zeigt einen Schichtstapel 26b mit nur einer Zwischenschicht 64. Zunächst werden die oben an Hand der Figur 2 erläuterten Prozessschritte einschließlich des optionalen Degas- und Reinigungsschrittes durchgeführt.

[0043] Danach wird der Wafer, auf dem die Isolierschicht 19b aufgebracht ist, in eine CVD-Kammer eingebracht. Es werden bspw. 1 nm CVD-RuO $_2$  einer Haftschicht 60 und 4 nm einer ersten Leitschicht 62 aus Bis(cyclopentadienyl)ruthenium (II) und O $_2$ -Ar-Gemischen bei bspw. 315 °C abgeschieden. Um zu Beginn RuO $_2$  abzuscheiden, wird anfänglich als Reaktionspartner ein Gasgemisch aus Sauerstoff O $_2$  und Argon mit 90 Prozent Sauerstoff O $_2$  verwendet. Nach Abscheidung von ca. 1 nm RuO $_2$  wird mit O $_2$ /(O $_2$  + Ar) = 22 Prozent reines Ruthenium mit einem spezifischen elektrischen Widerstand p =  $13\mu\Omega$ cm abgeschieden.

[0044] Der Wafer wird dann in eine weitere CVD-Kammer transportiert, bspw. in eine der zuerst benutzten CVD-Kammer benachbarte Kammer derselben Anlage. In der weiteren Kammer werden bspw. 3 nm CVD-TiN einer Zwischenschicht 64 aus Tetrakis(dimethylaminotitan) bei bspw. 350 °C und bspw. 4 Torr Gesamtdruck direkt auf der ersten Leitschicht 62 abgeschieden. Ein optionaler nachfolgender N<sub>2</sub>/H<sub>2</sub>-Plasma-Schritt (z. B. erzeugt durch Einkopplung einer HF-Spannung von 13,56 MHz, und einer Leistung von bspw. 5 W/cm²) dient zur Verdichtung und Stabilisierung der Schicht.

[0045] Danach wird der Wafer wieder in die zuerst genutzte CVD-Kammer oder in eine andere CVD-Kammer transportiert. Hier wird eine bspw. 5 nm starke CVD-Ru zweite Leitschicht 66 bei den gleichen Prozessbedingungen wie die erste Leitschicht 62 abgeschieden. Die zweite Leitschicht 66 hat wie die anderen mit einem ALD-bzw. CVD-Verfahren abgeschiedenen Schichten eine im

40

wesentlichen gleichbleibende Schichtdicke mit Dickeschwankungen kleiner als 10 Prozent bezogen auf den mittleren Schichtdickewert dieser Schicht.

[0046] Nach dem Erzeugen der zweiten Leitschicht 66 wird der Wafer bzw. das Substrat aus der Multikammeranlage zur Prozess-Station für elektrolytische Cu-Abscheidungen transportiert, wo sich die oben an Hand der Figur 2 erläuterten Prozessschritte anschließen, d.h. insbesondere elektrolytische Abscheidung einer bspw. 250 nm dicken Kupferschicht 68 für eine Leitbahn und/oder für eine Viafüllung, die Temperung und die weitere Bearbeitung.

**[0047]** Bei einem alternativen Ausführungsbeispiel werden die Schichten 60 bis 66 mit einem ALD-Verfahren oder einige Schichten mit CVD-Verfahren und andere Schichten mit einem ALD-Verfahren erzeugt.

[0048] Figur 4 zeigt einen Schichtstapel 78 zur Auskleidung eines Wolframkontaktes 92, der Teil der ersten Metallisierungslage ist, die unmittelbar benachbart zu einem einkristallinen Halbleitersubstrat liegt. Die Figur 4 gilt für einen Schichtstapel 78 an einer Seitenwand des Kontaktes 92, wobei der Schichtstapel 78 an ein Dielektrikum 80 grenzt, das aus einem elektrisch isolierenden Material besteht. Jedoch befindet sich ein dem Schichtstapel 78 identischer Schichtstapel auch am Boden des Wolframkontaktes, wobei jedoch an Stelle des Dielektrikums 80 das Halbleitersubstrat liegt, ggf. versehen mit einer dünnen Silizidschicht.

**[0049]** Es werden die der Erzeugung des Schichtstapel 78 vorhergehenden Prozessschritte zur Herstellung mikroelektronischer Bauelemente auf entsprechenden Substraten wie z. B. Siliziumwafern durchgeführt. Bspw. werden eine Vielzahl von Transistoren eines Prozessors oder eines Halbleiterspeichers erzeugt, z.B. eines flüchtig speichernden RAM (Random Access Memory) oder eines nicht flüchtig speichernden Halbleiterspeichers.

[0050] Zum Erzeugen der untersten Metallisierungslage werden bspw. 20 nm Siliziumnitrid SiN sowie bspw. 600 nm Isolationsschicht 80 aus BPSG (BorPhosphor SilikatGlas) und/oder TEOS-SiO2 (Tetra Ethyl Ortho Silikat) und thermisches Verfließen bei Temperaturen größer als 600 °C mittels bekannter Techniken der Halbleiterherstellung abgeschieden. Es folgt eine Planarisierung des Dielektrikums 80 durch Chemisch-Mechanisches Polieren (CMP) oder auf andere Art mittels bekannter Techniken der Halbleiterherstellung.

[0051] Danach werden Kontaktlöcher und/oder sogenannte lokale Verbindungen (local interconnects), d.h. von Gräben mit geringer lateraler Reichweite von bspw. kleiner als 10 Mikrometer, durch bekannte Abfolgen von Belackung, lithographische Belichtung und Erzeugung von Lackmasken, plasmaunterstützte Ätzschritte und Lackstripp-Verfahren mittels bekannter Techniken der Halbleiterherstellung erzeugt. In einem anschließenden Reinigungsschritt werden bspw. physikalisch oder nasschemisch mittels bekannter Techniken der Halbleiterherstellung die so geschaffenen Kontaktlöcher bzw. Gräben gesäubert.

[0052] Danach wird der das Dielektrikum 80 tragende Wafer bspw. in eine Multikammeranlage zur Abscheidung von metallischen Schichten mit Grundvakuum von besser als 1 Torr bzw. 133 Pa eingebracht. Es folgt ein optionaler Degas-Schritt, z.B. durch Argon-Plasma-Sputtern.

[0053] Der Wafer wird in eine ALD-Kammer transportiert, wo bspw. 1 nm ALD RuO<sub>2</sub> einer Haftschicht 82 und bspw. 3 nm einer ersten Leitschicht 84 aus ALD Ru abgeschieden. Es werden die gleichen Prozessbedingungen wie beim Erzeugen der Haftschciht 50 bzw. der ersten Leitschicht 52 verwendet.

**[0054]** Danach wird der Wafer in eine weitere ALD-Kammer transportiert, wo 2 nm ALD TaN einer Zwischenschicht 86 auf der ersten Leitschicht 84 abgeschieden werden, bspw. unter den gleichen Prozessbedingungen wie beim Erzeugen der Zwischenschicht 54.

[0055] Nach dem Transfer des Wafers in eine ALD-CVD-Kammer erfolgt die Abscheidung von 115 nm Wolfram zur Kontaktauffüllung durch bspw.:

- Spülen mit 20 sccm (Standard Kubikzentimeter)

Silan SiH<sub>4</sub> Fluss bei 370 °C für 15 Sekunden bei p

= 10 Torr bzw. 1333 Pa,

- Abscheiden einer zweiten Leitschicht 88 aus bspw.

nm ALD W mit Hilfe von alternierenden Wolframhexafluorid WF<sub>6</sub>- und Silan SiH<sub>4</sub>-Pulsen sowie zwischengelagerten N<sub>2</sub>-Purge-Pulsen, von bspw. fünf Sekunden bei bspw. 370 °C,

- Abscheiden einer Hilfsschicht 90 aus bspw. 10 nm W-CVD mit Hilfe von Silan SiH<sub>4</sub> (wobei der Silangasfluss bspw. 10 sccm beträgt), Argon Ar (bspw. 130 sccm), molekularem Wasserstoff H<sub>2</sub> (bspw. 120 sccm) und Wolframhexafluorid WF<sub>6</sub> (bspw. 30 sccm) bei bspw. 370 °C für bspw. 8 Sekunden bei einem Druck von bspw. p = 10 Torr bzw. 1333 Pa,

- Abscheiden der Kontakthauptfüllung 92 aus bspw. 100 nm W-CVD unter Verwendung von Argon Ar (bspw. 350 sccm), molekularem Wasserstoff H<sub>2</sub> (bspw. 1700 sccm) und Wolframhexafluorid WF<sub>6</sub> (bspw. 330 sccm) bei bspw. 370 °C für bspw. 30 Sekunden bei einem Druck von bspw. p = 80 Torr bzw. 10664 Pa.

- [5056] Danach werden die Wolfram-Durchkontaktierungen durch Entfernen von Teilen des Wolframs W, der Mehrschichtbarriere und des Dielektrikums 80 in mindestens einem CMP-Schritt mit nachfolgender Reinigung erzeugt. Es folgt die weitere Bearbeitung wie in den obigen Beispielen beschrieben oder gemäß dem Stand der Technik.

[0057] Erläutert wurde unter anderem eine integrierte Schaltungsanordnung 10, die eine elektrisch leitfähige Leitstruktur 16, 22 aus Kupfer oder einer Kupferlegierung enthält. An einer Seitenwand der Leitstruktur 16, 22 befindet sich ein Schichtstapel 32, der mindestens drei Schichten enthält. Trotz sehr dünner Schichten in dem Schichtstapel 32 lässt sich eine hohe Barrierewirkung

15

30

35

40

45

50

55

gegen Kupferdiffusion verbunden mit einer hohen elektrischen Leitfähigkeit erreichen, wie sie für eine elektrolytische Kupferabscheidung mit Außenstrom benötigt wird.

[0058] Bei den erläuterten Ausführungsbeispielen sind weitere Schichten zwischen den erläuterten Schichten nicht vorhanden, abgesehen von sich ggf. bildenden binären Grenzschichten zwischen benachbarten Schichten. Jedoch werden bei anderen Ausführungsbeispielen weitere Schichten zwischen den erläuterten Schichten angeordnet, insbesondere Schichten mit Schichtdicken kleiner als 6 nm.

### Patentansprüche

Integrierte Schaltungsanordnung (10), mit einer elektrisch leitfähigen Leitstruktur (59), mit einem zwischen der Leitstruktur (59) und einem Dielektrikum (19) an einer Seitenwand der Leitstruktur (59) angeordneten Schichtstapel (26), der in der folgenden Reihenfolge mit zunehmendem Abstand vom Dielektrikum (19) enthält:

eine elektrisch leitfähige erste Leitschicht (52, 62, 84) mit einer Schichtdicke im Bereich von 5 Angström bis 60 Angström,

wobei die erste Leitschicht (52, 62, 84) aus einem ersten Material besteht.

eine elektrisch leitfähige erste Zwischenschicht (54, 64, 86) mit einer Schichtdicke im Bereich von 2 Angström bis 30 Angström,

wobei die erste Zwischenschicht (54, 64, 86) aus einem anderen Material als die erste Leitschicht (52, 62, 84)besteht,

und wobei die erste Zwischenschicht (54, 64, 86) einen größeren spezifischen elektrischen Widerstand als die erste Leitschicht (52, 62, 84) hat.

eine elektrisch leitfähige zweite Leitschicht (56, 66, 88) mit einer Schichtdicke im Bereich von 5 Angström bis 60 Angström,

wobei die zweite Leitschicht (56, 66, 88) aus einem anderen Material als die erste Zwischenschicht (54, 64, 86) besteht, und wobei die zweite Leitschicht (56, 66, 88) einen kleineren spezifischen elektrischen Widerstand als die erste Zwischenschicht (54, 64, 86) hat.

- Schaltungsanordnung (10) nach Anspruch 1, dadurch gekennzeichnet, dass die Leitschichten (52, 56) jeweils eine Schichtdicke im Bereich von 10 Angström bis 60 Angström haben, und dass die erste Zwischenschicht (54, 64, 86) eine Schichtdicke im Bereich von 2,5 Angström bis 30 Angström hat.

- 3. Schaltungsanordnung nach Anspruch 1, gekennzeichnet durch eine zwischen der Leitstruktur (59)

und der zweiten Leitschicht (56) angeordnete elektrisch leitfähige zweite Zwischenschicht (57) des Schichtstapels (26),

wobei die zweite Zwischenschicht (57) aus einem anderen Material als die zweite Leitschicht (56) besteht,

und wobei die zweite Zwischenschicht (57) einen größeren spezifischen elektrischen Widerstand als die zweite Leitschicht (56) hat,

und **durch** eine zwischen der zweiten Zwischenschicht (57) und der Leitstruktur (59) angeordnete elektrisch leitfähige dritte Leitschicht (58) des Schichtstapels (26),

wobei die dritte Leitschicht (58) aus einem anderen Material als die zweite Zwischenschicht (57) besteht, und wobei die dritte Leitschicht (58) einen kleineren spezifischen elektrischen Widerstand als die zweite Zwischenschicht (57) hat.

- Schaltungsanordnung (10) nach Anspruch 3, dadurch gekennzeichnet, dass die Leitschichten (52, 56, 58) jeweils eine Schichtdicke im Bereich von 5 Angström bis 50 Angström haben, und dass die Zwischenschichten (54, 57) jeweils eine Schichtdicke im Bereich von 2 Angström bis 25 Angström haben.

- Schaltungsanordnung (10) nach Anspruch 3, gekennzeichnet durch

eine zwischen der Leitstruktur (59) und der dritten Leitschicht (58) angeordnete elektrisch leitfähige dritte Zwischenschicht des Schichtstapels (26), wobei die dritte Zwischenschicht aus einem anderen Material als die dritte Leitschicht (58) besteht, und wobei die dritte Zwischenschicht einen größeren spezifischen elektrischen Widerstand als die dritte Leitschicht (58) hat,

und **durch** eine zwischen der dritten Zwischenschicht und der Leitstruktur (59) angeordnete elektrisch leitfähige vierte Leitschicht des Schichtstapels (26),

wobei die vierte Leitschicht aus einem anderen Material als die dritte Zwischenschicht besteht, und wobei die vierte Leitschicht einen kleineren spezifischen elektrischen Widerstand als die dritte Zwischenschicht hat.

- 6. Schaltungsanordnung nach Anspruch 5, dadurch gekennzeichnet, dass die Leitschichten (52, 56, 58) jeweils eine Schichtdicke im Bereich von 5 Angström bis 40 Angström haben, und dass die Zwischenschichten (54, 57) jeweils eine Schichtdicke im Bereich von 2 Angström bis 25 Angström haben.

- Schaltungsanordnung (10) nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die Leitstruktur (59, 68) mindestens 50 Atomprozent Kupfer enthält,

und dass das Material mindestens einer Zwischen-

20

25

35

40

45

50

schicht (54, 57) oder aller Zwischenschichten eine Kupferdiffusionsbarriere ist.

15

- 8. Schaltungsanordnung (10) nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass der spezifische elektrische Widerstand des Materials mindestens einer Leitschicht (52, 56, 58) kleiner als 50  $\mu\Omega$ cm ist.

- Schaltungsanordnung (10) nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die erste Leitschicht (52, 62, 84) aus Ruthenium besteht oder Ruthenium enthält.

- Schaltungsanordnung (10) nach Anspruch 9, dadurch gekennzeichnet, dass zwischen der ersten Leitschicht (52, 62, 84) und dem Dielektrikum (19, 19b) eine elektrisch leitfähige Oxidschicht (50, 60, 82) angeordnet ist, insbesondere eine Rutheniumoxidschicht.

- **11.** Schaltungsanordnung (10) nach Anspruch 10, **dadurch gekennzeichnet, dass** die Oxidschicht (50, 60, 82) eine Schichtdicke im Bereich von 5 Angström bis 20 Angström hat.

- 12. Schaltungsanordnung (10) nach einem der Ansprüche 1 bis 8, dadurch gekennzeichnet, dass die erste Leitschicht (52, 62, 84) eines der folgenden Materialien enthält oder aus einem dieser Materialien besteht: Ruthenium, Wolfram, Rhodium, Rhenium, Molybdän.

- 13. Schaltungsanordnung (10) nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass mindestens eine Zwischenschicht (54, 57, 64, 86) oder alle Zwischenschichten eines der folgenden Materialien enthält oder aus einem der folgenden Materialien besteht:

Tantal, Tantalnitrid, Tantalkarbid, Tantalkarbonitrid, Tantalsilizonitrid,

Titannitrid, Titankarbid, Titankarbonitrid, Titansilizonitrid,

Wolframnitrid, Wolframkarbid, Wolframkarbonitrid, Wolframsilizonitrid,

Aluminium, Chrom, Nickel, Kobalt, Kohlenstoff, oder dass die Zwischenschicht (54, 57, 64, 86) eine Barriereschicht gegen Kupferdiffusion ist.

14. Schaltungsanordnung (10) nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass mindestens eine oder alle der von der ersten Leitschicht (52, 62, 84) verschiedenen Leitschichten (56, 58, 66, 88) eines der folgenden Materialien enthält oder aus einem der folgenden Materialien besteht:

Ruthenium, Wolfram, Rhodium, Rhenium, Molvhdän

Kupfer, Silber, Gold, Palladium, Platin.

- 5 15. Schaltungsanordnung (10) nach einem der Ansprüche 1 bis 8, dadurch gekennzeichnet, dass die erste Leitschicht (52) aus Ruthenium besteht, die erste Zwischenschicht (54) aus Tantalnitrid besteht.

- und dass die zweite Leitschicht (56) aus Ruthenium besteht.

- 16. Schaltungsanordnung (10) nach Anspruch 15, gekennzeichnet durch eine zwischen der Leitstruktur (59) und der zweiten Leitschicht (56) angeordnete zweite Zwischenschicht (57) des Schichtstapels (26) aus Tantalnitrid, und durch eine zwischen der zweiten Zwischenschicht (57) und der Leitstruktur (59) angeordnete dritte Leitschicht (58) des Schichtstapels (26) aus Ruthenium.

- 17. Schaltungsanordnung (10) nach einem der Ansprüche 1 bis 8, dadurch gekennzeichnet, dass die erste Leitschicht (62) aus Ruthenium besteht, die erste Zwischenschicht (64) aus Titannitrid besteht, und dass die zweite Leitschicht (66) aus Ruthenium besteht.

- 30 18. Schaltungsanordnung (10) nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die der Leitstruktur nächste Leitschicht des Schichtstapels aus einem anderen Material als die Leitstruktur besteht.

- 19. Schaltungsanordnung (10) nach einem der Ansprüche 1 bis 8, dadurch gekennzeichnet, dass die erste Leitschicht (84) aus Ruthenium besteht, die erste Zwischenschicht (86) aus Tantalnitrid oder Titannitrid besteht, und dass die zweite Leitschicht (88) aus Wolfram besteht.

- 20. Schaltungsanordnung (10) nach Anspruch 19, dadurch gekennzeichnet, dass die Leitstruktur (92) aus Wolfram besteht oder Wolfram enthält.

- 21. Verfahren zum elektrolytischen Abscheiden einer Kupfer-Leitstruktur (59, 68) in einer integrierten Schaltungsanordnung (10) nach einem der vorhergehenden Ansprüche, mit den Schritten:

Erzeugen des Schichtstapels (26, 26b), Verwenden der zuletzt erzeugten Leitschicht (58, 66) des Schichtstapels (26, 26b) für eine elektrolytische Abscheidung der Leitstruktur (59, 68), wobei die Leitstruktur (59, 68) mindestens 50 Atomprozent Kupfer enthält.

**22.** Verfahren nach Anspruch 21, **dadurch gekennzeichnet**, **dass** die Abscheidung mindestens einer Leitschicht (52, 56) mindestens einmal unterbrochen wird,

dass nach der Unterbrechung ein Temperschritt durchgeführt wird,

und dass die Abscheidung der Leitschicht (52, 56) nach dem Temperschritt fortgesetzt wird ohne dass zwischenzeitlich andere Materialien auf dem bereits abgeschiedenen Teil der Leitschicht (52, 56) abgeschieden werden.

23. Verfahren nach Anspruch 22, dadurch gekennzeichnet, dass die Abscheidung mindestens einer Leitschicht (52, 56) mindestens einmal unterbrochen wird,

dass nach der Unterbrechung für eine Zeitdauer kleiner als 20 Sekunden ein Plasma gezündet wird oder dass nach der Unterbrechung für eine Zeitdauer kleiner als 20 Sekunden ein Rücksputterschritt durchgeführt wird,

und dass nach dem Plasmalöschen bzw. nach dem Rücksputterschritt die Abscheidung der Leitschicht (52, 56) fortgesetzt wird ohne dass zwischenzeitlich andere Materialien auf dem bereits abgeschiedenen Teil der Leitschicht (52, 56) abgeschieden werden.

24. Verfahren nach einem der Ansprüche 21 bis 23, dadurch gekennzeichnet, dass die zuletzt erzeugte Leitschicht (58, 66) des Schichtstapels kupferfrei ist oder weniger als 10 Atomprozent Kupfer enthält und an die Leitstruktur angrenzt.

10

20

25

30

35

40

45

50

55

Nummer der Anmeldung

|                                                    | EINSCHLÄGIGE                                                                                                                                                                                                                 |                                                                                                                             |                                                                                               |                                                                               |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|

| Kategorie                                          | Kennzeichnung des Dokum<br>der maßgebliche                                                                                                                                                                                   | nents mit Angabe, soweit erforderlich,<br>en Teile                                                                          | Betrifft<br>Anspruch                                                                          | KLASSIFIKATION DER<br>ANMELDUNG (IPC)                                         |  |  |

| Х                                                  | US 5 942 799 A (DAN<br>24. August 1999 (19<br>* das ganze Dokumen                                                                                                                                                            | 99-08-24)                                                                                                                   | 1-8,<br>12-14,<br>18,21,24                                                                    | INV.<br>H01L21/768                                                            |  |  |

| X                                                  | WO 01/29893 A (ASM<br>KAI-ERIK; HAUKKA, S<br>AN) 26. April 2001<br>* Seite 8. Zeile 20                                                                                                                                       | AMERICA, INC; ELERS,<br>UVI, P; SAANILA, VILLE,<br>(2001-04-26)<br>- Seite 11, Zeile 23 *<br>1 - Seite 18, Zeile 5 *        | 12-17,2                                                                                       | 1                                                                             |  |  |

| <                                                  | 21. Januar 2003 (20                                                                                                                                                                                                          | CATA THOMAS J ET AL) 03-01-21) - Spalte 6, Zeile 34 *                                                                       | 1-4,7,8                                                                                       |                                                                               |  |  |

| X                                                  | US 6 500 761 B1 (WA<br>31. Dezember 2002 (<br>* Spalte 9, Zeile 3<br>61; Abbildungen 7,8                                                                                                                                     | 2002-12-31)<br>0 - Spalte 11, Zeile                                                                                         | 1-8,13,<br>18,21-2                                                                            |                                                                               |  |  |

| A                                                  | US 2004/155348 A1 (<br>12. August 2004 (20<br>* das ganze Dokumen                                                                                                                                                            | 1-18                                                                                                                        | RECHERCHIERTE<br>SACHGEBIETE (IPC)                                                            |                                                                               |  |  |

| A                                                  | US 2004/051117 A1 (<br>18. März 2004 (2004<br>* das ganze Dokumen                                                                                                                                                            |                                                                                                                             | 9-12,<br>14-17,19                                                                             | 9                                                                             |  |  |

| A                                                  | US 2002/048937 A1 (<br>25. April 2002 (200<br>* Absätze [0030] -                                                                                                                                                             | 2-04-25)                                                                                                                    | 1-4,22,                                                                                       |                                                                               |  |  |

| Dervo                                              | rliegende Recherchenbericht wu                                                                                                                                                                                               | rde für alle Patentansprüche erstellt                                                                                       | _                                                                                             |                                                                               |  |  |

|                                                    | Recherchenort                                                                                                                                                                                                                | Abschlußdatum der Recherche                                                                                                 | <u> </u>                                                                                      | Prüfer                                                                        |  |  |

|                                                    | Den Haag                                                                                                                                                                                                                     | 9. August 2006                                                                                                              | Plo                                                                                           | oner, G                                                                       |  |  |

| X : von<br>Y : von<br>ande<br>A : tech<br>O : nich | ATEGORIE DER GENANNTEN DOKU<br>besonderer Bedeutung allein betracht<br>besonderer Bedeutung in Verbindung<br>eren Veröffentlichung derselben Kateg<br>nologischer Hintergrund<br>tschriftliche Offenbarung<br>schenliteratur | JMENTE T : der Erfindung zur E : ätteres Patentdol et nach dem Anmel mit einer D : in der Anmeldun orie L : aus anderen Grü | grunde liegende<br>kument, das jedo<br>dedatum veröffe<br>g angeführtes Do<br>nden angeführte | Theorien oder Grundsätze<br>och erst am oder<br>ntlicht worden ist<br>okument |  |  |

## ANHANG ZUM EUROPÄISCHEN RECHERCHENBERICHT ÜBER DIE EUROPÄISCHE PATENTANMELDUNG NR.

EP 06 11 3643

In diesem Anhang sind die Mitglieder der Patentfamilien der im obengenannten europäischen Recherchenbericht angeführten Patentdokumente angegeben.

Die Angaben über die Familienmitglieder entsprechen dem Stand der Datei des Europäischen Patentamts am Diese Angaben dienen nur zur Unterrichtung und erfolgen ohne Gewähr.

09-08-2006

| Im Rechercher<br>ngeführtes Pater |         | Datum der<br>Veröffentlichung |                            | Mitglied(er) der<br>Patentfamilie |                         | Datum der<br>Veröffentlichung                                 |

|-----------------------------------|---------|-------------------------------|----------------------------|-----------------------------------|-------------------------|---------------------------------------------------------------|

| US 594279                         | 9 A     | 24-08-1999                    | KEIN                       | NE                                |                         |                                                               |

| WO 012989                         | 3 A     | 26-04-2001                    | AU<br>EP<br>JP             | 1221178                           | A<br>A1<br>T            | 30-04-200<br>10-07-200<br>19-08-200                           |

| US 650891                         | 9 B1    | 21-01-2003                    | CN<br>EP<br>JP<br>TW<br>WO | 001001                            | A<br>A2<br>T<br>B<br>A2 | 20-04-200<br>03-09-200<br>17-06-200<br>11-05-200<br>01-08-200 |

| US 650076                         | 1 B1    | 31-12-2002                    | JP                         | 2003203878                        | Α                       | 18-07-200                                                     |

| US 200415                         | 5348 A1 | 12-08-2004                    | KEII                       | NE                                |                         |                                                               |

| US 200405                         | 1117 A1 | 18-03-2004                    | KEIN                       | NE                                |                         |                                                               |

| US 200204                         | 8937 A1 | 25-04-2002                    | US                         | 6316353                           | B1                      | 13-11-200                                                     |

**EPO FORM P0461**

Für nähere Einzelheiten zu diesem Anhang : siehe Amtsblatt des Europäischen Patentamts, Nr.12/82