| (19) | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets                                                                                                        | (11) EP 1 736 751 A1                                                                                                                                                                                                                                 |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| (12) | EUROPEAN PATE                                                                                                                                                                          |                                                                                                                                                                                                                                                      |  |  |  |  |

| (43) | Date of publication:<br>27.12.2006 Bulletin 2006/52                                                                                                                                    | (51) Int Cl.:<br><i>G01J 3/28</i> <sup>(2006.01)</sup>                                                                                                                                                                                               |  |  |  |  |

| (21) | Application number: 06253186.8                                                                                                                                                         |                                                                                                                                                                                                                                                      |  |  |  |  |

| (22) | Date of filing: 20.06.2006                                                                                                                                                             |                                                                                                                                                                                                                                                      |  |  |  |  |

| (84) | Designated Contracting States:<br>AT BE BG CH CY CZ DE DK EE ES FI FR GB GR<br>HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI<br>SK TR<br>Designated Extension States:<br>AL BA HR MK YU | <ul> <li>(72) Inventors:</li> <li>Kageyama, Mitsuaki c/o Hamamatsu Photonics K. K.</li> <li>Hamamatsu-shi, Shizuoka 435-8558 (JP)</li> <li>Mizuno, Seiichiro c/o Hamamatsu Photonics K. K.</li> <li>Hamamatsu-shi, Shizuoka 435-8558 (JP)</li> </ul> |  |  |  |  |

| . ,  | Priority: 20.06.2005 JP 2005179466<br>Applicant: HAMAMATSU PHOTONICS K.K.<br>Hamamatsu-shi, Shizuoka-ken 435-8558 (JP)                                                                 | <ul> <li>(74) Representative: Frost, Alex John</li> <li>Boult Wade Tennant,</li> <li>Verulam Gardens</li> <li>70 Gray's Inn Road</li> <li>London WC1X 8BT (GB)</li> </ul>                                                                            |  |  |  |  |

# (54) Image sensor

(57) An image sensor 20A contains a photodiode array portion 21, a signal processor 22, a switching instruction part 23A and a control part 24A. Each switch  $SW_n$  is provided between the corresponding photodiode  $PD_n$  and the common output line L, and instructed to carry out the switching operation by the switching instruction part 23A so as to be closed, whereby the charges accumulated in the junction capacitance portion of the photodiode  $PD_n$  are output to the common output line L. On

the basis of the instruction from the switching instruction part 23A, the N switches SW<sub>1</sub> to SW<sub>N</sub> carry out the switching operation so that the N switches SW<sub>1</sub> to SW<sub>N</sub> are set to the close state in the different periods and the interval at which each switch SW<sub>n</sub> is set to the close state is equal to an integral multiple of a base period. As described above, the charge accumulation time of each of the N photodiodes PD<sub>1</sub> to PD<sub>N</sub> is set to an integral multiple of the base period.

Fig.2

#### Description

#### BACKGROUND OF THE INVENTION

#### Field of the Invention

**[0001]** The present invention relates to an image sensor containing plural photodiodes.

#### Related Background of the Invention

**[0002]** An image sensor containing plural photodiodes is used for a spectroscopic device, for example. In the spectroscopic device, light in some wavelength band which is output from a light source is made incident to a sample, light which is a part of the incident light and transmitted through the sample is spectroscopically separated by a spectroscope, and then the spectroscopically separated light beams having respective wavelengths are detected by the image sensor. In such a spectroscopic device, it is common that the intensity spectrum  $I(\lambda)$  of light output from the light source and the detecting sensitivity spectrum  $D(\lambda)$  of each photodiode contained in the image sensor are not flat in wavelength bands used for spectroscopic measurements.

**[0003]** Furthermore, the photodiode generates charges whose amount corresponds to the amount of light received, and accumulates the thus generated charges into a junction capacitance portion. When the junction capacitance portion is electrically connected to another circuit, the charges which have been accumulated in the junction capacitance portion until then are transmitted to the circuit concerned. However, the amount of charges to be accumulated in the junction capacitance portion capacitance portion of the photodiode is limited. When the amount of light received is small, the accumulated charge amount is proportional to the amount of light received is large, the accumulated charge amount is saturated.

**[0004]** As described above, it is required to set the charge accumulation time in the spectroscopic device so that the accumulated charge amount in the junction capacitance portion of the photodiode is not saturated at a wavelength  $\lambda$  at which the product  $(I(\lambda) \cdot D(\lambda))$  with the intensity spectrum  $I(\lambda)$  of light output from the light source and the detecting sensitivity spectrum  $D(\lambda)$  of the photodiode has a peak. An image sensor contained in a spectroscopic device disclosed in Japanese Patent No. 3,572,681 is designed so that the charge accumulation time is set to be as long as possible to the extent that the accumulated charge amount is not saturated at a wavelength  $\lambda$  at which the product  $(I(\lambda) \cdot D(\lambda))$  has a peak, whereby a spectroscopic measurement having high sensitivity can be performed.

#### SUMMARY OF THE INVENTION

[0005] In the spectroscopic device containing the im-

age sensor as disclosed in the above Patent Document 1, it is possible to carry out a high-sensitivity spectroscopic measurement in a wavelength range where the product  $(I(\lambda) \cdot D(\lambda))$  is large. However, in a wavelength range where the product  $(I(\lambda) \cdot D(\lambda))$  is small, noise com-

ponents cannot be disregarded with respect to signal components and thus the sensitivity is low.

**[0006]** The present invention has been implemented to solve the above problem point, and has an object to provide a appartmention double that each perform high

10 provide a spectroscopic device that can perform highsensitivity spectroscopic measurements in each wavelength, and an image sensor suitably used for the spectroscopic device as described above.

**[0007]** An image sensor according to the present invention is characterized by including: (1) N photodiodes  $PD_1$  to  $PD_N$  each of which generates charges whose amount corresponds to the amount of light received; (2) N switches  $SW_1$  to  $SW_N$  that are provided in one-to-one correspondence to the N photodiodes  $PD_1$  to  $PD_N$ , each

20 of the N switches being provided between the corresponding photodiode and a common output line; and (3) a switching instruction part for instructing a switching operation of each of the N switches SW<sub>1</sub> to SW<sub>N</sub>. Furthermore, the switching instruction part sets the respective

<sup>25</sup> N switches  $SW_1$  to  $SW_N$  to a close state in different periods, and instructs the switching operation of each switch  $SW_n$  so that the interval of the close state of each switch  $SW_n$  is equal to an integral multiple of a base period. Here, N represents an integer of 2 or more, and n represents each integer from 1 to N.

**[0008]** In this image sensor, the n-th photodiode  $PD_n$  of the N photodiodes  $PD_1$  to  $PD_N$  and the n-th switch  $SW_n$  of the N switches  $SW_1$  to  $SW_N$  are provided in correspondence with each other. Each switch  $SW_n$  is provided between the corresponding photodiode  $PD_n$  and the common output line, and it carries out the switching operation in response to an instruction from the switching instruction part to be closed, so that the charges accu-

mulated in the junction capacitance portion of the photodiode  $PD_n$  are output to the common output line. On the basis of the instruction from the switching instruction part, the N switches  $SW_1$  to  $SW_N$  are respectively set to the close state in different periods, and also carry out the switching operation so that the interval at which each of

$^{45}$  the switches  ${\rm SW}_{\rm n}$  is set to the close state is equal to an integral multiple of the base period. As described above, the charge accumulation time of each of the N photodiodes  ${\rm PD}_{\rm 1}$  to  ${\rm PD}_{\rm N}$  is set to an integral multiple of the base period.

<sup>50</sup> **[0009]** The switching instruction part preferably contains (a) a shift register for successively outputting each of switching instruction signals  $S_1$  to  $S_N$  for instructing the switching operation of the N switches  $SW_1$  to  $SW_N$ as a value instructing the close state, and (b) N gate <sup>55</sup> circuits  $G_1$  to  $G_N$  that are provided in one-to-one correspondence to the N switches  $SW_1$  to  $SW_N$ . In this case, it is preferable that each gate circuit  $G_n$  inputs the switching instruction signal  $S_n$  output from the shift register and

also inputs a control signal T<sub>n</sub>, whereby when the control signal T<sub>n</sub> is equal to a first value, each gate circuit G<sub>n</sub> directly outputs the switching instruction signal S<sub>n</sub> to the switch SW<sub>n</sub>, and when the control signal  $T_n$  is equal to a second value, each gate circuit Gn outputs the switching instruction signal having a value instructing an open state to the switch  $SW_n$ . It is also preferable that each gate circuit G<sub>n</sub> inputs the switching instruction signal S<sub>n</sub> output from the shift register and also inputs a common control signal  $T_0$ , whereby when the control signal  $T_0$  is equal to a first value, each gate circuit Gn directly outputs the switching instruction signal  $S_n$  to the switch  $SW_n$ , and when the control signal T<sub>o</sub> is equal to a second value, each gate circuit G<sub>n</sub> outputs the switching instruction signal having a value instructing an open state to the switch SW<sub>n</sub>. Each gate circuit G<sub>n</sub> is constructed by a logic circuit such as an AND circuit or the like, and the first value and the second value are set so that one of the values is set to a high level while the other is set to a low level.

**[0010]** When the switching instruction part is constructed as described above, each switching instruction signal  $S_n$  for instructing the switching operation of the switch  $SW_n$  is output from the shift register and input to the gate circuit  $G_n$ . The switching instruction signal supplied from each gate circuit  $G_n$  to the switch  $SW_n$  remains as the switching instruction signal  $S_n$  when the control signal  $T_n$  or the common control signal  $T_0$  is equal to the first value, and the switching instruction signal concerned is set to the value instructing the open state when the control signal  $T_n$  or the common control signal  $T_0$  is equal to the second value. That is, the charge accumulation time of the photodiode PD<sub>n</sub> is set to an integral multiple of the base period on the basis of the control signal  $T_n$  or the common control signal  $T_0$ .

[0011] The image sensor according to the present invention is preferably further provided with a signal processor for accumulating charges input from each photodiode PD<sub>n</sub> through the switch SW<sub>n</sub> and the common output line into a variable capacitance portion whose capacitance value is variable, and outputting the voltage value corresponding to the ratio between the amount of charges accumulated in the variable capacitance portion and the capacitance value of the variable capacitance portion. In this case, the charges output from each photodiode PD<sub>n</sub> through the switch SW<sub>n</sub> to the common output line are input to the signal processor and accumulated in the variable capacitance portion contained in the signal processor, and the voltage value corresponding to the ratio between the amount of charges accumulated in the variable capacitance portion and the capacitance value of the variable capacitance portion is output from the signal processor.

**[0012]** A spectroscopic device according to the present invention is characterized by including: a light source for outputting light; a spectroscope for spectroscopically separating light output from the light source and transmitted through a sample; and the above-described image sensor for receiving light of each wave-

length which is spectroscopically separated by the spectroscope. In the spectroscopic device, light which is a part of light output from the light source and transmitted through the sample is spectroscopically separated by the spectroscope and then received by the image sensor.

<sup>5</sup> spectroscope and then received by the image sensor. [0013] According to the present invention, a high-sensitivity spectroscopic measurement can be performed at each wavelength.

#### 10 BRIEF DESCRIPTION OF THE DRAWINGS

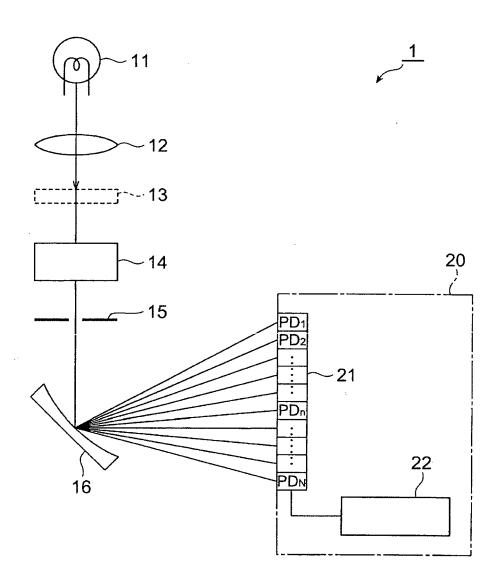

**[0014]** Fig. 1 is a schematic diagram showing the construction of a spectroscopic device 1 according to an embodiment;

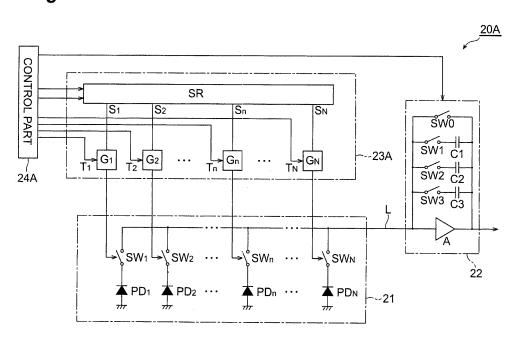

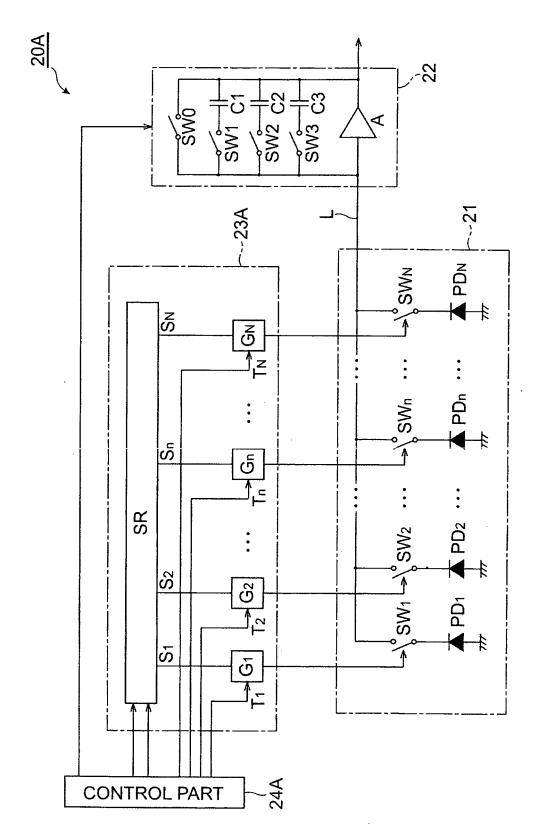

- <sup>15</sup> [0015] Fig. 2 is a diagram showing the construction of an image sensor 20A according to a first embodiment;

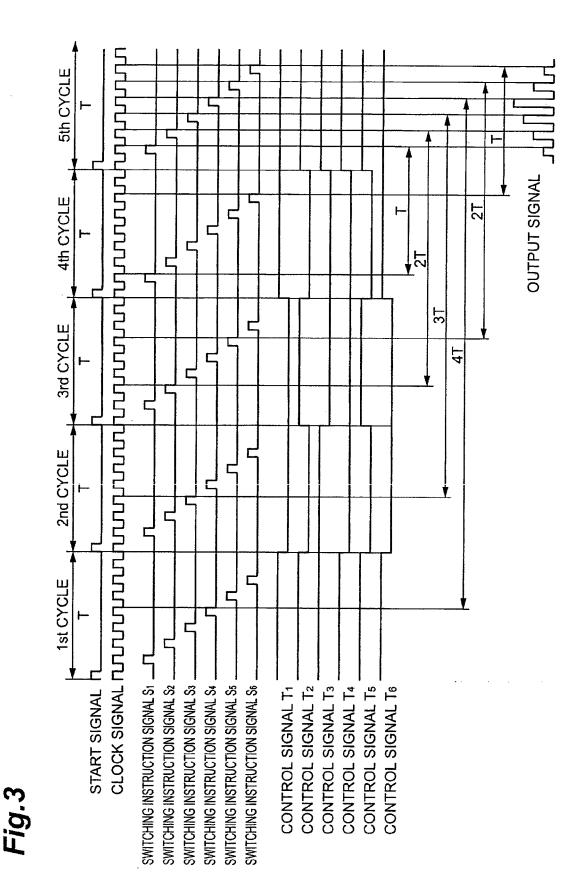

[0016] Fig. 3 is a timing chart showing the operation of the image sensor 20A according to the first embodiment;

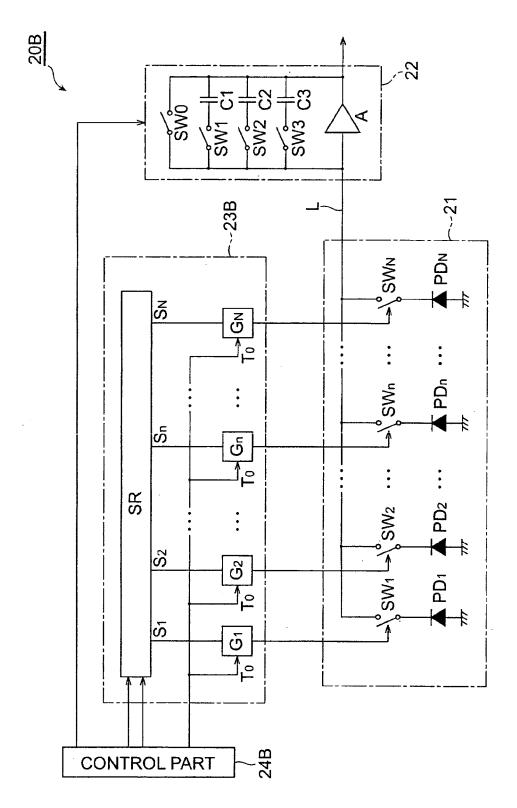

- 20 [0017] Fig. 4 is a diagram showing the construction of an image sensor 20B according to a second embodiment; and

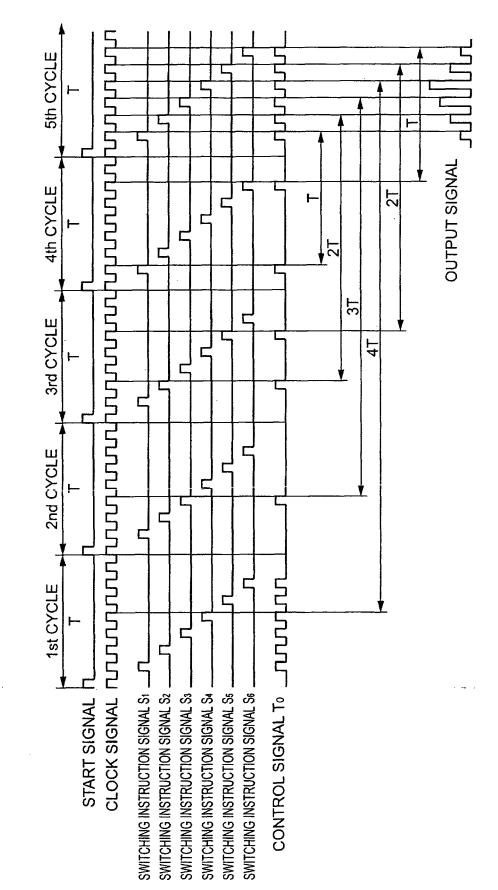

**[0018]** Fig. 5 is a timing chart showing the operation of the image sensor 20B according to the second embodiment.

## DESCRIPTION OF THE PREFERRED EMBODI-MENTS

30 [0019] Preferred embodiments for implementing the present invention will be described in detail with reference to the accompanying drawings. In the description of the drawings, the same elements are represented by the same reference numerals, and overlapping descrip 35 tion thereof is omitted.

[0020] (Embodiment of Spectroscopic Device)

[0021] First, an embodiment of the spectroscopic device according to the present invention will be described. Fig. 1 is a diagram showing the construction of the spectroscopic device 1 according to the embodiment. The

- spectroscopic device 1 shown in Fig. 1 is provided with a light source 11, a lens 12, a shutter 13, a sample cell 14, a slit 15, a diffraction grating 16 and an image sensor 20.

- <sup>45</sup> [0022] The light source 11 outputs light in some wavelength band, for example. It contains a deuterium lamp and a tungsten lamp, for example, and turns on these two lamps at the same time to output light in a broadband. The lens 12 condenses light output from the light source

- 50 11. The shutter 13 is provided at the rear stage of the condensing lens 12, and sets whether light is made incident to the sample cell 14. The sample cell 14 is a cell in which a sample as a measurement target is inserted. Light transmitted through the shutter 13 is made incident

55 to the sample, and light transmitted through the sample is emitted. The diffraction grating 16 is a concave reflection type diffraction grating, and it acts as a spectroscope for inputting light emitted from the sample cell 14 and is

then passed through the slit 15 and spectroscopically separates the light thus input.

**[0023]** The image sensor 20 contains a photodiode array portion 21 and a signal processor 22. The photodiode array portion 21 includes N photodiodes  $PD_1$  to  $PD_N$  arranged, and receives light of each wavelength  $\lambda_n$  spectroscopically separated by the diffraction grating 16 by each photodiode  $PD_n$ . The charge accumulation time in each photodiode  $PD_n$  is variable. The signal processor 22 inputs charges output from each photodiode  $PD_n$  contained in the photodiode array portion 21 and outputs the voltage value corresponding to the charge amount and the charge accumulation time. Here, N represents an integer of 2 or more, and n represents any integer from not less than 1 to not more than N.

**[0024]** In this spectroscopic device 1, light output from the light source 11 is condensed by the lens 12, passed through the shutter 13 and then incident to the sample in the sample cell 14. Light out of the incident light, which is transmitted through the sample in the sample cell 14, is passed through the slit 15 and then spectroscopically separated by the diffraction grating 16. Light of each wavelength  $\lambda_n$ , thus spectroscopically separated is received by the photodiode PD<sub>n</sub> contained in the photodiode PD<sub>n</sub> and the charge accumulation time is output from the signal processor 22.

**[0025]** As described above, the spectrum of the light passed through the sample in the sample cell 14 is measured by the image sensor 20. Furthermore, the spectrum of light when no sample is inserted in the sample cell 14 is also measured by the image sensor 20. A transmission spectrum of the sample in the sample cell 14 is determined from the two spectra. It is preferable to carry out dark current correction on the basis of a result measured by the image sensor 20 in a state that the light source 11 is turned off and the shutter 13 is closed. Furthermore, it is also preferable to carry out background correction on the basis of a result measured by the image sensor 20 in a state that the light source 11 is turned off and the shutter 13 is closed. Furthermore, it is also preferable to carry out background correction on the basis of a result measured by the image sensor 20 in a state that the light source 11 is turned off and the shutter 13 is closed. Furthermore, it is also preferable to carry out background correction on the basis of a result measured by the image sensor 20 in a state that the light source 11 is turned off and the shutter 13 is closed.

[0026] (First Embodiment of Image Sensor)

**[0027]** Next, a first embodiment of the image sensor according to the present invention will be described. Fig. 2 is a diagram showing the construction of an image sensor 20A according to the first embodiment. The image sensor 20A shown in Fig. 2 is suitably used as an image sensor 20 contained in the spectroscopic device 1 shown in Fig. 1, and contains a switching instruction part 23A and a control part 24A in addition to the photodiode array portion 21 and the signal processor 22.

**[0028]** The photodiode array portion 21 contains the N photodiode  $PD_1$  to  $PD_N$  and the N switches  $SW_1$  to  $SW_N$ . With respect to each photodiode  $PD_n$ , the anode terminal thereof is grounded and the cathode terminal thereof is connected to one end of the switch  $SW_n$ , and it generates charges whose amount corresponds to the

amount of light received. Each photodiode  $PD_n$  accumulates the charges into the junction capacitance portion thereof when the switch  $SW_n$  is opened, and outputs the charges to a common output line L when the switch  $SW_n$

$^5\,$  is closed. Each switch  ${\rm SW}_{\rm n}$  is provided between the corresponding photodiode  ${\rm PD}_{\rm n}$  and the common output line L.

[0029] The signal processor 22 contains an amplifier A, capacitors C1 to C3 and switches SW0 to SW3. The

<sup>10</sup> input terminal of the amplifier A is connected to the common output line L. The capacitor C1 and the switch SW1 are connected to each other in series, and provided between the input and output terminals of the amplifier A. The capacitor C2 and the switch SW2 are connected to

<sup>15</sup> each other in series and provided between the input and

output terminals of the amplifier A. The capacitor C3 and the switch SW3 are connected to each other in series, and provided between the input and output terminals of the amplifier A. The switch SW0 is provided between the input and output terminals of the amplifier A.

**[0030]** The capacitors C1 to C3 and the switches SW1 to SW3 constitute the variable capacitance portion whose capacitance value is variable. The capacitance value of the variable capacitance portion is changed in accord-

<sup>25</sup> ance with the switching state of each of the switches SW1 to SW3. When all the switches SW0 to SW3 are closed, each of the capacitors C1 to C3 is discharged. Furthermore, when the switch SW0 is opened, input charges are accumulated in the variable capacitance portion. The sig-

<sup>30</sup> nal processor 22 can accumulate charges input from each photodiode PD<sub>n</sub> through the switch SW<sub>n</sub> and the common output line L into the variable capacitance portion, and output the voltage value corresponding to the ratio between the charge amount accumulated in the variable capacitance portion and the capacitance value of

the variable capacitance portion. **[0031]** The switching instruction part 23A instructs the switching operation of each of the N switches  $SW_1$  to  $SW_N$  contained in the photodiode array portion 21. In particular, the switching instruction part 23A instructs the switching operation of each switch  $SW_n$  so that the N switches  $SW_1$  to  $SW_N$  are set to the close state in different periods, and also the interval at which the respective switches  $SW_n$  are set to the close state is equal to an integral multiple of a base period T.

[0032] Specifically, the switching instruction part 23A contains a shift register SR and N gate circuits G<sub>1</sub> to G<sub>N</sub>. The shift register SR successively outputs the switching instruction signals S<sub>1</sub> to S<sub>N</sub> for instructing the switching operation of the N switches SW<sub>1</sub> to SW<sub>N</sub> as a value instructing the close state on the basis of a start signal and a clock signal output from the control part 24A. Each gate circuit G<sub>n</sub> is provided in correspondence with the switch SW<sub>n</sub>. It inputs the switching instruction signal S<sub>n</sub> output from the shift register SR, and also inputs a control signal T<sub>n</sub> output from the control part 24A. When the control signal T<sub>n</sub> is equal to a first value, each gate circuit G<sub>n</sub> to a first value, big a start signal S<sub>n</sub> to the

switch SW<sub>n</sub>, and when the control signal T<sub>n</sub> is equal to a second value, each gate circuit G<sub>n</sub> outputs the switching instruction signal having a value indicating the open state to the switch SW<sub>n</sub>.

[0033] A proper logic circuit (AND circuit, OR circuit, NAND circuit, NOR circuit or the like) is selected for each gate circuit G<sub>n</sub> in accordance with the polarity of the signal instructing the switching operation of the switch SW<sub>n</sub>, the polarity of the switching instruction signal S<sub>n</sub> output from the shift register SR and the polarity of the control signal T<sub>n</sub> output from the control part 24A. For example, it is assumed that the switch SW<sub>n</sub> is closed when the signal instructing the switching operation of the switch SW<sub>n</sub> is set to a high level, the switching instruction signal S<sub>n</sub> instructs the close state of the switch  $SW_n$  when the switching instruction signal S<sub>n</sub> output from the shift register SR is set to a high level, and the gate circuit G<sub>n</sub> directly outputs the switching instruction signal S<sub>n</sub> to the switch  $SW_n$  when the control signal  $T_n$  output from the control part 24A is set to a high level. In this case, the gate circuit G<sub>n</sub> may be constructed by an AND circuit. This condition is assumed to be satisfied when the operation is described hereunder.

[0034] The control part 24A outputs a signal for controlling the operation of each of the signal processor 22 and the switching instruction part 23A. Specifically, the control part 24A outputs a signal for controlling the switching operation of each of the switches SW0 to SW3 contained in the signal processor 22, outputs the start signal and the clock signal to the shift register SR contained in the switching instruction part 23A, and outputs the control signal T<sub>n</sub> to each gate circuit G<sub>n</sub> contained in the switching instruction part 23A.

[0035] Next, an example of the operation of the image sensor 20A according to the first embodiment will be described. Fig. 3 is a timing chart showing the operation of the image sensor 20A according to the first embodiment. The start signal and the clock signal supplied from the control part 24A to the shift register SR, the switching instruction signals S1 to S6 output from the shift register SR, the control signals  $T_1$  to  $T_6$  supplied from the control part 24A to the gate circuits G1 to G6 and the amount of charges passed through the common output line L and input to the signal processor 22 are shown from the upper side in Fig. 3.

[0036] In this case, the value of N is set to 6. Furthermore, it is assumed that the switching instruction part 23A instructs the switching operation of each switch SW<sub>n</sub> so that the interval at which each switch SW<sub>n</sub> is set to the close state is equal to be one to four times as long as the base period T. The capacitance values of the capacitors C1 to C3 contained in the signal processor 22 may be set to C, 2C and 4C, and the capacitance value of the variable capacitance portion may be set to any one of C, 2C, 3C (=C+2C) and 4C. The following operation is carried out under the control of the control part 24A.

[0037] Each of the start signal and the clock signal supplied from the control part 24A to the shift register SR is a periodic signal whose level is varied at a fixed period. The period of the start signal is represented by T, and the period of the clock signal is shorter than T. In the following description, the period from some rising time of

- the start signal until the next rising time is referred to as 5 "cycle." The time of each cycle is equal to T. Furthermore, the clock signal contains at least N (in this case, N=6) pulses for the period from some falling time of the start signal until the next rising time.

- 10 [0038] The shift register SR is initialized at the rising time of the start signal, and then the switching instruction signals S<sub>1</sub> to S<sub>6</sub> for instructing the switching operation of the respective switches SW1 to SW6 are successively output as a value instructing the close state at each rising 15 time of the subsequent clock signal. That is, in each cycle,

the switching instruction signals S<sub>1</sub> to S<sub>6</sub> output from the shift register SR are successively set to a high level.

- [0039] The control signals T<sub>1</sub> to T<sub>6</sub> supplied from the control part 24A to the gate circuits G1 to G6 are as fol-20 lows. Each of the control signals  $T_1$  and  $T_6$  is set to a high level in a first cycle, to a low level in second and

- third cycles, and to a high level in fourth and fifth cycles. Each of the control signals T<sub>2</sub> and T<sub>5</sub> is set to a high level in the first cycle, to a low level in the second cycle, to a 25 high level in the third cycle, to a low level in the fourth

cycle, and to a high level in the fifth cycle. The control signal T<sub>3</sub> is set to a high level in the first and second cycles, to a low level in the third and fourth cycles, and to a high level in the fifth cycle. Furthermore, the control 30 signal T<sub>4</sub> is set to a high level in the first cycle, to a low

level in the second to fourth cycles and to a high level in the fifth cycle.

[0040] The switching instruction signal output from each gate circuit G<sub>n</sub> to the switch SW<sub>n</sub> is still the switching instruction signal S<sub>n</sub> output from the shift register SR during the cycle in which the control signal T<sub>n</sub> is set to a high level, however, it has a value instructing the open state during the cycle in which the control signal T<sub>n</sub> is set to a low level. That is, the switching instruction signal supplied

40 from each gate circuit G<sub>n</sub> to the switch SW<sub>n</sub> has a value instructing the close state when both the switching instruction signal S<sub>n</sub> output from the shift register SR and the control signal T<sub>n</sub> are set to a high level, and it has a value instructing the open state when any one of the

45 switching instruction signal S<sub>n</sub> and the control signal T<sub>n</sub> is set to a low level.

[0041] Accordingly, the switching instruction signal output from the gate circuit  $G_1$  to the switch SW<sub>1</sub> is still the switching instruction signal S1 output from the shift 50 register SR in the first, fourth and fifth cycles, however, it has a value instructing the open state in the other cycles. The switching instruction signal output from the gate circuit  $\mathsf{G}_2$  to the switch  $\mathsf{SW}_2$  is still the switching instruction signal S2 output from the shift register SR in the first, third and fifth cycles, however, it has a value instructing the open state in the other cycles.

[0042] The switching instruction signal output from the gate circuit G<sub>3</sub> to the switch SW<sub>3</sub> is still the switching

35

**[0043]** The switching instruction signal output from the gate circuit  $G_5$  to the switch  $SW_5$  is still the switching instruction signal  $S_5$  output from the shift register SR in the first, third and fifth cycles, however, it has a value instructing the open state in the other cycles. The switching instruction signal output from the gate circuit  $G_6$  to the switch  $SW_6$  is still the switching instruction signal  $S_6$  output from the shift register SR in the first, fourth and fifth cycles, however, it has a value instruction signal signal output from the first, fourth and fifth cycles, however, it has a value instructing the open state in the other cycles.

**[0044]** Each switch SW<sub>n</sub> contained in the photodiode array portion 21 is closed for some period when the switching instruction signal arriving from the gate circuit  $G_n$  is set to a high level, and opened in another period. In each of the first and fifth cycles, the switches SW<sub>1</sub> to SW<sub>6</sub> are successively closed.

**[0045]** The switch SW<sub>1</sub> is closed when the switching instruction signal S<sub>1</sub> is set to a high level during the fifth cycle, whereby the charges accumulated in the junction capacitance portion of the photodiode PD<sub>1</sub> are output to the signal processor 22 via the common output line L during the period T subsequent to the time when the switching instruction signal S<sub>1</sub> is set to a high level during the preceding fourth cycle. The switch SW<sub>2</sub> is closed when the switching instruction signal S<sub>2</sub> is set to a high level during the junction capacitance portion of the photo-diode PD<sub>2</sub> are output to the signal processor 22 via the common output line L during the time 2T subsequent to the time when the switching instruction signal S<sub>2</sub> is set to a high level during the processor 22 via the common output line L during the time 2T subsequent to the time when the switching instruction signal S<sub>2</sub> is set to a high level during the preceding the preceding third cycle.

**[0046]** The switch SW<sub>3</sub> is closed when the switching instruction signal S<sub>3</sub> is set to a high level during the fifth cycle, whereby the charges accumulated in the junction capacitance portion of the photodiode PD<sub>3</sub> are output to the signal processor 22 via the common output line L during the time 3T subsequent to the time when the switching instruction signal S<sub>3</sub> is set to a high level during the preceding second cycle. The switch SW<sub>4</sub> is closed when the switching instruction signal S<sub>4</sub> is set to a high level during the fifth cycle, whereby the charges accumulated in the junction capacitance portion of the photodiode PD<sub>4</sub> are output to the signal processor 22 via the common output line L during the time 4T subsequent to the time when the switching instruction signal S<sub>4</sub> is set to a high level during the preceding the fifth cycle, signal processor 22 via the common output line L during the time 4T subsequent to the time when the switching instruction signal S<sub>4</sub> is set to a high level during the preceding first cycle.

**[0047]** The switch SW<sub>5</sub> is closed when the switching instruction signal S<sub>5</sub> is set to a high level during the fifth cycle, whereby the charges accumulated in the junction capacitance portion of the photodiode PD<sub>5</sub> are output to

the signal processor 22 via the common output line L during the time 2T subsequent to the time when the switching instruction signal  $S_5$  is set to a high level during the preceding third cycle. The switch SW<sub>6</sub> is closed when the switching instruction signal S<sub>6</sub> is set to a high level during the fifth cycle, whereby the charges accumulated

in the junction capacitance portion of the photodiode PD<sub>6</sub> are output to the signal processor 22 via the common output line L during the period T subsequent to the time <sup>10</sup> when the switching instruction signal S<sub>6</sub> is set to a high

level during the preceding fourth cycle.

[0048] As described above, the charges passed through the common output line L and then input to the processor 22 in the fifth cycle correspond to the charges

accumulated in the junction capacitance portion during the period T with respect to the photodiode PD1, the charges accumulated in the junction capacitance portion

during the time 2T with respect to the photodiode PD<sub>2</sub>, the charges accumulated in the junction capacitance portion during the time 3T with respect to the photodiode PD<sub>3</sub>, the charges accumulated in the junction capacitance portion during the time 4T with respect to the pho-

todiode PD<sub>4</sub>, the charges accumulated in the junction capacitance portion during the time 2T with respect to

the photodiode PD<sub>5</sub>, and the charges accumulated in the junction capacitance portion during the period T with respect to the photodiode PD<sub>6</sub>. As described above, the interval at which each switch SW<sub>n</sub> is set to the close state is equal to an integral multiple of the base period T, whereby the charge accumulation time in each photodi-

ode  $PD_n$  is also equal to an integral multiple of the base period T.

**[0049]** In the fifth cycle, the charges which are passed from each photodiode  $PD_n$  through the switch  $SW_n$  and the common output line L and then input to the signal processor 22 are accumulated in the variable capacitance portion of the signal processor 22, and the voltage value corresponding to the ratio between the amount of charges accumulated in the variable capacitance portion and the capacitance value of the variable capacitance

portion is output from the signal processor 22. The capacitance value of the variable capacitance portion is set in proportion to the charge accumulation time in each photodiode PD<sub>n</sub> for generating charges to be accumu-45 lated.

[0050] That is, when the charges input from the photodiode PD1 are accumulated in the variable capacitance portion, the capacitance value of the variable capacitance portion is set to C. When the charges input from 50 the photodiode PD<sub>2</sub> are accumulated in the variable capacitance portion, the capacitance value of the variable capacitance portion is set to 2C. When the charges input from the photodiode PD<sub>3</sub> are accumulated in the variable capacitance portion, the capacitance value of the varia-55 ble capacitance portion is set to 3C. When the charges input from the photodiode PD<sub>4</sub> are accumulated in the variable capacitance portion, the capacitance value of the variable capacitance portion is set to 4C. When the

35

charges input from the photodiode PD<sub>5</sub> are accumulated in the variable capacitance portion, the capacitance value of the variable capacitance portion is set to 2C. When the charges input from the photodiode PD<sub>6</sub> are accumulated in the variable capacitance portion, the capacitance value of the variable capacitance portion is set to C.

**[0051]** As described above, in the image sensor 20A according to the first embodiment, the interval at which each switch  $SW_n$  is set to the close state is set to an integral multiple of the base period T, whereby the charge accumulation time in each photodiode  $PD_n$  can be set to an integral multiple of the base period T. Accordingly, with respect to each photodiode  $PD_n$ , the charge accumulation time can be changed to the extent that the accumulated charge amount in the junction capacitance portion is not saturated. Accordingly, the spectroscopic device 1 provided with the image sensor 20A as described above can perform high-sensitivity spectroscopic measurements in each wavelength.

**[0052]** Furthermore, with respect to each photodiode  $PD_n$ , by changing the capacitance value of the variable capacitance portion of the signal processor 22 in accordance with the charge accumulation time, the effect caused by the difference in charge accumulation time between the respective photodiodes  $PD_n$  is excluded from the voltage value output from the signal processor 22.

[0053] For example, the setting of the charge accumulating time in each photodiode PD<sub>n</sub> is carried out as follows. First, in the state that the charge accumulation time in each of the photodiodes PD<sub>1</sub> to PD<sub>N</sub> is set as the base period T and the capacitance value of the variable capacitance portion of the signal processor 22 is set to C, when light having excessive intensity is made incident to each photodiode  $\mathsf{PD}_{\mathsf{n}}$  and the accumulated charge amount in the junction capacitance portion of the photodiode  $PD_n$  is saturated, the voltage value  $V_{sat}$  output from the signal processor 22 is determined. Furthermore, in this state, light to be measured is made incident to each photodiode  $PD_n$ , and the voltage value  $V_n$  output from the signal processor 22 is determined. On the basis of the ratio  $(V_{sat}/V_n)$  between the voltage value  $V_{sat}$  and the voltage value  $V_{\mbox{\scriptsize n}},$  it is determined how many times the base period T should be multiplied to achieve the charge accumulation time in the photodiode PD<sub>n</sub>.

[0054] (Second Embodiment of Image Sensor)

**[0055]** Next, a second embodiment of the image sensor according to the present invention will be described. Fig. 4 is a diagram showing the construction of an image sensor 20B according to the second embodiment. The image sensor 20B shown in Fig. 4 is suitably used as the image sensor 20 contained in the spectroscopic device 1 shown in Fig. 1, and it further contains a switching instruction part 23B and a control part 24B in addition to the photodiode array portion 21 and the signal processor 22.

**[0056]** As compared with the image sensor 20A according to the first embodiment shown in Fig. 2, the image

sensor 20B according to the second embodiment shown in Fig. 4 has the same construction with respect to the photodiode array portion 21 and the signal processor 22, however, it is different in that it contains a switching in-

struction part 23B in place of the switching instruction part 23A, and also in that it contains a control part 24B in place of the control part 24A.

[0057] The switching instruction part 23B instructs the switching operation of each of the N switches  $SW_1$  to

SW<sub>N</sub> contained in the photodiode array portion 21. Particularly, the switching instruction part 23B instructs the switching operation of each switch SW<sub>n</sub> so that the N switches SW<sub>1</sub> to SW<sub>N</sub> are set to the close state in different periods, and also the interval at which each switch SW<sub>n</sub> is set to the close state is equal to an integral multiple of

the base period T.

[0058] Specifically, the switching instruction part 23B contains the shift register SR and the N gate circuits G1 to G<sub>N</sub>. On the basis of the start signal and the clock signal 20 output from the control part 24B, the shift register SR successively outputs the switching instruction signals  $S_1$ to S<sub>N</sub> for instructing the switching operation of the respective N switches SW1 to SWN as a value instructing the close state. Each gate circuit G<sub>n</sub> is provided in cor-25 respondence with the switch SW<sub>n</sub>. It inputs the switching instruction signal S<sub>n</sub> output from the shift register SR and also inputs a common control signal T<sub>0</sub> output from the control part 24B. When the control signal  $T_0$  is equal to a first value, each gate circuit  $\boldsymbol{G}_n$  directly outputs the 30 switching instruction signal  $S_n$  to the switch  $SW_n$ , and when the control signal T<sub>0</sub> is equal to a second value, each gate circuit G<sub>n</sub> outputs the switching instruction signal having a value instructing the open state to the switch SW<sub>n</sub>.

<sup>35</sup> [0059] For each gate circuit G<sub>n</sub>, a proper logic circuit (AND circuit, OR circuit, NAND circuit, NOR circuit or the like) is selected in accordance with the polarity of a signal instructing the switching operation of the switch SW<sub>n</sub>, the polarity of the switching instruction signal S<sub>n</sub> output from the shift register SR and the polarity of the control signal T<sub>0</sub> output from the control part 24B. For example, it is assumed that when the signal instructing the switching operation of the switching

switch SW<sub>n</sub> is closed, when the switching instruction signal S<sub>n</sub> output from the shift register SR is set to a high level, the switching instruction signal S<sub>n</sub> instructs the close state of the switch SW<sub>n</sub> and when the control signal T<sub>0</sub> output from the control part 24B is set to a high level, the gate circuit G<sub>n</sub> directly outputs the switching instruction signal S<sub>n</sub> to the switch SW<sub>n</sub>. In this case, the gate circuit G<sub>n</sub> may be constructed by an AND circuit. This condition is satisfied when the operation is described below.

[0060] The control part 24B outputs signals for controlling the operation of the signal processor 22 and the switching instruction part 23B. Specifically, the control part 24B outputs a signal for controlling the switching operation of each of the switches SW0 to SW3 contained

in the signal processor 22, outputs the start signal and the clock signal to the shift register SR contained in the switching instruction part 23B and outputs the common control signal  $T_0$  to each gate circuit  $G_n$  contained in the switching instruction part 23B.

**[0061]** Next, an example of the operation of the image sensor 20B according to the second embodiment will be described. Fig 5 is a timing chart showing the operation of the image sensor 20B according to the second embodiment. The start signal and the clock signal supplied from the control part 24B to the shift register SR, the switching instruction signals S<sub>1</sub> to S<sub>6</sub> output from the shift register SR, the common control signal T<sub>0</sub> supplied from the control part 24B to the signal processor 22 through the common output line L are shown from the upper side in Fig. 5.

**[0062]** In this case, the value of N is set to 6. The switching instruction part 23B instructs the switching operation of each switch  $SW_n$  so that the interval at which each switch  $SW_n$  is set to the close state is set to one to four times of the base period T. The capacitance values of the capacitors C1 to C3 contained in the signal processor 22 are set to C, 2C and 4C, and the capacitance value of the variable capacitance portion is set to any one of C, 2C, 3C (=C+2C) and 4C. The following operation is carried out under the control of the control part 24B.

**[0063]** The start signal and the clock signal supplied from the control part 24B to the shift register SR and the switching instruction signals  $S_1$  to  $S_6$  output from the shift register SR are the same as the first embodiment.

[0064] The common control signal T<sub>0</sub> supplied from the control part 24B to the gate circuits  $G_1$  to  $G_6$  is as follows. In the first and fifth cycles, the control signal T<sub>0</sub> is set to a high level during the period when any one of the switching instruction signals S<sub>1</sub> to S<sub>6</sub> output from the shift register SR is set to a high level, and in the other period, the control signal T<sub>0</sub> is set to a low level. In the second cycle, during the period when the switching instruction signal S<sub>3</sub> output from the shift register SR is set to a high level, the control signal  $T_0$  is set to a high level, and in the other period, the control signal T<sub>0</sub> is set to a low level. In the third cycle, during the period when the switching instruction signal  $S_2$  or  $S_5$  output from the shift register SR is set to high period, the control signal T<sub>0</sub> is set to a high level, and in the other period, the control signal T<sub>0</sub> is set to a low level. In the fourth cycle, during the period when the switching instruction signal S<sub>1</sub> or S<sub>6</sub> output from the shift register SR is set to a high level, the control signal T<sub>0</sub> is set to a high level, and in the other period, the control signal  $T_0$  is set to a low level.

**[0065]** The switching instruction signal output from each gate circuit  $G_n$  to the switch  $SW_n$  is still the switching instruction signal  $S_n$  output from the shift register SR for the period when the control signal  $T_0$  is set to a high level, however, it has a value instructing the open state during the period when the control signal  $T_0$  is set to a low level. That is, the switching instruction signal from each gate

circuit G<sub>n</sub> to the switch SW<sub>n</sub> has a value instructing the close state when both the switching instruction signal S<sub>n</sub> output from the shift register SR and the control signal T<sub>0</sub> are set to a high level, however, it has a value instruct-

ing the open state when any one of the switching instruction signal  $S_n$  and the control signal  $T_0$  is set to a low level. [0066] Accordingly, the switching instruction signal output from the gate circuit  $G_1$  to the switch  $SW_1$  is still the switching instruction signal  $S_1$  output from the shift

register SR in the first, fourth and fifth cycles, however, it has a value instructing the open state in the other cycles. The switching instruction signal output from the gate circuit G<sub>2</sub> to the switch SW<sub>2</sub> is still the switching instruction signal S<sub>2</sub> output from the shift register SR in the first, third

and fifth cycles, however, it has a value instructing the

open state in the other cycles.

[0067] The switching instruction signal output from the gate circuit G<sub>3</sub> to the switch SW<sub>3</sub> is still the switching instruction signal S<sub>3</sub> output from the shift register SR in

20 the first, second and fifth cycles, however, it has a value instructing the open state in the other cycles. The switching instruction signal output from the gate circuit G<sub>4</sub> to the switch SW<sub>4</sub> is still the switching instruction signal S<sub>4</sub> output from the shift register SR in the first and fifth cycles, however, it has a value instruction signal support from the shift register SR in the first and fifth cycles, however, it has a value instruction signal S<sub>4</sub> output from the shift register SR in the first and fifth cycles, however, it has a value instructing the open state in the

<sup>25</sup> however, it has a value instructing the open state in the other cycles.

[0068] The switching instruction signal output from the gate circuit G<sub>5</sub> to the switch SW<sub>5</sub> is still the switching instruction signal S<sub>5</sub> output from the shift register SR in

<sup>30</sup> the first, third and fifth cycles, however, it has a value instructing the open state in the other cycles. The switching instruction signal output from the gate circuit G<sub>6</sub> to the switch SW<sub>6</sub> is still the switching instruction signal S<sub>6</sub> output from the shift register SR in the first, fourth and

<sup>35</sup> fifth cycles, however, it has a value instructing the open state in the other cycles.

**[0069]** Each switch  $SW_n$  contained in the photodiode array portion 21 is closed during the period when the switching instruction signal arriving from the gate circuit

<sup>40</sup>  $G_n$  is set to a high level, and it is opened in the other period. As a result, in the operation of the second embodiment, the switching operation of each switch  $SW_n$  and the operation of the signal processor 22 are the same as the operation of the first embodiment.

<sup>45</sup> [0070] As described above, according to the image sensor 20B according to the second embodiment, by setting the interval of the close state of each switch SW<sub>n</sub> to an integral multiple of the base period T, the charge accumulation time in each photodiode PD<sub>n</sub> can be set to an integral multiple of the base period T, whereby the charge accumulation time can be changed to the extent that the accumulated charge amount in the junction capacitance portion with respect to each photodiode PD<sub>n</sub> is not saturated. Accordingly, the spectroscopic device

<sup>55</sup> 1 having the image sensor 20B as described above can perform high-sensitivity spectroscopic measurement in each wavelength.

[0071] Furthermore, by changing the capacitance val-

15

[0072] Furthermore, as compared with the construction of the image sensor 20A of the first embodiment, in the image sensor 20B of the second embodiment, the common control signal T<sub>0</sub> is supplied from the control part 24B to the N gate circuits G1 to GN, and thus it is sufficient to provide only one wire for the control signal T<sub>0</sub>. Accordingly, the image sensor 20B according to the second embodiment can be miniaturized, and thus manufactured at a low price.

#### Claims

1. An image sensor comprising:

N photodiodes PD<sub>1</sub> to PD<sub>N</sub> each of which generates charges whose amount corresponds to the amount of light received,

N switches  $SW_1$  to  $SW_N$  that are provided in one-to-one correspondence to the N photodiodes PD<sub>1</sub> to PD<sub>N</sub>, each of the N switches being provided between the corresponding photodiode and common output line, N representing an integer of 2 or more, and n representing an integer from not less than 1 to not more than N; and a switching instruction part for instructing the switching operation of each of the N switches SW<sub>1</sub> to SW<sub>N</sub>, wherein

the switching instruction part instructs the switching operation of each switch SWn so that the N switches  $SW_1$  to  $SW_N$  are set to a close state in different periods, and an interval at which each switch state SWn is set to the close state 40 is equal to an integral multiple of a base period.

2. The image sensor according to claim 1, wherein the switching instruction part includes a shift register for successively outputting switching instruction signals S<sub>1</sub> to S<sub>N</sub> for instructing the switch-45 ing operation of each of the N switches SW1 to SWN as a value instructing the close state, and N gate circuits  $G_1$  to  $G_N$  provided in one-to-one correspondence to the N switches  $SW_1$  to  $SW_N$ , wherein each gate circuit G<sub>n</sub> inputs a switching instruction 50 signal S<sub>n</sub> output from the shift register and also inputs a control signal T<sub>n</sub>, and each gate circuit G<sub>n</sub> directly outputs the switching instruction signal S<sub>n</sub> to a switch  $SW_n$  when the control signal  $T_n$  is equal to a first value, and outputs a switching instruction signal hav-55 ing a value instructing an open state to the switch  $SW_n$  when the control signal  $T_n$  is equal to a second value.

- 3. The image sensor according to claim 1, wherein the switching instruction part includes a shift register for successively outputting switching instruction signals S<sub>1</sub> to S<sub>N</sub> for instructing the switching operation of each of the N switches SW<sub>1</sub> to SW<sub>N</sub> as a value instructing the close state, and N gate circuits G<sub>1</sub> to G<sub>N</sub> that are provided in one-toone correspondence to the N switches SW<sub>1</sub> to SW<sub>N</sub>, wherein

- 10 each gate circuit G<sub>n</sub> inputs a switching instruction signal S<sub>n</sub> output from the shift register and also inputs a common control signal To, whereby when the control signal T<sub>0</sub> is equal to a first value, each gate circuit G<sub>n</sub> directly outputs the switching instruction signal  $S_n$  to the switch  $SW_n$ , and when the control signal  $T_0$  is equal to a second value, each gate circuit  $G_n$ outputs the switching instruction signal having a value instructing the open state to the switch SW<sub>n</sub>.

- 20 4. The image sensor according to claim 1, further comprising a signal processor for accumulating charges input from each photodiode PD<sub>n</sub> through the switch SW<sub>n</sub> and the common output line into a variable capacitance portion whose capacitance value is vari-25 able, and outputting the voltage value corresponding to the ratio between the amount of charges accumulated in the variable capacitance portion and the capacitance value of the variable capacitance portion.

- 30 5. A spectroscopic device comprising a light source for outputting light, a spectroscope for spectroscopically separating light output from the light source and transmitted through a sample, and the image sensor according to claim 1 for receiving light of each wavelength which is spectroscopically separated by the 35 spectroscope.

# Fig.1

EP 1 736 751 A1

Fig.5

European Patent Office

# **EUROPEAN SEARCH REPORT**

Application Number EP 06 25 3186

|                                                                                                                                                                | DOCUMENTS CONSIDER                                                                      | ED TO BE RELEVANT                                                                            |                                                                                                                                                                                                |                                            |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|

| Category                                                                                                                                                       | Citation of document with indica<br>of relevant passages                                |                                                                                              | Relevant<br>to claim                                                                                                                                                                           | CLASSIFICATION OF THE<br>APPLICATION (IPC) |  |  |

| X<br>Y                                                                                                                                                         | US 4 674 880 A (SEKI<br>23 June 1987 (1987-06<br>* column 3, line 5 -                   | -23)<br>line 21 *                                                                            | 1,5<br>2-4                                                                                                                                                                                     | INV.<br>G01J3/28                           |  |  |

|                                                                                                                                                                | * column 3, line 30 -<br>* column 4, line 28 -<br>* figures 1,3,4 *                     | line 40 *<br>line 49 *                                                                       |                                                                                                                                                                                                |                                            |  |  |

| Y                                                                                                                                                              | EP 0 355 174 A (HEWLE<br>28 February 1990 (199<br>* column 7, line 28 -<br>* figure 3 * | 0-02-28)                                                                                     | 2,3                                                                                                                                                                                            |                                            |  |  |

| Y                                                                                                                                                              | EP 0 399 057 A (HEWLE<br>28 November 1990 (199<br>* page 4, line 56 - p<br>* figure 3 * | 0-11-28)                                                                                     | 4                                                                                                                                                                                              |                                            |  |  |

|                                                                                                                                                                | -                                                                                       |                                                                                              |                                                                                                                                                                                                |                                            |  |  |

|                                                                                                                                                                |                                                                                         |                                                                                              |                                                                                                                                                                                                | TECHNICAL FIELDS<br>SEARCHED (IPC)         |  |  |

|                                                                                                                                                                |                                                                                         |                                                                                              |                                                                                                                                                                                                | G01J                                       |  |  |

|                                                                                                                                                                |                                                                                         |                                                                                              |                                                                                                                                                                                                |                                            |  |  |

|                                                                                                                                                                |                                                                                         |                                                                                              |                                                                                                                                                                                                |                                            |  |  |

|                                                                                                                                                                |                                                                                         |                                                                                              |                                                                                                                                                                                                |                                            |  |  |

|                                                                                                                                                                |                                                                                         |                                                                                              |                                                                                                                                                                                                |                                            |  |  |

|                                                                                                                                                                |                                                                                         |                                                                                              |                                                                                                                                                                                                |                                            |  |  |

|                                                                                                                                                                |                                                                                         |                                                                                              |                                                                                                                                                                                                |                                            |  |  |

|                                                                                                                                                                | The present search report has been drawn up for all o                                   |                                                                                              | -                                                                                                                                                                                              |                                            |  |  |

| Place of search<br>Munich                                                                                                                                      |                                                                                         | Date of completion of the search<br>26 September 2006 Jac                                    |                                                                                                                                                                                                | Examiner<br>Cquin, Jérôme                  |  |  |

|                                                                                                                                                                |                                                                                         | •                                                                                            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                          |                                            |  |  |

| CATEGORY OF CITED DOCUMENTS<br>X : particularly relevant if taken alone<br>Y : particularly relevant if combined with another<br>document of the same category |                                                                                         | E : earlier patent do<br>after the filing da<br>D : document cited i<br>L : document cited f | T : theory or principle underlying the ir<br>E : earlier patent document, but publis<br>after the filing date<br>D : document cited in the application<br>L : document cited for other reasons |                                            |  |  |

| O : non                                                                                                                                                        | nological background<br>-written disclosure<br>mediate document                         | & : member of the s                                                                          | & : member of the same patent family, corresponding document                                                                                                                                   |                                            |  |  |

# EP 1 736 751 A1

## ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 06 25 3186

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

26-09-2006

| Patent document<br>cited in search report |   | Publication<br>date |                                  | Patent family<br>member(s)                                       |                     | Publication<br>date                                                              |

|-------------------------------------------|---|---------------------|----------------------------------|------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------|

| US 4674880                                | A | 23-06-1987          | JP                               | 61011622                                                         | A                   | 20-01-1980                                                                       |

| EP 0355174                                | A | 28-02-1990          | DE<br>DE<br>ES<br>JP<br>JP<br>US |                                                                  | A<br>B2             | 01-04-1993<br>09-06-1993<br>16-07-1993<br>29-03-1990<br>23-10-2000<br>25-09-1990 |

| EP 0399057                                | A | 28-11-1990          | DE<br>DE<br>ES<br>JP<br>JP<br>US | 68903831<br>68903831<br>2035985<br>3010126<br>3143747<br>5116123 | T2<br>T3<br>A<br>B2 | 21-01-1993<br>15-04-1993<br>01-05-1993<br>17-01-1993<br>07-03-2003<br>26-05-1993 |

FORM P0459

$\stackrel{\text{O}}{=}$  For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

## **REFERENCES CITED IN THE DESCRIPTION**

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

## Patent documents cited in the description

• JP 3572681 B [0004]