# (11) EP 1 760 565 A1

(12)

## **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication: **07.03.2007 Bulletin 2007/10**

(51) Int Cl.: **G05F** 3/26 (2006.01)

(21) Numéro de dépôt: 05291823.2

(22) Date de dépôt: 01.09.2005

(84) Etats contractants désignés:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI SK TR

Etats d'extension désignés:

AL BA HR MK YU

(71) Demandeurs:

- STMicroelectronics SA 92120 Montrouge (FR)

- STMicroelectronics S.r.l.

20041 Agrate Brianza (Milano) (IT)

- (72) Inventeurs:

- Sirito-Olivier, Philippe

13500 Carro par Martigues (FR)

- Chiricosta, Mario 98121 Messina (IT)

- (74) Mandataire: Ferrari, Barbara Botti & Ferrari S.r.I., Via Locatelli, 5 20124 Milano (IT)

## (54) Miroir de courant

(57) L'invention se réfère à un miroir de courant du type comprenant au moins un premier et un second transistors de miroir (Q1, Q2) insérés entre une première et une seconde référence de tension (Vcc, GND) et branchés respectivement à une borne d'entrée (IN) et à une borne de sortie (OUT) du miroir de courant (10), le miroir de courant comprenant un bloc de compensation du courant de base (12) inséré entre la borne d'entrée (IN) et les bornes de contrôle communes du premier et du second transistors de miroir (Q1, Q2) et branché à une référence de tension (Vcc, GND).

Avantageusement selon l'invention, le bloc de compensation du courant de base (12) comprend au moins: - un générateur de courant de polarisation (G2) d'un courant de polarisation (Ipol) et un premier transistor de compensation (Q4) inséré, en séquence l'un par rapport à l'autre, entre la référence de tension (Vcc, GND) et la borne d'entrée (IN); et

- un second transistor de compensation (Q6) inséré entre la référence de tension (Vcc, GND) et les bornes de contrôle communes des transistors de miroir (Q1, Q2) et ayant une borne de contrôle branchée à une borne de contrôle du premier transistor de compensation (Q4).

## Description

5

20

30

35

40

45

50

55

## Domaine d'application

[0001] La présente invention se réfère à un miroir de courant.

**[0002]** Plus spécifiquement, l'invention se réfère à un miroir de courant du type comprenant au moins un premier et un second transistors de miroir insérés entre une première et une seconde référence de tension et branchés respectivement à une borne d'entrée et à une borne de sortie du miroir de courant, le miroir de courant comprenant un bloc de compensation du courant de base inséré entre ladite borne d'entrée et les bornes de contrôle communes du premier et du second transistors de miroir et branché à une référence de tension.

## Art antérieur

**[0003]** On connaît que les miroirs de courant sont largement utilisés dans toute sorte de circuits électroniques. Le miroir de courant est substantiellement un circuit conçu en vue de copier un courant passant par un dispositif actif tout en contrôlant un courant dans un autre dispositif actif, en gardant le courant de sortie d'une borne de sortie du miroir de courant indépendamment des valeurs de charge appliquées à la même borne de sortie.

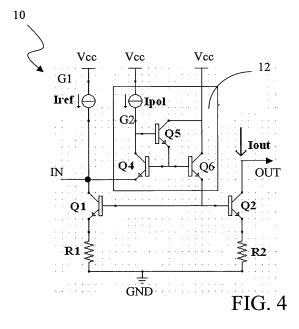

[0004] Un miroir de courant réalisé en utilisant des transistors bipolaires est montré schématiquement dans la figure 1. [0005] En particulier, le miroir de courant 1 comprend une première branche ou branche d'entrée comprenant un générateur de courant G 1 émettant un courant de référence lref, un premier transistor de miroir Q1 et une première résistance d'émetteur R1, insérés, en séquence l'un par rapport à l'autre, entre une première et une seconde référence de tension, en particulier une référence de la tension d'alimentation Vcc et de masse GND.

**[0006]** En outre, le miroir de courant 1 comprend une seconde branche ou branche de sortie comprenant un second transistor de miroir Q2 et une seconde résistance d'émetteur R2, insérés, en séquence l'un par rapport à l'autre, entre une borne de sortie OUT du miroir du courant 1 et une borne de masse GND.

[0007] Le premier et le second transistors de miroir, Q1 et Q2, sont des transistors bipolaires dont les bornes de base sont branchées l'une à l'autre.

**[0008]** Pour améliorer la précision du miroir de courant, une solution classique consiste dans le fait d'utiliser des résistances d'émetteur et un bloc de compensation du courant de base, tel qu'il est montré dans la figure 1 et globalement indiqué avec le numéro 2.

**[0009]** En particulier, le bloc 2 de compensation du courant de base est branché aux bornes de base communes des transistors de miroir, Q1 et Q2, et à la borne de collecteur du premier transistor de miroir Q1. La borne de collecteur du premier transistor de miroir Q1 est aussi la borne d'entrée IN du miroir de courant 1.

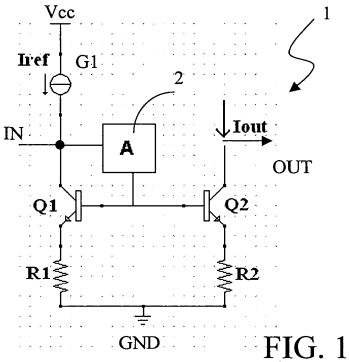

**[0010]** Le bloc 2 de compensation du courant de base est utilisé pour compenser les courants de base du premier et du second transistors de miroir, Q1 et Q2. Une réalisation bien connue de ce bloc est décrite dans Analysis and Design of Analog Integrated Circuits, Paul R. Gray, Robert G. Meyer, Troisième édition, page 276, et montrée schématiquement dans la figure 2.

**[0011]** En particulier, le bloc 2 de compensation du courant de base comprend un transistor de compensation Q3, inséré entre la référence de la tension d'alimentation Vcc et les bornes de contrôle ou de base communes des transistors de miroir, Q1 et Q2, et ayant une borne de base branché à la borne de collecteur du premier transistor bipolaire de miroir Q1. Le transistor de compensation Q3 est un transistor bipolaire.

[0012] On peut vérifier que le transistor de compensation Q3 réduit l'erreur d'un courant de sortie de la borne de sortie OUT selon l'équation suivante:

$$Iout = \frac{Iref}{1 + \frac{2}{\beta_F(\beta_F + 1)}}$$

(1)

où lout est le courant de sortie, lref est le courant de référence et  $\beta_F$  est le gain bipolaire de courant de Q1, Q2 et Q3 (qu'on suppose égal à une approximation du premier ordre).

[0013] En outre, la première et la seconde résistance d'émetteur, R1 et R2, améliorent l'adaptation [matching] du miroir de courant 1, comme on explique dans le manuel mentionné ci-dessus, pages 317 à 320.

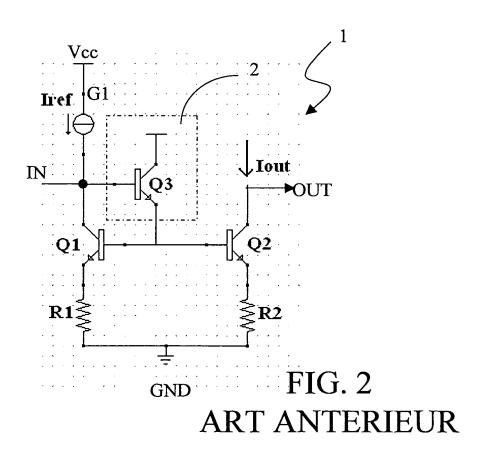

[0014] On connaît aussi une réalisation alternative du bloc 2 de compensation du courant de base utilisant un transistor MOS M3, tel qu'il est montré dans la figure 3.

#### EP 1 760 565 A1

[0015] Dans ce cas-là, le courant de la gate d'un transistor MOS étant zéro, le courant de sortie lout est égal au courant de référence lref et les courants de base du premier et du second transistors bipolaires de miroir, Q1 et Q2, sont alimentés par le transistor MOS M3.

[0016] Même avantageuse sous de nombreux profils, la solution connue montre plusieurs inconvénients, parmi lesquels on trouve le fait que la tension d'entrée appliquée à la borne de collecteur du premier transistor de miroir Q1 devrait être supérieure à une valeur-seuil, qui s'avère être trop haute dans de nombreuses applications. En particulier, une telle tension de seuil est:

- 2xVbe + R1xIref, pour le bloc 2 de compensation du courant de base réalisé par un transistor bipolaire et montré dans la figure 2

- Vgs + Vbe + R1xIref, pour le bloc 2 de compensation du courant de base réalisé par un transistor MOS et montré dans la figure 3

15 où:

10

Vbe est la tension émetteur-base du premier transistor de miroir Q1; et

Vgs est la tension d'alimentation de la gate du transistor MOS M3.

[0017] Par exemple, si Vbe=0.8V, Vgs=1V et R1xIref=0.2V (qui sont des quantités communes à ces valeurs) la tension d'entrée minimum est environ 1.8V ou 2V, qui augmente jusqu'à 2V ou 2.3V avec des variations de température et de processus.

**[0018]** Le problème technique à la base de la présente invention consiste dans le proposer un miroir de courant ayant des caractéristiques structurelles et fonctionnelles qui permettent d'obtenir une bonne précision et une basse tension d'entrée, indépendamment de la tension de sortie, ce qui rend possible de dépasser les limites dont souffrent encore les dispositifs réalisés selon l'art antérieur.

## Résumé de l'invention

**[0019]** L'idée de solution à la base de la présente invention consiste dans le fait de proposer un bloc de compensation du courant de base réduisant la valeur de tension à proximité de la borne de collecteur du premier transistor de miroir de courant.

**[0020]** À partir d'une telle idée de solution, le problème technique est résolu par un miroir de courant comme indiqué au préalable et défini par la partie caractérisante de la revendication 1.

**[0021]** Les caractéristiques et les avantages du miroir de courant selon l'invention seront évidents à partir de la description suivante de ses réalisations donnée en façon d'un exemple indicatif et non limitant par rapport aux dessins ci-joints.

## Description des dessins

[0022] Dans ces dessins:

Les figures 1 à 3 montrent schématiquement des miroirs de courant réalisés selon l'art antérieur;

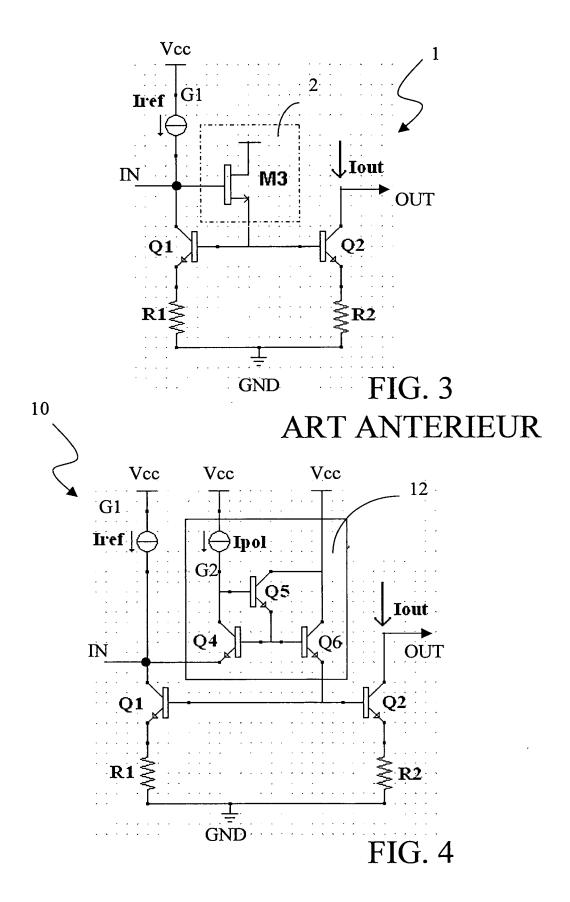

La figure 4 montre schématiquement un miroir de courant réalisé selon la présente invention;

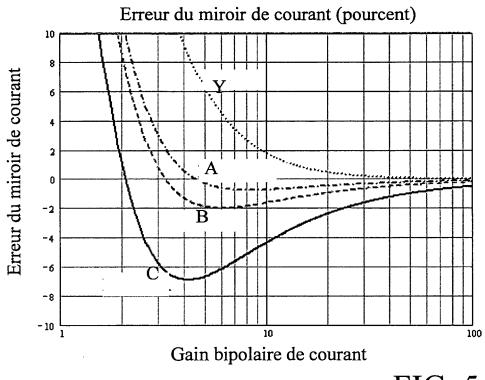

La figure 5 montre schématiquement les valeurs d'erreur de courant des miroirs de courant connus par rapport aux valeurs d'erreur de courant du miroir de courant selon la présente invention;

La figure 6 montre schématiquement une réalisation alternative du miroir de courant selon la présente invention.

### Description détaillée

[0023] En ce qui concerne lesdites figures, et notamment la figure 4, un miroir de courant réalisé selon la présente invention est montré schématiquement et globalement indiqué avec le numéro 10.

[0024] Pour des éléments structurellement et/ou fonctionnellement égaux par rapport aux circuits décrits dans la section consacrée à l'art antérieur, on appliquera les mêmes numéros de référence.

3

20

30

45

50

55

#### EP 1 760 565 A1

**[0025]** Comme on a déjà expliqué au sujet des miroirs de courant réalisés selon l'art antérieur, le miroir de courant 10 comprend une première branche ou branche d'entrée comprenant à son tour un générateur de courant G1 émettant un courant de référence lref, un premier transistor de miroir Q1 et une première résistance d'émetteur R1, insérés, en séquence l'un par rapport à l'autre, entre une première et une seconde référence de tension, en particulier une référence de tension d'alimentation Vcc et de masse GND.

**[0026]** En outre, le miroir de courant 10 comprend une seconde branche ou branche de sortie comprenant un second transistor de miroir Q2 et une seconde résistance d'émetteur R2, insérés, en séquence l'un par rapport à l'autre, entre une borne de sortie OUT du miroir de courant 10 et la masse GND.

[0027] Le premier et le second transistors de miroir, Q1 et Q2, sont des transistors bipolaires dont les bornes de contrôle ou de base sont branchées l'une à l'autre.

**[0028]** En outre, le miroir de courant 10 comprend un bloc 12 de compensation du courant de base branché aux bornes de base communes des transistors de miroir, Q1 et Q2, et à la borne de collecteur du premier transistor de miroir Q1. La borne de collecteur du premier transistor de miroir Q1 est aussi la borne d'entrée IN du miroir de courant 10.

**[0029]** Avantageusement selon l'invention, le bloc 12 de compensation du courant de base comprend un second générateur de courant G2 d'un lpol de courant de polarisation et un premier transistor de compensation Q4 inséré, en séquence l'un par rapport à l'autre, entre la référence de tension d'alimentation Vcc et la borne d'entrée IN du miroir de courant 10.

**[0030]** Le bloc 12 de compensation du courant de base comprend aussi un second transistor de compensation Q6 inséré entre la référence de tension d'alimentation Vcc et les bornes de base communes des transistors de miroir, Q1 et Q2, et ayant une borne de base branchée à une borne de base du premier transistor de compensation Q4.

**[0031]** Enfin, le bloc 12 de compensation du courant de base du miroir de courant 10 selon la présente invention comprend un troisième transistor de compensation Q5 inséré entre la référence de la tension d'alimentation Vcc et les bornes de base communes du premier et du second transistors de compensation, Q4 et Q6, et ayant une borne de base branchée à une borne de collecteur du premier transistor de compensation Q4 et, donc, au second générateur de courant G2.

[0032] Dans l'exemple montré par la figure 4, les transistors de compensation Q4, Q5 et Q6 sont des transistors bipolaires.

**[0033]** Avantageusement selon l'invention, le bloc 12 de compensation du courant de base réduit une tension sur la borne de collecteur du premier transistor de miroir Q1, par exemple la tension d'entrée, à une valeur égale à:

# Vbe + (Iref + Ipol)xR1

où:

10

20

25

30

35

45

50

Vbe est la tension d'émetteur de base du premier transistor du miroir Q 1;

40 Iref est le courant de référence émis par le premier générateur de courant G1;

Ipol est le courant de polarisation émis par le second générateur de courant G2; et

R1 est la valeur de la première résistance d'émetteur branchée au premier transistor de miroir Q1.

**[0034]** Il faudrait remarquer que la valeur de tension ci-dessus est la tension d'entrée minimum qui peut être atteinte en utilisant un miroir de courant comprenant les résistances d'émetteur.

[0035] En particulier, la tension d'entrée minimum d'un miroir de courant bipolaire utilisant la résistance d'émetteur R1 est obtenue (en se référant à l'art antérieur) lorsque le bloc 2 de la figure 1 est un simple court-circuit entre le collecteur et la base de Q1. Cependant, dans ce cas-là, l'erreur de courant calculée selon l'équation 1 mentionnée ci-dessus est supérieure et égale à:

$$Iout = \frac{Iref}{1 + \frac{2}{\beta_F}}$$

55

**[0036]** En utilisant les valeurs communes pour les transistors et les résistances comprises dans le miroir de courant 10, on peut obtenir une valeur de tension d'entrée de 1÷1.2V.

[0037] Le miroir de courant 10 montré dans la figure 4 a un courant de sortie lout donné par l'équation suivante:

5

10

$$Iout = \frac{Iref + \frac{(\beta_F + 1)^2}{\beta_F (\beta_F + 1) + 1} Ipol}{1 + \frac{2}{\beta_F^2 (\beta_F + 1) + 1}}$$

(2)

où lout est le courant de sortie, Iref est le courant de référence émis par le premier générateur de courant G1, Ipol est le courant de polarisation émis par le second générateur de courant G2, et β<sub>F</sub> est le gain bipolaire de courant de Q1, Q2, Q4, Q5 et Q6 (qu'on suppose égal à une approximation du premier ordre).

**[0038]** La figure 5 montre une comparaison de l'erreur de courant de sortie du miroir de courant 10 réalisée selon l'invention et le miroir de courant connu 1 tels qu'illustré dans la figure 2.

[0039] En particulier, l'erreur du miroir de courant tracé ici est définie comme:

20

pour le miroir de courant connu 1 illustré dans la figure 2 (diagramme Y) :

$$Erreur = (1 - \frac{Iout}{Iref}) * 100$$

25

pour le miroir de courant 10 selon l'invention:

30

$$Erreur = (1 - \frac{Iout}{Iref + Ipol}) * 100$$

35

40

45

50

55

Ipol étant égal respectivement à 50%, 20% et 10% d'Iref pour les cas A, B, C.

**[0040]** À partir des diagrammes de la figure 5, on peut vérifier que, par rapport au miroir de courant classique, le courant de sortie du miroir de courant 10 selon la présente invention est supérieur par rapport à la référence plus des courants de polarisation (l'erreur est négative).

**[0041]** Il faudrait aussi souligner que, avantageusement selon la présente invention, l'erreur du miroir de courant peut être maintenue basse (1%) pour une gamme supérieure du gain bipolaire de courant  $\beta_F$  si le courant de polarisation lpol ne dépasse pas 10% du courant de référence lref (diagramme C).

[0042] Cela peut être intéressant pour des transistors PNP avec un bas rendement comme montre la figure 6.

**[0043]** Dans ce cas, les transistors de miroir Q1 et Q2 sont des transistors du type P et les résistances d'émetteur R1 et R2 sont branchées à la référence de tension d'alimentation Vcc.

[0044] Le bloc 12 de compensation du courant de base est donc branché à la masse GND.

**[0045]** Il faudrait aussi remarquer que, avantageusement selon l'invention, le bloc 12 de compensation du courant de base du miroir de courant 10 présente aussi le même avantage (réduction de la tension d'entrée) lorsque les résistances d'émetteur R1 et R2 ne sont pas utilisées.

**[0046]** En résumé, le miroir de courant 10 selon la présente invention est un miroir de courant bipolaire ayant un bon degré de précision et une basse tension d'entrée, indépendamment de la tension de sortie.

**[0047]** Compte tenu de ce qu'on vient d'expliquer, on appréciera qu'en dépit du fait que des réalisations spécifiques de l'invention y ont été décrites en façon illustrative, plusieurs modifications peuvent être apportées sans sortir de l'esprit et du domaine de l'invention. En particulier, il est évident que le bloc 12 de compensation du courant de base peut être aussi réalisé en utilisant des transistors MOS ainsi que des transistors bipolaires et MOS.

## EP 1 760 565 A1

#### Revendications

5

10

15

35

40

45

50

55

- 1. Miroir de courant du type comprenant au moins un premier et un second transistors (Q1, Q2) insérés entre une première et une seconde références de tension (Vcc, GND) et branchés respectivement à une borne d'entrée (IN) et à une borne de sortie (OUT) du miroir de courant (10), le miroir de courant comprenant un bloc de compensation du courant de base (12) inséré entre ladite borne d'entrée (IN) et les bornes de contrôle communes du premier et du second transistors de miroir (Q1, Q2) et branché à une référence de tension (Vcc, GND), caractérisé en ce que ledit bloc de compensation du courant de base (12) comprend au moins:

- un générateur de courant de polarisation (G2) d'un courant de polarisation (Ipol) et un premier transistor de compensation (Q4) inséré, en séquence l'un par rapport à l'autre, entre ladite référence de tension (Vcc, GND) et ladite borne d'entrée (IN); et

- un second transistor de compensation (Q6) inséré entre ladite référence de tension (Vcc, GND) et lesdits bornes de contrôle communes desdits transistors de miroir (Q1, Q2) et ayant une borne de contrôle branché à une borne de contrôle dudit premier transistor de compensation (Q4).

- 2. Miroir de courant selon la revendication 1, caractérisé en ce que ledit bloc de compensation du courant de base (12) comprend également:

- un troisième transistor de compensation (Q5) inséré entre la référence de tension (Vcc, GND) et les bornes de contrôle communes dudit premier et second transistors de compensation (Q4, Q6), et ayant une borne de contrôle branchée à la borne d'entrée (IN) du miroir de courant (10).

- 3. Miroir de courant selon la revendication 2, **caractérisé en ce que** lesdits transistors de compensation (Q4, Q5, Q6) sont des transistors bipolaires.

- Miroir de courant selon la revendication 2, caractérisé en ce que lesdits transistors de compensation (Q4, Q5, Q6) sont des transistors MOS.

- 5. Miroir de courant selon la revendication 2, **caractérisé en ce que** lesdits transistors de compensation (Q4, Q5, Q6) comprennent des transistors bipolaires et MOS.

- **6.** Miroir de courant selon la revendication 1, **caractérisé en ce que** ladite référence de tension (Vcc, GND) est une référence d'alimentation de tension (Vcc).

- 7. Miroir de courant selon la revendication 1, caractérisé en ce que ladite référence de tension (Vcc, GND) est une masse (GND).

ART ANTERIEUR

Vcc PIG. 5

Vcc Q2

IN Q4

Q4

Q5

Iref

GND

FIG. 6

Numéro de la demande EP 05 29 1823

| Catégorie                                       | Citation du document avec<br>des parties pertine                                                                              | indication, en cas de besoin,<br>entes                                     | Revendication concernée                                                                                         | CLASSEMENT DE LA<br>DEMANDE (IPC)        |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------|

| X                                               | PATENT ABSTRACTS OF<br>vol. 015, no. 108 (<br>14 mars 1991 (1991-<br>& JP 03 001707 A (S<br>8 janvier 1991 (199<br>* abrégé * | E-1045),<br>03-14)<br>HARP CORP),                                          | 1-7                                                                                                             | INV.<br>G05F3/26                         |

| X                                               | PATENT ABSTRACTS OF<br>vol. 1999, no. 07,<br>31 mars 1999 (1999-<br>& JP 07 212141 A (K<br>TELECOMMUN), 11 aoû<br>* abrégé *  | 03-31)<br>OREA ELECTRON                                                    | 1-7                                                                                                             |                                          |

| X                                               | PATENT ABSTRACTS OF<br>vol. 016, no. 215 (<br>20 mai 1992 (1992-0<br>& JP 04 035511 A (F<br>6 février 1992 (199<br>* abrégé * | E-1204),<br>5-20)<br>UJITSU LTD),                                          | 1-7                                                                                                             |                                          |

|                                                 | 3                                                                                                                             |                                                                            |                                                                                                                 | DOMAINES TECHNIQUES<br>RECHERCHES (IPC)  |

|                                                 |                                                                                                                               |                                                                            |                                                                                                                 | G05F                                     |

|                                                 |                                                                                                                               |                                                                            |                                                                                                                 |                                          |

|                                                 |                                                                                                                               |                                                                            |                                                                                                                 |                                          |

| •                                               | ésent rapport a été établi pour tou                                                                                           |                                                                            |                                                                                                                 |                                          |

| l                                               | ieu de la recherche                                                                                                           | Date d'achèvement de la recherche                                          |                                                                                                                 | Examinateur                              |

| X : parti<br>Y : parti                          | TEGORIE DES DOCUMENTS CITES culièrement pertinent à lui seul culièrement pertinent en combinaison                             | B T: théorie ou<br>E: document<br>date de déj<br>avec un D: cité dans l    | principe à la base de l'i<br>de brevet antérieur, ma<br>pôt ou après cette date<br>a demande                    | nvention<br>ais publié à la              |

| CA X : parti Y : parti autre A : arriè O : divu | La Haye  TEGORIE DES DOCUMENTS CITES cullèrement pertinent à lui seul                                                         | 23 juin 2006  T: théorie ou E: document date de déj avec un L: cité pour d | principe à la base de l'i<br>de brevet antérieur, ma<br>pôt ou après cette date<br>a demande<br>'autres raisons | nobert, D<br>nvention<br>ais publié à la |

## ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

EP 05 29 1823

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Lesdits members sont contenus au fichier informatique de l'Office européen des brevets à la date du

Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

23-06-2006

| Document brevet cité<br>au rapport de recherche | 9 | Date de publication |          | Membre(s) de la<br>famille de brevet(s) | Date de publication  |

|-------------------------------------------------|---|---------------------|----------|-----------------------------------------|----------------------|

| JP 03001707                                     | Α | 08-01-1991          | JP<br>JP | 2081562 C<br>7112137 B                  | 23-08-19<br>29-11-19 |

| JP 07212141                                     | A | 11-08-1995          | KR       | 9402107 B1                              | 17-03-19             |

| JP 04035511                                     | Α | 06-02-1992          | AUCUN    |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

|                                                 |   |                     |          |                                         |                      |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82

**EPO FORM P0460**