## (12)

## CORRECTED EUROPEAN PATENT APPLICATION

Note: Bibliography reflects the latest situation

(15) Correction information:

Corrected version no 1 (W1 A1) **Bibliography** INID code(s) 72

(51) Int Cl.: G06F 13/40 (2006.01)

(48) Corrigendum issued on:

10.10.2007 Bulletin 2007/41

(43) Date of publication:

14.03.2007 Bulletin 2007/11

(21) Application number: 05019644.3

(22) Date of filing: 09.09.2005

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI

**Designated Extension States:**

AL BA HR MK YU

- (71) Applicant: STMicroelectronics S.r.I. 20041 Agrate Brianza (Milano) (IT)

- (72) Inventors:

- · Ciccarelli, Luca I-47900 Rimini (IT)

- Magagni, Luca I-40137 Bologna (IT)

- · Fazzi, Alberto I-41034 Finale Emilia (MO) (IT)

- · Canegallo, Roberto I-47900 Rimini (IT)

- · Guerrieri, Roberto I-40122 Bologna (IT)

- (74) Representative: Botti, Mario Botti & Ferrari S.r.l., Via Locatelli, 5 20124 Milano (IT)

## (54)Chip-to-chip communication system

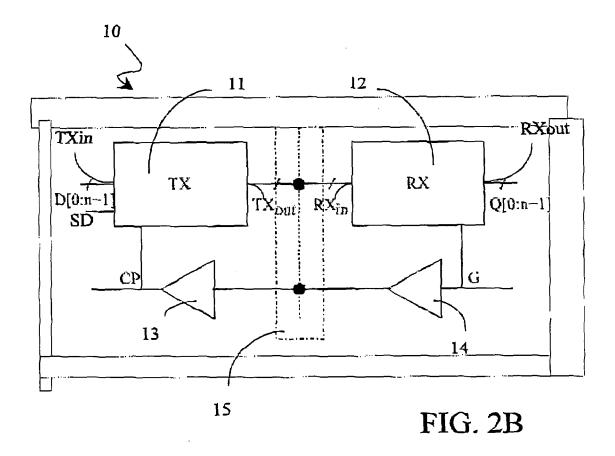

(57)The invention relates to a chip-to-chip communication system (10) of the type comprising at least a transmitter TX (11) and a receiver RX (12), inserted between a first and a second voltage references (Vdd, GND) and connected to respective transmitter and receiver clock terminal wherein respective transmitter and receiver clock signals (CP, G) are applied, the transmitter TX (11) having an input terminal (TXin) receiving an input data (D) and an output terminal (TXout) connected to an input terminal (RXin) of the receiver RX (12) at a connection block (15), the receiver RX (12) having an output terminal (RXout) issuing an output signal (Q).

Advantageously according to the invention:

- the transmitter TX (11) comprises at least a precharge and an evaluation blocks (18, 19) connected to each other and to the transmitter clock terminal (CP);

- the receiver RX (12) comprises at least a precharge block (25) connected to the receiver clock terminal (G)

the precharge blocks (18, 25) precharging the output terminal (TXout) of the transmitter TX (11) and the input terminal (RXin) of the receiver RX (12), respectively, to a value corresponding to a first voltage reference (Vcc)

during a low phase of the transmitter clock signal (CP).