# (11) **EP 1 787 886 A1**

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

23.05.2007 Bulletin 2007/21

(51) Int Cl.: **B61L** 5/18 (2006.01) **H05B** 33/08 (2006.01)

G08G 1/095 (2006.01)

(21) Application number: 05292461.0

(22) Date of filing: 18.11.2005

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI SK TR

Designated Extension States:

AL BA HR MK YU

(71) Applicant: ALCATEL Transport Solution Deutschland GmbH 70430 Stuttgart (DE) (72) Inventor: Klose, Bernd 71679 Asperg (DE)

(74) Representative: Kohler Schmid Möbus

Patentanwälte Ruppmannstrasse 27 70565 Stuttgart (DE)

(54) Electrical circuit for an LED signal lamp with a switching threshold for switching between a daylight operation mode and a nighttime operation mode

(57) An electrical circuit (1, 21) for operating a signal lamp (5),

with a signal lamp (5) comprising at least one light emitting diode (D3, D4, D5, D6), with a voltage input (V1) for supplying the electrical circuit (1, 21) with AC voltage, and with a diode (D1) connected in series with the voltage input (V1), is characterized in that the electrical circuit (1, 21) comprises a first subcircuit (11) connecting the cathode (4) of the diode (D1) with the signal lamp (5), that the electrical circuit (1, 21) comprises a second subcircuit (12a, 12b) providing a low resistance current path (R6, R7, Q1) in parallel to the signal lamp (5), as compared

to the signal lamp (5), when the AC voltage is below a first critical level, that the electrical current (1; 21) comprises a third subcircuit (13) disabling the low resistance current path (R6, R7, Q1) in parallel to the signal lamp (5), as compared to the signal lamp (5), when the AC voltage is above the first critical level, and that the electrical circuit (1, 21) comprises a fourth subcircuit (14) providing a low resistance connection (M1, R3, R4) from cathode (4) of the diode (D1) to the signal lamp (5), as compared to the first subcircuit (11), when the AC voltage is above a second critical level (scl). The inventive electrical circuit allows an adaptation of the luminous intensity by varying the AC input voltage.

#### Description

#### Background of the invention

**[0001]** The invention relates to an electrical circuit for operating a signal lamp, with a signal lamp comprising at least one light emitting diode,

1

with a voltage input for supplying the electrical circuit with AC voltage, and with a diode connected in series with the voltage input.

[0002] An electrical circuit of this type is known from US2005/0151665A1.

**[0003]** Signal lamps are used in a variety of fields, in particular in traffic applications. Of particular importance are railway signal lamps. The signal lamps are used to indicate a train operator whether an upcoming part of a railway track (such as a track switch) can be entered safely.

**[0004]** During daytime, the light of a railway signal lamp must be bright enough for the train operator to recognize the status of the signal lamp well before arriving at the signal lamp. During nighttime, however, the luminous intensity of the signal lamp must be low enough so the train operator is not dazzled. This means that the luminous intensity of a railway signal lamp should be adapted in the course of a day.

[0005] Railway signal lamps of the state of the art typically use conventional light bulbs as their illuminant. In order to adapt the luminous intensity of these light bulbs, the railway control center modifies the AC input voltage of the railway signal lamps. During nighttime, the light bulbs are operated at a reduced voltage of about 66%, as compared to the voltage used during daytime. In the evening and in the morning, the input voltage is switched accordingly in order to have this day/night adaptation.

[0006] Recently, railway signal lamps have been equipped with power light emitting diodes (=LEDs) as their illuminant. Power LEDs have proven to me more reliable and cost-effective than conventional light bulbs. [0007] However, the characteristic of an LED is very different from the characteristic of a light bulb, in particular as far as the correlation between input voltage and luminous intensity is concerned. When replacing conventional light bulbs with LEDs in a railway signal lamp, the existing equipment at railway control centers for adapting the luminous intensity by changing the input voltage is no more suitable.

**[0008]** In the state of the art, LED signal lamps with variable luminous intensity are provided with a special power supply with a variable current, according to the needs of the LEDs.

**[0009]** US2005/0151665A1 describes a signaling control device apparatus for an LED signal lamp, with a sensor for detecting the external light load and a switching power supply. An electrical control system adapts the LED current, and thus the luminous intensity of the LEDs, according to a control signal generated by the sensor.

[0010] This signalling control device apparatus is in-

compatible with adapting the luminous intensity by a change of an AC input voltage. Therefore, when retrofitting existing railway signals with LEDs, in the state of the art, it is necessary to retrofit the railway control center and its luminous intensity control system, too. This is rather expensive and cumbersome.

#### Object of the invention

10 [0011] It is therefore the object of the invention to allow a day/night adaptation of the luminous intensity of an LED based signal lamp by varying the AC input voltage. In particular, it is the object of the invention to allow the use of an existing luminous intensity control system (applying variable input voltages suitable for light bulb based signal lamps) with LED based signal lamps.

#### Short description of the invention

**[0012]** This object is achieved, in accordance with the invention, by an electrical circuit as described in the beginning, characterized in that the electrical circuit comprises a first subcircuit connecting the cathode of the diode with the signal lamp,

that the electrical circuit comprises a second subcircuit providing a low resistance current path in parallel to the signal lamp, as compared to the signal lamp, when the AC voltage is below a first critical level,

that the electrical current comprises a third subcircuit disabling the low resistance current path in parallel to the signal lamp, as compared to the signal lamp, when the AC voltage is above the first critical level,

and that the electrical circuit comprises a fourth subcircuit providing a low resistance connection from cathode of the diode to the signal lamp, as compared to the first subcircuit, when the AC voltage is above a second critical level.

[0013] The inventive electrical circuit with its LED based signal lamp imitates the characteristics of a light bulb based signal lamp when switching the input voltage. In particular, the inventive electrical circuit is designed to be operated at different voltages of the voltage input. Namely, at a first operation voltage (between first and second critical level), the electrical circuit allows a night-time operation with a low luminous intensity of the LED based signal lamp. At a second operation voltage (above second critical level), the signal lamp allows a daytime operation with high luminous intensity of the LED based signal lamp.

[0014] As long as the AC voltage is below the first critical level, what is typically the case with unwanted interference voltage, all current is redirected via the second subcircuit, and the signal lamp does not shine. When the AC voltage is above first, but below second critical level, the signal lamp is powered via the first subcircuit. Its components define the current available at the signal lamp. When the AC voltage is above second critical level, the signal lamp is powered by the fourth subcircuit. The first

45

15

30

40

45

50

subcircuit may be negligible or disabled then. So in summary, the distribution of the incoming current between LED(s) and load resistors within the inventive electrical circuit is changed at switching thresholds. By carefully choosing the load resistors, the inventive electrical circuit has, at its voltage input, the characteristic of a conventional light bulb. In particular, the voltage/current characteristic of a conventional light bulb can be imitated with only small steps, resulting in a basically continuous characteristic.

**[0015]** For retrofitting purposes, an inventive electrical circuit or a number of inventive electrical circuits connected in parallel can take the place of a light bulb of an existing railway signal or other signal, such as a traffic signal.

**[0016]** In a preferred embodiment of the inventive electrical circuit, the first subcircuit comprises a supply transistor in series with a resistor, and a resistor connecting the basis of the supply transistor with the signal lamp. Through the supply transistor and the resistor connected to the basis, a low current may be provided for nighttime operation. The first subcircuit can easily be disabled by setting identical voltages to the emitter and the basis of said supply transistor when above the second critical level.

[0017] In another preferred embodiment, the second subcircuit comprises a diverting transistor connected to the signal lamp via at least one resistor, wherein the basis of the diverting transistor is connected to the cathode of the diode via a resistor. The low resistance current path, which is in parallel to the signal lamp and via the at least one resistor and the diverting transistor, may be activated by setting a sufficient voltage at the basis of the diverting transistor. The resistor connecting the basis of the diverting transistor and the cathode of the diode is chosen such that a sufficient voltage is set at the basis well before the signal lamp could emit light due to interference voltages. Moreover, the diverting transistor can easily be disabled by turning off the voltage at the basis.

**[0018]** Further preferred is an embodiment the third subcircuit comprises a disabling transistor, wherein the basis of the disabling transistor is tapping between two resistors connected in series which contact the cathode of the diode and the pole of the voltage input which is not connected to the diode. The two resistors connected in series act as a potential divider and thus the first critical level may easily be chosen. The disabling transistor may easily cooperate with the second subcircuit.

**[0019]** In a preferred further development of the former two embodiments, the disabling transistor is connected to the basis of the diverting transistor. When the disabling transistor is conductive, the diverting transistor loses its voltage at the basis and the diverting transistor conducts no more.

**[0020]** A highly preferred embodiment of the inventive electrical circuit is characterized in that the fourth subcircuit comprises a reference element with an output, a control input and a low resistance input, wherein the output

of the reference element is connected to the cathode of the diode via a first resistance and a second resistance connected in series, wherein the output of the reference element is connected to the low resistance input of the reference element when the AC voltage is above the second critical level, and that the fourth subcircuit further comprises a field effect transistor connecting the cathode of the diode and the signal lamp, wherein the gate of the field effect transistor taps between the first resistance and the second resistance. The field effect transistor provides a low resistance current path to the signal lamp. It is activated when the reference element gives sufficient voltage to the gate of the field effect transistor. Thus, the reference element and the components at the control input determine the second critical level. In summary, this embodiment provides easy switching of the low resistance current path and an easy determination of the second critical level.

[0021] In a further development of this embodiment, the fourth subcircuit further comprises a capacitor connecting the cathode of the diode and the gate of the field effect transistor. The capacitor smoothes the voltage at the gate, i.e. keeps the field effect transistor conducting, over a full period of the AC voltage at the voltage input, as long as the capacitor is reloaded after each period.

[0022] In a particularly preferred embodiment, the signal lamp comprises at least four LEDs, distributed on at least two parallel current paths, in particular wherein in each current path at least two LEDs are connected in series. Each parallel current path works independent from the other parallel current paths, so a failure of one LED does not affect LEDs on another current path. Con-

necting LEDs in series allows the use of higher voltages

and more LEDs with the same equipment. [0023] Also within the scope of the present invention is a signal lamp arrangement, with at least a first and at least a second inventive electrical circuit as described above, with a common voltage input for the electrical circuits, wherein the at least one first electrical circuit has an opposite polarity with respect to the poles of the common voltage input as compared to the at least one second electrical circuit. This arrangement allows the use of both half waves of the AC voltage. As a result, over a complete period of the AC voltage, there are always LEDs of either the first or the second electrical circuit shining, preventing flickering. The total number of electrical circuits connected in parallel, as well as the number of LEDs per electrical circuit, is chosen with respect to the needed availability of LEDs (which is maximum with one LED per electrical circuit) and the acceptable design costs (which are minimum with all LEDs in just two electrical circuits of opposite polarity). The total number of LEDs is chosen corresponding to the needed maximum luminous intensity of the signal lamp arrangement.

**[0024]** Moreover within the scope of the present invention is the use of a signal lamp arrangement as described above as a railway signal or as a traffic light signal.

[0025] Further advantages can be extracted from the

35

40

description and the enclosed drawing. The features mentioned above and below can be used in accordance with the invention either individually or collectively in any combination. The embodiments mentioned are not to be understood as exhaustive enumeration but rather have exemplary character for the description of the invention.

#### Drawing

[0026] The invention is shown in the drawing.

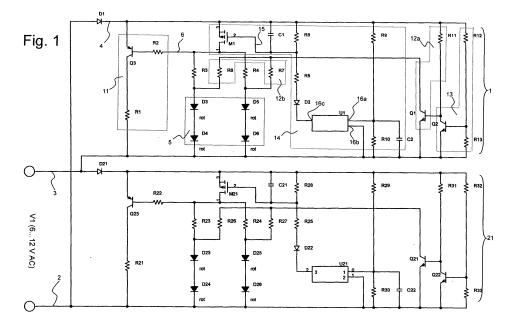

- Fig. 1 shows a schematic circuit diagram of an inventive signal lamp arrangement comprising two inventive electrical circuits;

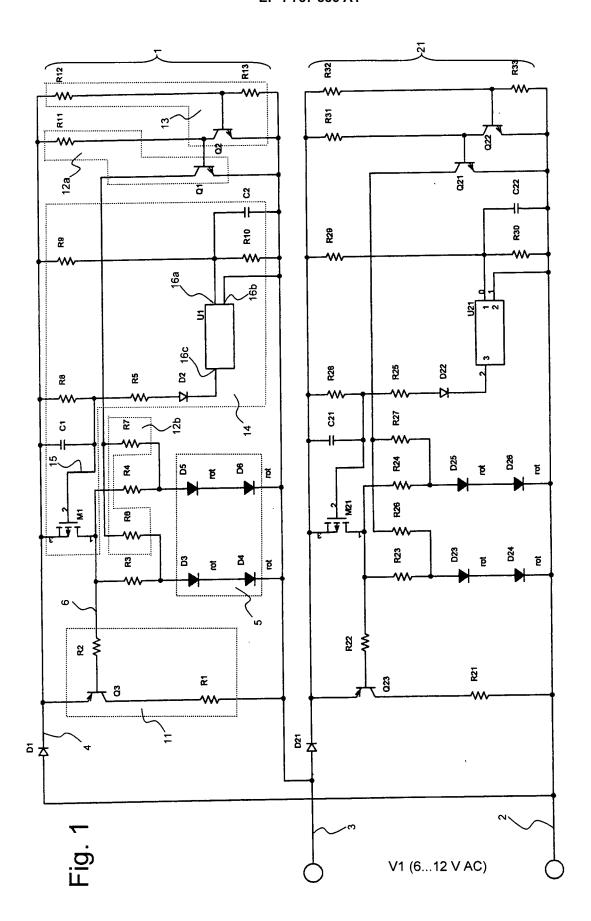

- Fig. 2 shows a schematic circuit diagram of the reference unit of Fig. 1;

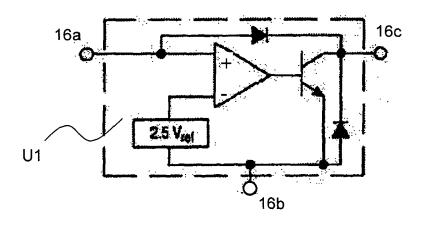

- Fig. 3 shows diagrams illustrating parameters of an inventive electrical circuit as a function of time during daytime operation mode.

[0027] Fig. 1 shows a schematic circuit diagram of an inventive signal lamp arrangement comprising two inventive electrical circuits 1, 21. The electrical circuits 1, 21 are connected in parallel to a common voltage input V1, with the modification of an opposite polarity. The voltage input V1 provides an alternating current (AC) of sinusoidal type with a voltage of about 6 to 12V (peak voltage). With this voltage, the luminous intensity is controlled. For simplification, only the function of the upper electrical circuit 1 is explained in detail; however, the lower electrical circuit 21 functions identically with the other half wave of the AC voltage. The reference signs of electrical circuit 21 correspond to the reference signs of electrical circuit 1 of a number 20 lower (e.g. resistor R3 in electrical circuit 21).

**[0028]** In series to the lower pole 2 of voltage input V1, there is a diode D1 functioning as a one way rectifier. The cathode 4 of the diode D1 and the upper pole 3 of the voltage input V1 provide the power supply to the electrical circuit 1.

[0029] The electrical circuit 1 comprises, as its most important part, a signal lamp 5. The signal lamp 5 comprises four light emitting diodes (LEDs) D3, D4, D5, D6, wherein LEDs D5, D6 are connected in series on a right current path, and LEDs D3, D4 are connected in series on a left current path. For each current path, there is a resistor R4, R3 connected in series for providing a voltage to the LEDs to function. In that sense, the resistors R3, R4 can also be considered as part of the mentioned current paths and the signal lamp 5. The left and right current path are connected in parallel to a signal lamp input 6. [0030] The electrical circuit 1 has three switching thresholds at about 1V (neglect level), about 6V (first critical value, barring unwanted interference voltages below)

and about 10V (second critical value, separating night-

time/daylight operation mode) of the AC voltage present

at voltage input V1.

**[0031]** Low voltages at voltage input V1 are generally set to the signal lamp input 6 via a first subcircuit 11 comprising a supply transistor Q3 and resistors R1, R2. A voltage between the cathode 4 of the diode D1, which corresponds to the emitter of Q3, and the base of Q3 causes some current to flow through R2 and generally provides a current for the signal lamp input 6.

6

**[0032]** Below 1 V of input voltage at V1, the signal lamp 5 will not shine at all. For this reason, no efforts are undertaken to keep such a voltage away from the signal lamp 5 and its LEDs D3-D6.

[0033] An input voltage above 1V may cause the signal lamp 5 to shine and therefore is dealt with. A second subcircuit comprising the parts of both reference numbers 12a, 12b comprises a diverting transistor Q1 and a resistor R11 connected to its base. When the AC voltage is above 1V, a sufficient voltage is set at R11 and at the base of Q1 so that Q1 becomes conductive. The resistors R6, R7 connected in parallel to the current paths of the signal lamp 5, together with Q1, offer a low resistance current path as compared to the signal lamp 5. The current flowing through resistor R2 then flows exclusively through R6, R7 and Q1, and not (or only to a negligible part) through the signal lamp 5. As a result, the signal lamp does not shine.

[0034] At an input voltage above the first critical level of here about 6V, the signal lamp 5 is intended to shine in its nighttime mode. The first subcircuit 11 provides some current to the signal lamp 5, wherein this current is basically determined by the resistor R2. The resistor R1, receiving some of the current running through supply transistor Q3, is used for adapting the characteristic of the signal lamp 5 to the characteristic of a light bulb. In this nighttime mode, the second subcircuit 12a, 12b must be deactivated.

[0035] This is performed by a third subcircuit 13, comprising a disabling transistor Q2 and two resistors R12, R13. When the AC voltage at the cathode 4 is above the first critical value of about 6V, at the base of transistor Q2 there is a voltage high enough to make the disabling transistor Q2 conductive. As a result, the voltage at the base of the diverting transistor Q1 breaks down, and Q1 blocks. Then the low resistance current path via resistors R6, R7 and Q1 is no more available, and the current passing through R2 will also pass through the LEDs D3-D6 of the signal lamp 5. This is the nighttime operation condition.

**[0036]** When the AC voltage at the cathode 4 is above the second critical value of about 10V, the luminous intensity should be increased significantly for daylight operation. This is achieved by establishing a new low resistance current path from the cathode 4 to the input 6 of signal lamp 5 with a lower resistance than the supply connections of the first current path 11. The new low resistance path allows a relatively high current to flow through the signal lamp 5.

[0037] This new low resistance current path comprises

a field effect transistor (FET) M1, which is part of a fourth subcircuit 14, as marked in Fig. 1. The FET M1 connects the cathode 4 of the diode D1 and the signal lamp input 6. The FET M1 is only conductive when a sufficient voltage is set at the gate 15. Such a sufficient voltage can be set by a reference element U1. The reference element U1 has a control input 16a, a low resistance input 16b and an output 16c. The low resistance input 16b is directly connected to pole 3 of the voltage input V1, and the control input 16a is connected to said pole 3 via resistor R10 which is parallel to a capacitor C2. The output 16c is connected to the gate 15 via a diode D2 and a resistor R5. [0038] If the voltage at the control input 16a is high enough, the low resistance input 16b and the output 16c are connected within reference element U1, and gate 15 gets enough voltage to make FET M1 conductive. Else, i.e. if the voltage at control input 16a is low, the output 16c is not connected and thus of high resistance. The resistors R9, R10 and capacitor C2 are chosen such that the switching in reference element U1 occurs when at the cathode 4 of the diode D1 there is just the second critical voltage level.

[0039] A sufficient voltage is set by the reference element U1 at gate 15 only during a small time interval of a full AC voltage period, namely near the voltage peak of one half period. In order to keep the signal lamp shining during a complete half period of the AC voltage (i.e. as long as current passes through diode D1), a capacitorr C1 smoothes the voltage at the gate 15. Capacitor C1 is discharged via the resistor R8, though. The dimensions of C1, R8 are chosen such that during a full period of the AC voltage, the voltage at gate 15 is kept high enough to keep the FET M1 conductive, but that without a refreshing (charging) of the voltage at C1 by the reference element U1 within the next period or within a few further periods, the FET M1 blocks again.

**[0040]** As long as FET M1 is conductive, the voltage between the emitter of supply transistor Q3 and its base breaks down, and without a base current, the supply transistor Q3 shuts. Current to the signal lamp 5 is only provided via the FET M1 then.

[0041] Since different current supply paths to the signal lamp 5 are used during daylight operation condition and nighttime operation condition, these two paths can be designed independently. As a result, the luminous intensity of the signal lamp 5 at two target voltages (and the characteristic around these target voltages) can be set independently and at a wide range. For daylight operation, a target voltage of 12V is typical for railway applications. For nighttime operation, about 66% of the daylight voltage, namely 8 V, is typical. During nighttime, the luminous intensity can be reduced to 0.2% of the daylight luminous intensity, in accordance with the invention. This can easily be achieved with the inventive electrical circuit by choosing resistors R2 and R1 accordingly.

**[0042]** As an advantage of the embodiment shown, the comparison of the of the input voltage with the second critical value at reference element U1 on the one hand,

and the recording of the state of the fourth subcircuit at C1 during at least one period of the AC voltage on the other hand are separated. This allows a very exact definition of the second critical value at U1, with an accuracy of about 1-2%. It also allows a broad variation of the dwelling time at the output 16c of U1, in particular with the possibility of a quick switching form daylight operation mode to nighttime operation mode.

**[0043]** In accordance with the invention, a signal may comprise, e.g., 17 electrical circuits for the positive half wave of the AC voltage, and 17 electrical circuits for the negative half wave. The complete signal apparatus, e.g. a railway signal, then comprises a total of 136 LEDs.

**[0044]** Fig. 2 shows a circuit diagram of a reference element U1, as it may be used as part of the inventive electrical circuit 1 shown in Fig. 1. The control input 16a and the low resistance input 16b are fed into an operational amplifier, whereas the output 16c is connected to the collector of a transistor. The base of this transistor is connected to the output of the operational amplifier.

**[0045]** Fig. 3 illustrates a few parameters (upward axes) within the electrical circuit 1 of Fig. 1 during three periods (time axes t to the right) of the AC voltage during daylight operation mode, here with an AC voltage of about 12V (at the peak).

**[0046]** The upper diagram illustrates the voltage U(4) at the cathode 4 of the diode D1 (see Fig. 1). Only the positive half wave passes the diode D1. For orientation, the second critical level (=scl) is marked. The scl level is about 10V here. The voltage U(4) is higher than scl near the voltage peak.

**[0047]** The second diagram (counted from the top) illustrates the output resistance R(16c) at output 16c of reference element U1. Exactly when the scl has been reached by U(4), the resistance R(16c) drops due to switching the output 16c to the low resistance input 16a. In turn, when U(4) drops below scl again, R(16c) rises again.

**[0048]** The third diagram illustrates the voltage U(15) at the gate 15 of FET M1, which is identical to the voltage at capacitor C1. As soon as R(16c) drops (and concurrently U(4) reaches scl), the charging of capacitor C1 begins. The time constant of this loading process is  $\tau$ =R5\*C1. As soon as R(16c) is high again, a discharging of C1 begins, with another (longer) time constant  $\tau$ =R8\*C1. For orientation, the threshold voltage of FET M1, named sM1, is marked. Over one period, i.e. until the next charging, U(15) stays well above sM1.

[0049] The fourth diagram indicates the voltage U(M1) from source to drain of FET M1, i.e. from the cathode 4 to the signal lamp input 6. At the beginning of the first period, the voltage U(M1) increases in parallel with U(4). However, when U(15) reaches sM1, the FET M1 becomes conductive, and U(M1) breaks down to a low level. During the negative half wave of the AC input voltage, no voltage is present at M1 (zero level). During later positive half wave times, since U(15) stays above sM1, U (M1) is at the low level. During the times when U(M1) is

10

15

20

25

30

35

40

45

50

at its low (but not zero) level, the signal lamp 5 shines brightly in daylight mode.

#### Claims

Electrical circuit (1, 21) for operating a signal lamp (5).

with a signal lamp (5) comprising at least one light emitting diode (D3, D4, D5, D6),

with a voltage input (V1) for supplying the electrical circuit (1, 21) with AC voltage,

and with a diode (D1) connected in series with the voltage input (V1),

#### characterized in

that the electrical circuit (1,21) comprises a first subcircuit (11, Q3, R1, R2) connecting the cathode (4) of the diode (D1) with the signal lamp (5), that the electrical circuit (1, 21) comprises a second subcircuit (12a, 12b, R11, Q1, R6, R7) providing a low resistance current path (R6, R7, Q1) in parallel to the signal lamp (5), as compared to the signal lamp (5), when the AC voltage is below a first critical level, that the electrical current (1; 21) comprises a third subcircuit (13, R12, R13, Q2) disabling the low resistance current path (R6, R7, Q1) in parallel to the signal lamp (5), as compared to the signal lamp (5), when the AC voltage is above the first critical level, and that the electrical circuit (1, 21) comprises a fourth subcircuit (14, M1, C1, R8, R5, D2, U1, R9, R10, C2) providing a low resistance connection (M1, R3, R4) from cathode (4) of the diode (D1) to the signal lamp (5), as compared to the first subcircuit (11, Q3, R1, R2), when the AC voltage is above a second critical level (scl).

- Electrical circuit (1, 21) according to claim 1, characterized in that the first subcircuit (11, Q3, R1, R2) comprises a supply transistor (Q3) in series with a resistor (R1), and a resistor (R2) connecting the basis of the supply transistor (Q3) with the signal lamp (5).

- 3. Electrical circuit (1, 21) according to claim 1, **characterized in that** the second subcircuit (12a, 12b, R11, Q1, R6, R7) comprises a diverting transistor (Q1) connected to the signal lamp (5) via at least one resistor (R6, R7), wherein the basis of the diverting transistor (Q1) is connected to the cathode (4) of the diode (D1) via a resistor (R11).

- 4. Electrical circuit (1,21) according to claim 1, characterized in that the third subcircuit (13, R12, R13, Q2) comprises a disabling transistor (Q2), wherein the basis of the disabling transistor (Q2) is tapping between two resistors (R12, R13) connected in series which contact the cathode (4) of the diode (D1) and the pole (3) of the voltage input (V1) which is

not connected to the diode (D1).

- Electrical circuit (1, 21) according to claims 3 and 4, characterized in that the disabling transistor (Q2) is connected to the basis of the diverting transistor (Q1).

- Electrical circuit (1, 21) according to claim 1, characterized in that the fourth subcircuit (14, M1, C1, R8, R5, D2, U1, R9, R10, C2) comprises a reference element (U1) with an output (16c), a control input (16a) and a low resistance input (16b), wherein the output (16c) of the reference element (U1) is connected to the cathode (4) of the diode (D1) via a first resistance (R8) and a second resistance (R5) connected in series, wherein the output (16c) of the reference element (U1) is connected to the low resistance input (16b) of the reference element (U1) when the AC voltage is above the second critical level (scl), and that the fourth subcircuit (14, M1, C1, R8, R5, D2, U1, R9, R10) further comprises a field effect transistor (M1) connecting the cathode (4) of the diode (D1) and the signal lamp (5), wherein the gate (15) of the field effect transistor (M1) taps between the first resistance (R8) and the second resistance (R5).

- 7. Electrical circuit (1, 21) according to claim 6, characterized in that the fourth subcircuit (14, M1, C1, R8, R5, D2, U1, R9, R10, C2) further comprises a capacitor (C1) connecting the cathode (4) of the diode (D1) and the gate (15) of the field effect transistor (M1).

- 8. Electrical circuit (1,21) according to claim 1, characterized in that the signal lamp (5) comprises at least four LEDs (D3, D4, D5, D6), distributed on at least two parallel current paths, in particular wherein in each current path at least two LEDs (D3, D4, D5, D6) are connected in series.

- 9. Signal lamp arrangement, with at least a first (1) and at least a second electrical circuit (21) according to claim 1, with a common voltage input (V1) for the electrical circuits (1, 21), wherein the at least one first electrical circuit (1) has an opposite polarity with respect to the poles (2, 3) of the common voltage input (V1) as compared to the at least one second electrical circuit (21).

- **10.** Use of a signal lamp arrangement according to claim 9 as a railway signal or as a traffic light signal.

Fig. 2

Fig. 3

## **EUROPEAN SEARCH REPORT**

Application Number EP 05 29 2461

|                                          | DOCUMENTS CONSIDERE  Citation of document with indicati                                                                                                            |                                                                                  | Relevant                                     | CLASSIFICATION OF THE                                      |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------|

| Category                                 | of relevant passages                                                                                                                                               | оп, инсте арргорнаю,                                                             | to claim                                     | APPLICATION (IPC)                                          |

| A                                        | EP 0 992 961 A (SIEMEN: AKTIENGESELLSCHAFT) 12 April 2000 (2000-04 * paragraphs [0025] - * paragraphs [0036], * figures 2-4 *                                      | -12)<br>[0030] *                                                                 | 1-10                                         | INV.<br>B61L5/18<br>G08G1/095<br>H05B33/08                 |

| A                                        | WO 95/12512 A (SIEMENS<br>VERKEHRSTECHNIK AG)<br>11 May 1995 (1995-05-1<br>* page 2, line 14 - page<br>* figures 1,2 *                                             | 1)                                                                               | 1-10                                         |                                                            |

| A                                        | WO 03/096753 A (SIEMENS AKTIENGESELLSCHAFT; CO ZIMMERMANN, DIRK) 20 November 2003 (2003 * page 4, line 15 - page 4 figures 1-3 *                                   | LBERG, JENS;<br>-11-20)                                                          | 1-10                                         |                                                            |

| A                                        | US 2005/029961 A1 (POP<br>10 February 2005 (2005<br>* paragraphs [0005] -<br>* figures 1-5 *                                                                       | -02-10)                                                                          | )  1-10                                      | TECHNICAL FIELDS<br>SEARCHED (IPC)<br>B61L<br>G08G<br>H05B |

| A                                        | EP 1 324 641 A (WESTING SIGNAL COMPANY LIMITED 2 July 2003 (2003-07-07) * paragraphs [0001] - * figures 1,2 *                                                      | )<br>2)                                                                          | 1                                            | 11035                                                      |

|                                          |                                                                                                                                                                    | -/                                                                               |                                              |                                                            |

|                                          |                                                                                                                                                                    |                                                                                  |                                              |                                                            |

|                                          | The present search report has been c                                                                                                                               | ·                                                                                |                                              |                                                            |

|                                          | Place of search  Munich                                                                                                                                            | Date of completion of the search 21 April 2006                                   | Ma                                           | Examiner<br>SSalski, M                                     |

|                                          |                                                                                                                                                                    | <u> </u>                                                                         |                                              | <u> </u>                                                   |

| X : part<br>Y : part<br>docu<br>A : tech | ATEGORY OF CITED DOCUMENTS<br>icularly relevant if taken alone<br>icularly relevant if combined with another<br>unent of the same category<br>nological background | E : earlier patent<br>after the filing<br>D : document cite<br>L : document cite | ed in the application<br>d for other reasons | ished on, or                                               |

|                                          | -written disclosure<br>mediate document                                                                                                                            | & : member of the document                                                       | e same patent fami                           | y, corresponding                                           |

## **EUROPEAN SEARCH REPORT**

Application Number EP 05 29 2461

| Category                                 |                                                                                                                                                                                                                      | dication, where appropriate,                                                                 | Relevant                                  | CLASSIFICATION OF THE                   |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------|

| Category<br>A                            | Citation of document with in of relevant passay  ZABEL M ET AL: "LE GENERATION VON LICH EISENBAHNSIGNALE" SIGNAL + DRAHT, TEL DARMSTADT, DE, no. September 2000 (200 XP009033674 ISSN: 0037-4997 * page 31 - page 33 | D - EINE NEUE<br>TQUELLEN FUER<br>ZLAFF VERLAG GMBH.<br>9,<br>0-09), pages 31-30,            | Relevant to claim                         | CLASSIFICATION OF THE APPLICATION (IPC) |

|                                          |                                                                                                                                                                                                                      |                                                                                              |                                           | TECHNICAL FIELDS<br>SEARCHED (IPC)      |

|                                          | The present search report has be place of search Munich                                                                                                                                                              | een drawn up for all claims  Date of completion of the search  21 April 2006                 |                                           | Examiner<br>SSalski, M                  |

| X : part<br>Y : part<br>docu<br>A : tech | ATEGORY OF CITED DOCUMENTS icularly relevant if taken alone icularly relevant if combined with another and the same category inclogical background written disclosure                                                | T : theory or prin E : earlier patent after the filing er D : document cit L : document cite | ciple underlying the<br>document, but pub | invention<br>lished on, or              |

EPO FORM 1503 03.82 (P04C01)

## ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 05 29 2461

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

21-04-2006

|    | Patent document<br>ed in search report |    | Publication date |                                  | Patent family member(s)                                                |                     | Publication date                                                           |

|----|----------------------------------------|----|------------------|----------------------------------|------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------|

|    | 0992961                                | A  | 12-04-2000       | AT<br>DE<br>NO                   | 250259<br>19846753<br>994889                                           | A1                  | 15-10-200<br>13-04-200<br>10-04-200                                        |

| WO | 9512512                                | Α  | 11-05-1995       | AT<br>DE<br>DK<br>EP<br>NO       | 170472<br>59406833<br>678078<br>0678078<br>951743                      | D1<br>T3<br>A1      | 15-09-199<br>08-10-199<br>07-06-199<br>25-10-199<br>05-07-199              |

| WO | 03096753                               | Α  | 20-11-2003       | AU<br>DE<br>EP                   | 2003229273<br>10221573<br>1502481                                      | A1                  | 11-11-200<br>04-12-200<br>02-02-200                                        |

| US | 2005029961                             | A1 | 10-02-2005       | AU<br>CN<br>WO<br>DE<br>EP<br>MX | 2002366246<br>1605227<br>03053110<br>10164561<br>1454511<br>PA04005775 | A<br>A1<br>A1<br>A1 | 30-06-200<br>06-04-200<br>26-06-200<br>10-07-200<br>08-09-200<br>10-09-200 |

| EP | 1324641                                | Α  | 02-07-2003       | CA<br>GB<br>GB<br>HK<br>US       | 2411127<br>2383180<br>2408834<br>1053187<br>2003137427                 | A<br>A<br>A1        | 11-06-200<br>18-06-200<br>08-06-200<br>08-07-200<br>24-07-200              |

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

## EP 1 787 886 A1

#### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

## Patent documents cited in the description

• US 20050151665 A1 [0002] [0009]