Europäisches

Patentamt

European

Patent Office

Office européen

des brevets

(11)

EP 1 792 864 A1

(12)

**EUROPEAN PATENT APPLICATION**

published in accordance with Art. 158(3) EPC

(43) Date of publication:

06.06.2007 Bulletin 2007/23

(51) Int Cl.:

**B66B 5/00 (2006.01)**      **B66B 3/00 (2006.01)**

(21) Application number: **04788085.1**

(86) International application number:

**PCT/JP2004/013926**

(22) Date of filing: **24.09.2004**

(87) International publication number:

**WO 2006/033153 (30.03.2006 Gazette 2006/13)**

(84) Designated Contracting States:

**DE ES FR NL PT**

(72) Inventor: **MATSUOKA, Tatsu,

Mitsubishi Denki Kabushiki Kaisha

Tokyo 100-8310 (JP)**

(71) Applicant: **MITSUBISHI DENKI KABUSHIKI

KAISHA

Chiyoda-ku, Tokyo 100-8310 (JP)**

(74) Representative: **HOFFMANN EITLE

Patent- und Rechtsanwälte

Arabellastrasse 4

81925 München (DE)**

**(54) ELEVATOR APPARATUS**

(57) In an elevator apparatus, an electronic safety apparatus detects abnormality of an elevator based on a detection signal from a sensor and outputs an instruction signal for shifting the elevator to a safe state. The

electronic safety apparatus can detect abnormality of the electronic safety apparatus itself. When abnormality of the electronic safety apparatus itself is detected, the electronic safety apparatus also outputs the instruction signal for shifting the elevator to the safe state.

**FIG. 1**

**Description**

## Technical Field

5 [0001] The present invention relates to an elevator apparatus which employs an electronic safety controller for detecting abnormality of an elevator based on a detection signal from a sensor.

## Background Art

10 [0002] In a conventional elevator safety system, sensors or the like are connected to bus nodes provided to a hoistway, a machine room, and a car, which allows information from the sensors or the like to be sent through the bus nodes and a communication network bus to a safety controller (see, for example, Patent Document 1).

[0003] Patent Document 1: JP 2002-538061 A

15 Disclosure of the Invention

## Problem to be solved by the Invention

20 [0004] In the conventional elevator apparatus, information is inputted from the sensors to the safety controller through the communication network. Thus, to secure high reliability for a safety system, a considerably highly reliable communication network is required. This makes hardware and software that implement the communication network more complicated and more expensive.

25 [0005] The present invention has been devised to solve the problem as described above. It is an object of the invention to provide an elevator apparatus capable of improving the reliability of a safety system with a relatively simple structure.

## Means for solving the Problem

30 [0006] An elevator apparatus according to the invention includes: a sensor that generates detection signal for detecting a state of an elevator; and an electronic safety controller that detects abnormality of the elevator based on the detection signal from the sensor to output an instruction signal for shifting the elevator to a safe state, in which the electronic safety controller can detect abnormality of the electronic safety controller itself and, when abnormality of the electronic safety controller itself is detected, the electronic safety controller also outputs the instruction signal for shifting the elevator to the safe state.

35 Brief Description of the Drawings

**[0007]**

40 [Fig. 1] A diagram of an elevator apparatus according to a first embodiment of the invention.

[Fig. 2] A graph of a pattern of overspeed set in speed governor and an ETS circuit unit of Fig. 1.

[Fig. 3] A block diagram of a relation of connection among an electronic safety controller, an elevator control panel, and various sensors of Fig. 1.

[Fig. 4] A block diagram of the structure of a main part of the electronic safety controller of Fig. 1.

[Fig. 5] A explanatory diagram of a method of executing arithmetic processing by a microprocessor of Fig. 4.

45 [Fig. 6] A block diagram of the main part of the electronic safety controller of Fig. 1.

[Fig. 7] A diagram of a specific configuration of a clock abnormality detection circuit of Fig. 6.

[Fig. 8] An explanatory diagram of separated areas in a RAM of the electronic safety controller of Fig. 1.

[Fig. 9] A flowchart of an initial operation of the electronic safety controller of Fig. 1.

[Fig. 10] A flowchart of a first example of an interrupt computation of the electronic safety controller of Fig. 1.

50 [Fig. 11] A block diagram of the main part of the electronic safety controller of Fig. 1.

[Fig. 12] A block diagram of the main part of the electronic safety controller of Fig. 1.

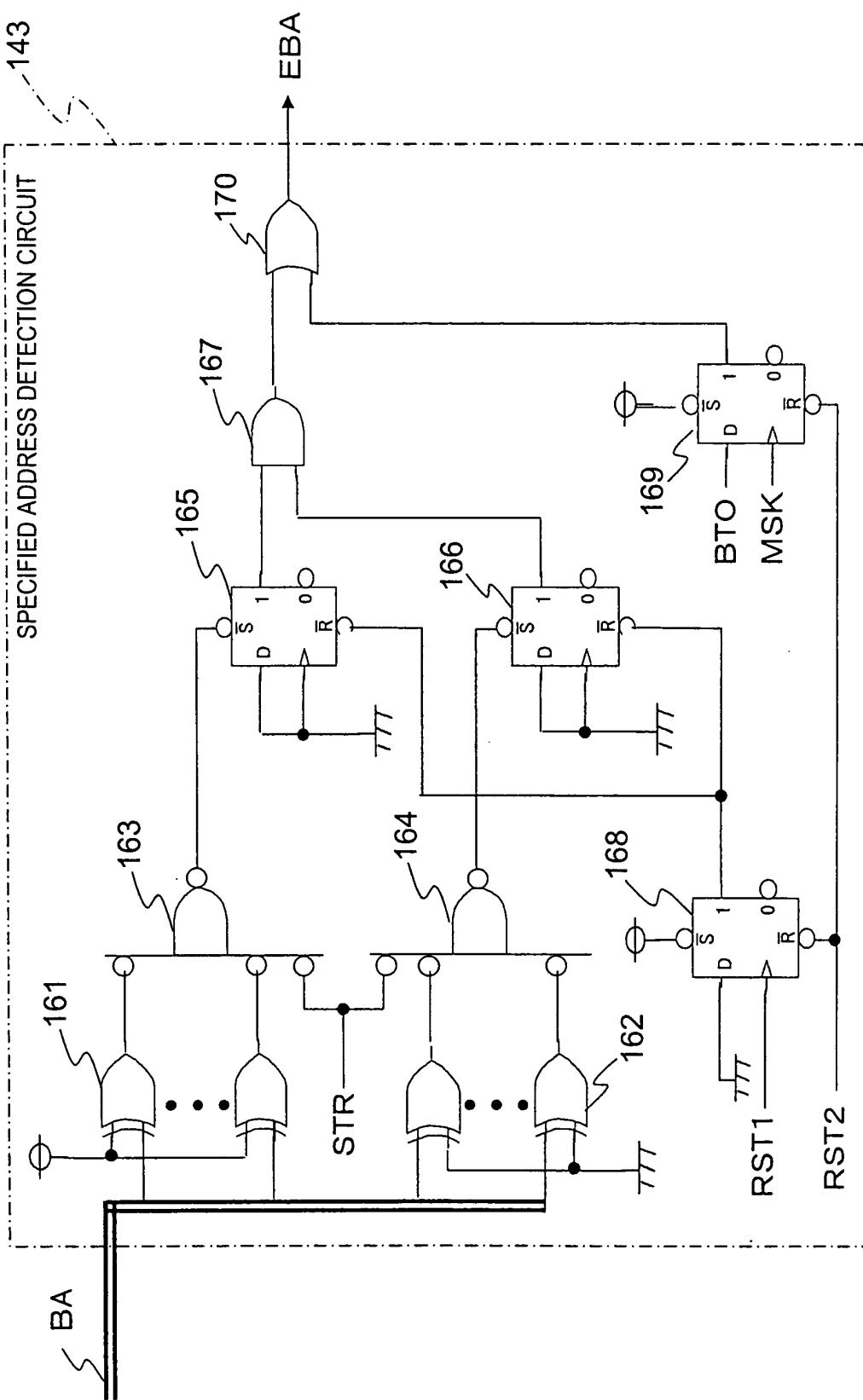

[Fig. 13] A circuit diagram of an example of a specific configuration of a check function circuit of Fig. 12.

[Fig. 14] An explanatory diagram of meanings of data regarding the respective bits of data buses when the check function circuit of Fig. 12 is read by first and second CPUs.

55 [Fig. 15] A flowchart of a method of checking soundness of monitoring of a power source voltage at the first CPU of Fig. 12.

[Fig. 16] A flowchart of an operation when the CPUs are reset in the elevator control apparatus of Fig. 12.

[Fig. 17] A an explanatory diagram of a relation between a stage of an initialization operation of the ETS circuit unit

of Fig. 1 and operations of the operation control unit and the safety circuit unit.

[Fig. 18] An explanatory diagram of movement of the car in an initialization operation mode of the elevator apparatus of Fig. 1.

[Fig. 19] A circuit diagram of an abnormal contact point detection unit of the electronic safety controller of Fig. 1.

[Fig. 20] A flowchart for explaining a method of operating the safety relay main contact point of Fig. 19.

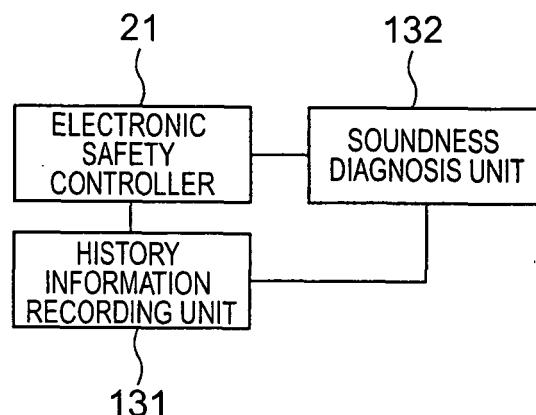

[Fig. 21] A block diagram of the electronic safety controller of Fig. 1 connected to a history information recording unit and a soundness diagnosis unit.

[Fig. 22] An explanatory diagram of an example of information stored in a history information recording unit of Fig. 21.

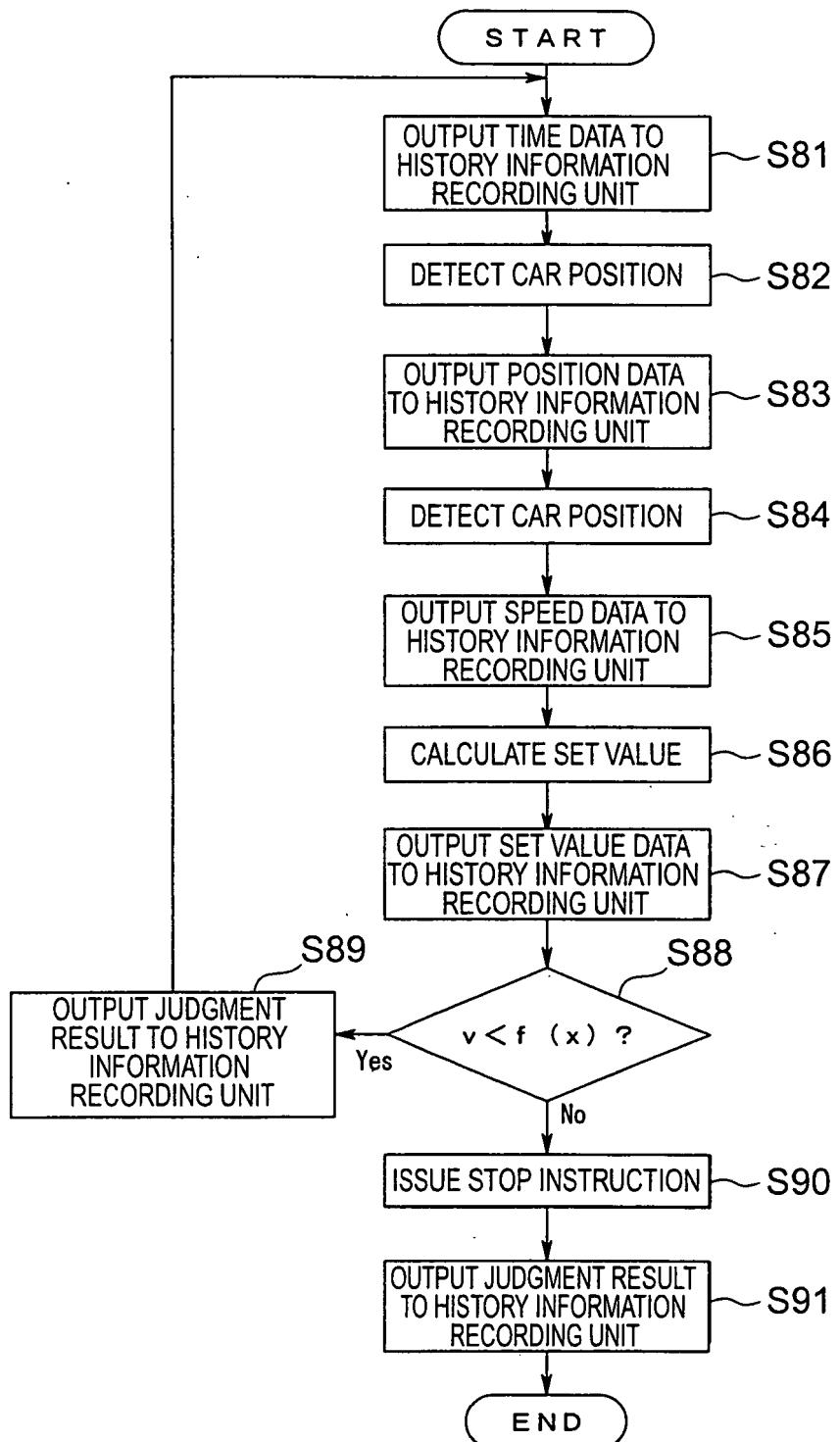

[Fig. 23] A flowchart for explaining an operation of the electronic safety controller of Fig. 21.

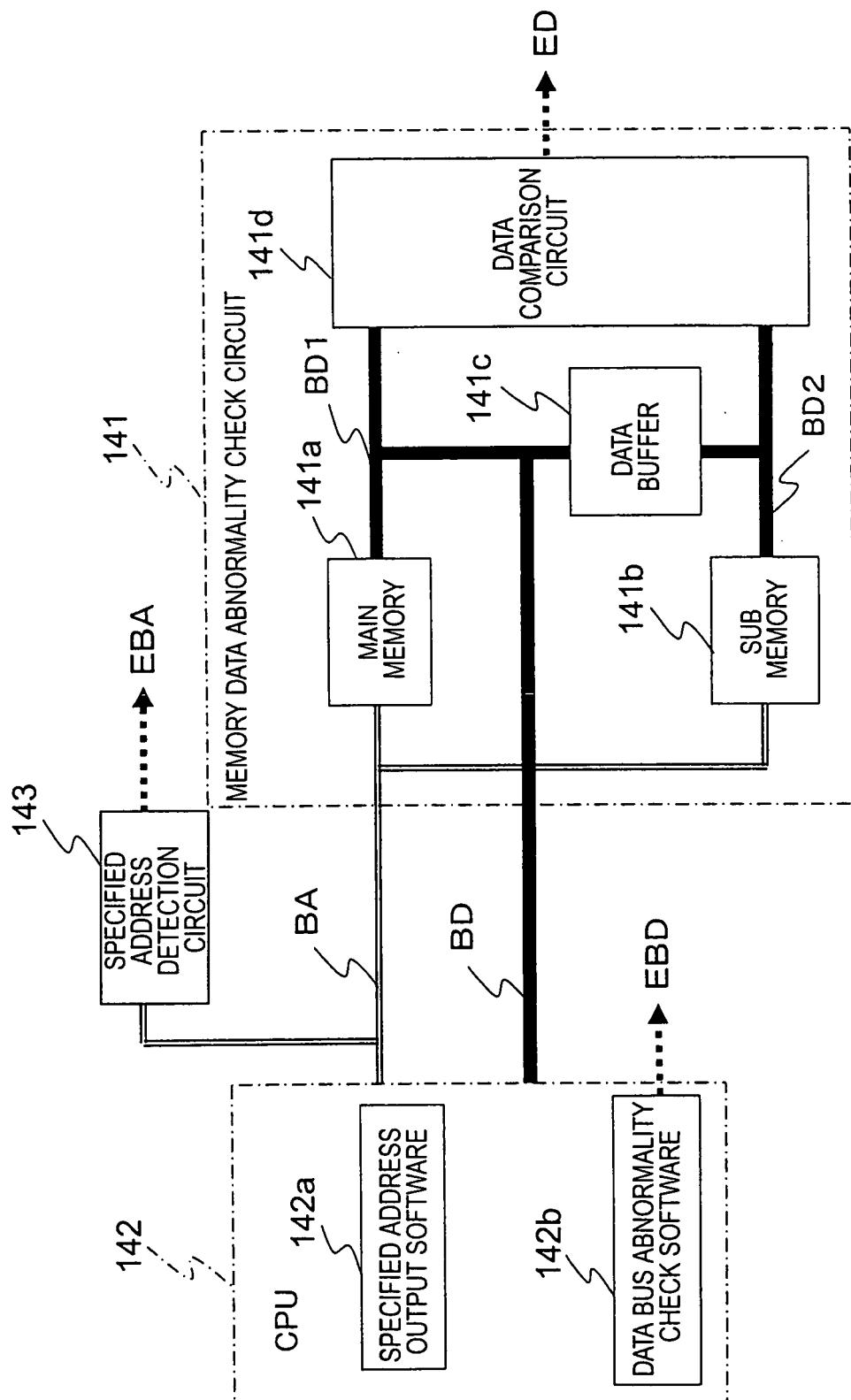

[Fig. 24] A block diagram of the main part of the electronic safety controller of Fig. 1.

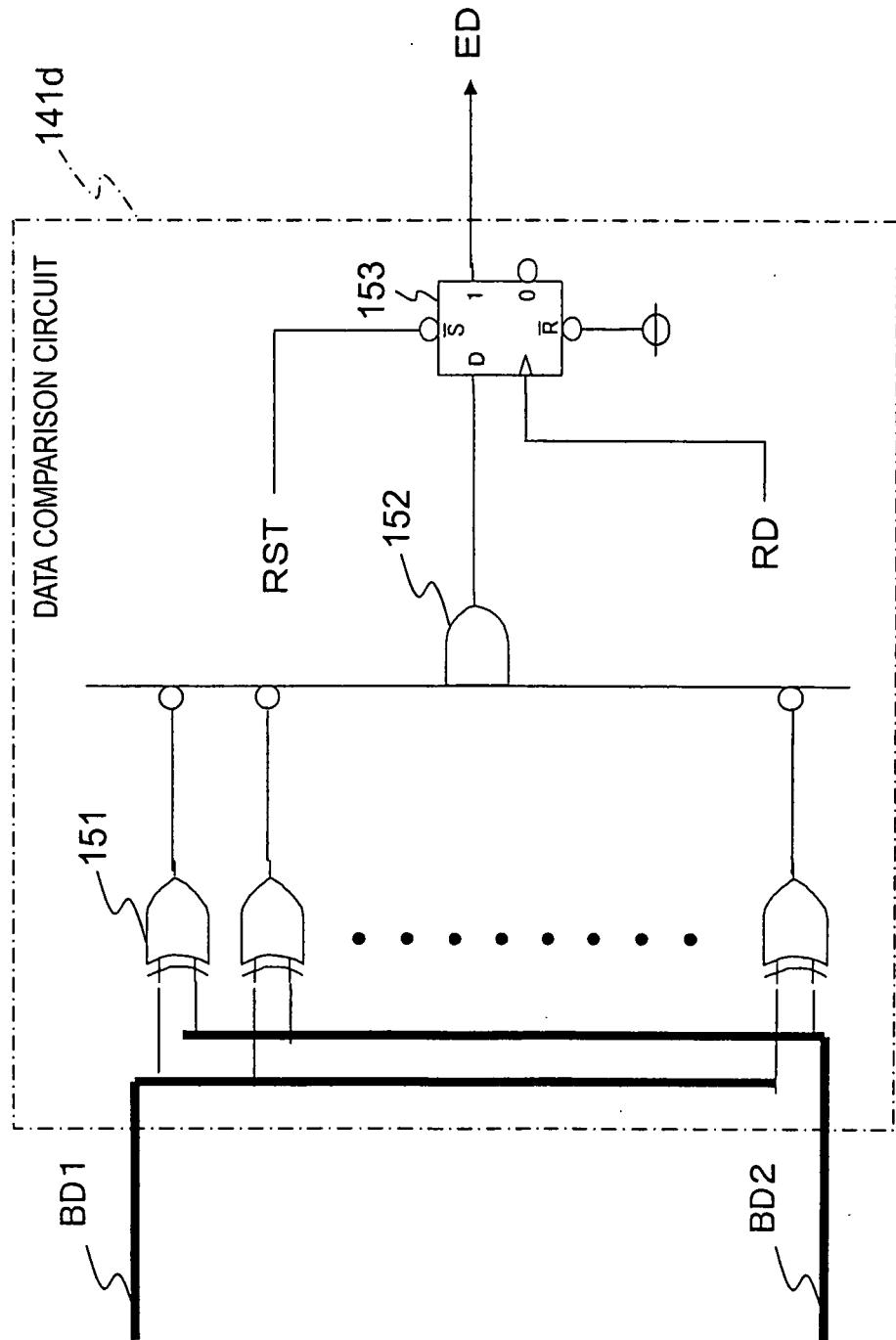

[Fig. 25] A circuit diagram specifically, showing a data comparison circuit for data abnormality check of Fig. 24.

[Fig. 26] A circuit diagram for specifically showing a designated address detection circuit for address bus abnormality check of Fig. 24.

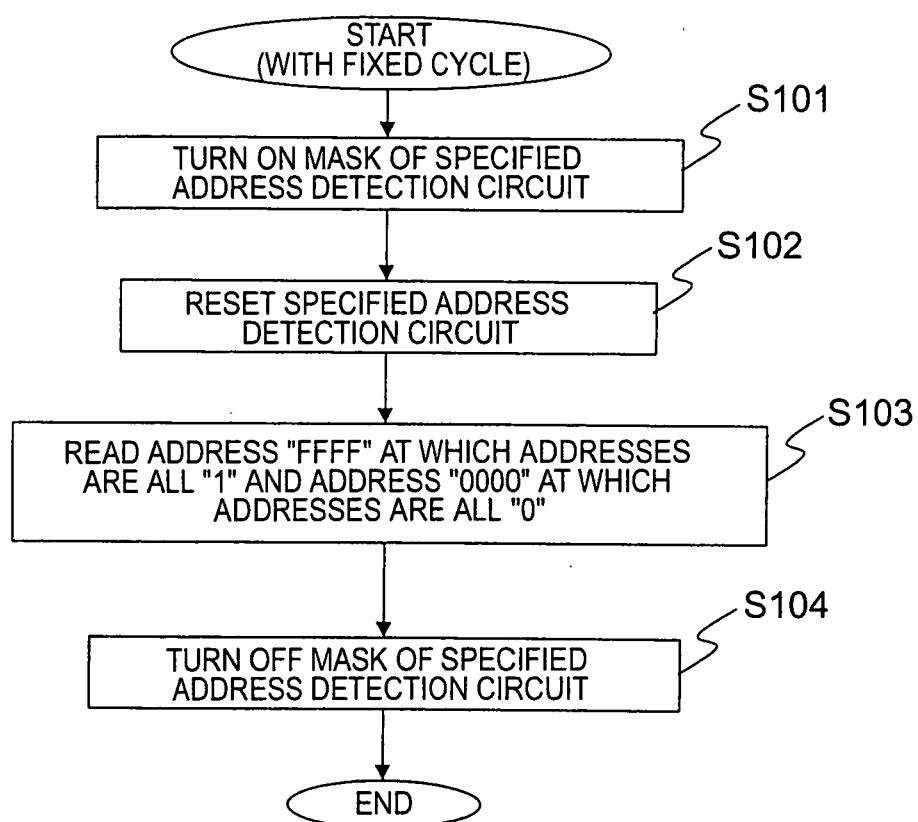

[Fig. 27] A flowchart of a processing operation by designated address output software and a designated address detection circuit in a CPU of Fig. 24.

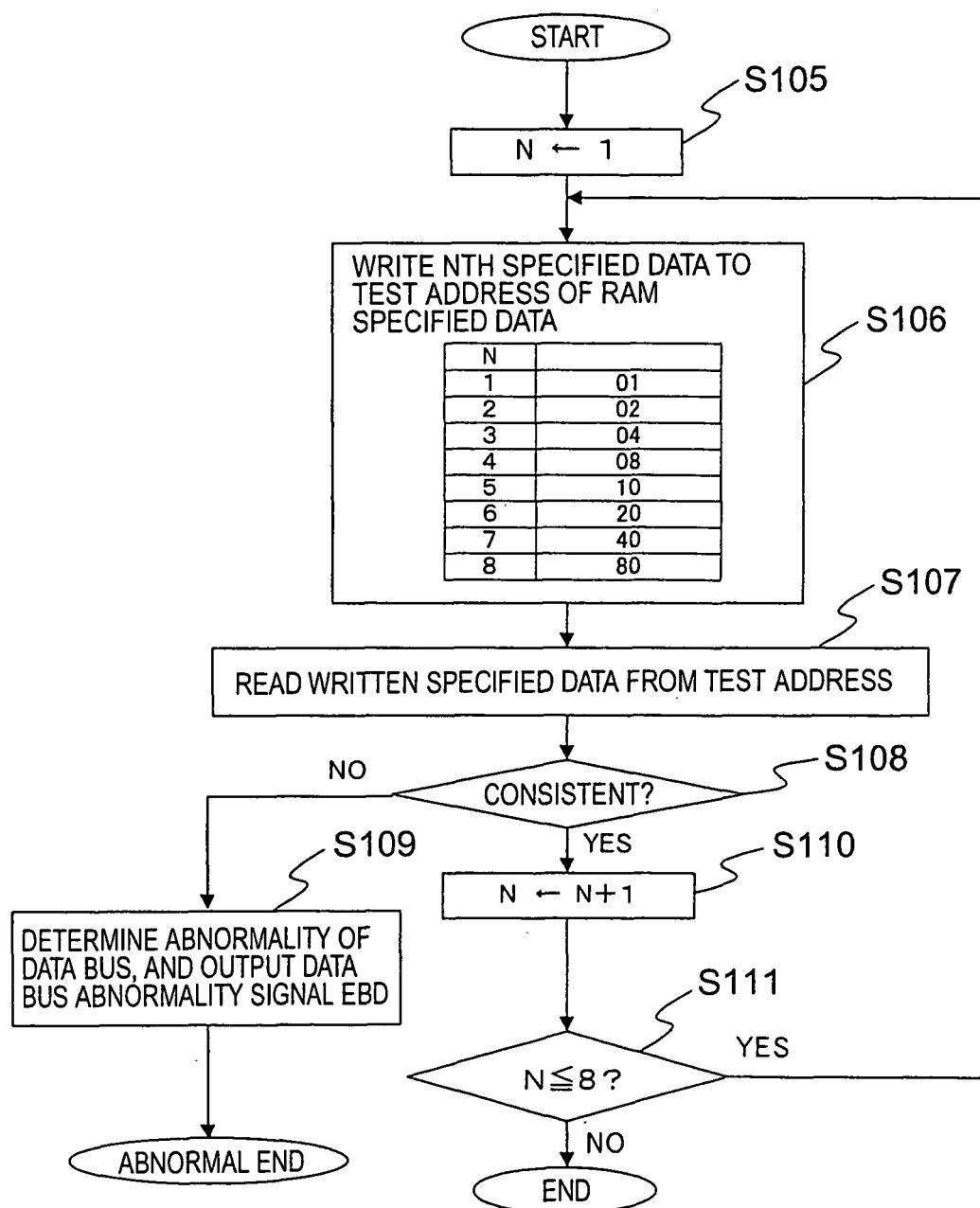

[Fig. 28] A flowchart of a processing operation by data bus abnormality check software in the CPU of Fig. 24.

#### Best Mode for carrying out the Invention

**[0008]** Preferred embodiments of the invention will be hereinafter described with reference to the drawings.

#### First embodiment

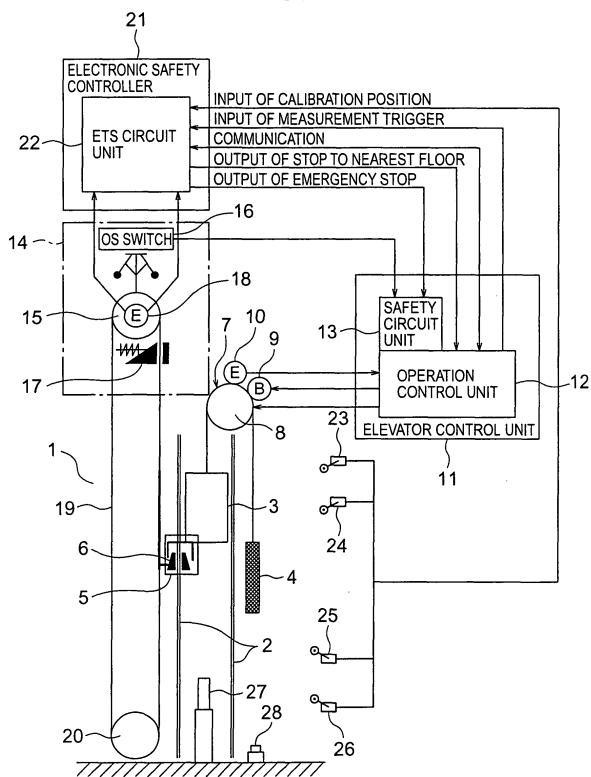

**[0009]** Fig. 1 is a diagram of an elevator apparatus according to a first embodiment of the invention. In the drawing, a hoistway 1 includes a pair of car guide rails 2 and a counterweight guide rail (not shown). A car 3 is raised and lowered in the hoistway 1 while being guided by the car guide rails 2. A counterweight 4 is raised and lowered in the hoistway 1 while being guided by the counterweight guide rail.

**[0010]** In a lower part of the car 3, a safety device 5 that engages with the car guide rails 2 to stop the car 3 in an emergency is provided. The safety device 5 has a pair of braking pieces (wedge members) 6 that are operated by mechanical operation and pushed toward the car guide rails 2.

**[0011]** In the upper part of the hoistway 1, a driving apparatus (traction machine) 7 that raises and lowers the car 3 and the counterweight 4 via a main rope is provided. The driving apparatus 7 has: a drive sheave 8; a motor unit (not shown) that rotates the drive sheave 8; a brake unit 9 that brakes the rotation of the drive sheave 8; and a motor encoder 10 that generates a detection signal according to the rotation of the drive sheave 8.

**[0012]** The brake unit 9 is, for example, an electromagnetic brake apparatus. In the electromagnetic brake apparatus, a spring force of a braking spring is used to push a brake shoe toward a braking surface to brake the rotation of the drive sheave 8 and an electromagnetic magnet is excited to separate the brake shoe from the braking surface to cancel the braking.

**[0013]** An elevator control panel 11 is provided, for example, in a lower part of the hoistway 1. The elevator control panel 11 includes: an operation control unit 12 that controls the operation of the driving apparatus 7; and a safety circuit unit (relay circuit unit) 13 that suddenly stops the car 3 when the elevator has abnormality. The operation control unit 12 is inputted with a detection signal from the motor encoder 10. Based on the detection signal from the motor encoder 10, the operation control unit 12 calculates the position and speed of the car 3 to control the driving apparatus 7.

**[0014]** When the relay circuit of the safety circuit unit 13 is opened, an electric current to the motor unit of the driving apparatus 7 is blocked and an electric current to the electromagnetic magnet of the brake unit 9 is also blocked, whereby the drive sheave 8 is braked.

**[0015]** In the upper part of the hoistway 1, a speed governor (mechanical speed governor) 14 is provided. The speed governor 14 includes: a speed governor sheave 15, an overspeed detection switch 16, a rope catch 17, and a speed governor encoder 18 serving as a sensor. The speed governor sheave 15 is wound at a speed governor rope 19. Both ends of the speed governor rope 19 are connected to the operation mechanism of the safety device 5. The lower end of the speed governor rope 19 is wound around a tightening pulley 20 provided in the lower part of the hoistway 1.

**[0016]** When the car 3 is raised or lowered, the speed governor rope 19 is rotated and the speed governor sheave 15 is rotated at a rotation speed corresponding to a traveling speed of the car 3. The speed governor 14 mechanically detects that the traveling speed of the car 3 reaches an overspeed. Overspeeds to be detected are set as a first overspeed (OS speed) that is higher than a rated speed and a second overspeed (Trip speed) that is higher than the first overspeed.

**[0017]** When the traveling speed of the car 3 reaches the first overspeed, the overspeed detection switch 16 is operated. When the overspeed detection switch 16 is operated, the relay circuit of the safety circuit unit 13 is opened. When the traveling speed of the car 3 reaches the second overspeed, the rope catch 17 grips the speed governor rope 19 to stop

the rotation of the speed governor rope 19. When the rotation of the speed governor rope 19 is stopped, the safety device 5 provides a braking operation.

**[0018]** The speed governor encoder 18 generates a detection signal according to the rotation of the speed governor sheave 15. The speed governor encoder 18 is a dual sense type encoder that simultaneously outputs two types of detection signals, i.e., first and second detection signals.

**[0019]** The first and second detection signals from the speed governor encoder 18 are inputted to an ETS circuit unit 22 of an Emergency Terminal Slowdown apparatus (ETS apparatus) provided at an electronic safety controller 21. The ETS circuit unit 22 detects, based on a detection signal from the speed governor encoder 18, abnormality of an elevator to output an instruction signal for shifting the elevator to a safe state. In other words, the ETS circuit unit 22 calculates, based on the signal from the speed governor encoder 18, the traveling speed and a position of the car 3 independent of the operation control unit 12 and monitors whether the traveling speed of the car 3 in the vicinity of a terminal landing reaches an ETS monitoring overspeed.

**[0020]** The ETS circuit unit 22 also converts the signal from the speed governor encoder 18 to a digital signal to perform a digital arithmetic processing and determine whether the traveling speed of the car 3 reaches an ETS monitoring overspeed. When the ETS circuit unit 22 determines that the traveling speed of the car 3 reaches the ETS monitoring overspeed, the relay circuit of safety circuit unit 13 is opened.

**[0021]** The ETS circuit unit 22 can also detect abnormality of the ETS circuit unit 22 itself and abnormality of the speed governor encoder 18. When the ETS circuit unit 22 detects abnormality of the ETS circuit unit 22 itself or abnormality of the speed governor encoder 18, the ETS circuit unit 22 outputs a nearest floor stop instruction signal as an instruction signal for shifting the elevator to a safe state to the operation control unit 12. The ETS circuit unit 22 can also have an interactive communication with the operation control unit 12.

**[0022]** In predetermined positions in the hoistway 1, there are provided first to fourth reference sensors 23 to 26 for detecting that the car 3 is located at a reference position in the hoistway. The reference sensors 23 to 26 can be top and bottom terminal landing switches. Detection signals from the reference sensors 23 to 26 are inputted to the ETS circuit unit 22. Based on the detection signals from the reference sensors 23 to 26, the ETS circuit unit 22 corrects the information for the position of the car 3 calculated in the ETS circuit unit 22.

**[0023]** Between a bottom face of the hoistway 1 and lower faces of the car 3 and the counterweight 4, a car buffer 27 and a counterweight buffer 28 are respectively provided. Here, the car buffer 27 and the counterweight buffer 28 are provided in the lower part in the hoistway 1. The car buffer 27 is provided just below the car 3 and reduces an impact caused when the car 3 collides with a bottom part of the hoistway 1. The counterweight buffer 28 is provided just below the counterweight 4 and reduces an impact caused when the counterweight 4 collides with a bottom part of the hoistway 1. These buffers 27 and 28 may be, for example, an oil-filled-type or spring-type buffer.

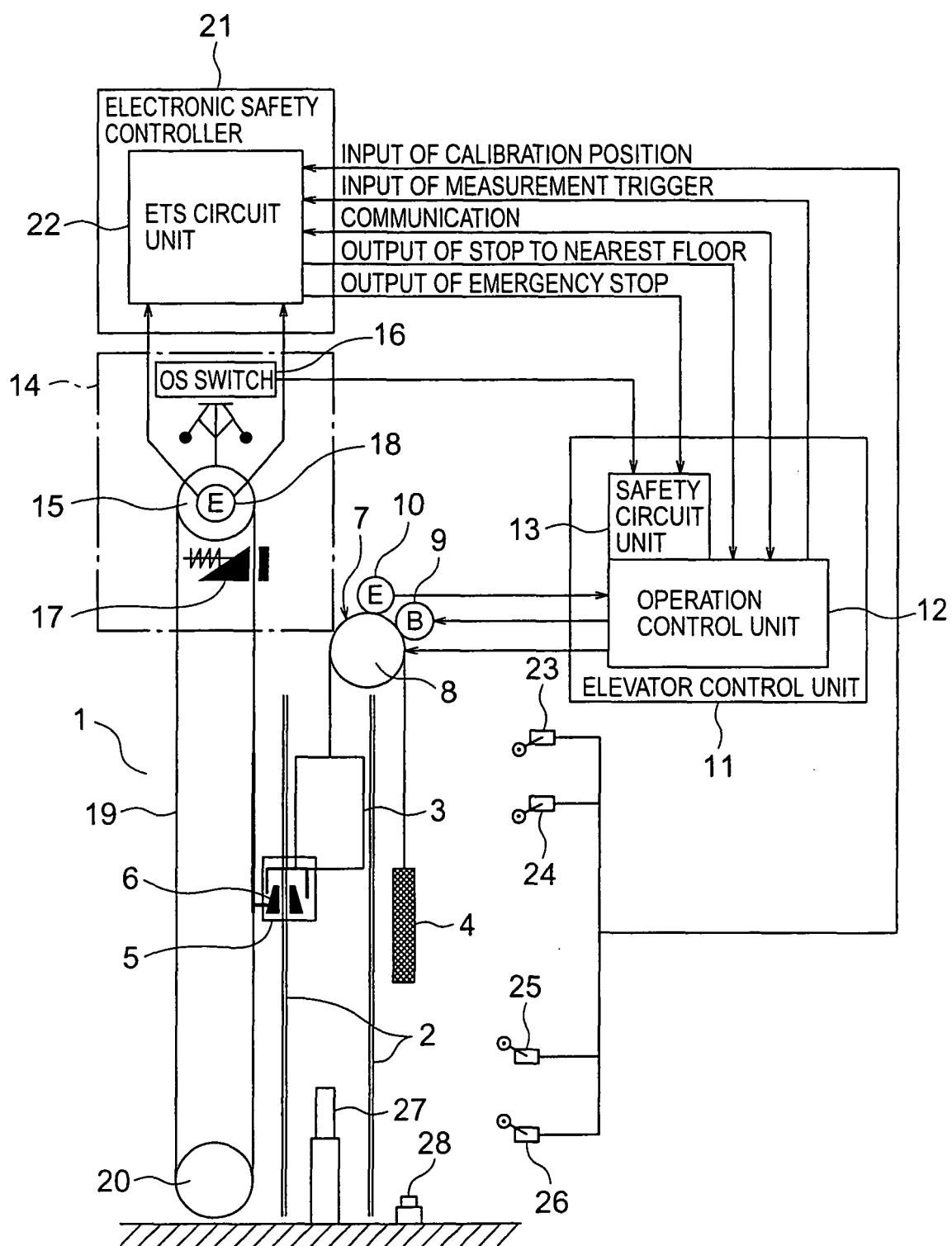

**[0024]** Fig. 2 is a graph of overspeed patterns set in the speed governor 14 and the ETS circuit unit 22 of Fig. 1. In the drawing, when the car 3 travels at a normal speed (rated speed) from a bottom terminal landing to a top terminal landing, the car 3 draws a normal speed pattern V0. The speed governor 14 is associated with first and second overspeed patterns V1 and V2 by a mechanical position adjustment. The ETS circuit unit 22 is associated with an ETS monitoring overspeed pattern VE.

**[0025]** The ETS monitoring overspeed pattern VE is set to be higher than the normal speed pattern V0. The ETS monitoring overspeed pattern VE is also set to have an equal interval from the normal speed pattern V0 in the entire ascending/descending process. In other words, the ETS monitoring overspeed pattern VE changes according to a car position. More specifically, the ETS monitoring overspeed pattern VE is set to be fixed in the vicinity of an intermediate floor and is set to continuously and smoothly decline, in the vicinity of a terminal landing, while being closer to an end of the hoistway 1 (upper end and lower end). In this manner, the ETS circuit unit 22 monitors the traveling speed of the car 3 not only in a position in the vicinity of a terminal landing but also in a position in the vicinity of an intermediate floor (a fixed speed traveling zone in the normal speed pattern V0). However, the ETS circuit unit 22 does not always have to monitor the traveling speed of the car 3 in a position in the vicinity of the intermediate floor.

**[0026]** The first overspeed pattern V1 is set to be higher than the ETS monitoring overspeed pattern VE. The second overspeed pattern V2 is set to be higher than the first overspeed pattern V1. The first and second overspeed patterns V1 and V2 are fixed at all heights in the hoistway 1.

**[0027]** The counterweight buffer 28 has a buffer stroke that is set, according to a collision speed of the counterweight 4 to the counterweight buffer 28 limited by the ETS circuit unit 22, to be shorter than a stroke specified according to a collision speed limited by the speed governor 14. The car buffer 27 has a buffer stroke specified according to the collision speed limited by the speed governor 14.

**[0028]** The buffers 27 and 28 have a buffer stroke that is determined according to an initial speed at the time when the car 3 or the counterweight 4 first come into contact with the buffer 27 or 28 and an allowable deceleration until the car 3 or the counterweight 4 stops. Thus, the buffer stroke of the car buffer 27 is set to be shorter than the buffer stroke of the counterweight buffer 28. In other words, the buffer stroke of the counterweight buffer 28 is set to be shorter than the buffer stroke of the car buffer 27.

[0029] The counterweight buffer 28 has a sufficient capacity so as to not to be broken even when the counterweight buffer 28 collides with the counterweight 4 at speed higher than speed specified in the ETS monitoring overspeed pattern VE (e.g., when the main rope is broken). The sufficient capacity of the counterweight buffer 28 may be secured, for example, by using a buffer having a capacity higher than a general capacity or by using plural buffers having a general capacity.

[0030] A size of a clearance between the upper end part of the car 3 and the ceiling part of the hoistway 1 at the time when the car 3 reaches a top floor is set according to a collision speed of the counterweight 4 with the counterweight buffer 28 that is limited by the ETS circuit unit 22. In other words, the size of a clearance at the top part of the hoistway 1 is set so as to prevent, even when the counterweight 4 collides with the counterweight buffer 28, the car 3 from colliding with the ceiling part of the hoistway 1.

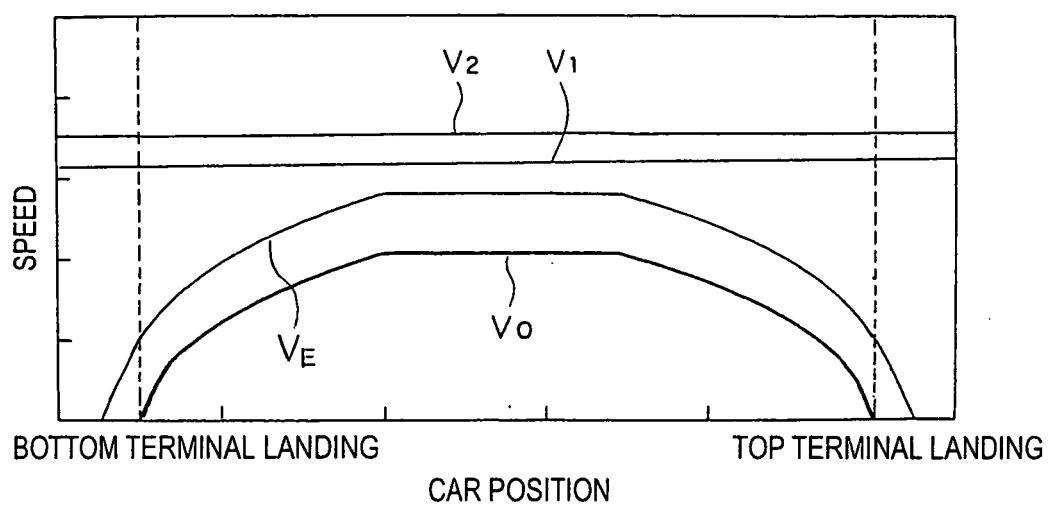

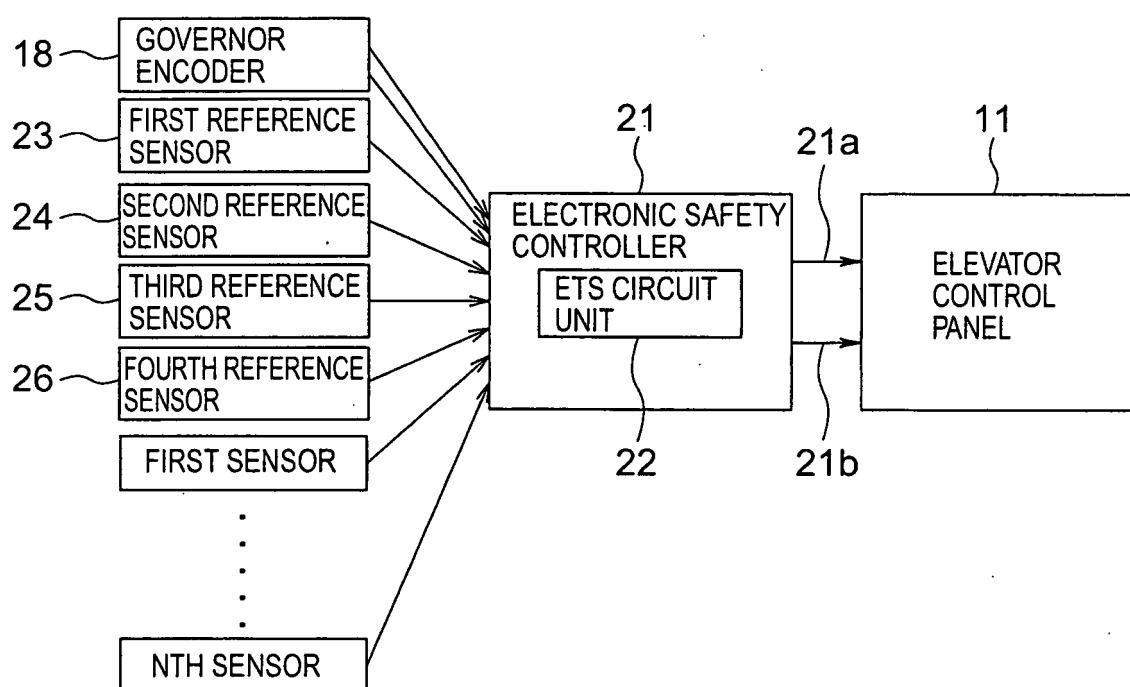

[0031] Fig. 3 is a block diagram of a relation of connection among the electronic safety controller 21, the elevator control panel 11, and various sensors of Fig. 1. In the figure, the electronic safety controller 21 is inputted with two types of detection signals from the speed governor encoder 18, that is, detection signals from the first to fourth reference sensors 23 to 26 and signals from other sensors (first to Nth sensor). The electronic safety controller 21 also has plural signal input ports corresponding to the respective sensors. In other words, the electronic safety controller 21 receives separate signals from the respective sensors as inputs. Thus, the electronic safety controller 21 can detect abnormality of the respective sensors.

[0032] When the electronic safety controller 21 detects some abnormality (e.g., overspeed, sensor failure, or abnormality of the electronic safety controller 21 itself), a failure/abnormality content signal including content of the failure or abnormality is inputted to a control unit (not shown) of the elevator control panel 11 and a stop signal according to the content of the failure or abnormality is inputted to a driving/braking unit (not shown) of the elevator control panel 11.

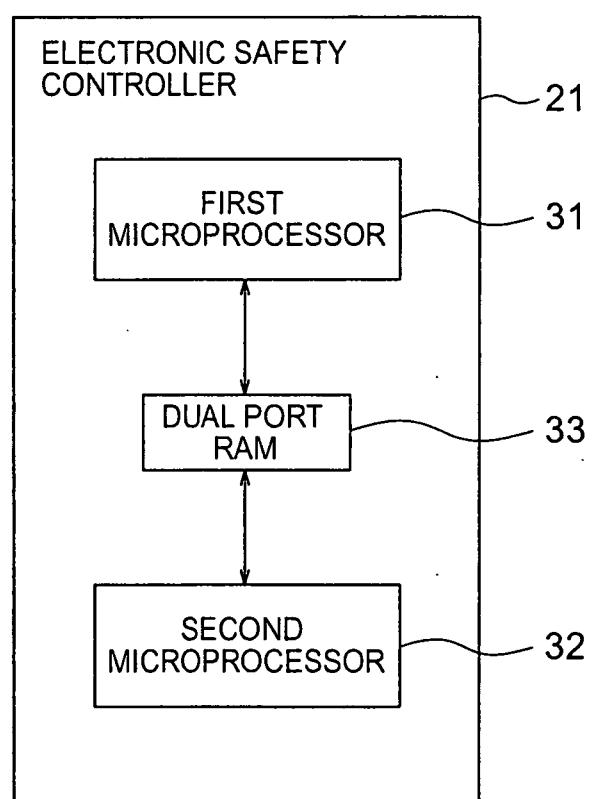

[0033] Fig. 4 is a block diagram of the apparatus configuration of the main part of the electronic safety controller 21 of Fig. 1. The electronic safety controller 21 includes: a first microprocessor 31 that performs arithmetic processing for detecting abnormality of the elevator based on a first safety program; and a second microprocessor 32 that performs arithmetic processing for detecting abnormality of the elevator based on a second safety program.

[0034] The first safety program is a program that has the same content as that of the second safety program. The first and second microprocessors 31 and 32 can have mutual communication via an interprocessor bus and a dual port RAM 33. The first and second microprocessors 31 and 32 can also check the soundness of the first and second microprocessors 31 and 32 themselves by mutually comparing the results of the arithmetic processing. In other words, the soundness of the first and second microprocessors 31 and 32 is checked by causing the first and second microprocessors 31 and 32 to perform an identical processing and the processing results are communicated and compared via the dual port RAM 33 or the like.

[0035] In addition to the abnormality of the microprocessors 31 and 32 themselves, the microprocessors 31 and 32 can also detect abnormality of the electronic safety controller 21 by arithmetic processing.

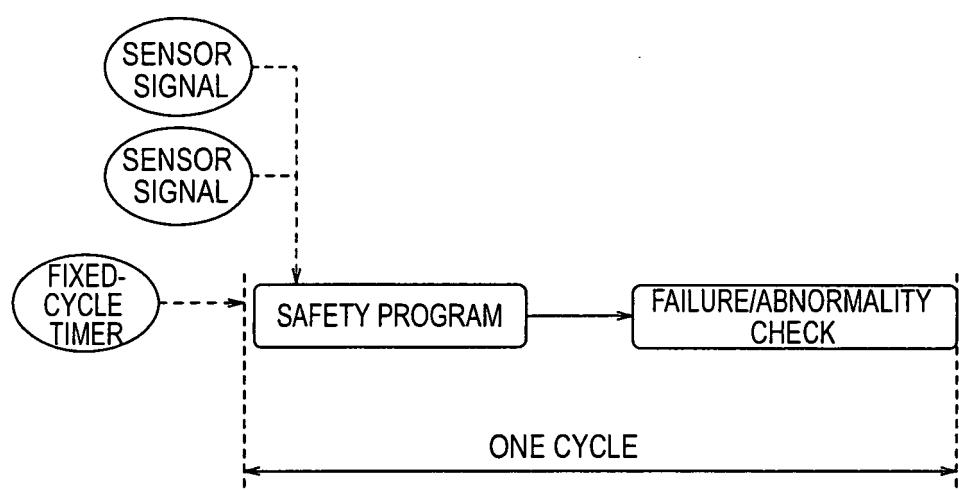

[0036] Fig. 5 is an explanatory diagram of a method of performing arithmetic processing by the microprocessors 31 and 32 of Fig. 4. The microprocessors 31 and 32 repeatedly perform arithmetic processing with a predetermined computation cycle (e.g., 50 msec) based on a signal from a fixed-cycle timer and according to a program stored in a ROM. A program executed in one cycle includes a safety program for detecting abnormality of an elevator and a failure/abnormality check program for detecting the failure/abnormality of the electronic safety controller 21 itself and various sensors. The failure/abnormality check program may be executed only when predetermined states are satisfied.

[0037] In the elevator apparatus, the electronic safety controller 21 can detect abnormality of the electronic safety controller 21 itself and outputs, even when abnormality of the electronic safety controller 21 itself is detected, an instruction signal for shifting the elevator to a safe state. Thus, a relatively-simple structure can be used to improve the reliability of a safety system while improving speed to detect abnormality of an elevator and speed of the processing for the abnormality.

[0038] The electronic safety controller 21 can also detect abnormality of various sensors and can output, even when abnormality of the sensor is detected, an instruction signal for shifting the elevator to a safe state. Thus, the safety system can have a further improved reliability.

[0039] Furthermore, the electronic safety controller 21 includes first and second microprocessors 31 and 32. The first and second microprocessors 31 and 32 can check the soundness of the first and second microprocessors 31 and 32 themselves by mutually comparing results of the arithmetic processing. Thus, the safety system can have a further improved reliability.

[0040] Specific examples of a constitution and an operation of the electronic safety controller 21 will be hereinafter explained.

55

«Detection of clock abnormality»

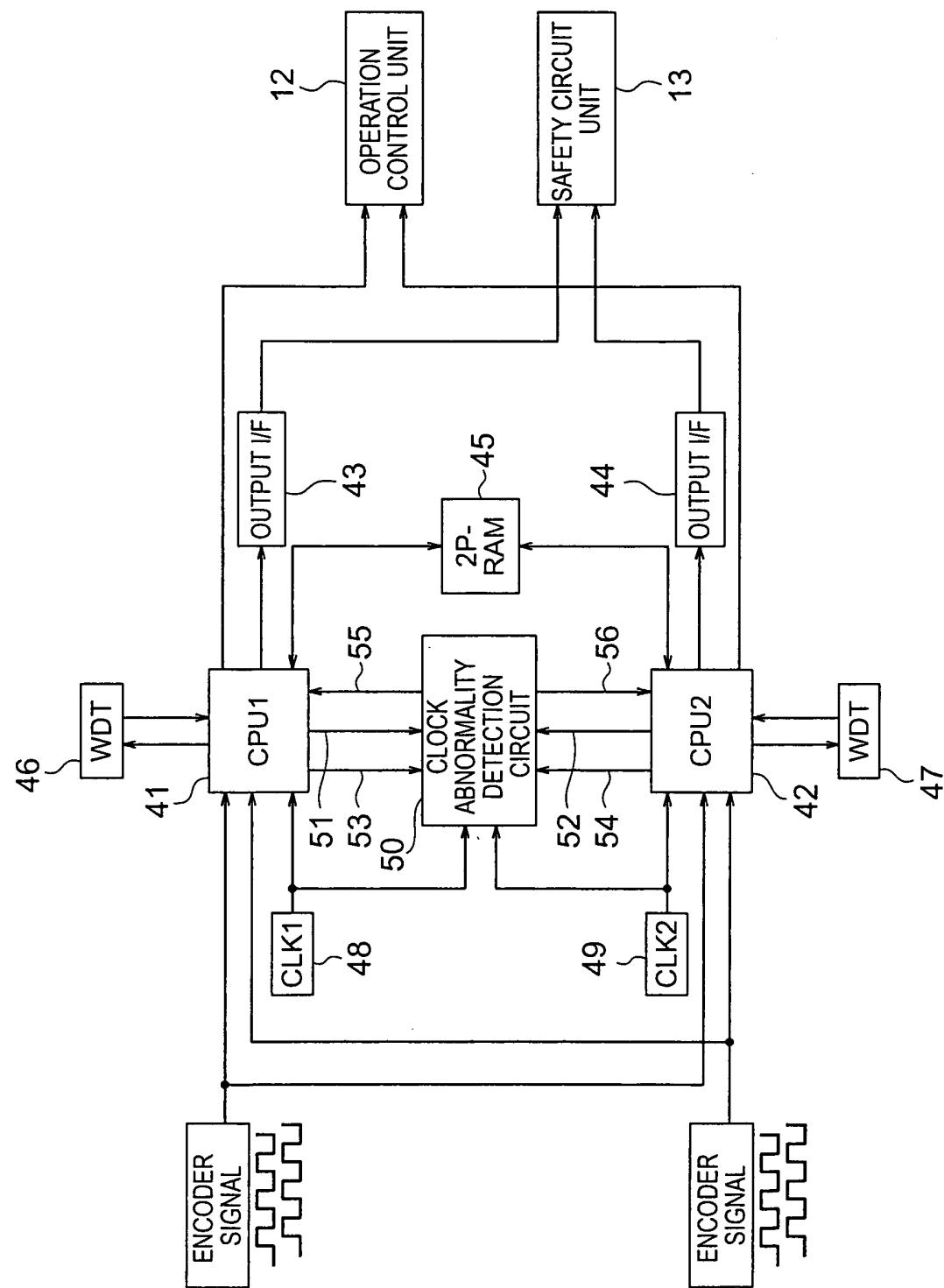

[0041] Fig. 6 is a block diagram of the main part of the electronic safety controller 21 of Fig. 1. To secure a sufficient

reliability, the electronic safety controller 21 adopts a double circuit configuration.

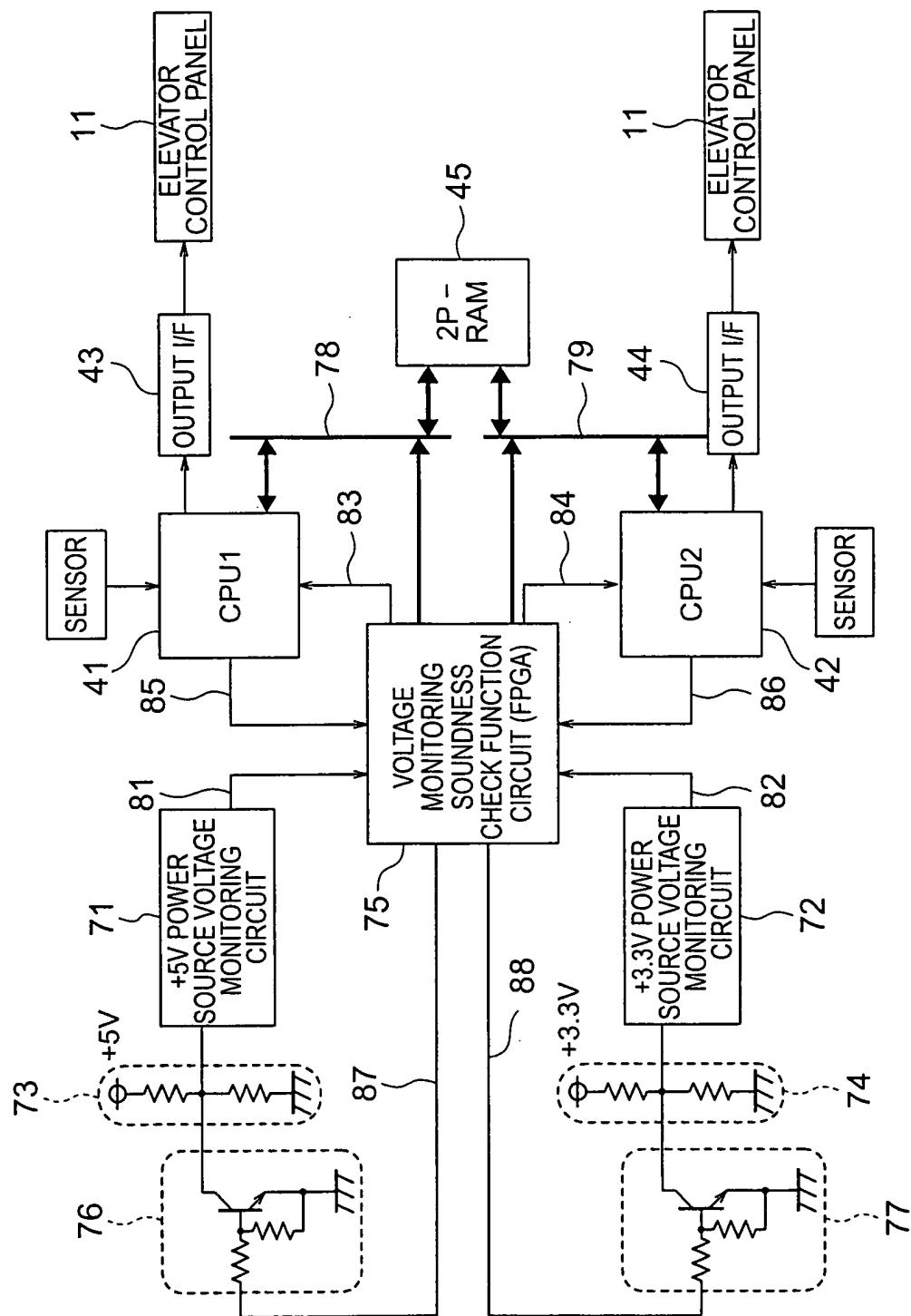

[0042] The electronic safety controller 21 uses first and second CPUs (processing units) 41 and 42 as the first and second microprocessors. The first CPU 41 outputs control signals to the operation control unit 12 and a first output interface (output unit) 43. The second CPU 42 outputs control signals to the operation control unit 12 and a second output interface (output unit) 44.

[0043] When receiving the control signals from the first and second CPUs 41 and 42, the operation control unit 12 is controlled by the control signals. Based on the control signals from the first and second CPUs 41 and 42, the first and second output interfaces 43 and 44 output signals for opening the safety circuit unit 13.

[0044] The first and second CPUs 41 and 42 are connected to a dual port RAM 45 to perform data transfer between the CPUs. The first CPU 41 is connected to a first watchdog timer 46. The second CPU 42 is connected to a second watchdog timer 47.

[0045] The first CPU 41 has two types of signals from the speed governor encoder 18 (Fig. 1) as inputs. The second CPU 42 has also two types of signals from the speed governor encoder 18 as inputs. The signals from the speed governor encoder 18 are subjected to the arithmetic processing by the CPUs 41 and 42, whereby speed and a position of the car 3 are calculated (Fig. 1). In other words, the speed governor encoder 18 functions both as speed sensor and a position sensor. The CPUs 41 and 42 have also signals from various sensors as inputs as shown in Fig. 3.

[0046] The first CPU 41 has a first clock signal from the first clock 48 as an input. The second CPU 42 has a second clock signal from the second clock 49 as an input. The first and second clock signals are set to have an identical frequency.

[0047] The first and second clock signals are also inputted to a clock abnormality detection circuit 50. The clock abnormality detection circuit 50 counts the number of pulses of the first and second clock signals to detect, based on the difference of the number of pulses, abnormalities of the first and second clock signals.

[0048] The first and second CPUs 41 and 42 transmit, to the clock abnormality detection circuit 50, test mode signals 51 and 52 to check the soundness of the clock abnormality detection circuit 50. The first and second CPUs 41 and 42 also transmits, to the clock abnormality detection circuit 50, detection start instruction signals 53 and 54 to start the detection of clock abnormality.

[0049] When clock abnormality is detected, the clock abnormality detection circuit 50 inputs error signals 55 and 56 to the first and second CPUs 41 and 42.

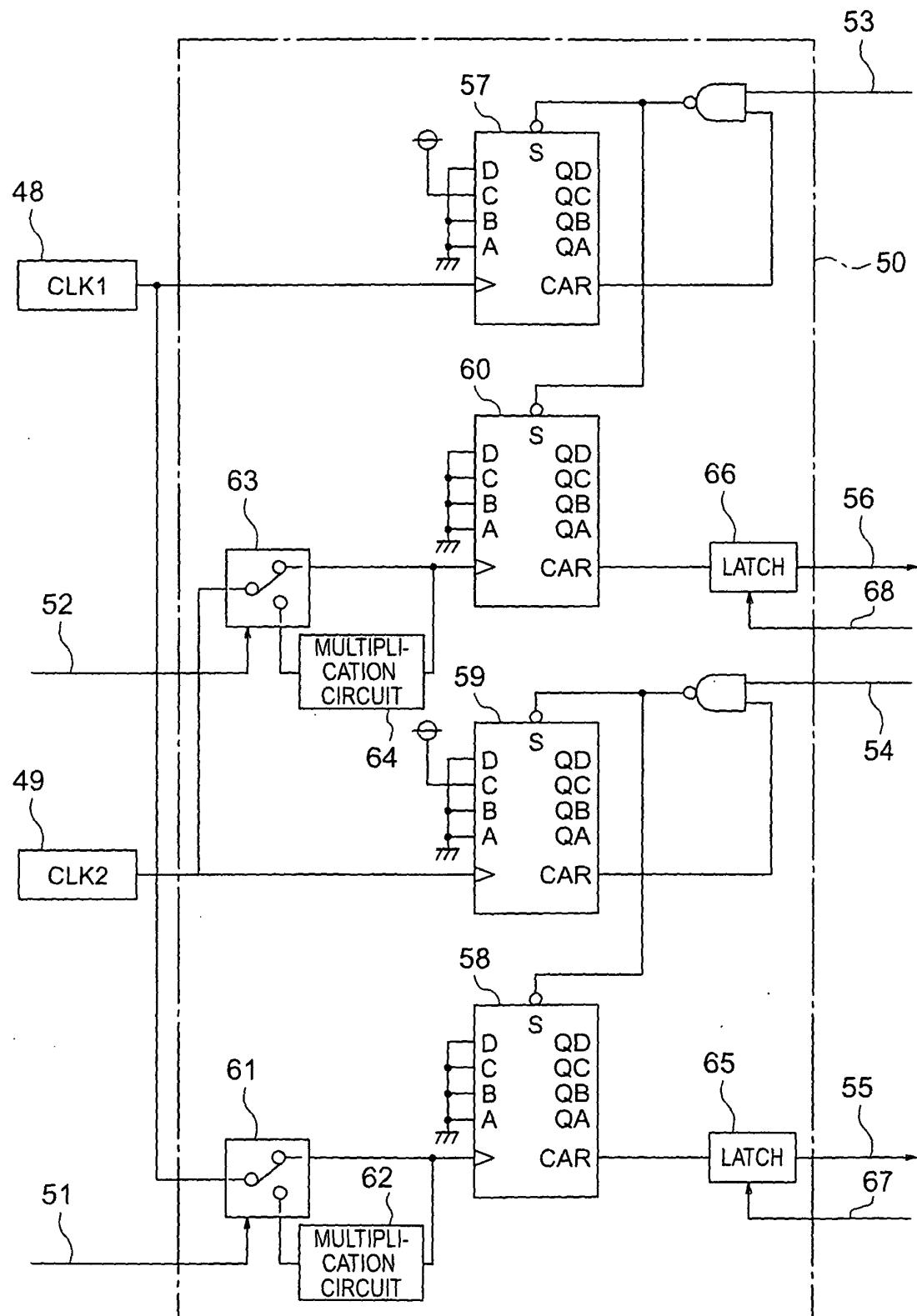

[0050] Fig. 7 is a diagram of a specific structure of the clock abnormality detection circuit 50 of Fig. 6. The clock abnormality detection circuit 50 includes: a first monitoring counter 57 and a first monitored counter 58 for counting pulse edges of the first clock signal; and a second monitoring counter 59 and a second monitored counter 60 for counting pulse edges of the second clock signal.

[0051] The first clock signal is inputted to the first monitored counter 58 via a first selector 61. The first selector 61 can provide switching between a normal circuit and a test circuit. In the normal circuit, the first clock signal is directly inputted to the first monitored counter 58. In the test circuit, the first clock signal is multiplied in the first multiplication circuit 62 to be inputted to the first monitored counter 58. The switching to the test circuit is performed when the test mode signal 51 from the first CPU 41 is inputted to the first selector 61.

[0052] Similarly, the second clock signal is inputted to the second monitored counter 60 via the second selector 63. The second selector 63 can provide switching between the normal circuit and the test circuit. In the normal circuit, the second clock signal is directly inputted to the second monitored counter 60. In the test circuit, the second clock signal is multiplied by the second multiplication circuit 64 and then inputted to the second monitored counter 60. The switching to the test circuit is performed when the test mode signal 52 from the second CPU 42 is inputted to the second selector 63.

[0053] Ripple carry output signals (i.e., error signals 55 and 56) from the first and second monitored counters 58 and 60 are latched by first and second latch units 65 and 66. The first and second latch units 65 and 66 cancel the latch status when the latch units receive latch cancellation signals 67 and 68 from the first and second CPUs 41 and 42.

[0054] When error signals from the clock abnormality detection circuit 50 are inputted to the CPUs 41 and 42, the CPUs 41 and 42 output abnormality detection signals to the output interfaces 43 and 44. Then, the output interfaces 43 and 44 output operation signals to the safety circuit unit 13. The safety circuit unit 13 shifts the elevator to a safe state.

[0055] The electronic safety controller 21 includes a computer (microcomputer) including the CPUs 41 and 42 and a ROM shown in Fig. 6.

[0056] Next, the operation will be explained. Two types of pulse signals outputted from the speed governor encoder 18 are inputted to the CPUs 41 and 42. Then, the pulse signals are subjected to the arithmetic processing by the respective CPUs 41 and 42, whereby a position and speed of the car 3 are calculated. The calculated position and speed are compared with each other via the dual port RAM 45 to be subsequently compared with a set value (reference value) to determine abnormality (e.g., ETS monitoring overspeed).

[0057] When abnormality such as overspeed or an abnormal position is detected, a signal is outputted, according to the contents of the abnormality, to the operation control unit 12 or the safety circuit unit 13 to shift the elevator to a safe state. The expression "shift the elevator to a safe state" means, for example, suddenly stopping the car 3 or stopping the car 3 at the nearest floor. After shifting the elevator to a safe state, the operation control unit 12 is further controlled

as required.

**[0058]** Shift of the elevator to a safe state is also performed when the CPUs 41 and 42 have different computation results and it is judged that any system of the CPUs 41 and 42 has abnormality.

When the calculated position and speed have no abnormality, a control signal for permitting the traveling of the car 3 is generated and is outputted to the operation control unit 12.

**[0059]** The CPUs 41 and 42 perform the computation to calculate a car speed by counting pulse signals inputted within a fixed time. A timer that measures the "fixed time" is generated by clock signals from the clocks 48 and 49. Thus, the frequency of a clock signal is very important.

**[0060]** When overspeed of the car 3 is monitored, attention must be paid to, in particular, abnormality causing a higher frequency. The reason is that, when a clock signal cycle is halved due to some failure when pulse signals are intended to be counted every 10ms, pulse signals are actually counted every 5ms despite the intention. In this case, the car speeds calculated by the CPUs 41 and 42 are mistakenly recognized as the halves of an actual car speed, thus causing a situation where the overspeed cannot be detected.

**[0061]** On the other hand, in this example, the clock signals from the first and second clocks 48 and 49 are inputted to the clock abnormality detection circuit 50 and it is monitored whether the clock signals have abnormality.

**[0062]** Next, an operation for monitoring a clock abnormality will be explained in detail. First, when a power source is reset, the counters 57 to 60 immediately start counting clock pulses as soon as the respective devices are stabilized. As a result, the error signals 55 and 56 are latched. However, at first, the CPUs 41 and 42 ignore these error signals 55 and 56.

**[0063]** Thereafter, the detection start instruction signals 53 and 54 are given with High signals. Then, the latch cancellation signals 67 and 68 are sent from the CPUs 41 and 42 to the clock abnormality detection circuit 50.

**[0064]** With the first ripple carry output signals from the monitoring counters 57 and 59 after the detection start instruction signals 53 and 54 are High, preset data values of the respective counters 57 to 60 are loaded to the respective counters 57 to 60 to start a countup. The preset data values are count values at which the count by the counters 57 to 60 is started.

**[0065]** Preset data values of the monitored counters 58 and 60 are set to be, for example, 0 in advance. As preset data values of the monitoring counters 57 and 59, threshold values for judging a clock abnormality are set in advance. The preset data values of the monitoring counters 57 and 59 are set to be higher than the preset data values of the monitored counters 58 and 60 (set to 4 in this example).

**[0066]** The monitoring counters 57 and 59 repeatedly count the number of pulses in a range smaller than those covered by the monitored counters 58 and 60 and reset the monitored counters 57 and 59 whenever the carryover thereof is caused. The monitored counters 58 and 60 also try to repeatedly count the number of pulses. However, when no abnormality is caused, the carryover of the monitoring counters 57 and 59 is caused prior to the carryover of the monitored counters 58 and 60 to reset the monitored counters 58 and 60.

**[0067]** The preset data values can be arbitrarily set by configuring the clock abnormality detection circuit 50 by, for example, an FPGA (field programmable gate array).

**[0068]** When the two clocks 48 and 49 have no abnormality, the monitored counters 58 and 60 are reset by the ripple carry output signals of the monitoring counters 57 and 59 at a counter value that is smaller by four than a counter value at which the carryover of the monitored counters 58 and 60 is caused and a ripple carry output signal (i.e., error signals 55 and 56) is outputted. Thus, the error signals 55 and 56 are not outputted.

**[0069]** On the other hand, when abnormality in which a frequency of, for example, the first clock 48 is increased is caused, prior to the reset of the first monitored counter 58 by the ripple carry output signal of the second monitoring counter 59, the ripple carry output signal of the first monitored counter 58 (i.e., error signal 55) is outputted and the error signal 55 is latched by the latch unit 65.

**[0070]** When abnormality is caused in which a frequency of the second clock 49 is increased, the error signal 56 is similarly outputted from the second monitored counter 60 and the error signal 56 is latched by the latch unit 66.

**[0071]** Furthermore, when the clocks 48 and 49 are stopped, the stop can also be detected by the clock abnormality detection circuit 50. However, the watchdog timers 46 and 47 work to provide a forced reset to prevent a dangerous state.

**[0072]** This mechanism eliminates the need to use an exclusive clock for detecting a clock abnormality and can directly use the clocks 48 and 49 used for the double CPUs 41 and 42 for detecting a clock abnormality. This makes it possible to efficiently use of hardware resource. Therefore, a simple circuit configuration can be used to improve the reliability.

**[0073]** Since it is also possible to arbitrarily set preset data values of the counters 57 to 60, a critical frequency drift can also be detected. As a result, time during which the operation is delayed until the safety circuit unit 13 is driven and controlled can be reduced and a safer design can be realized.

**[0074]** Furthermore, since the four counters 57 to 60 and the watchdog timers 46 and 47 are used in combination, it is possible to easily specify in which of the clocks 48 and 49 abnormality of an increasing frequency has occurred.

**[0075]** Next, a function to check the soundness of the clock abnormality detection circuit 50 will be explained. For example, when the test mode signal 51 is sent from the first CPU 41 to the clock abnormality detection circuit 50, the selector 61 provides switching to the test circuit and the first clock signal is multiplied by the first multiplication circuit 62.

In other words, the first clock signal inputted to the first monitored counter 58 is put in an abnormal state purposely. As a result, when the clock abnormality detection circuit 50 has no abnormality, the first monitored counter 58 will output the error signal 55.

**[0076]** Therefore, in the CPU 41, the error signal 55 is received in response to the transmission of the test mode signal 51. As a result, the soundness of the clock abnormality detection circuit 50 can be checked. Similarly, the soundness of the second clock 49 can also be checked.

**[0077]** By adding the function to check the soundness of the clock abnormality detection circuit 50, such a failure that a final output pin of the clock abnormality detection circuit 50 is fixed to the normal side can be detected and the reliability can be further improved.

**[0078]** Although the double circuit configuration using two CPUs is described in this embodiment, a multiple circuit configuration using three or more CPUs may be used.

**[0079]** In this manner, the electronic safety controller 21 of this example includes: the first and second processing units to doubly perform a computation for the control of the elevator; the first clock that sends the first clock signal to the first processing unit; the second clock that sends the second clock signal to the second processing unit; and the clock abnormality detection circuit that is inputted with the first and second clock signals to detect abnormality of the first and second clock signals. The clock abnormality detection circuit counts the number of pulses of the first and second clock signals to detect, based on the difference in the number of pulses, the abnormality of the first and second clock signals.

**[0080]** The clock abnormality detection circuit has a monitored counter that counts the number of pulses of any one of the first and second clock signals and a monitoring counter that counts the number of pulses of the other of the first and second clock signals. A preset data value as a count value at which the counting by the monitored counter is started is set to be higher than a preset data value as a count value at which the counting by the monitoring counter is started. When the carryover of the monitoring counter is caused, the number counted by the monitored counter is reset and the carryover of the monitored counter is caused. Abnormality of the first and second clock signals is detected.

**[0081]** Furthermore, the monitoring counter includes the first monitoring counter that counts the number of pulses of the first clock signal and the second monitoring counter that counts the number of pulses of the second clock signal. The monitored counter includes a first monitored counter that counts the number of pulses of the first clock signal and a second monitored counter that counts the number of pulses of the second clock signal.

**[0082]** Furthermore, the preset data value of the monitoring counter can be arbitrarily set. By putting a clock signal inputted to the monitored counter in the test mode in an abnormal state purposely, the soundness of the clock abnormality detection circuit can be checked. Furthermore, the clock abnormality detection circuit includes the multiplication circuit that multiplies the clock signal inputted to the monitored counter in the test mode.

<<Detection of abnormality of stack area>>

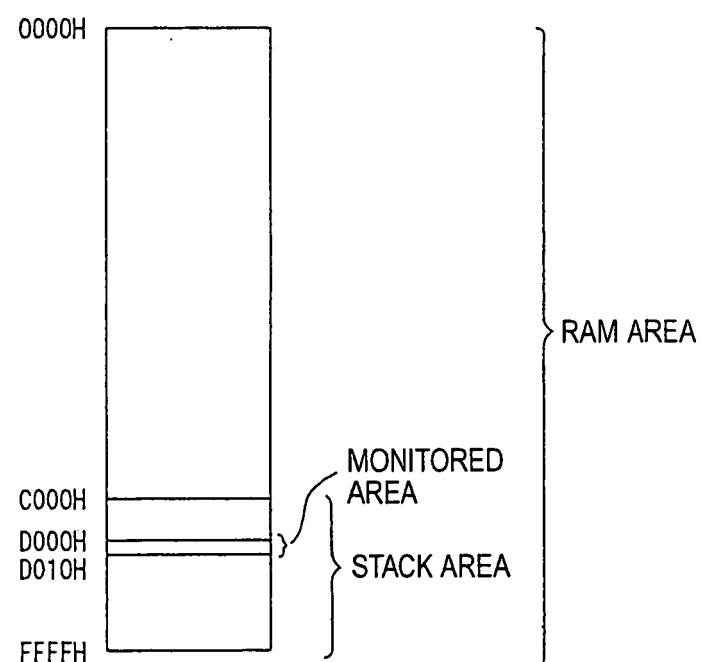

**[0083]** Next, detection of abnormality of a stack area in a RAM used in the electronic safety controller 21 will be explained. Fig. 8 is an explanatory diagram of separated areas of the electronic safety controller 21 of Fig. 1. The RAM includes a stack area that stores information required for computation by the CPU. The stack area stores therein, for example, a return address of a subroutine call, a return address of a timer interrupt, and an argument of a subroutine call.

**[0084]** The ROM stores therein a program for monitoring a predetermined monitored area in the stack area of the RAM. In other words, the stack area monitoring unit has a CPU and a ROM.

**[0085]** In this example, areas of C000H to FFFFH are set as stack areas. Areas of D000H to D010H are set as monitored areas.

**[0086]** A method of using a stack area is determined according to a microcomputer and is generally provided such that data is accumulated from an end address to preceding addresses in this order by a stack pointer owned by the microcomputer. In the case of Fig. 8, an initial value of the stack pointer is FFFFH and data is accumulated to addresses in an order of FFFFH, FFFEH, FFFDH, ..., C001H, and C000H. Thus, monitored areas D000H to D010H are areas that are used when 75% of the stack areas is used.

**[0087]** A monitored area in a position where 50% or more stack areas are used is preferable. A monitored area in a position where 60% or more stack areas are used is particularly preferable. A monitored area in a position where 90% or less stack areas are used is also preferable. A monitored area in a position where 80% or less stack areas are used is particularly preferable.

**[0088]** Stack areas are set to be 0 in advance. The stack area monitoring unit monitors whether the entirety of a monitored area is 0. When the monitored area includes data other than 0, the stack area monitoring unit judges that a stack over is caused.

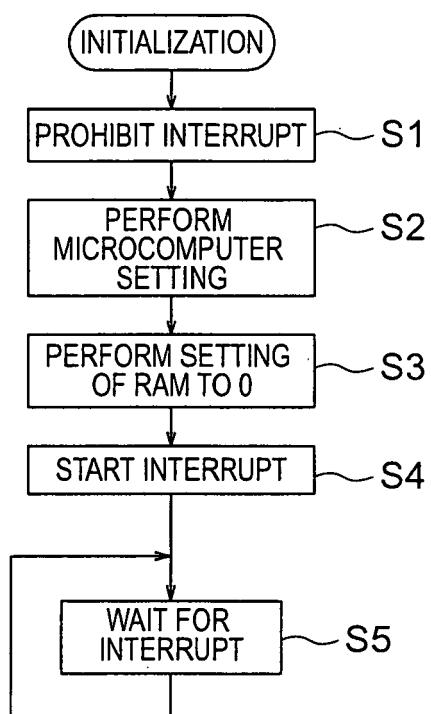

**[0089]** Fig. 9 is a flowchart of an initial operation of the electronic safety controller 21 of Fig. 1. When the elevator is started, the electronic safety controller 21 is initialized. When the initialization is started, all interrupt computations are prohibited (step S1). Thereafter, the microcomputer is initialized (step S2) and the RAM area is set to be 0 (step S3). After that, an interrupt computation becomes possible (step S4) and an interrupt is waited (step S5). An interrupt

computation is repeatedly performed at every computation cycle time.

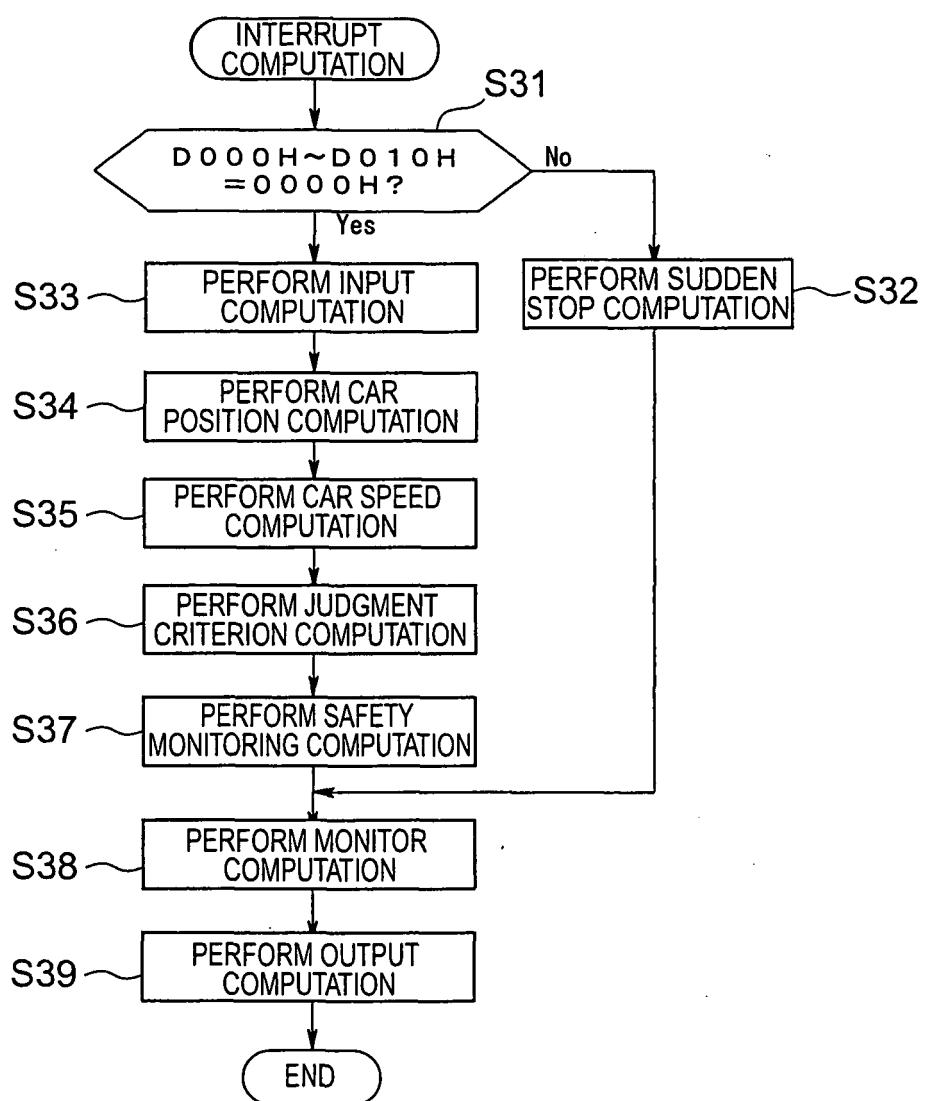

[0090] Fig. 10 is a flowchart of a first example of an interrupt computation by the electronic safety controller 21 of Fig. 1. When the interrupt computation is started, first, the state of monitored areas is checked (step S31). In other words, it is checked whether a state of the monitored areas D000H to D010H is 0000H.

[0091] When the monitored areas are not 0000H, it is judged that the RAM has a stack over or is highly likely to be in a stack over. In other words, values of the monitored areas other than 0 lead to a judgment that a time to process an interrupt computation has small margin to prevent the interrupt computation from being completed within a computation cycle time, causing a stack over. When the stack over is detected, a computation for suddenly stopping the car 3 is performed (step S32) and an emergency stop instruction is outputted to the safety circuit unit 13. When the stack over is detected, abnormality detection signal is sent to an elevator monitoring room.

[0092] When the monitored areas have no abnormality, an input computation for inputting a signal required for a computation is performed (step S33). A car position computation for calculating a current position of the car 3 and a distance from the current position to a terminal landing (step S34), a car speed computation for calculating the speed of the car 3 based on a travel distance of the car 3 (step S35), and a judgment criterion computation for calculating a judgment criterion value for an abnormal speed according to the distance to the terminal landing (e.g., Fig. 2) (step S36) are performed.

[0093] Thereafter, a safety monitoring computation is performed to detect, based on the car speed and the judgment criterion value, an abnormal car speed (step S37). When the safety monitoring computation or a sudden stop computation is performed, a monitor computation for displaying a state of the elevator on a monitor is performed (step S38). Finally, an output computation for outputting an instruction signal required for permitting the traveling of the car 3 or suddenly stopping the car 3 is performed (step S39).

[0094] In such an electronic safety controller 21, the stack area monitoring unit monitors the state of monitored areas. When it is judged that the monitored areas have abnormality, the car 3 is suddenly stopped. Thus, an abnormal program execution due to the stack over of the RAM is prevented. This prevents damage to machines. In other words, a computation by a computer regarding an operation control can be performed more securely and the reliability can be improved.

[0095] Here, an investigation of a cause of a stack over (stack accumulation) is difficult, requiring a long time to recover a failure. The stack over may be caused by abnormality of a microcomputer or a program. However, if the microcomputer or the program has no abnormality, the most probable cause of the abnormality is considered to be that an interrupt computation is not completed within a computation cycle time (computation time out).

[0096] The computation time out is generally not caused but is caused when a computation time is increased temporarily (e.g., when a great number of call buttons are operated to require a long period of time to perform a call scan computation). The computation time out may be caused when repeated modifications or improvements of software gradually increases the computation time.

[0097] When the computation time over is caused, the stack over is caused and a stack area is used improperly and a return address from a timer interrupt may be broken. When the return address is broken, an abnormal program execution may be caused or RAM data may be broken to make it impossible to control the elevator.

[0098] In view of the above, the electronic safety controller 21 of this example can detect the stack over at an earlier stage to prevent the generation of a second failure to improve the reliability.

[0099] The stack area monitoring unit also checks the pattern of processing information for each predetermined computation cycle. Thus, presence or absence of stack over can be always monitored to further improve the reliability.

[0100] Furthermore, when it is judged that there is abnormality in the monitoring area, the car can be suddenly stopped to prevent the abnormality from causing more severe failure.

[0101] In the example, the car 3 is suddenly stopped when the abnormality in the monitoring area is detected. However, a nearest floor stop instruction may be outputted to the operation control unit 12 to stop the car 3 at the nearest floor. As a result, passengers in the car 3 can get out of the car 3 to a landing smoothly.

[0102] Alternatively, when abnormality of a monitored area is detected, a signal for shifting the elevator to a safe state may be outputted and the state of the electronic safety controller 21 at the time may be recorded as a history (history computation). The history is recorded in, for example, an area other than a RAM stack area. This can prevent the generation of stack over and can use the history to investigate the reason of stack over. This can also reduce the time required to recover a failure.

[0103] In this manner, the electronic safety controller 21 in this example includes the RAM having stack areas for storing therein information required for the computation for monitoring the safety of the elevator and the stack area monitoring unit for monitoring a predetermined monitored area in the stack areas. According to the state of the monitored area detected by the stack area monitoring unit, the electronic safety controller 21 controls the operation of the elevator.

[0104] The stack area monitoring unit also checks the state of the monitored area for each predetermined computation cycle. Furthermore, the check of the state of the monitored area is performed as a part of an interrupt arithmetic processing for monitoring the safety of the elevator.

«Detection of abnormality in order of execution of arithmetic processing»

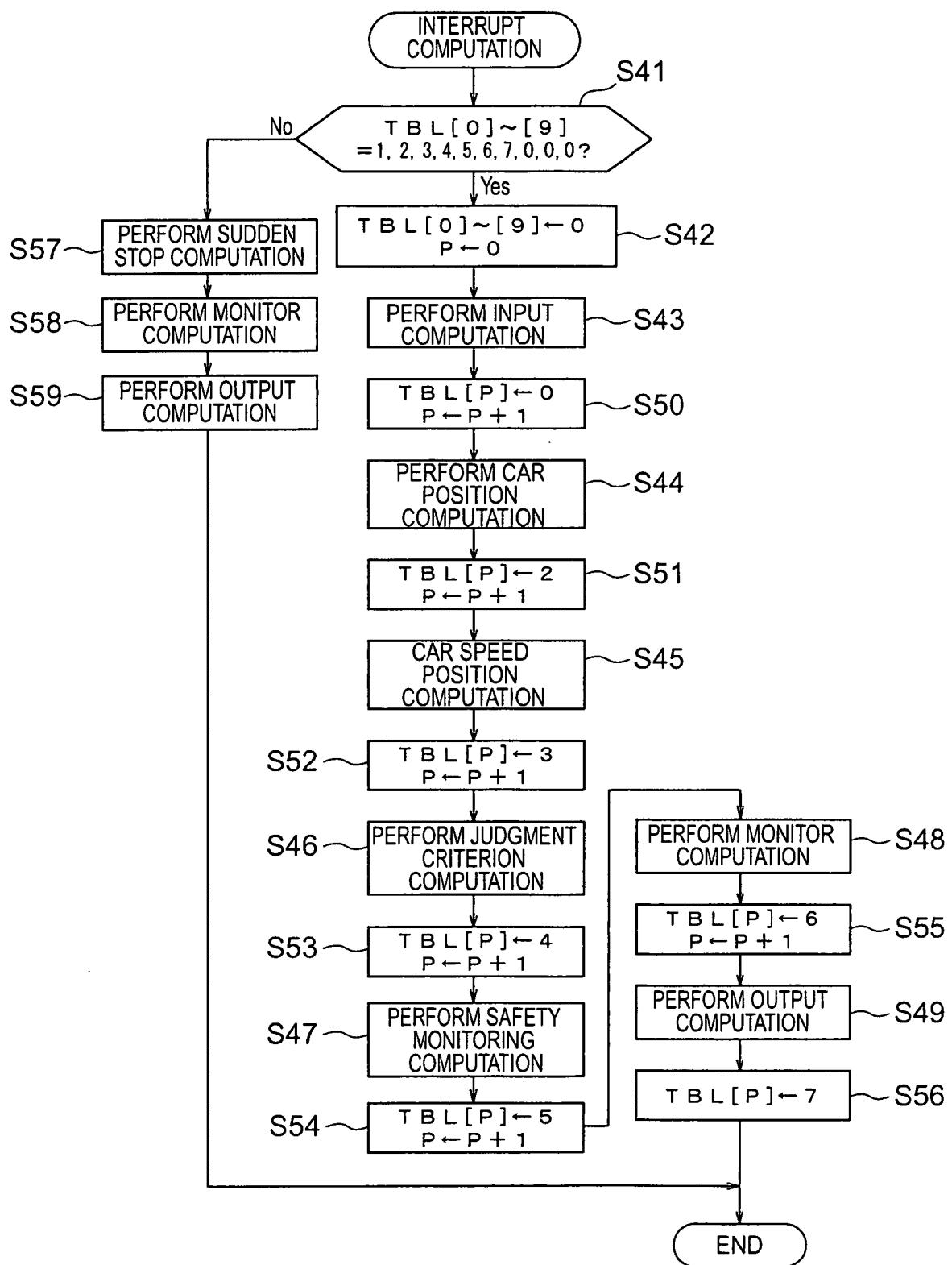

[0105] Next, a method of detecting abnormality in an order of the execution of arithmetic processing by the electronic safety controller 21 will be explained. Fig. 11 is a flowchart of a second example of the flow of an interrupt computation by the electronic safety controller 21 of Fig. 1.

[0106] When the interrupt computation is started, first, a pattern of processing information written in the RAM is checked (step S41). Here, the processing information is a value predetermined for each arithmetic processing task (functional unit) (identification value). The processing information is written in a table set in a predetermined area in the RAM. In this example, identification values of 1 to 7 are allocated to seven arithmetic processing and are written in corresponding TBL[0] to [6]. Values of TBL[7] to [9] are still set to be 0 because there is no corresponding arithmetic processing.

[0107] When the processing information pattern has no abnormality, TBL [0] to [6] and a storage pointer of the table are initialized to be 0 (step S42). Thereafter, an input computation to input a signal required for the computation (step S43), the car position computation to obtain a current position of the car and a distance from the current position to a terminal landing (step S44), the car speed computation to calculate the car speed based on the travel distance of the car (step S45), and the judgment criterion computation for obtaining a judgment criterion value for an abnormal speed according to the distance to the terminal landing (e.g., Fig. 2) (step S46) are performed.

[0108] Thereafter, the safety monitoring computation is performed to detect, based on the car speed and the judgment criterion value, an abnormal car speed (step S47). When the safety monitoring computation or the sudden stop computation is performed, the monitor computation to display a state of the elevator on a monitor is performed (step S48). Finally, the output computation for outputting, according to the result of the safety monitoring computation, an instruction signal required to permit the traveling of the car 3 or to suddenly stop the car 3 is performed (step S49).

[0109] Immediately after the execution of each of the computations, an identification value is written in the corresponding table (steps S50 to S56). In other words, arithmetic processing and the writing of an identification value are performed alternately.

[0110] In other words, immediately after the execution of an initial input computation, 1 is written in TBL[P] and 1 is added to the storage pointer P (step S15). Next, immediately after the execution of the car position computation, 2 is written in TBL[P] and 1 is added to the storage pointer P (step S16). Immediately after the sequential execution of the processing and the execution of the final output computation, 7 is written in TBL[6].

[0111] The pattern of the identification values thus written is checked when the next interrupt computation is started (step S41). In other words, by checking the pattern of the identification values, it is judged whether an order of the execution of the arithmetic processing is correct.

[0112] When abnormality is detected in the order of the execution of the arithmetic processing, the sudden stop computation to suddenly stop the car is performed (step S57). At the same time, when abnormality is detected in the order of the execution of the arithmetic processing, abnormality detection signal is also transmitted to an elevator monitoring room. When the sudden stop computation is performed, the monitor computation is performed (step S58), the output computation for outputting an instruction signal required to suddenly stop the car is performed (step S59), and the interrupt arithmetic processing ends.

[0113] The electronic safety controller 21 can quickly detect abnormality in an order of the execution of arithmetic processing. This allows a computation for the control of an operation by a computer to be performed more securely, thus improving the reliability. The electronic safety controller 21 can also detect abnormality of a program such as a self loop. In other words, the present invention can be applied to both of an operation control apparatus and a safety apparatus.

[0114] Here, an investigation of a cause of abnormality in an order of the execution of arithmetic processing is difficult, requiring a long time to recover a failure. Abnormality in an order of the execution of arithmetic processing may be caused by abnormality of a microcomputer or a program. However, if a microcomputer or a program has no abnormality, the most probable cause of the abnormality in an order of the execution of arithmetic processing is considered to be that an interrupt computation is not completed within a computation cycle time (computation time out).

[0115] The computation time out is generally not caused but is caused when a computation time is increased temporarily (e. g. , when a great number of call buttons are operated to require a long period of time to perform a call scan computation). The computation time out may be caused when repeated modifications or improvements of software gradually increases the computation time.

[0116] In view of the above, the electronic safety controller 21 can detect abnormality in an order of the execution of arithmetic processing at an earlier stage to prevent the generation of a second failure to improve the reliability.

[0117] The electronic safety controller 21 also checks the pattern of processing information for each predetermined computation cycle. Thus, presence or absence of abnormality can be always monitored to further improve the reliability.

[0118] Furthermore, when it is judged that there is abnormality in an order of the execution of arithmetic processing, the car can be suddenly stopped to prevent the abnormality from causing more severe failure.

[0119] In the example, the car 3 is suddenly stopped when it is judged that there is abnormality in an order of the

execution of arithmetic processing. However, a nearest floor stop instruction may be outputted to the operation control unit 12 to stop the car 3 at the nearest floor. As a result, passengers in the car 3 can get out of the car 3 to a landing smoothly.

**[0120]** Alternatively, when abnormality is found in an order of the execution of arithmetic processing, a signal for shifting the elevator to a safe state may be outputted and the state of the electronic safety controller 21 may be recorded as a history (history computation).

**[0121]** Furthermore, in the example, pieces of processing information are allocated to all arithmetic processing. However, pieces of processing information are not always required to be allocated to all arithmetic processing. In other words, pieces of processing information may be allocated only to arithmetic processing for which an order of the execution is desired to be monitored.

**[0122]** In this manner, the electronic safety controller 21 in this example includes a controller body that has a program storage unit for storing a RAM and a program regarding a safety monitoring and a processing unit for executing plural arithmetic processing based on the program. The controller body writes, to the RAM, processing information corresponding to the respective arithmetic processing when arithmetic processing is executed, and monitors, based on the pattern of the processing information written in the RAM, whether an order of the execution of arithmetic processing is normal.

**[0123]** Processing information is a numeric value set for each arithmetic processing. The control apparatus body also checks the pattern of processing information for each predetermined computation cycle. Furthermore, the writing of processing information and the check of the pattern of processing information are executed as a part of an interrupt arithmetic processing to monitor the safety of the elevator.

«Detection of abnormality of power source voltage»

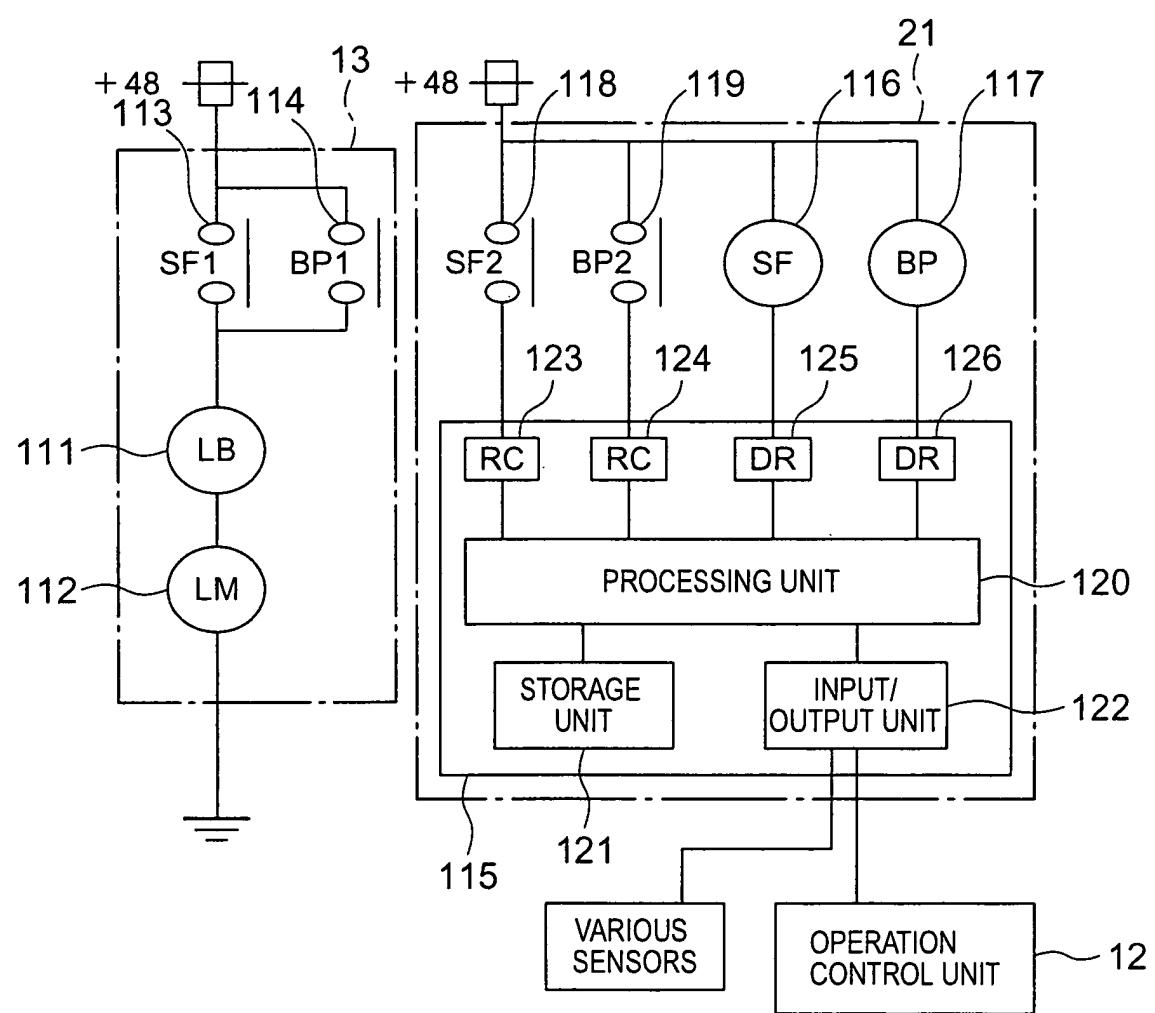

**[0124]** Next, a method of detecting abnormality of a power source voltage in the electronic safety controller 21 will be explained. Fig. 12 is a block diagram of the main part of the electronic safety controller 21 of Fig. 1. In this example, two types of instruction signals are outputted to the elevator control panel 11 to improve the reliability. Thus, a double circuit configuration is used and the first and second CPUs (processing units) 41 and 42 are used.

**[0125]** The first CPU 41 outputs an instruction signal via the first output interface 43 to the elevator control panel 11. The second CPU 42 outputs an instruction signal via the second output interface 44 to the elevator control panel 11. When receiving the instruction signals from the first and second output interfaces 43 and 44, the elevator control panel 11 shifts the elevator to a safe state.

**[0126]** The first and second CPUs 41 and 42 are connected to the dual port RAM 45 to perform data transfer between the CPUs. The first CPU 41 is inputted with a signal from the first sensor. The second CPU 42 is inputted with a signal from the second sensor.

**[0127]** The signals from the first and second sensors are subjected to arithmetic processing by the CPUs 41 and 42 to calculate speed and a position of the car 3. The first and second sensors may be, for example, the speed governor encoder 18.

**[0128]** Data obtained by arithmetic processing by the CPUs 41 and 42 are exchanged between the CPUs 41 and 42 via the dual port RAM 45. Then, the CPUs 41 and 42 compare the respective pieces of data. When the results of the computations show a significant difference or overspeed, an instruction signal is outputted via the output interfaces 43 and 44 to the elevator control panel 11 to shift the elevator to a safe state.

**[0129]** This elevator control apparatus also includes a +5-V power source voltage monitoring circuit 71 and a +3.3-V power source voltage monitoring circuit 72 for monitoring the power source voltages of the CPUs 41 and 42. The power source voltage monitoring circuits 71 and 72 are constituted, for example, by an IC (integrated circuit).

**[0130]** The power source voltage monitoring circuits 71 and 72 monitor whether a stable power source voltage is supplied to the CPUs 41 and 42. When an abnormal power source voltage enough to deviate from a rated voltage of the CPUs 41 and 42 is caused, the CPUs 41 and 42 are forcedly reset based on the information from the power source voltage monitoring circuits 71 and 72 and the car 3 is suddenly stopped by the safety circuit unit 13 designed to have a fail-safe configuration.

**[0131]** The +5-V power source voltage monitoring circuit 71 is inputted with a monitoring voltage from the first monitoring voltage input circuit 73. The +3.3-V power source voltage monitoring circuit 72 is inputted with a monitoring voltage from the second monitoring voltage input circuit 74.

**[0132]** The power source voltage monitoring circuits 71 and 72 and the CPUs 41 and 42 are connected to a voltage monitoring soundness check function circuit 75 (hereinafter simply referred to as check function circuit 75) that monitors the soundness of the power source voltage monitoring circuits 71 and 72. The check function circuit 75 is constituted by a programmable gate IC such as an FPGA (field programmable gate array). The check function circuit 75 can also be realized by, for example, ASIC, CPLD, PLD, or a gate array.

**[0133]** When an abnormal power source voltage is detected, the power source voltage monitoring circuits 71 and 72 output voltage abnormality detection signals 81 and 82 to the check function circuit 75. The check function circuit 75 outputs reset signals 83 and 84 to the CPUs 41 and 42.

[0134] The check function circuit 75 is inputted with the control signals 85 and 86 from the CPUs 41 and 42. The check function circuit 75 outputs monitoring-purpose input voltage forced change signals 87 and 88 to forcedly change voltage input pins of the power source voltage monitoring circuits 71 and 72 to have a low voltage.

[0135] When the monitoring-purpose input voltage forced change signals 87 and 88 are outputted, the monitoring-purpose input voltage forced change circuits 76 and 77 forcedly cause the voltage input pins of the power source voltage monitoring circuits 71 and 72 to have a low voltage.

[0136] The check function circuit 75 is also connected to the first data bus 78 for the first CPU 41 and the second data bus 79 for the second CPU 42.

[0137] A program to calculate the position and speed of the car 3, a program for judging abnormality of the elevator, a program for checking the soundness of the power source voltage monitoring circuits 71 and 72, and the like are stored in a ROM as a storage unit connected to the CPUs 41 and 42.

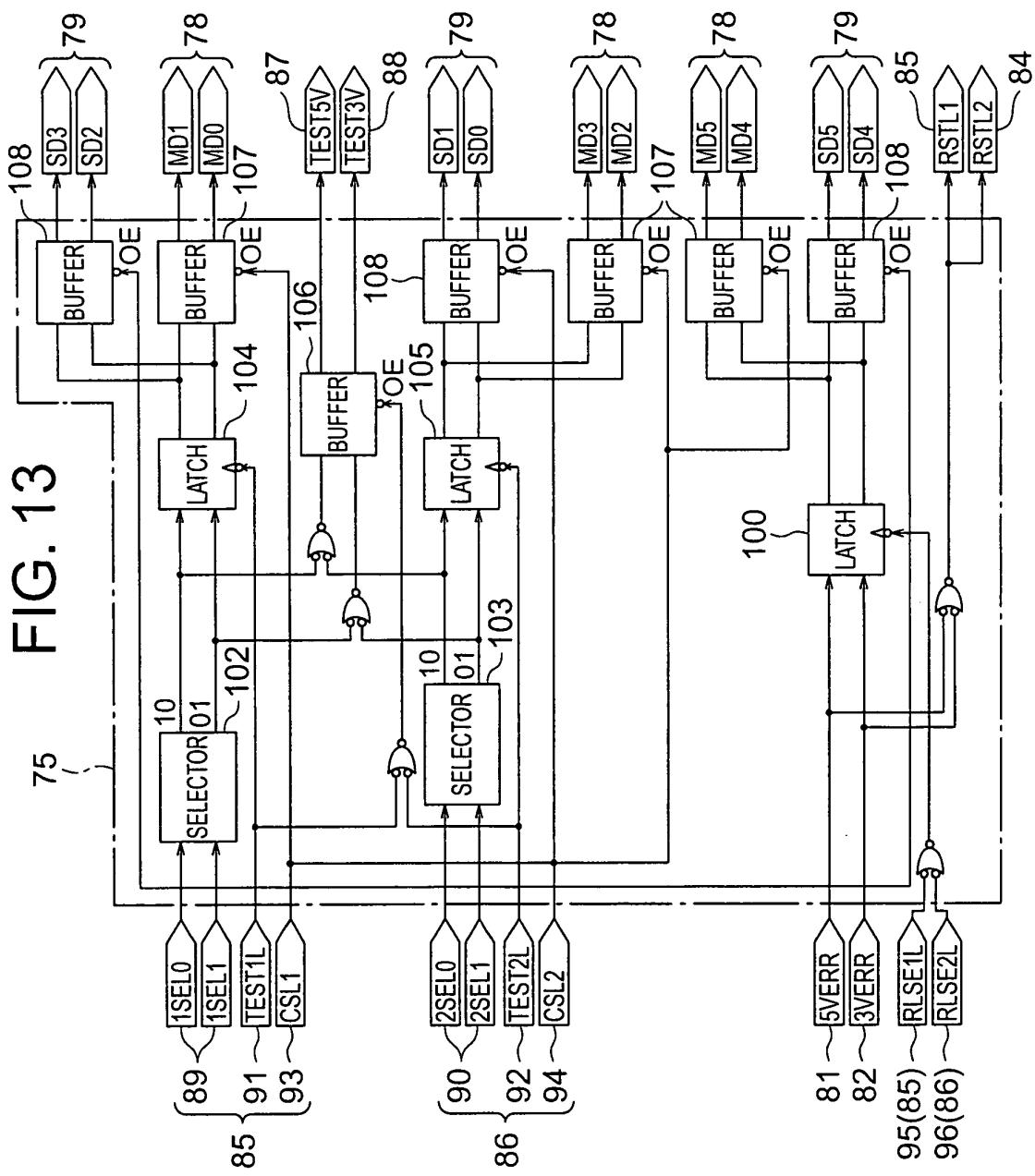

[0138] Fig. 13 is a circuit diagram of an example of a specific structure of the check function circuit 75 of Fig. 12. The control signals 85 and 86 include selection signals 89 and 90, output permission signals 91 and 92, and chip select signals 93 and 94.

[0139] The selection signals 89 and 90 are two bit signals for selecting the power source voltage monitoring circuit 71 or 72 for which the soundness should be checked. The output permission signals 91 and 92 are signals for permitting the output of the monitoring-purpose input voltage forced change signals 87 and 88 from the check function circuit 75 and latching the contents selected by the selection signals 89 and 90. In other words, the output permission signals 91 and 92 also work as a latch trigger signal.

[0140] When abnormality of a power source voltage is detected, a voltage abnormality signal latch circuit 101 in the check function circuit 75 latches the voltage abnormality detection signals 81 and 82. The latch status by the voltage abnormality signal latch circuit 101 is cancelled when latch cancellation signals 95 and 96 as a part of the control signals 85 and 86 are inputted.

[0141] The selection signals 89 and 90 are inputted to the first and second selectors 102 and 103. The first and second selectors 102 and 103 switch, based on the selection signals 89 and 90, the power source voltage monitoring circuits 71 and 72 for which the soundness should be checked. The contents selected by the selectors 102 and 103 are latched by the first and second selection contents latch circuits 104 and 105.

[0142] The former stage of the output of the monitoring-purpose input voltage forced change signals 87 and 88 includes a change signal output buffer 106.

[0143] . The check function circuit 75 includes plural data bus output buffers 107 of the first CPU 41 and plural data bus output buffers 108 of the second CPU 42.

[0144] Here, Fig. 14 is an explanatory diagram of the meanings of data regarding the respective bits of the data buses 78 and 79 when the check function circuit 75 of Fig. 12 is read by the first and second CPUs 41 and 42.

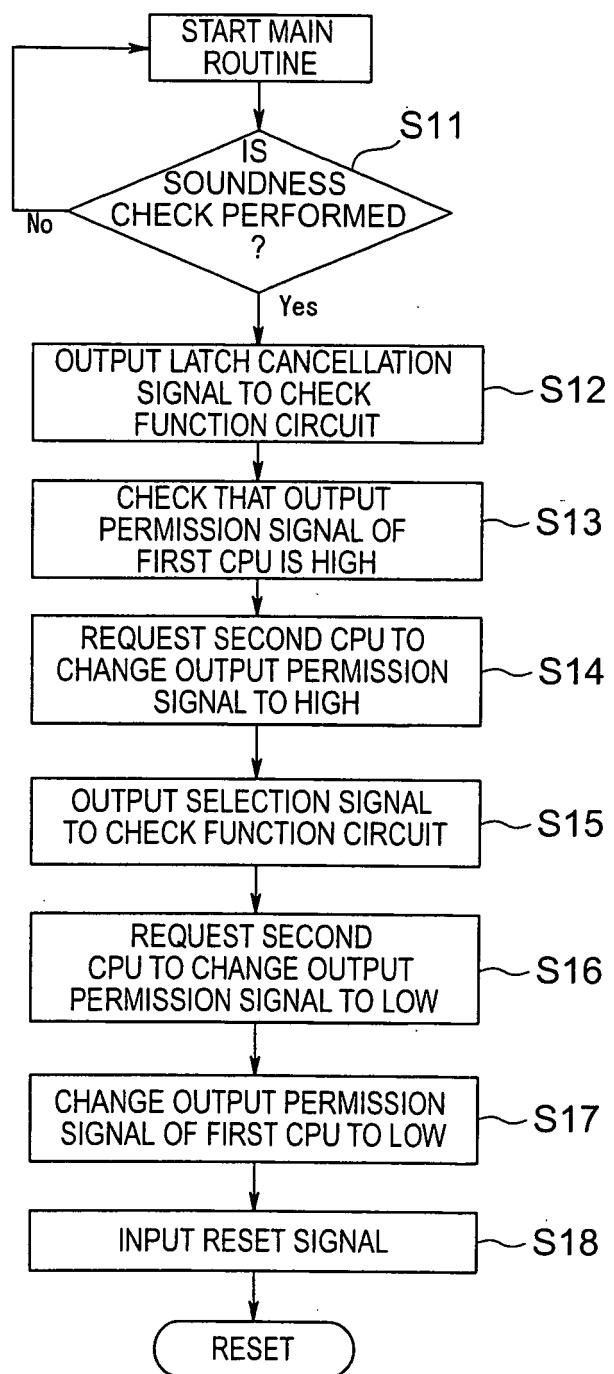

[0145] Next, Fig. 15 is a flowchart of a method of checking the soundness of the monitoring of a power source voltage at the first CPU 41 of Fig. 12. The electronic safety controller 21 executes, for each computation cycle (e.g., 5 msec), an interrupt computation including arithmetic processing to monitor abnormality of the car 3, e.g., overspeed. Then, when executing a main routine of the interrupt computation, the electronic safety controller 21 judges whether the soundness check of the power source voltage monitoring circuits 71 and 72 is performed (step S11).

[0146] The soundness check is performed at a predetermined timing. In other words, the soundness check is performed when the car 3 is stopped for a period of time longer than a predetermined time. In other words, the soundness check is performed, for example, in an off time during which the elevator is used by few users or which the elevator is out of service at night.

[0147] When the soundness check is not performed, the processing returns to the main routine. When the soundness check is performed, first, the latch status of the voltage abnormality detection signals 81 and 82 as an error signal in the check function circuit 75 is cancelled. In other words, the electronic safety controller 21 outputs the latch cancellation signal 95 to the check function circuit 75 (step S12). The latch cancellation signal 95 is inputted to the voltage abnormality signal latch circuit 101 and the latch status of the voltage abnormality detection signals 81 and 82 is cancelled.

[0148] Next, the electronic safety controller 21 checks whether the output permission signal 91 of the first CPU 41 is High (step S13). Then, the electronic safety controller 21 requests the second CPU 42 via the dual port RAM 45 to change the output permission signal 92 to High (step S14).

[0149] Thereafter, the electronic safety controller 21 outputs the select signal 89 for selecting which of the power source voltage monitoring circuits 71 and 72 for the soundness check to the check function circuit 75 and latches the circuit (step S15).

[0150] Next, the electronic safety controller 21 requests the second CPU 42 via the dual port RAM 45 to change the output permission signal 92 to Low (step S6). When it is checked that the output permission signal 92 is Low, the electronic safety controller 21 changes the output permission signal 91 to Low (step S7). As a result, in the check function circuit 75, the select signal 89 is latched by the selection contents latch circuit 104 in synchronization with the fall of the output permission signal 91. Then, the check function circuit 75 outputs the monitoring-purpose input voltage forced

change signal 87 to the power source voltage monitoring circuit 71.

[0151] As a result, the power source voltage monitoring circuit 71 detects an abnormal voltage and the voltage abnormality detection signal 81 is inputted to the check function circuit 75. Then, in the check function circuit 75, the voltage abnormality signal latch circuit 101 latches the voltage abnormality detection signal 81. At the same time, the CPUs 41 and 42 are inputted with the reset signals 83 and 84 from the check function circuit 75 (step S8). Consequently, the CPUs 41 and 42 are reset.

[0152] In this process, only one power source voltage monitoring circuit is always checked through one soundness check operation. Thus, when one soundness check operation is continuously followed by another soundness check of a power source voltage monitoring circuit, one soundness check operation of a power source voltage monitoring circuit is completed before the soundness check of another power source voltage monitoring circuit is performed. Even when one CPU is supplied with plural power sources having plural different voltages and thus plural power source voltage monitoring circuits are provided, the respective power source voltage monitoring circuits are subjected to a soundness check one by one in a sequential manner. The sequential execution of the soundness check of plural power source voltage monitoring circuits can be set in a program (software) in advance.

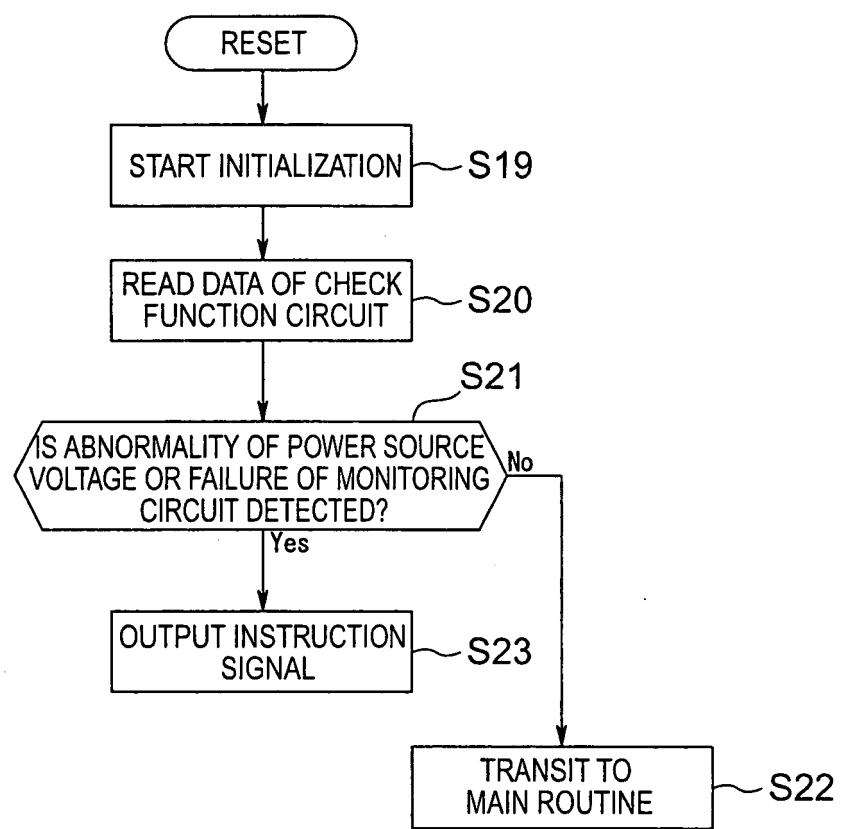

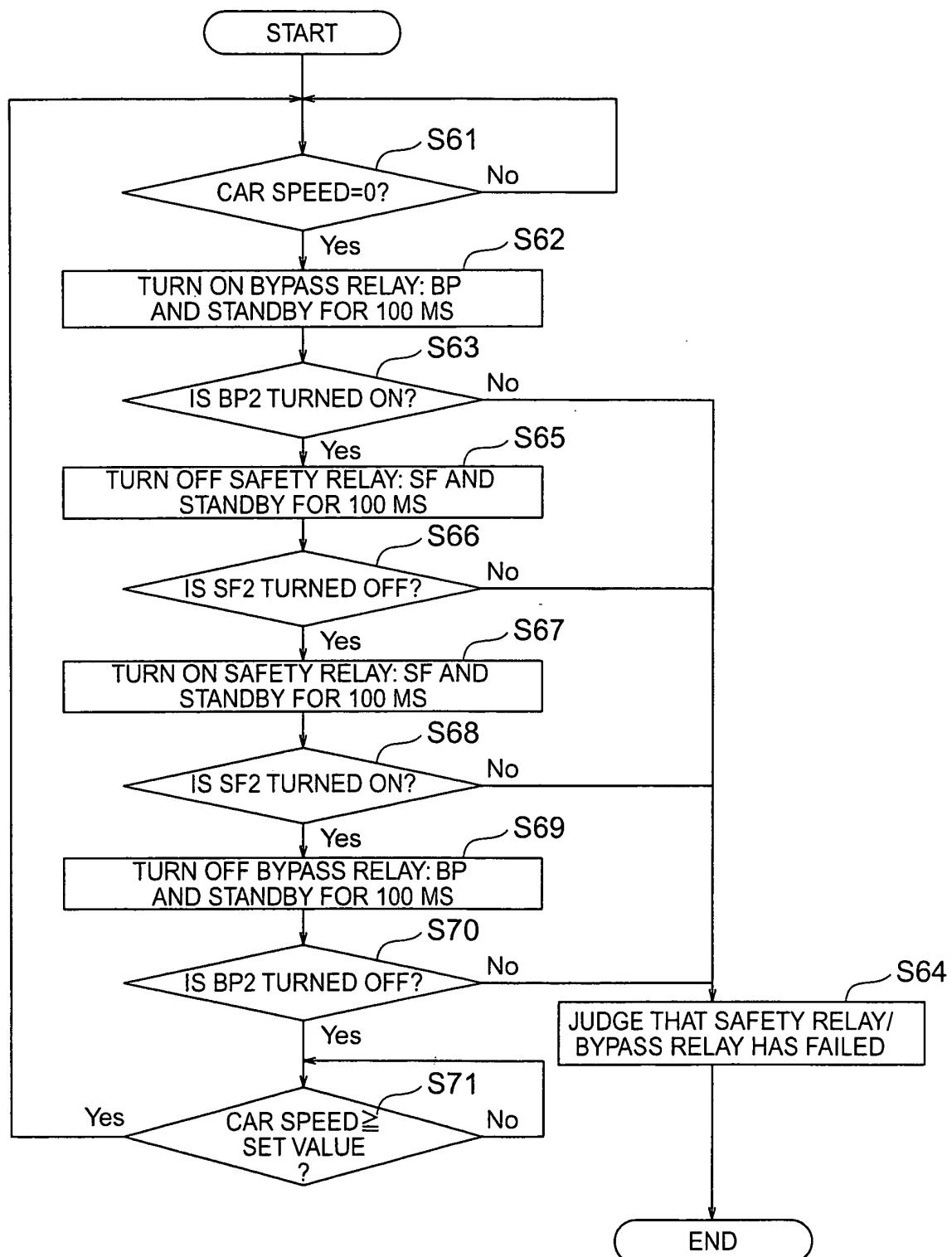

[0153] Fig. 16 is a flowchart of an operation when the CPUs 41 and 42 are reset in the elevator control apparatus of Fig. 12. It goes without saying that the CPUs 41 and 42 may be reset not only due to the soundness check but also due to an actual abnormal power source voltage or other causes.

[0154] When the CPUs 41 and 42 are reset, first, the CPUs 41 and 42 start software initialization processing (step S19). Next, in the initialization processing, the CPUs 41 and 42 read data of the check function circuit 75 (step S20). Then, the CPUs 41 and 42 check the status before the reset based on the latched contents to judge whether an abnormal power source voltage or a failure of the power source voltage monitoring circuits 71 and 72 is present (step S21). In other words, it is judged whether the reset is caused by the soundness check or by an actual abnormal power source voltage.

[0155] When an abnormal voltage is shown in spite of the fact that the outputs of the output permission signals 91 and 92 are not set to be Low, it is judged that an actual abnormal power source voltage is caused. Furthermore, when the data of check function circuit 75 does not show an abnormal voltage in spite of the fact that the outputs of the output permission signals 91 and 92 are set to be Low, it is judged that the power source voltage monitoring circuits 71 and 72 or the check function circuit 75 itself has a failure. When the monitoring-purpose input voltage forced change signals 87 and 88 are outputted in this state, it is judged that the power source voltage monitoring circuits 71 and 72 have a failure. When the monitoring-purpose input voltage forced change signals 87 and 88 are not outputted, it is judged that the check function circuit 75 itself has a failure.

[0156] As a result of reading the data of the check function circuit 75, abnormality or a failure is not detected, the CPUs 41 and 42 permit the transition to the main routine (step S22). However, although this section describes only the reset for the power source voltage, the reset may be triggered by the detection of another failure and the soundness check of another circuit. In this case, all abnormalities and failures are checked and then the transition to the main routine is permitted.

[0157] As a result of reading the data of the check function circuit 75, some abnormality or failure is detected, the CPUs 41 and 42 output an instruction signal to the elevator control panel 11 (step S23) to shift the elevator to a safe state.

[0158] The electronic safety controller 21 can monitor the soundness by monitoring not only an abnormal power source voltage but also a failure of the power source voltage monitoring circuits 71 and 72. Thus, the reliability of the monitoring of a power source voltage can be further improved.

[0159] Although a conventional design has used a double circuit configuration also for each power source voltage monitoring circuit to provide a fail-safe function or to secure the safety, the electronic safety controller 21 does not require the double circuit configuration. Thus, the electronic safety controller 21 can use a simple structure and can suppress an increase in cost. The electronic safety controller 21 can also provide reliability equal to that provided when each power source voltage monitoring circuit has a double circuit configuration.

[0160] Furthermore, the double circuit configuration using the two CPUs 41 and 42 is used and the soundness check operations by the respective CPUs 41 and 42 can be checked via the dual port RAM 45. Thus, failures of the check function circuit 75 and software can also be detected.

[0161] In this manner, the electronic safety controller 21 in this example includes a processing unit for performing a processing regarding a monitoring of the safety of an elevator and a power source voltage monitoring circuit for monitoring a power source voltage supplied to the processing unit. The electronic safety controller 21 further includes a voltage monitoring soundness check function circuit that outputs, according to a control signal from the processing unit, a monitoring-purpose input voltage forced change signal for forcedly changing the power source voltage inputted to the power source voltage monitoring circuit and that is inputted with a voltage abnormality detection signal from the power source voltage monitoring circuit. The voltage monitoring soundness check function circuit retains at least a part of the contents exchanged between the processing unit and the power source voltage monitoring circuit. The processing unit reads the data retained by the voltage monitoring soundness check function circuit to check the soundness of the power

source voltage monitoring circuit.

[0162] The processing unit also includes the first and second CPUs. The first and second CPUs can mutually check the soundness check operations via the dual port RAM.

5 [0163] Furthermore, the electronic safety controller 21 further includes a monitoring-purpose input voltage forced change circuit that forcedly lowers, by inputting a monitoring-purpose input voltage forced change signal, a power source voltage inputted to the power source voltage monitoring circuit.

10 [0164] Furthermore, the power source voltage monitoring circuit includes plural power source voltage monitoring circuits for monitoring different voltages of plural power sources. A control signal from the processing unit to the voltage monitoring soundness check function circuit includes a selection signal for selecting one of plural power source voltage monitoring circuits which is to be subjected to the soundness check.

[0165] The processing unit can subject the respective power source voltage monitoring circuits to the soundness check one by one sequentially.

Furthermore, the voltage monitoring soundness check function circuit can be constituted by a programmable gate IC.

15 «ETS initialization»

[0166] Next, an initialization operation of the ETS circuit unit 22 will be explained. As described above, the ETS circuit unit 22 detects the position of the car 3 independent of the operation control unit 12. Thus, for example, when the elevator is started, the initialization operation of the ETS circuit unit 22 (initialization operation step) is performed. Furthermore, 20 when some difference is caused between the position information of the car 3 in the operation control unit 12 and the position information of the car 3 in the ETS circuit unit 22 due to some reason, the initialization operation of the ETS circuit unit 22 is performed. When the initialization operation is performed, the operation mode of the operation control unit 12 is switched to the initialization operation mode.

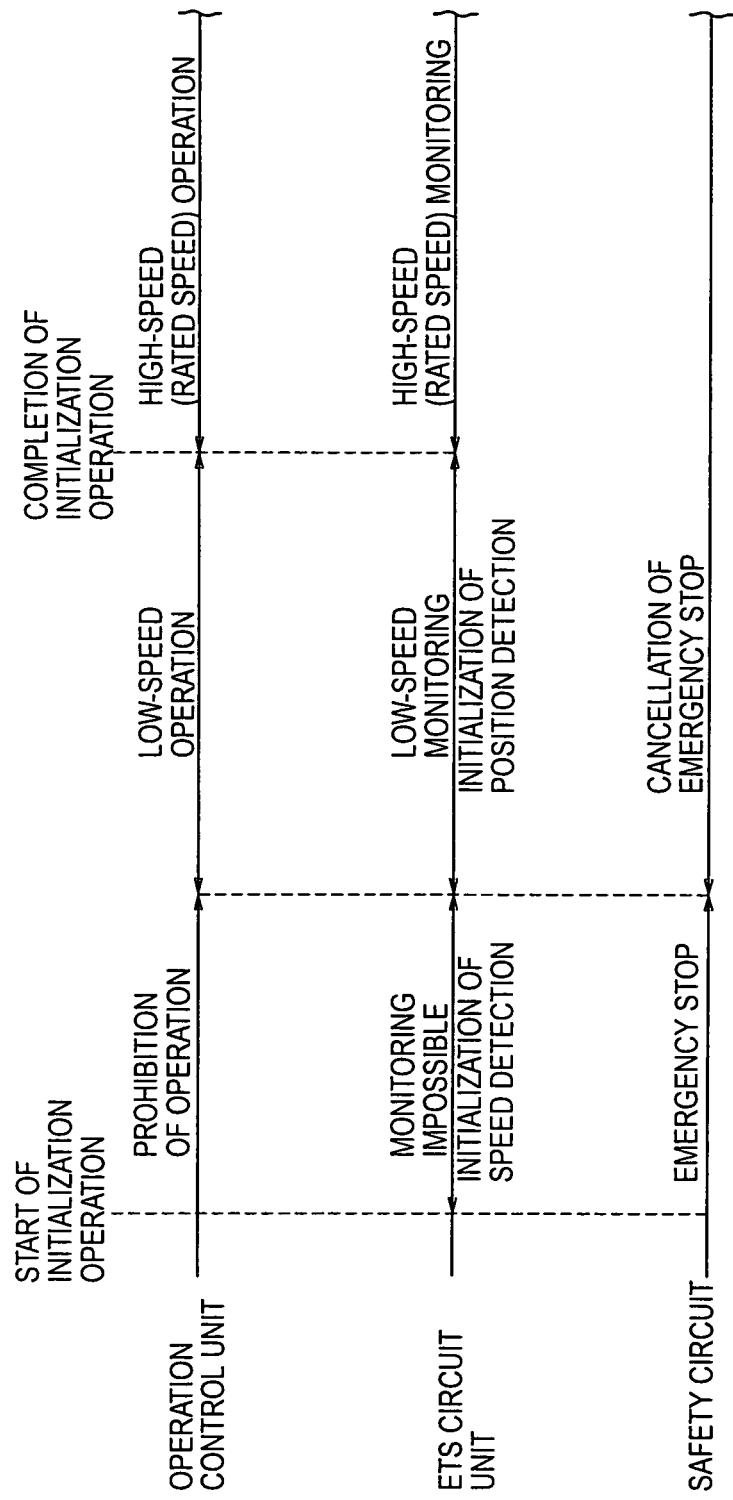

25 [0167] Fig. 17 is an explanatory diagram of a relation between a stage of the initialization operation of the ETS circuit unit 22 of Fig. 1 and the operations of the operation control unit 12 and the safety circuit unit 13. First, through the initialization operation, an initialization of speed detection is performed and then an initialization of position detection is performed.

30 [0168] When an initialization operation is started, the safety circuit unit 13 puts the driving apparatus 7 in an emergency stop state. In other words, a power source of a motor of the driving apparatus 7 is blocked to bring the brake unit 9 of the driving apparatus 7 into a braking state. The ETS circuit unit 22 outputs an operation-prohibition instruction to the operation control unit 12.

35 [0169] Until the initialization of speed detection is completed, the safety circuit unit 13 is put in an emergency stop state and the operation control unit 12 is also in an operation-prohibited state. Thus, the monitoring by the ETS circuit unit 22 is impossible.

[0170] When the initialization of speed detection is completed, the electronic safety controller 21 outputs, to the operation control unit 12, a permission signal to permit a low-speed operation. The emergency stop state of the safety circuit unit 13 can also be cancelled. In this state, the ETS circuit unit 22 performs an operation for initializing position detection.

40 [0171] In the operation to initialize position detection, the car 3 is caused to travel from the lower part to the upper part of the hoistway 1 at speed equal to or lower than the allowable collision speeds of the buffers 27 and 28. Then, the ETS circuit unit 22 sets the relation between a signal from the speed governor encoder 18 and the position of the car 3 in the hoistway 1.

45 [0172] When the initialization operation is completed, the electronic safety controller 21 outputs, to the operation control unit 12, a permission signal for permitting a high-speed operation (rated speed operation). The ETS circuit unit 22 makes it possible to perform a high-speed monitoring.

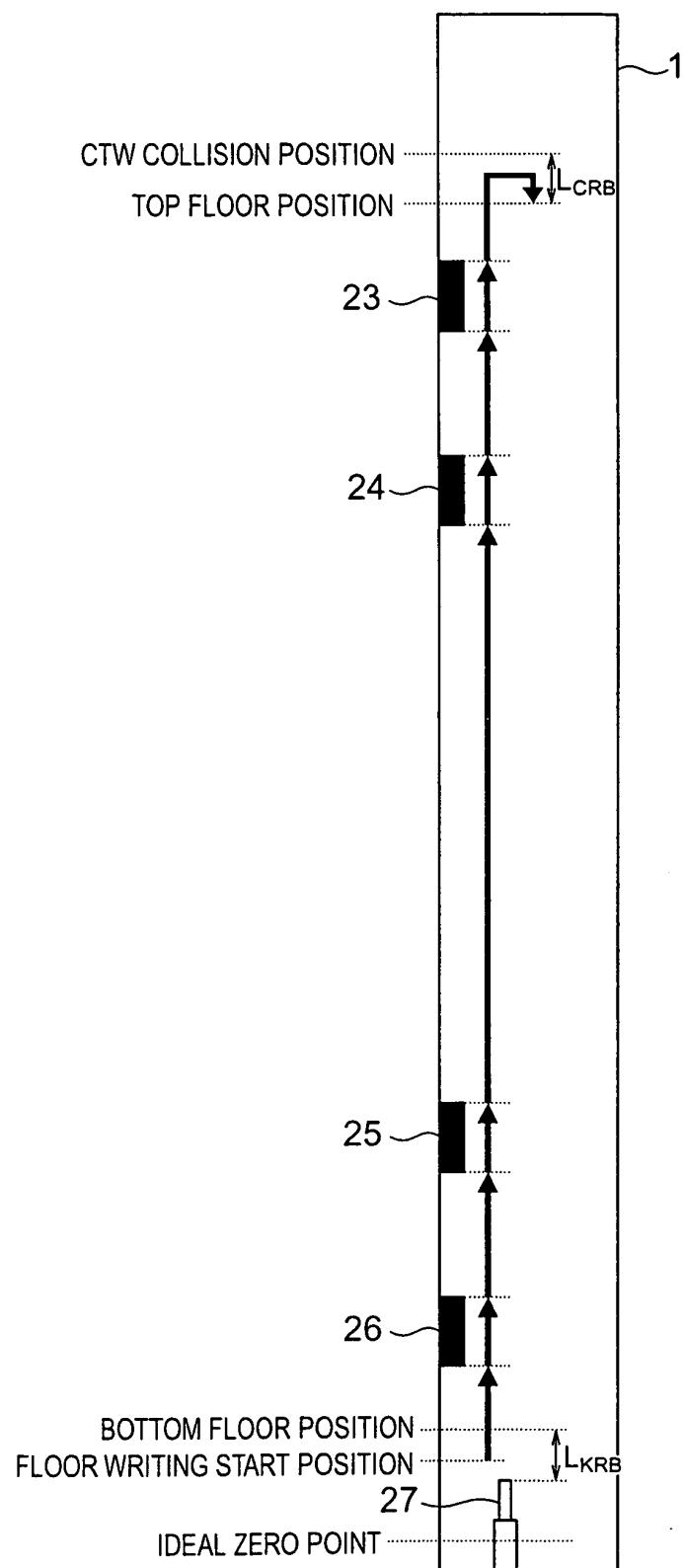

50 [0173] Next, Fig. 18 is an explanatory diagram of the movement of the car 3 in the initialization operation mode of the elevator apparatus of Fig. 1. In the initialization operation mode, the completion of the initialization of speed detection is followed by the movement of the car 3 to a floor writing start position in the lower part of the hoistway 1. The floor writing start position is a position where the car 3 is lower than a bottom floor position  $P_{BOT}$  and is higher than the car buffer 27. When the car 3 is located at the floor writing start position, the car 3 (specifically, operation plates of reference sensors 23 to 26 provided at the car 3) is in a position lower than that of the fourth reference sensor 26.

55 [0174] The hoistway 1 includes plural end point switches (not shown) for detecting the position of the bottom floor or the top floor using the operation control unit 12. The movement of the car 3 to the floor writing start position is controlled by the operation control unit 12.

[0175] Thereafter, while causing the car 3 to ascend from the floor writing start position, a temporary current position  $P_{current}$  of the car 3 corresponding to the signal from the speed governor encoder 18 is obtained. In other words, the floor writing start position is assumed as 0.

$$P_{\text{current temp}} \leftarrow 0$$

5 Thereafter, the temporary current position is updated with every computation cycle (e.g., every 100 msec).

**[0176]** Here, the ETS circuit unit 22 includes an updown counter for counting encoder pulses of the speed governor encoder 18. Assuming that a travel distance in one computation cycle of the updown counter is GC1, the temporary current position  $P_{\text{current temp}}$  at the Nth computation cycle is calculated by the following formula.

10

$$P_{\text{current temp } N} \leftarrow P_{\text{current temp } N-1} + GC1$$

15 In other words, the temporary current position and the travel distance in one computation cycle are calculated as the number of encoder pulses.

**[0177]** In this manner, the temporary current position is updated according to the ascent of the car 3. Positions at which the operation plates enter the reference sensors 23 to 26 and positions at which the operation plates exit from the reference sensors 23 to 26 are written in a table of a storage unit (memory) provided in the ETS circuit unit 22.

20 **[0178]** When an enter of an operation plate to the fourth reference sensor 26 is detected with, for example, the Nth computation cycle, the entering position  $P_{\text{tmp ETS}}^{\text{enter}}$  is calculated by the following formula.

$$P_{\text{tmp ETS}}^{\text{enter}} \leftarrow P_{\text{current temp } N-1} + GC1 - GC2$$

25

The term "GC2" represents a travel distance of an updown counter after the enter to the fourth reference sensor 26. The entering positions to other reference sensors 23, 24, and 25 are similarly written in the table.

**[0179]** When the exit from the reference sensor 26 is detected at the Nth computation cycle, the exit position  $P_{\text{tmp ETS}}^{\text{exit}}$  is calculated by the following formula.

30

$$P_{\text{tmp ETS}}^{\text{exit}} \leftarrow P_{\text{current temp } N-1} + GC1 - GC3$$

35 The term "GC3" represents the travel distance of the updown counter after the exit from the fourth reference sensor 26. The exit positions from other reference sensors 23, 24, and 25 are similarly written in the table.