## (11) **EP 1 798 716 A1**

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

20.06.2007 Bulletin 2007/25

(51) Int Cl.:

G09G 3/34 (2006.01)

G09G 3/32 (2006.01)

(21) Application number: 05112302.4

(22) Date of filing: 16.12.2005

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI SK TR

Designated Extension States:

AL BA HR MK YU

(71) Applicant: Toppoly Optoelectronics Corp. Chu-Nan 350, Miao-Li County (TW) (72) Inventors:

- Peng, Du-Zen 302, Jhubei City Hsinchu County (TW)

- Chang, Shih-Chang 310, Jhudong Township Hsinchu County (TW)

- (74) Representative: Patentanwälte Kewitz & Kollegen Corneliusstrasse 18 60325 Frankfurt am Main (DE)

## (54) Systems for controlling brightness of displayed images

(57) Systems for controlling brightness of displayed images of a display panel are provided. A representative system incorporates a control unit that is operative to adjust brightness of a corresponding display panel based upon at least one of: detected brightness of ambient light and brightness of light emitting elements of the display panel. The system comprises a control unit (324) for sampling a reference voltage (414) during a first period and

storing it on a capacitor (362). During a second period a reference signal (Sp), e.g. a triangular waveform, is applied by the control unit to the capacitor and, after a period of time dependent on the sampled voltage, causes the output of an inverter circuit (34) to switch states (STV). The duty ratio of the signal output by the inverter is then used to control the brightness of a panel comprising LEDs as pixels or string lamps, or the backlight of a liquid crystal display.

EP 1 798 716 A1

# BACKGROUND

[0001] The disclosure relates to image display.

**[0002]** Display panels of mobile electronic systems are typically user adjustable to compensate for varying levels of environmental brightness. For example, a display panel should be able to generate high brightness to display an image in a bright environment. Conversely, the display of a dark image in a darker environment requires less display panel brightness.

1

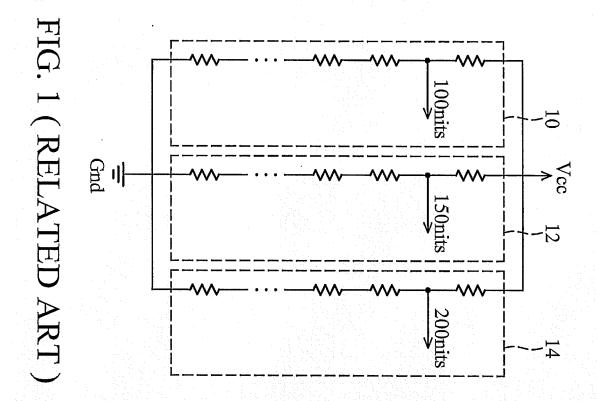

[0003] A conventional method controls brightness of light emitted from a display panel according to voltage generated by a voltage divider. Fig. 1 is a schematic diagram of a conventional voltage divider. A voltage between two resistors can be adjusted according to the resistance of two resistors. A first maximum gray level provided by voltage divider 10 is 100 nits, a second maximum gray level provided by voltage divider 12 is 150nits, and a third maximum gray level provided by voltage divider 14 is 200nits. Therefore, the brightness of light emitted from the display panel can be adjusted by providing different maximum gray levels. Unfortunately, since such a conventional method utilizes numerous voltage dividers to generate multiple voltages for adjusting the brightness of light emitted from the display panel, the cost and size of the display panel can be high.

#### **SUMMARY**

[0004] Systems for controlling brightness of displayed images are provided. In this regard, a representative embodiment of such a system comprises a signal generator that comprises a control unit, a first processing unit, and a storage unit. The control unit outputs a reference voltage according to the brightness of light emitted from the lamp during a first period and outputs a reference signal during a second period. The first processing unit comprises a first input terminal and a first output terminal. Voltage of the first input terminal is equal to that of the first output terminal during the first period. A logic level of the first output terminal is inverse to a logic level of the first input terminal. The storage unit stores a response voltage according to the reference voltage and the voltage of the first input terminal during the first period and controls the logic level of the first input terminal according to the reference voltage and the response voltage during the second period.

**[0005]** Another embodiment of such a system comprises a control unit that is operative to adjust brightness of a corresponding display panel based upon at least one of: detected brightness of ambient light and brightness of light emitting elements of the display panel.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

[0006] The invention can be more fully understood by

reading the subsequent detailed description and examples with reference made to the accompanying drawings, wherein:

- Fig. 1 is a schematic diagram of a conventional voltage divider;

- Fig. 2a is a schematic diagram of an embodiment of a system for controlling brightness of displayed images:

- Fig. 2b is a schematic diagram of the embodiment of Fig. 2a, showing the signal generator in greater detail:

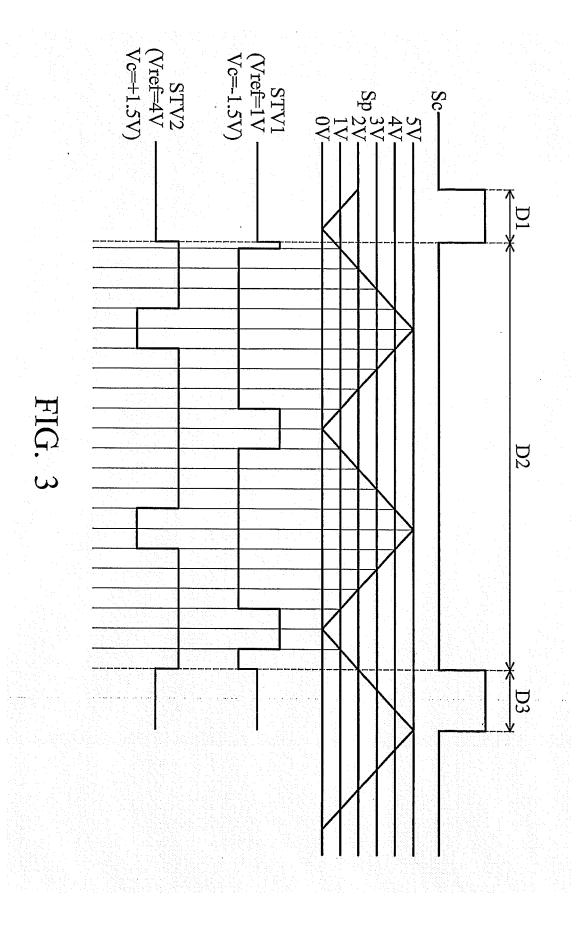

- Fig. 3 is a timing diagram of the preset signal STV shown in Fig. 2b;

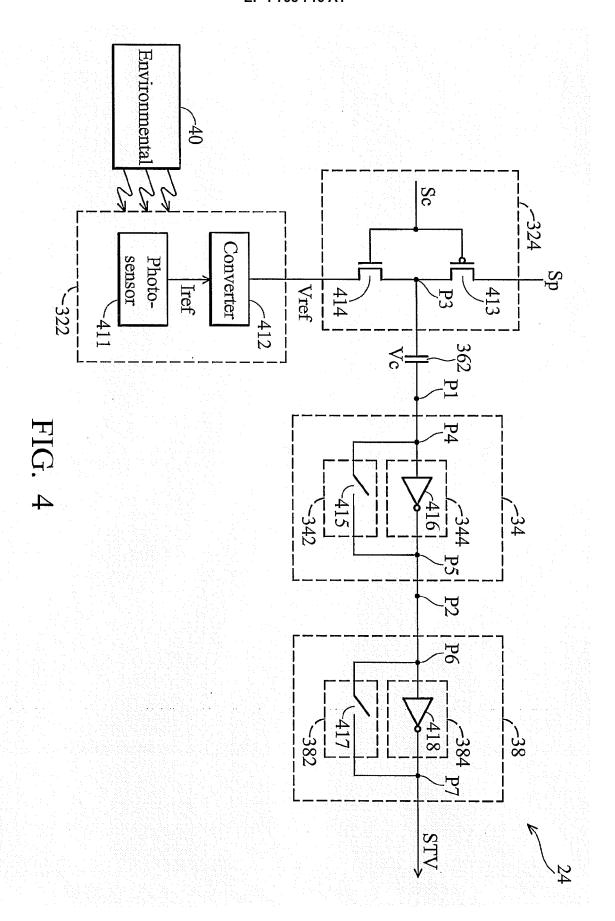

- Fig. 4 is a schematic diagram of another exemplary embodiment of a system for controlling brightness of displayed images;

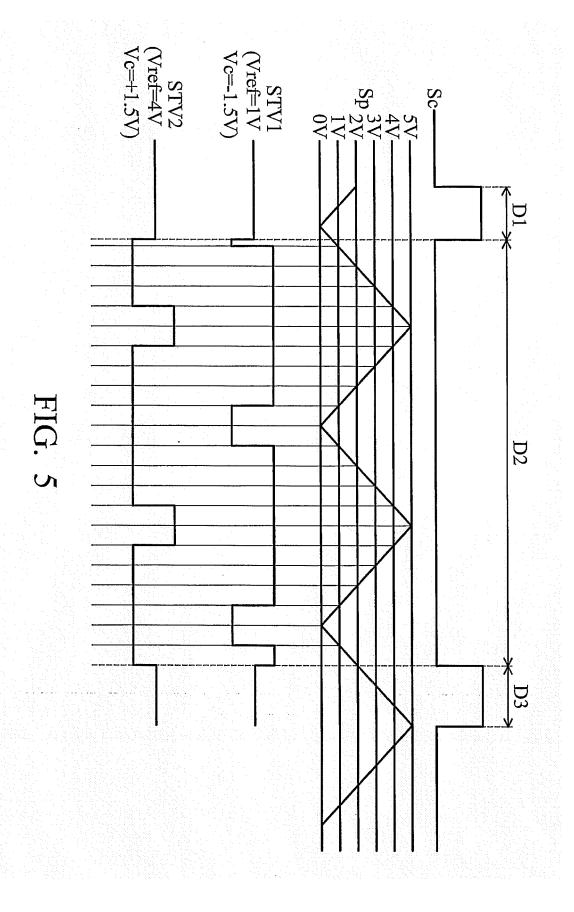

- Fig. 5 is a timing diagram of the preset signal STV shown in Fig. 2c;

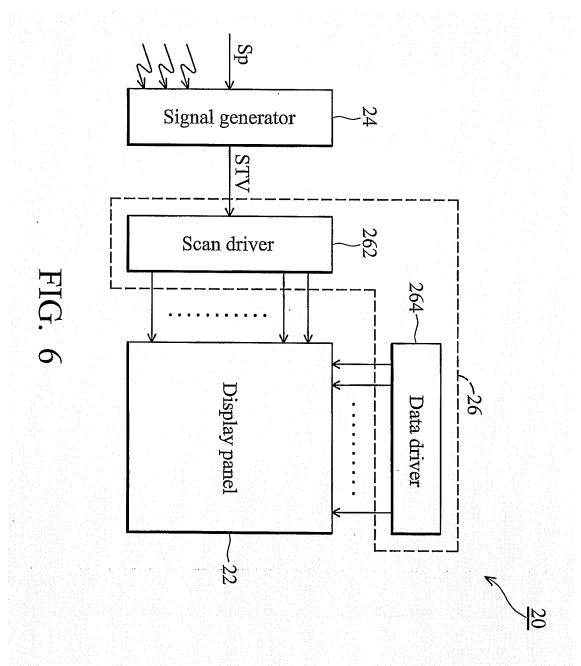

- Fig. 6 is a schematic diagram of another embodiment of a system for controlling brightness of displayed images:

- Fig. 7 is a schematic diagram of an embodiment of a pixel; and

- Fig. 8 is a schematic diagram of another embodiment of a pixel.

#### **DETAILED DESCRIPTION**

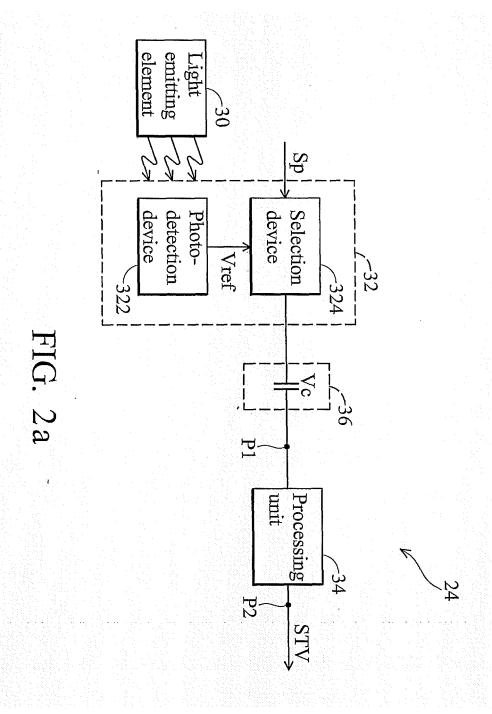

[0007] Systems for controlling brightness of displayed images are provided. In this regard, an exemplary embodiment of such a system is depicted schematically in Fig. 2a. As shown in Fig. 2a, the system incorporates a signal generator 24. Signal generator 24 comprises a control unit 32, a first processing unit 34, and a storage unit 36 connected therebetween.

[0008] During a first period, control unit 32 outputs a reference voltage Vref according to brightness emitted from light-emitting element 30. During a second period, control unit 32 outputs a reference signal Sp. Control unit 32 comprises a photo-detection device 322 and selection device 324. Photo-detection device 322 provides reference voltage Vref according to the brightness of light emitted from lamp 30. Selection device 324 outputs reference voltage Vref or reference signal Sp according to a control signal Sc (not shown). In this embodiment, the logic level of control signal Sc is high during the first period and that of control signal Sc is low during the second period. Threrfore, selection device 324 outputs reference voltage Vref during the first period and otuputs reference signal Sp during the second period. In this embodiment, reference signal Sp is a triangular signal provided from external.

**[0009]** The first processing unit 34 comprises an input terminal P1 and an output terminal P2. A voltage of the input terminal P1 is equal to that of the output terminal P2 during the first period. Additionally, a logic level of the output terminal P2 is inverse to a logic level of the input

40

terminal P1 during the second period.

**[0010]** Storage unit 36 stores a response voltage Vc according to reference voltage Vref and the voltage of the input terminal P1 during the first period. Additionally, storage unit 36 controls the logic level of the input terminal P1 according to reference voltage Vref and the response voltage Vc during the second period. The output terminal P2 provides preset signal STV according the logic level of the input terminal P1 during the second period. In this embodiment, storage unit 36 is a capacitor.

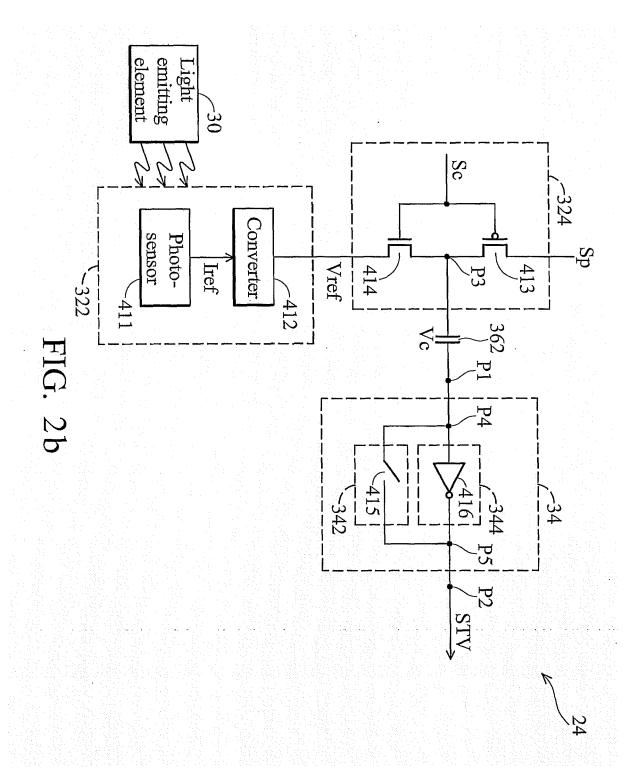

[0011] Fig. 2b is a schematic diagram of the embodiment of the system for controlling brightness of displayed images of Fig. 2a showing the signal generator 24 in greater detail. In this regard, photo-detection device 322 comprises a photo-sensor 411 and a converter 412 and provides reference voltage Vref according to brightness of light emitted from light-emitting element 30. Photo-sensor 411 detects the brightness of light emitted from lightemitting element 30 and provides a corresponding current Iref. Converter 412 converts the current Iref to reference voltage Vref. Since a value of the current Iref is small, a current mirror unit (not shown) is utilized to amplify the current Iref. Converter 412 receives the amplified current Iref. Additionally, an amplifier (not shown) can be utilized for amplifying reference voltage Vref. Selection device 324 comprises transistors 413 and 414. Transistor 413 is a P-type transistor and transistor 414 is an N-type transistor. A source of transistor 413 receives reference signal Sp, a gate thereof receives a control signal Sc, and a drain thereof is coupled to a drain of transistor 414. A gate of transistor 414 receives the control signal Sc and a source thereof receives reference voltage Vref.

**[0012]** As the control signal Sc is at high logic level during the first period, transistor 414 is turned on. Therefore, voltage of a node P3 is approximately equal to reference voltage Vref. As the control signal Sc is at low logic level during the second period, transistor 413 is turned on. Therefore, voltage of a node P3 is approximately equal to voltage of reference signal Sp.

**[0013]** The first processing unit 34 comprises a switching device 342 and an inverting device 344 connected in parallel with switching device 342. During the first period, switching device 342 is turned on such that a voltage of an input terminal P4 of inverting device 344 is equal to that of an output terminal P5 of inverting device 344. During the second period, switching device 342 is turned off such that a logic level of the output terminal P5 is the inverse of the input terminal P4. In some embodiments, inverting device 344 can be an inverter 416 and switching device 342 can be a switch 415.

**[0014]** To increase a sensitivity of inverting device 344, inverting device 344 can include inverters connected in series, with a switch being coupled between an input terminal of a first of the inverters and an output terminal of a last inverters. Additionally, inverting device 344 can comprise a plurality of inverters connected in series, with a plurality of switches, each connected in parallel with one of the inverters. Since inverting device 344 has an

inverse function during the second period, the number of inverters should be odd.

[0015] In the embodiment of Fig. 2b, photo-sensor 411 detects brightness of light emitted from light-emitting elements of a display panel. Since the light-emitting elements age, the brightness of light emitted from the light-emitting elements typically will decay. Thus, signal generator 24 can compensate for the decaying brightness due to aging of light-emitting elements.

**[0016]** The operating principle of the system shown in Fig. 2b is described in the following. In this regard, Fig. 3 is a timing diagram of the preset signal STV of Fig. 2b. Assuming the high voltage of inverter 416 is equal to 5V and low voltage thereof is equal to 0V, then during a first period D1, switch 415 is turned on such that voltages of nodes P4 and P5 are equal to 2.5V. Therefore, preset signal STV1 approximately equals 2.5V.

**[0017]** During first period D1, control signal Sc is at a high logic level such that transistor 414 is turned on. Therefore, voltage of node P3 equals reference voltage Vref. If the brightness of light emitted from light-emitting elements of a display panel changes from bright to dark, the reference voltage Vref output from photo-detection device 322 is equal to 1V. When voltage  $V_{P4}$  of node P4 equals 2.5V and voltage  $V_{P3}$  of node P3 equals 1V, the voltage Vc of capacitor 362 equals -1.5V.

**[0018]** During the second period, control signal Sc is at a low logic level such that transistor 413 is turned on. Therefore, the voltage  $V_{P3}$  is equal to reference signal Sp. Reference signal Sp is a triangular signal in this embodiment having a maximum voltage equal to 5V and a minimum voltage equal to 0V. Since voltage Vc equals to - 1.5V, when voltage  $V_{P3}$  is less than 1V, preset signal STV1 is at a high logic level, and when voltage  $V_{P3}$  is more than 1V, preset signal STV1 is at a low logic level. **[0019]** During the third period D3, switch 415 is turned on such that voltages of nodes P4 and P5 are equal to 2.5V. Therefore, preset signal STV1 is equal to 2.5V and voltage Vc will be changed according to reference voltage Vref.

**[0020]** If the brightness of light emitted from light-emitting elements of a display panel changes from dark to bright, the reference voltage Vref output from photo-detection device 322 is equal to 4V. When voltage  $V_{P4}$  of node P4 equals 2.5V and voltage  $V_{P3}$  of node P3 equals to 4V, voltage Vc of capacitor 362 equals 1.5V.

**[0021]** During the second period, control signal Sc is at a low logic level such that transistor 413 is turned on. Therefore, the voltage  $V_{P3}$  equals reference signal Sp. Since voltage Vc equals 1.5V when voltage  $V_{P3}$  is less than 4V, preset signal STV2 is at a high logic level, and when voltage  $V_{P3}$  is more than 4V, preset signal STV2 is at a low logic level.

**[0022]** During the third period D3, switch 415 is turned on such that voltages of nodes P4 and P5 are equal to 2.5V. Therefore, preset signal STV2 is equal to 2.5V and voltage Vc will be changed according to reference voltage Vref.

15

20

40

**[0023]** As shown in Fig. 3, when the brightness emitted from light-emitting elements of a display panel changes, reference voltage Vref output from photo-detection device 322 changes to adjust a duty cycle of preset signal STV.

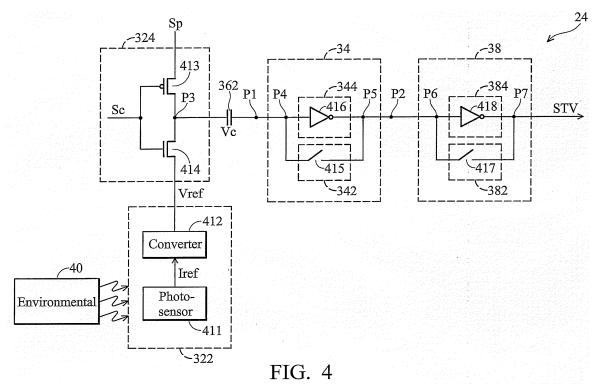

[0024] Fig. 4 is a schematic diagram of another exemplary embodiment of a system for controlling brightness of displayed images. Fig. 4 is similar to the embodiment of Fig. 2b except that a second processing unit 38 is coupled to first processing unit 34. In this embodiment, the first processing unit 38 comprises a switching device 382 and an inverting device 384 connected in parallel with switching device 382. During the first period, switching device 382 is turned on such that a voltage of an input terminal P6 of inverting device 384 is equal to that of an output terminal P7 of inverting device 384. During the second period, switching device 382 is turned off such that a logic level of the output terminal P7 is the inverse of the input terminal P6. In some embodiments, inverting device 384 can be an inverter 418 and switching device 382 can be a switch 417.

**[0025]** To increase a sensitivity of inverting device 384, inverting device 384 can include inverters connected in series, with a switch coupled between an input terminal of a first of the inverters and an output terminal of a last of the inverters.

Additionally, inverting device 384 can comprise a plurality of inverters connected in series, and a plurality switches, each connected in parallel to one of the inverters. Since inverting device 384 has an inverse function during the second period, the number of inverters should be odd. The number of inverters of inverting devices 344 and 384 preferably is even.

**[0026]** In the embodiment of Fig. 4, photo-sensor 411 detects environmental brightness (ambient light). The brightness perceived by a viewer of the display panel that is lower if the environmental brightness is high. Therefore, the brightness of light emitted from the light-emitting elements of a display panel is directly proportional to environmental brightness.

**[0027]** Fig. 5 is a timing diagram of the preset signal STV of Fig. 4. Since signal generator 24 shown in Fig. 4 detects environmental brightness, preset signals STV1 and STV2 are generated accordingly. Preset signal STV1 is generated when environmental brightness is high. Preset signal STV2 is generated when environmental brightness is low

**[0028]** Additionally, since the signal generator shown in Fig. 4 comprises second processing unit, the preset signals STV 1 and STV2 shown in Fig. 5 are inverse to the preset signals STV1 and STV2 shown in Fig. 3.

**[0029]** Fig. 6 is a schematic diagram of another embodiment of a system for controlling brightness of displayed images. In this embodiment, system 20 comprises a display panel 22, a signal generator 24, and a driving device 26. Display panel 22 comprises a plurality of lightemitting elements (not shown). Generally display panel 22 is a liquid crystal display panel although in other em-

bodiments, the panel could be an electroluminescent display panel for example. If display panel 22 is a liquid crystal display panel, the light-emitting elements of display panel 22 are string lamps. If display panel 22 is an electroluminescent display panel, the light-emitting elements of display panel 22 are electroluminescent elements.

**[0030]** Signal generator 24 generates a preset signal STV according to brightness of light such as environmental light or light from a light-emitting element. Driving device 26 comprises a scan driver 262 and a data driver 264. Driving device 26 adjusts brightness of light emitted from the light-emitting elements according to preset signal STV.

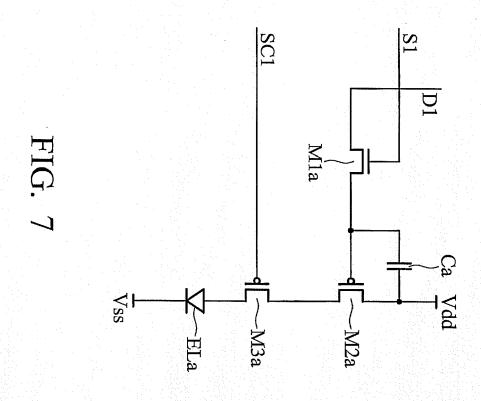

[0031] If display panel 22 is an electroluminescent display panel, display panel 22 comprises a plurality of pixels. Each pixel comprises an electroluminescent element. In this regard, Fig. 7 is a schematic diagram of an embodiment of a pixel. For clarity, only one pixel is shown.

[0032] When scan driver 262 asserts scan signal S1, a transistor M1a is turned on such that a capacitor Ca is charged according to a data signal D1 provided from data driver 264. As the voltage stored in capacitor Ca is sufficient to turn on a transistor M2a, high voltage Vdd can be output to a transistor M3a.

[0033] If driving signal SC1 provided by scan driver 262 is at a high logic level, transistor M3a is turned off such that electroluminescent element ELa does not emit light. If driving signal SC1 is at low logic level, transistor M3a is turned on such that electroluminescent element ELa emits light.

[0034] When the turn-on time of the transistor M3a is longer, luminiferous time of electroluminescent element ELa is longer such that brightness emitted from display panel 22 is brighter. When the turn-on time of transistor M3a is shorter, luminiferous time of electroluminescent element ELa is shorter such that brightness emitted from display panel 22 is less. Therefore, a duty cycle of preset signal STV is utilized to control the turn-on time of transistor M3a for controlling the brightness emitted from display panel 22.

[0035] For example, referring again to Fig. 3, preset signal STV1 is generated while brightness emitted from light-emitting elements of display panel 22 is changed from bright to dark. Scan driver 262 provides driving signal SC1 according to preset signal STV1 shown in Fig. 3. In this embodiment, driving signal SC1 is equal to preset signal STV1. When the gate of transistor M3a receives driving signal SC1, turn-on time of electroluminescent element ELa is longer than the turn-off time of electroluminescent element ELa. Thus, brightness emitted from display panel 22 is high. Preset signal STV2 is generated while brightness of light emitted from the lightemitting elements of display panel 22 is changed from dark to bright. Scan driver 262 provides driving signal SC1 according to preset signal STV2 shown in Fig. 3. In this embodiment, driving signal SC 1 is equal to preset

5

15

20

35

signal STV2. When the gate of transistor M3a receives driving signal SC1, turn-off time of electroluminescent element ELa is longer than turn-on time of electroluminescent element ELa. Therefore, brightness emitted from display panel 22 is low.

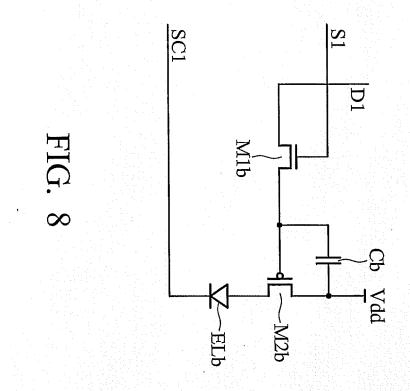

**[0036]** Fig. 8 is a schematic diagram of another embodiment of a pixel. As transistor M1b is turned on, capacitor Cb can be charged. When voltage stored in capacitor Cb is sufficient to turn on transistor M2b, an anode of electroluminescent element ELb receives high voltage Vdd

**[0037]** When driving signal SC1 is at a low logic level, electroluminescent element ELb emits light. When driving signal SC1 is at a high logic level, electroluminescent element ELb does not emit light.

[0038] For example, reference with Fig. 5 and Fig. 8, preset signal STV1 is generated as environmental brightness is low. Scan driver 262 provides driving signal SC1 according to preset signal STV1 shown in Fig. 5. In this embodiment, driving signal SC1 is equal to preset signal STV1. When the anode of electroluminescent element ELb receives STV1, turn-off time of electroluminescent element ELb is longer than turn-on time of electroluminescent element ELb. Therefore, brightness emitted from display panel 22 is low when environmental brightness is low. Preset signal STV2 is generated as brightness emitted from an environment is bright. Scan driver 262 provides driving signal SC1 according to preset signal STV2 shown in Fig. 5. In this embodiment, driving signal SC1 is equal to preset signal STV2. When the anode of electroluminescent element ELb receives STV1, turn-on time of electroluminescent element ELa is longer than turn-off time of electroluminescent element ELb. Therefore, brightness emitted from display panel 22 is high.

**[0039]** As described previously, signal generator 24 controls a duty cycle of a preset signal according to brightness of environmental light and/or of light of a light-emitting element. When the signal generator 24 is utilized in an electronic system comprising a display panel, if the signal generator 24 detects environmental brightness, brightness of the display panel is changed accordingly. If the signal generator 24 detects brightness of light emitted from the light-emitting element, aging of the light-emitting element can be mitigated.

**[0040]** While the invention has been described by way of example and in terms of embodiments, it is to be understood that the invention is not limited thereto. To the contrary, it is intended to cover various modifications and similar arrangements (as would be apparent to those skilled in the art). Therefore, the scope of the appended claims should be accorded the broadest interpretation so as to encompass all such modifications and similar arrangements.

#### Claims

- A system for controlling brightness of displayed images comprising:

- a signal generator, comprising:

a control unit outputting a reference voltage according to the brightness of light emitted during a first period and outputting a reference signal during a second period;

a first processing unit comprising a first input terminal and a first output terminal, wherein a voltage of the first input terminal is equal to that of the first output terminal during the first period and a logic level of the first output terminal is inverse to a logic level of the first input terminal; and

a storage unit storing a response voltage according to the reference voltage and the voltage of the first input terminal during the first period and controlling the logic level of the first input terminal according to the reference voltage and the response voltage during the second period.

- 2. The system as claimed in claim 1, wherein the control unit comprises:

- a photo-detection device providing the reference voltage according to the brightness of the light emitted; and

- a selection device outputting the reference voltage during the first period and outputting the reference signal during the second period.

- **3.** The system as claimed in claim 2, wherein the reference signal is a triangular signal.

- 40 **4.** The system as claimed in claim 1, further comprising a light emitting element; and wherein the light is generated by the light-emitting element.

- 5. The system as claimed in claim 1, wherein the first processing unit comprises:

a switching device turned on during the first period and turned off during the second period; and an inverting device coupled to the switching device in parallel, wherein a voltage of an input terminal of the inverting device is equal to that of an output terminal of the inverting device as the switching device is turned on and a logic level of the output terminal of the inverting device is inverse to that of the input terminal of the inverting device.

6. The system as claimed in claim 1, wherein the stor-

50

10

25

30

45

50

age unit comprises a capacitor.

- 7. The system as claimed in claim 1, further comprising a second processing unit comprising a second input terminal coupled to the first output terminal and a second output terminal, wherein the voltage of the first input terminal is equal to that of the second output terminal during the first period and a logic level of the second output terminal is equal to that of the first input terminal during the second period.

- **8.** The system as claimed in claim 7, wherein the first and the second processing units respectively comprise:

a switching device turned on during the first period and turned off during the second period; and an inverting device coupled to the switching device in parallel, wherein voltage of an input terminal of the inverting device is equal to that of a output terminal of the inverting device as the switching device is turned on and a logic level of the output terminal of the inverting device is inverse to that of the input terminal of the inverting device.

- The signal generator as claimed in claim 8, wherein the control unit outputs the reference voltage in accordance with a detected brightness of ambient light.

- **10.** A system for controlling brightness of displayed images comprising:

an electronic system comprising:

a display panel comprising a plurality of light-emitting elements; and a signal generator comprising:

a control unit outputting a reference voltage according to the brightness of light emitted during a first period and outputting a reference signal during a second period;

a first processing unit comprising a first input terminal and a first output terminal, wherein a voltage of the first input terminal is equal to that of the first output terminal during the first period and a logic level of the first output terminal is inverse to a logic level of the first input terminal; and

a storage unit storing a response voltage according to the reference voltage and the voltage of the first input terminal during the first period and controlling the logic level of the first input terminal according to the reference voltage and

the response voltage during the second period.

- 11. The system of claim 10, further comprising a driving device operative to adjust brightness of light emitted from the light-emitting elements according to the logic level of the first output terminal.

- **12.** The system of claim 10, further comprising:

means for adjusting brightness of light emitted from the light-emitting elements according to the logic level of the first output terminal.

- 5 13. The system as claimed in claim 10, wherein the signal generator controls the logic level of the first output terminal according to the brightness of light emitted from the light-emitting elements.

- 14. The system as claimed in claim 10, further comprising the light-emitting elements are string lamps.

- 15. The system as claimed in claim 10, wherein the signal generator further comprises a second processing unit comprising a second input terminal coupled to the first output terminal and a second output terminal, wherein the voltage of the first input terminal is equal to that of the second output terminal during the first period and a logic level of the second output terminal is equal to that of the first input terminal during the second period and wherein the logic level of the second output terminal is controlled according to brightness of ambient light detected.

- 35 16. The system as claimed in claim 14, further comprising a driving device; and wherein the driving device provides a driving signal to the light-emitting element for controlling brightness emitted from the light-emitting element according to the logic level of the second output terminal.

- **17.** The system as claimed in claim 16, wherein the brightness emitted from the light-emitting element is proportional to a detected brightness of ambient light.

- **18.** A system for controlling brightness of displayed images of a display panel, said system comprising:

- a control unit operative to adjust brightness of a corresponding display panel based upon at least one of: detected brightness of ambient light and brightness of light emitting elements of the display panel.

## **EUROPEAN SEARCH REPORT**

Application Number EP 05 11 2302

|                                            | DOCUMENTS CONSIDE                                                                                                                                                        | RED TO BE RELEVAN                                                | 1T                                                                                                                                  |                                    |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Category                                   | Citation of document with inc<br>of relevant passag                                                                                                                      |                                                                  | Relevar<br>to claim                                                                                                                 |                                    |

| X<br>Y                                     | US 5 170 155 A (PLUS<br>8 December 1992 (199<br>* column 4, line 7 -<br>figure 3 *                                                                                       | 92-12-08)                                                        |                                                                                                                                     | G09G3/34<br>G09G3/32               |

| (                                          | DE 102 27 487 A1 (W)                                                                                                                                                     |                                                                  | 18                                                                                                                                  |                                    |

| ,                                          | 18 March 2004 (2004-<br>* paragraph [0012] -<br>figure 1 *                                                                                                               |                                                                  | 2,3,9,<br>11,14,                                                                                                                    |                                    |

|                                            | US 2004/105287 A1 (0<br>3 June 2004 (2004-06<br>* paragraph [0033] -<br>* paragraph [0061] -                                                                             | 5-03)<br>- paragraph [0042] *                                    |                                                                                                                                     |                                    |

|                                            | figures 1,3 * EP 0 685 831 A (SHAF                                                                                                                                       | <br>RP KABUSHIKI KAISHA)                                         | 18                                                                                                                                  |                                    |

|                                            | 6 December 1995 (199<br>* column 28, line 14<br>figures 1,2 *                                                                                                            | 95-12-06)                                                        |                                                                                                                                     | TECHNICAL FIELDS<br>SEARCHED (IPC) |

|                                            | WO 2005/006291 A (KC<br>ELECTRONICS N.V; HOR<br>J., L; VA) 20 Januar<br>* page 6, line 11 -                                                                              | PPENBROUWERS, JURGEN<br>ry 2005 (2005-01-20)                     | 10-12,                                                                                                                              | G09G<br>H02M                       |

|                                            | figures 1,2 * US 2004/012340 A1 ()                                                                                                                                       |                                                                  | 16,17                                                                                                                               |                                    |

|                                            | 22 January 2004 (200                                                                                                                                                     |                                                                  | 10-17                                                                                                                               |                                    |

|                                            | The present search report has be                                                                                                                                         | sen drawn un for all claims                                      |                                                                                                                                     |                                    |

|                                            | Place of search                                                                                                                                                          | Date of completion of the sea                                    | ırch                                                                                                                                | Examiner                           |

|                                            | Munich                                                                                                                                                                   | 13 April 2006                                                    | 1                                                                                                                                   | lorris, D                          |

| X : parti<br>Y : parti<br>docu<br>A : tech | ATEGORY OF CITED DOCUMENTS icularly relevant if taken alone icularly relevant if combined with anothe iment of the same category nological background written disclosure | E : earlier pat<br>after the fil<br>D : document<br>L : document | orinciple underlying t<br>ent document, but p<br>ing date<br>cited in the applicat<br>cited for other reaso<br>f the same patent fa | ublished on, or<br>ion<br>ins      |

### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 05 11 2302

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

13-04-2006

| Patent docun<br>cited in search |         | Publication date |                                              | Patent family<br>member(s)                                                                          |                          | Publication date                                                                                         |

|---------------------------------|---------|------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------|

| US 5170155                      | 5 A     | 08-12-1992       | DE<br>DE<br>EP<br>WO<br>JP<br>JP<br>JP<br>JP | 69124988<br>69124988<br>0506906<br>9207351<br>3270034<br>2000155558<br>5503175<br>3128073<br>221106 | A1<br>B2<br>A<br>T<br>B2 | 10-04-19<br>12-06-19<br>07-10-19<br>30-04-19<br>02-04-20<br>06-06-20<br>27-05-19<br>29-01-20<br>15-09-19 |

| DE 1022748                      | 37 A1   | 18-03-2004       | NONE                                         |                                                                                                     |                          |                                                                                                          |

| US 2004105                      | 5287 A1 | 03-06-2004       | NONE                                         |                                                                                                     |                          |                                                                                                          |

| EP 0685831                      | L A     | 06-12-1995       | DE<br>DE<br>JP<br>JP<br>KR                   | 69512704<br>69512704<br>3027298<br>7325286<br>166145                                                | T2<br>B2<br>A            | 18-11-19<br>27-04-20<br>27-03-20<br>12-12-19<br>20-03-19                                                 |

| WO 2005006                      | 5291 A  | 20-01-2005       | NONE                                         |                                                                                                     |                          |                                                                                                          |

| US 2004012                      | 2340 A1 | 22-01-2004       | JP                                           | 2003295826                                                                                          | Α                        | 15-10-20                                                                                                 |

FORM P0459

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82