# (11) **EP 1 811 491 A1**

(12)

## **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication:25.07.2007 Bulletin 2007/30

(51) Int Cl.: **G09G 3/28** (2006.01)

(21) Numéro de dépôt: 07290067.3

(22) Date de dépôt: 18.01.2007

(84) Etats contractants désignés:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI SK TR

Etats d'extension désignés:

AL BA HR MK YU

(30) Priorité: 20.01.2006 FR 0600556

(71) Demandeur: STMICROELECTRONICS SA 92120 Montrouge (FR)

(72) Inventeurs:

- Bezal, Jean-Raphael 38000 Grenoble (FR)

- Permezel, Jean-Marie 38000 Grenoble (FR)

- Troussel, Gilles 38000 Grenoble (FR)

- (74) Mandataire: Zapalowicz, Francis Bureau Casalonga & Josse Bayerstrasse 71/73 80335 München (DE)

## (54) Procede et dispositif de commande d'un ecran a plasma matriciel

(57) L'invention porte sur un dispositif de commande d'un écran plasma matriciel comprenant un circuit de commande des lignes aptes à sélectionner séquentiellement les lignes de la matrice et un circuit de commande des colonnes comprenant pour chaque colonne (Cj) de la matrice un bloc individuel de commande de colonnes (BCCj), comprenant un moins un premier transistor de type MOS (T2), apte à émettre vers chaque colonne d'un ensemble de colonne désiré, un signal de changement d'état pour permettre le passage dudit ensemble d'un premier état vers un deuxième état, et un moyen de con-

trôle (MCj). Le premier transistor est apte à émettre les signaux de changement d'état qui comprennent un état transitionnel depuis un état bas vers un état haut, ledit moyen de contrôle comprenant un transistor de contrôle (TC) comprenant une électrode connectée directement à la borne d'alimentation et une autre électrode apte à délivrer une tension de contrôle sur l'électrode de commande du premier transistor, de façon à limiter la valeur du courant (I<sub>T2</sub>) traversant ledit premier transistor (T2) au cours de l'état transitionnel, de manière à réguler le temps de montée du signal de changement d'état.

Fig.4

EP 1 811 491 A1

40

sinage proche.

#### Description

**[0001]** L'invention concerne les écrans à plasma, et plus particulièrement la commande des cellules d'un tel écran.

1

[0002] Un écran à plasma est un écran de type matriciel, formé de cellules disposées aux intersections de lignes et de colonnes. Une cellule comprend une cavité remplie d'un gaz rare, et au moins deux électrodes de commande. Pour créer un point lumineux sur l'écran en utilisant une cellule donnée, on sélectionne la cellule en appliquant une différence de potentiel entre ses électrodes de commande, puis on déclenche une ionisation du gaz de la cellule généralement au moyen d'une troisième électrode de commande. Cette ionisation s'accompagne d'une émission de rayons ultraviolets. La création du point lumineux est obtenue par excitation d'un matériau luminescent rouge, vert ou bleu, par les rayons émis.

[0003] Classiquement, la commande d'un écran à plasma comporte essentiellement deux phases, à savoir une phase d'adressage dans laquelle on détermine les cellules (pixels) qui devront être allumées et celles qui devront être éteintes, ainsi qu'une phase d'affichage proprement dite dans laquelle on allume effectivement les cellules ayant été sélectionnées dans la phase d'adressage.

[0004] La phase d'adressage comporte une sélection séquentielle des lignes de la matrice. A titre d'exemple, les lignes non sélectionnées sont mises à un potentiel de repos, par exemple 150 volts, tandis qu'une ligne sélectionnée est amenée à un potentiel d'activation, par exemple 0 volt. Pour sélectionner des pixels choisis de la ligne sélectionnée, pixels qui devront être allumés dans la phase d'affichage, les colonnes correspondantes de la matrice sont par exemple amenées à un potentiel relativement élevé, par exemple 70 volts, par l'intermédiaire d'un étage de puissance comportant des transistors MOS de puissance. Les colonnes correspondant aux autres pixels de la ligne sélectionnée, qui ne devront pas être allumées, sont amenées au potentiel 0 volt. Ainsi, les cellules de la ligne activée, qui devront être allumées, voient un potentiel colonne-ligne égal à environ 70 volts tandis que les autres cellules de cette ligne, voient un potentiel colonne-ligne égal à 0 volt.

[0005] Cela étant, il est également envisageable dans la phase d'adressage, moyennant l'application de potentiels différents sur les lignes de la matrice, d'appliquer un potentiel haut sur une colonne pour sélectionner un pixel qui devra être éteint, et d'appliquer un potentiel bas sur une colonne pour sélectionner un pixel qui devra être allumé.

[0006] La demande de brevet internationale WO 02/15 163 donne un exemple du fonctionnement général d'un tel écran à plasma, et se focalise en particulier sur le problème de la sélection des colonnes lorsqu'une ligne a été sélectionnée. Plus précisément, ce document de l'art antérieur évoque et résout le problème du pic de courant traversant les transistors de puissance connec-

tés à la ligne sélectionnée, lorsqu'un très grand nombre de colonnes sont sélectionnées simultanément (correspondant à un très grand nombre de pixels qui devront être allumés).

[0007] Outre le problème du pic de courant traversant les transistors de puissance lorsqu'un très grand nombre de colonnes sont sélectionnées simultanément, les inventeurs ont identifié un autre problème dans la commande des cellules d'un écran à plasma, plus particulièrement lorsque la commande est effectuée avec un signal comprenant une transition d'un potentiel bas à un potentiel haut.

**[0008]** Plus précisément, supposons que tous les pixels de la ligne i doivent être dans un premier état donné, par exemple allumés (ou éteints, selon la convention choisie) et que tous les pixels de la ligne suivante i+1 doivent être dans l'autre état, par exemple éteints (ou allumés, selon la convention envisagée). Dans ce cas, dans la phase d'adressage, lors de la sélection de la ligne i, toutes les colonnes de l'écran seront commandées pour changer d'état, c'est-à-dire que leur potentiel sera porté à un état haut (à 70 volts par exemple), en suivant un front de montée en un temps donné.

**[0009]** Puis, lorsque la ligne suivante, i+1, est activée, il faut refaire tomber le potentiel des colonnes à un état bas (0 volt par exemple).

**[0010]** Le passage d'un état à l'autre s'effectue en appliquant un signal logique à un module de commande situé sur chacune des colonnes de façon à ce que l'un des transistors de puissance du module de commande devienne passant pour autoriser la charge ou la décharge (selon la convention considérée) de la capacité de la cellule considérée.

[0011] Il a été observé que lorsqu'un très grand nombre de colonnes passent d'un potentiel bas à un potentiel haut, par exemple deux tiers des colonnes au moins de l'écran, les fronts de montée des tensions de colonnes respectives sont particulièrement raides, c'est-à-dire que le temps de montées est de l'ordre de 40 nanosecondes.

[0012] Ceci conduit à l'émission de perturbations électromagnétiques supplémentaires qui peuvent gêner le

fonctionnement d'autres composants situés dans un voi-

[0013] En outre, d'un circuit à l'autre, en fonction de la valeur de la charge connectée au circuit de sélection, la valeur du courant de sélection peut varier. En particulier, lorsque la valeur de la charge est relativement faible, le courant de sélection peut prendre une valeur très importante entraînant un fort pic de surtension au niveau de la source de tension fournissant le potentiel d'activation haut (ici 70 volts) du circuit de commande des colonnes de l'écran.

[0014] La demande de brevet internationale WO 02/41 292 au nom de la demanderesse propose une solution où le circuit de commande des colonnes comprend une source de courant de façon à contrôler la tension appliquée sur la grille du transistor de puissance délivrant le signal de sélection. Le contrôle va s'effectuer durant tou-

35

40

te la montée du signal de transition de sa valeur basse à sa valeur haute. Le temps de montée du signal de sélection est donc fixé et constant, et la valeur de courant délivré par le transistor de puissance contrôlé, sera limitée durant toute la transition.

**[0015]** Cependant, l'intégration d'une source de courant dans le circuit de contrôle des colonnes représente un coût élevé en terme de surface de silicium nécessaire pour réaliser le circuit.

**[0016]** En outre, le front raide du signal de sélection est atténué par le contrôle effectué par la source de courant, mais en fin de transition, celle-ci est par contre plus raide qu'elle ne l'était, ce qui génère des signaux haute-fréquence, qui favorisent les émissions électromagnétiques.

**[0017]** Par ailleurs, la source de courant est sensible aux fluctuations de la tension d'alimentation du circuit de commande, ce qui perturbe le contrôle effectué sur la grille du transistor de puissance.

**[0018]** L'invention vise à apporter une solution à ces problèmes.

**[0019]** Un but de l'invention est de limiter de façon très simple les émissions électromagnétiques liées à la raideur des fronts de montée des signaux de sélection (ou de désélection) de colonne, et des pics de courant résultants, quelle que soit la charge vue par le circuit, et sans augmenter de façon significative la surface de silicium nécessaire à la réalisation du circuit.

**[0020]** Un autre but de l'invention est de diminuer la sensibilité du circuit aux variations de la tension d'alimentation, liée à l'utilisation d'une source de courant.

**[0021]** Un autre but de l'invention est de favoriser la diminution des émissions électromagnétiques liées à la raideur de la transition, lorsque le signal de changement d'état atteint sa valeur haute.

[0022] Ainsi, selon un aspect de l'invention, il est proposé un procédé de commande d'un écran à plasma matriciel comprenant une sélection séquentielle de lignes de la matrice et pour une ligne sélectionnée, l'émission d'un signal de changement d'état vers chaque colonne d'un ensemble de colonnes désirées, à l'aide d'un premier transistor de type MOS, pour permettre le passage de chaque colonne dudit ensemble d'un premier état vers un deuxième état.

**[0023]** Selon une caractéristique générale de cet aspect de l'invention, chaque signal de changement d'état comprend un état transitionnel depuis un état bas vers un état haut. Par ailleurs, on régule le temps de montée du signal de changement d'état, en limitant la valeur du courant traversant ledit premier transistor au cours de l'état transistionnel, par le contrôle de la valeur de la tension délivrée sur l'électrode de commande du premier transistor à l'aide d'un transistor de contrôle.

[0024] En d'autres termes, on régule le temps de montée du signal de changement d'état en contrôlant le courant qui circule dans le transistor délivrant le signal de changement d'état, uniquement lors de la transition depuis l'état bas vers l'état haut, et plus particulièrement au démarrage de cette transition.

[0025] Par ailleurs, du fait du contrôle de la valeur de la tension délivrée sur l'électrode de commande du premier transistor, le passage depuis un état bas vers un état haut du signal de changement d'état comprend une augmentation progressive de la valeur dudit signal selon une rampe donnée. Le contrôle effectué a pour avantage d'imposer un temps de montée minimal quelle que soit la valeur de la charge connectée au dispositif de commande, tout en assurant une fin de transition plus douce du signal de changement d'état, étant donné que la valeur du courant traversant ledit premier transistor n'est limitée qu'au démarrage de la transition.

**[0026]** De préférence, la valeur du courant traversant ledit premier transistor est limitée uniquement pendant l'état transitionnel. Par exemple, la valeur du courant traversant ledit premier transistor peut être limitée tant que la valeur de la tension de commande dudit premier transistor est inférieure à un seuil fonction des caractéristiques dudit transistor de contrôle.

**[0027]** De préférence, le temps de montée du signal de changement d'état est compris dans un intervalle s'étendant de 70 nanosecondes à 150 nanosecondes.

**[0028]** En d'autres termes on détermine la rampe du signal de changement d'état pour que celui-ci s'effectue dans la plage précitée.

[0029] Selon un autre aspect de l'invention, il est proposé un dispositif de commande, un écran plasma matriciel comprenant un circuit de commande des lignes apte à sélectionner séquentiellement les lignes de la matrice et un circuit de commande des colonnes comprenant pour chaque colonne de la matrice un bloc individuel de commande de colonnes, comprenant au moins un premier transistor de type MOS, apte à émettre vers chaque colonne d'un ensemble de colonnes désirées, un signal de changement d'état pour permettre le passage dudit ensemble d'un premier état vers un deuxième état, et un moyen de contrôle.

[0030] Selon une caractéristique générale de cet autre aspect de l'invention, le premier transistor est apte à émettre les signaux de changement d'état qui comprennent un état transitionnel depuis un état bas vers un état haut, ledit moyen de contrôle comprenant un transistor de contrôle comprenant une électrode connectée directement à la borne d'alimentation et une autre électrode apte à délivrer une tension de contrôle sur l'électrode de commande du premier transistor, de façon à limiter la valeur du courant traversant ledit premier transistor au cours de l'état transitionnel, de manière à réguler le temps de montée du signal de changement d'état.

**[0031]** Ce circuit a pour avantage d'être particulièrement simple à réaliser puisque seul le dimensionnement du transistor de contrôle permet la limitation du courant circulant dans le premier transistor délivrant le signal de changement d'état.

**[0032]** En utilisant les paramètres du transistor de contrôle, la limitation du courant traversant le premier transistor MOS n'est effective qu'au démarrage, puis s'atté-

nue en raison du changement de zone de fonctionnement du transistor de contrôle, lorsque le signal de changement d'état atteint une certaine valeur.

[0033] Le temps de montée du signal de changement d'état est de préférence compris dans un intervalle s'étendant de 70 nanosecondes à 150 nanosecondes.

[0034] Selon un mode de réalisation, le transistor de contrôle comprend :

- une électrode de commande apte à recevoir ledit signal de commande de changement d'état, et

- une première électrode connectée à l'électrode de commande du premier transistor et apte à délivrer une tension du contrôle ayant une transition depuis un état bas vers un état haut avec un temps de montée équivalent au temps de montée du signal de changement d'état.

[0035] Selon un mode de réalisation, le moyen de contrôle comprend en outre une résistance de contrôle connectée entre la borne d'alimentation et une deuxième électrode du transistor de contrôle, la valeur de laquelle est déterminée en fonction du temps de montée du signal de changement d'état.

**[0036]** Ainsi, en utilisant une résistance de contrôle ayant une valeur choisie, il est possible d'utiliser un transistor de contrôle avec un paramétrage moins fin de ses dimensions et par exemple d'ajuster la durée de la limitation du courant traversant le premier transistor simplement à l'aide de la résistance de contrôle.

[0037] Par exemple, la résistance de contrôle peut avoir une valeur de l'ordre de quelques dizaines de  $k\Omega$ . [0038] De préférence, le moyen de contrôle comprend en outre un deuxième transistor connecté entre le premier transistor et la masse.

**[0039]** Selon un autre aspect de l'invention, il est également proposé un écran à plasma comprenant un écran à plasma matriciel et un dispositif de commande tels que décrit ci-avant.

**[0040]** D'autres avantages et caractéristiques de l'invention apparaîtront à l'examen de la description détaillée de modes de réalisation et de mise en oeuvre, nullement limitatifs, et des dessins annexés sur lesquels :

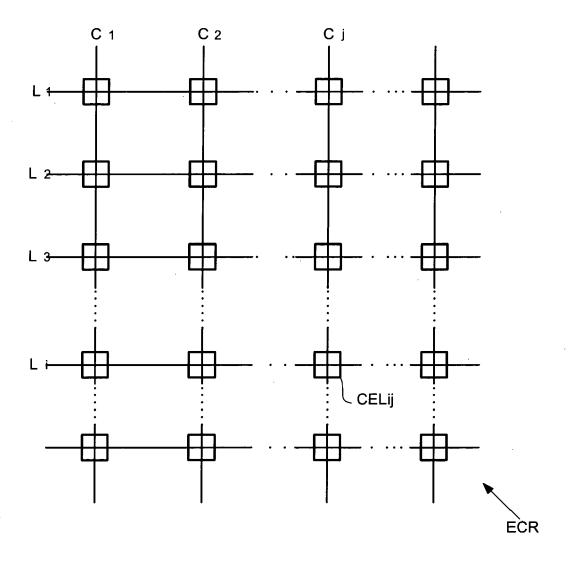

- la figure 1 est une illustration très schématique d'un écran matriciel selon un mode de réalisation de l'invention,

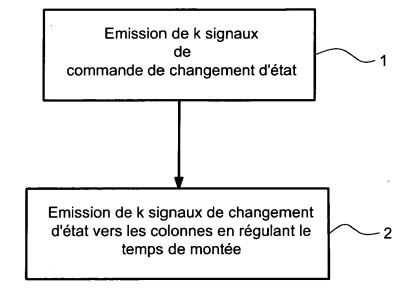

- la figure 2 décrit un mode de mise en oeuvre du procédé selon l'invention,

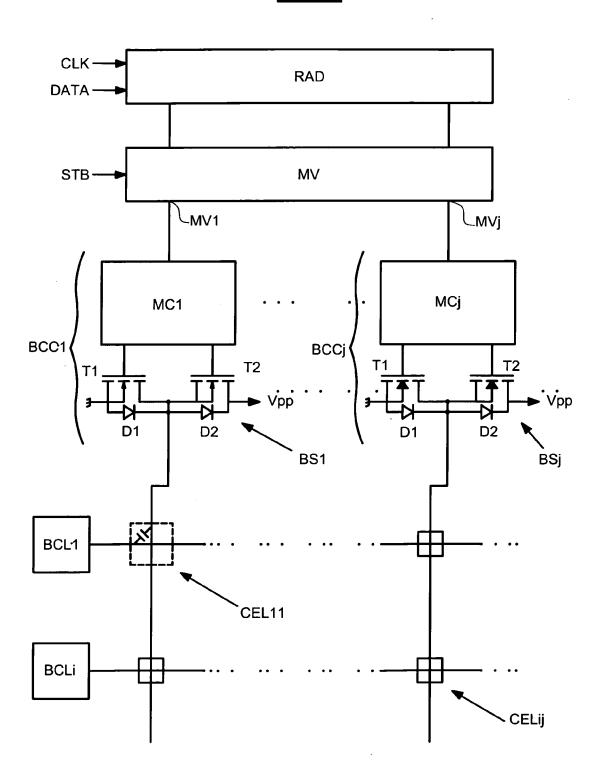

- la figure 3 est une représentation détaillée d'un mode de réalisation d'un dispositif de commande selon l'invention.

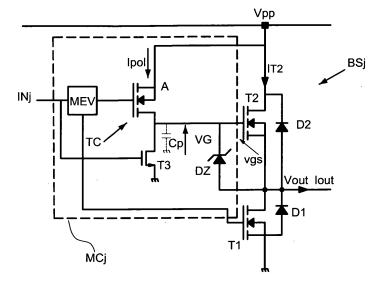

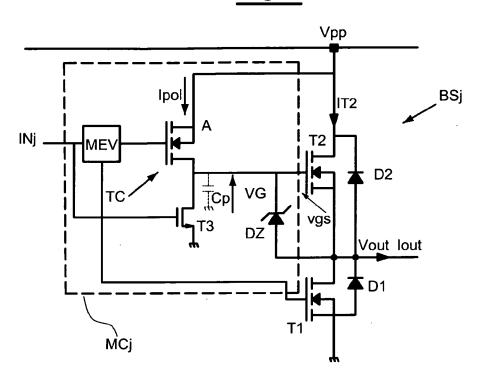

- la figure 4 illustre plus précisément un mode de réalisation d'un moyen de contrôle selon l'invention,

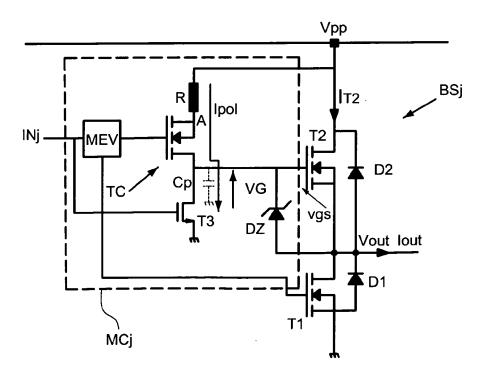

- la figure 5 illustre une variante d'un moyen de contrôle selon l'invention,

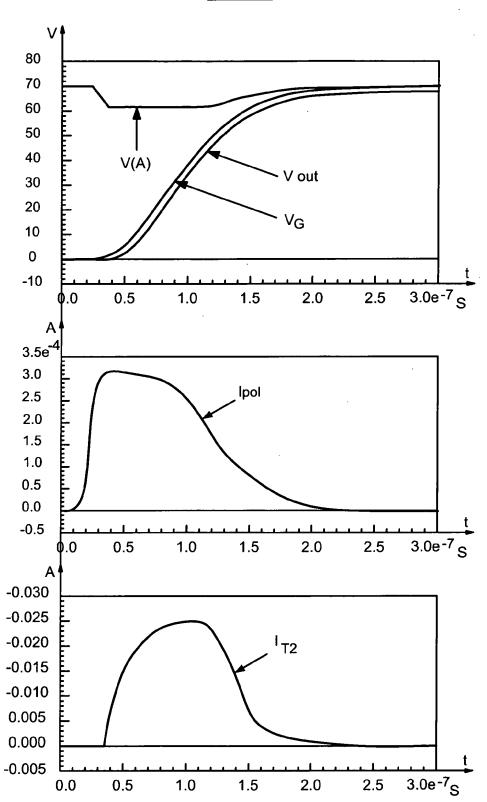

- la figure 6 illustre la variation des signaux mis en oeuvre par un moyen de contrôle selon l'invention,

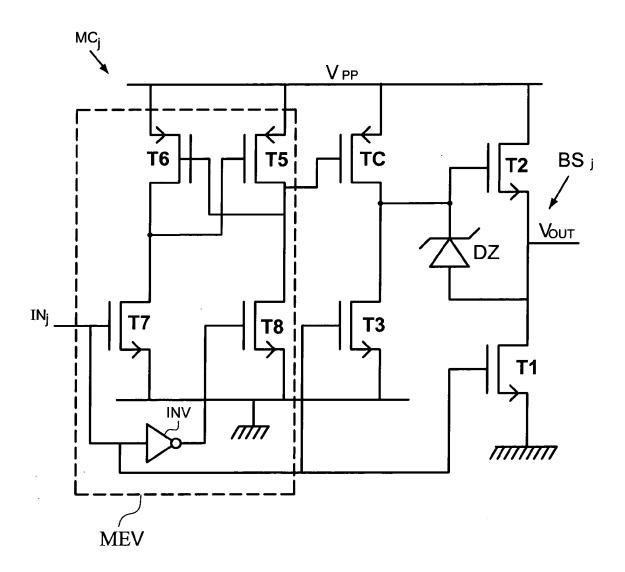

la figure 7 illustre plus en détail un exemple de réalisation d'une partie d'un moyen de contrôle selon l'invention,

[0041] La figure 1 représente très schématiquement une structure d'un écran à plasma matriciel ECR formé de cellules CELij (correspondant à des pixels de l'image). Chaque cellule CELij a deux électrodes de commande respectivement reliées à une ligne Li et à une colonne Cj. Chaque cellule a une capacité équivalente de l'ordre de plusieurs dizaines de picofarads. Le dispositif de commande de cet écran comporte un circuit de commande de lignes apte à sélectionner séquentiellement les lignes de la matrice, et un circuit de commande de colonnes apte à sélectionner et éventuellement désélectionner plusieurs colonnes précédemment sélectionnées.

**[0042]** Ces circuits sont généralement intégrés sur une puce semiconductrice.

**[0043]** Classiquement, lorsqu'une colonne a été sélectionnée, son potentiel est porté à une valeur élevée Vpp, typiquement de l'ordre de 70 volts (pour allumer ou éteindre un pixel selon le mode d'utilisation choisi pour l'écran).

[0044] Comme décrit sur la figure 2, lorsque k colonnes doivent être sélectionnées (pour éteindre ou allumer un pixel selon le mode d'utilisation choisi pour l'écran), il faut amener la tension de chaque colonne de la valeur zéro à la valeur Vpp, par exemple. Pour cela, k signaux de commande de changement d'état sont émis dans une première étape, entraînant lors d'une deuxième étape, l'émission simultanée des k signaux de.sélection des k colonnes, tout en régulant le temps de montée de chacun de ces signaux.

**[0045]** La figure 3 illustre schématiquement un mode de réalisation d'un dispositif de commande selon l'invention permettant une mise en oeuvre du procédé selon l'invention.

**[0046]** Le circuit de commande de lignes comporte ici des blocs individuels de commande lignes BCL1-BCLi, de structure classique et connue en soi, respectivement connectés sur les lignes de la matrice de l'écran.

**[0047]** Les circuits de commande de colonnes comportent des blocs individuels de commande BCC1-BCCj respectivement connectés sur les colonnes C1-Cj de l'écran.

[0048] Le circuit de commande de colonnes comprend également, en amont de ces blocs individuels de commande, un registre à décalage RAD, cadencé par un signal d'horloge CLK et recevant les données binaires référencées DATA, et destiné notamment à éventuellement désélectionner des colonnes qui ont été précédemment sélectionnées lors de la sélection d'une ligne précédente.

**[0049]** Les sorties du registre à décalage RAD sont reliées aux entrées d'une mémoire-verrou MV dont les sorties respectives sont connectées aux entrées des blocs individuels de commande BCC1-BCCj.

[0050] La mémoire-verrou MV est commandée par un

signal d'activation STB qui va délivrer sur ces sorties MV1-MVj les données présentes en entrée de la mémoire-verrou MV.

**[0051]** Chaque bloc individuel de commande BCCj comporte un moyen de contrôle MCj dont la structure sera décrite plus en détail ci-après.

[0052] La sortie du bloc MCj est reliée à un étage de puissance BSj formé ici de deux transistors MOS, T1 et T2, des NMOS dans ce cas. Dans cet exemple, le transistor T1 peut délivrer un signal de désélection de la colonne, tandis que le transistor T2 peut délivrer un signal de sélection de la même colonne.

**[0053]** Les signaux de sélection des colonnes peuvent être émis simultanément ou non.

[0054] Les grilles de chaque transistor sont connectées respectivement à deux sorties du moyen de contrôle MCj. Par ailleurs, la source du transistor T1 est reliée à la masse, tandis que le drain du transistor T2 est relié à la tension Vpp. La source du transistor T2 et 1e drain du transistor T1 sont mutuellement connectés.

[0055] En outre, l'étage de puissance BSj comprend deux diodes D1 et D2 connectées respectivement entre la source et le drain de T1 d'une part et entre la source et le drain de T2 d'autre part. Les deux diodes D1 et D2 sont des diodes de protection pour les deux transistors T1 et T2, bien connues de l'homme du métier.

[0056] Le noeud commun entre les deux transistors T1 et T2 est relié à chaque colonne correspondante.

**[0057]** On se réfère à présent à la figure 4 qui décrit un premier mode de réalisation d'un moyen de contrôle MCj.

[0058] Le moyen de contrôle reçoit en entrée un signal de commande de changement d'état INj issu d'une sortie MVj de la mémoire-verrou MV. Le signal est à l'état bas ou haut selon que la colonne Cj est sélectionnée ou non. Par exemple, INj est égal à 0 Volt à l'état bas, et 5 Volt à l'état haut.

**[0059]** Le signal INj est délivré à un moyen MEV qui forme un circuit élévateur de tension, de façon à porter la tension du signal INj à la valeur Vpp.

**[0060]** Le moyen MEV est connecté à la grille d'un transistor de contrôle TC, dont la source est connectée à la tension Vpp, et le drain, à la grille du transistor T2 de l'étage de puissance BSj. Le transistor de contrôle TC est choisi pour pouvoir supporter de fortes tensions entre ses électrodes de grille et de source.

[0061] Par exemple, il est particulièrement avantageux d'utiliser un transistor de type à oxyde de grille épais (« Thick Gate Oxyde », « TGO » en langue anglaise), de type PMOS dans ce cas. A titre indicatif, il est préférable que le transistor de contrôle possède une couche d'oxyde de grille ayant une épaisseur supérieure à 0.5 µm.

**[0062]** En variante, l'homme du métier saura adapter les types de conductivité des transistors T1, T2 et TC.

**[0063]** Le moyen de contrôle comprend également un condensateur Cp connecté entre le drain du transistor de contrôle TC et la masse. Le condensateur Cp représente l'ensemble des condensateurs parasites présents

dans le circuit. La capacité du condensateur Cp comprend notamment les valeurs du condensateur de grille de T2, des condensateurs du transistor TC ainsi que celle des diodes présentes dans le circuit.

[0064] Une diode Zenner DZ est également connectée entre la grille du transistor T2 et sa source de façon à protéger la grille du transistor T2 d'éventuelles surtensions pouvant apparaître.

**[0065]** Lorsque le signal de commande de changement d'état lNj passe de l'état bas à l'état haut, indiquant dans cet exemple la sélection de la colonne Cj, un courant de polarisation lpol circule dans le transistor de contrôle TC.

[0066] Le courant lpol charge le condensateur Cp, et une tension de rampe  $V_G$  apparaît à ses bornes.

**[0067]** Par conséquent, la tension  $V_{gs}$ , entre la grille et la source du transistor T2, qui est fonction de la tension de rampe  $V_G$ , permet de rendre passant le transistor T2. Un courant  $I_{T2}$  circule alors à travers le transistor T2. Un courant de sortie lout est généré vers la colonne Cj et le signal de tension de changement d'état Vout passe progressivement de l'état bas à l'état haut, en suivant l'évolution de la tension de rampe,  $V_G$ , qui commande donc la grille de T2.

**[0068]** Le bloc BSj comprend également un transistor MOS T3 connecté entre la grille de T2 et la masse et commandé sur sa grille par le signal INj. Le transistor T3 a pour fonction de fixer le potentiel sur la grille de T2, lorsque le circuit passe en désélection, ce qui permet d'éviter que la grille se retrouve dans un état de haute-impédance.

[0069] La figure 5 représente un mode de réalisation du moyen de contrôle MCj analogue au mode de réalisation décrit précédemment, mais intégrant en plus une résistance R, par exemple de l'ordre d'une dizaine de  $k\Omega$ , entre la borne délivrant la tension Vpp et la source du transistor TC.

**[0070]** L'utilisation d'une résistance R autorise un paramétrage moins fin du transistor de contrôle.

[0071] Le paramétrage du transistor de contrôle TC, dans le mode de réalisation de la figure 4, et le choix de la valeur de la résistance dans le mode de réalisation de la figure 5 sont deux moyens simples à mettre en oeuvre pour limiter le courant de polarisation Ipol qui va charger le condensateur Cp. Sa charge progressive va permettre l'augmentation progressive de la valeur de la tension de sortie Vout, ainsi qu'une limitation du courant de sortie lout.

**[0072]** La figure 6 représente la variation du courant lpol, de la tension au point A, de la tension de sortie et du courant l<sub>T2</sub>, dans le mode de réalisation comprenant une résistance R.

**[0073]** La figure 6 représente tout d'abord la variation de la tension au point A, c'est-à-dire à la source du transistor TC. Cette tension du fait de la valeur de la résistance R, diminue légèrement au début du changement d'état de façon à fixer la valeur de  $V_{\rm gs}$  du transistor TC de façon à délivrer le courant Ipol adapté.

**[0074]** La tension Vout, quant à elle, augmente progressivement entre un état bas, ici 0 volt jusqu'à l'état haut, ici 70 volts. Elle a le même profil que la tension de commande de la grille du transistor  $T2V_G$ , correspondant à la charge du condensateur Cp.

[0075] La rampe de la tension Vout est donc fonction de la valeur du condensateur parasite Cp et du courant de charge lpol, fonction des caractéristiques du transistor de contrôle TC et/ou, le cas échéant, de la résistance R. [0076] La figure 6 représente également la variation du courant lpol. Le transistor de contrôle TC a une tension drain-source qui le place dans la zone de fonctionnement à saturation. Le transistor TC laisse alors passer un courant saturé d'une valeur ici de 300 microampères. Puis l'augmentation de tension sur la grille du transistor T2,  $\rm V_G$ , entraîne la diminution de la tension drain-source du transistor de contrôle TC.

**[0077]** En fonction des caractéristiques du transistor de contrôle TC, lorsque la tension drain-source de ce transistor est suffisamment faible, le transistor de contrôle TC bascule dans sa zone de fonctionnement ohmique.

[0078] Le courant lpol décroît alors régulièrement jusqu'à atteindre la valeur nulle.

**[0079]** Enfin, la figure 6 illustre la variation de la valeur du courant  $I_{T2}$  circulant à travers le transistor T2.

**[0080]** Dès que la différence Vout-V<sub>G</sub> rejoint la tension de seuil du transistor T2, celui ne laisse plus passer le courant, et la tension Vout est stabilisée.

[0081] A titre indicatif, les courbes de la figure 6 sont obtenues avec une résistance R avec une valeur de l'ordre de quelques dizaines de  $k\Omega,$  un condensateur Cp avec une valeur d'environ 1pF, et un transistor TC avec une largeur et une longueur de l'ordre d'une dizaine de  $\mu m$  chacune.

**[0082]** On se rapporte à présent à la figure 7 qui porte sur un mode de réalisation du moyen MEV réalisant un moyen élévateur de tension, quiest un mode de réalisation parmi d'autres.

**[0083]** Le moyen MEV comprend un premier transistor NMOS T7 recevant sur sa grille le signal INj et ayant son drain connecté à la masse.

**[0084]** Un transistor T8 de type NMOS est commandé sur sa grille par le signal opposé au signal INj. Un inverseur INV recevant le signal INj est donc connecté en amont de la grille de T8.

[0085] Le drain du transistor T8 est relié à la masse. [0086] Le moyen MEV comprend également deux autres transistors PMOS T6 et T5, dont les drains sont connectés respectivement aux drains des transistors T7 et T8.

[0087] Les sources des transistors T6 et T5 reçoivent la tension Vpp.

**[0088]** La grille du transistor T5 est reliée au drain du transistor T7, et la grille du transistor T6 est reliée au drain du transistor T8.

[0089] Dans cet exemple, la sélection d'une colonne implique le passage de l'état haut à l'état bas du signal

INj, de façon à délivrer une tension Vout passant de l'état bas à l'état haut. A l'inverse, une désélection implique le passage de l'état bas à l'état haut de ce même signal INj. [0090] Dans le cas d'une sélection, le signal INj passe de l'état haut à l'état bas. Les grilles des transistors T7, T3 et T1 sont donc à 0 volt (ici la valeur correspondant à l'état bas) et sont par conséquent bloquées. Par contre, la grille du transistor T8 est à 5 volts (ici la valeur correspondant à l'état haut), le transistor T8 est donc passant. Le drain du transistor T5 est donc à 0 volt, de même que la grille du transistor T6. Ce dernier est passant, ce qui amène la grille du transistor T5 à la valeur Vpp.

et donc passant du fait que le transistor T8 est passant. Aussi, la grille du transistor T2 de l'étage de puissance BSj est à la valeur Vpp, il est par conséquent passant. [0092] Dans le cas d'une désélection, le signal INj passe d'une valeur basse (par exemple 0 volt) à une valeur haute (par exemple 5 volts). Les grilles des transistors T1 et T3 passent à 5 volts, les deux transistors sont donc passants. Par conséquent, la grille du transistor T2 est à la valeur 0 volt, et est bloqué.

[0091] La grille du transistor T4 est à la valeur 0 volt,

[0093] Ainsi, l'invention permet d'obtenir un temps de montée du signal de changement d'état (ici Vout) compris dans une plage donnée, de préférence entre 70 ns et 150 ns, et ceci quelle que soit la charge connectée au circuit.

[0094] La régulation du temps de montée s'effectue par le contrôle de la grille du transistor délivrant le signal de changement d'état, ce contrôle étant concentré sur le démarrage du changement d'état. En effet, cet instant est le plus critique, notamment en ce qui concerne la génération de pics de tension au niveau du circuit de commande.

5 [0095] En outre, en limitant le contrôle au démarrage du changement d'état, des moyens faciles à implémenter et peu encombrants peuvent être utilisés tels qu'un paramétrage spécifique du transistor TC, l'ajout d'une résistance ayant une valeur choisie.

[0096] Bien entendu, l'invention n'est pas limitée aux modes de réalisation qui viennent d'être décrits mais en embrasse toutes les variantes.

### 5 Revendications

1. Procédé de commande d'un écran à plasma matriciel comprenant une sélection séquentielle de lignes de la matrice et pour une ligne sélectionnée, l'émission (2) d'un signal de changement d'état vers chaque colonne d'un ensemble de colonnes désiré, à l'aide d'un premier transistor de type MOS (T2), pour permettre le passage de chaque colonne dudit ensemble d'un premier état vers un deuxième état, caractérisé par le fait que chaque signal de changement d'état comprend un état transitionnel depuis un état bas vers un état haut et par le fait qu'on régule le temps de montée du signal de changement

50

55

10

15

d'état, en limitant la valeur du courant traversant ledit premier transistor au cours de l'état transitionnel, par le contrôle de la valeur de la tensi on délivrée sur l'électrode de commande du premier transistor à l'aide d'un transistor de contrôle (TC).

- 2. Procédé selon la revendication 1, dans lequel la valeur du courant traversant ledit premier transistor est limitée uniquement pendant l'état transitionnel.

- 3. Procédé selon la revendication 1 ou 2, dans lequel la valeur du courant traversant ledit premier transistor est limitée tant que la valeur de la tension de commande dudit premier transistor est inférieure à un seuil fonction des caractéristiques dudit transistor de contrôle.

- 4. Procédé selon l'une des revendications 1 à 3, dans lequel le temps de montée du signal de changement d'état est compris dans un intervalle s'étendant de 70 ns à 150 ns.

- 5. Dispositif de commande d'un écran plasma matriciel comprenant un circuit de commande des lignes aptes à sélectionner séquentiellement les lignes de la matrice et un circuit de commande des colonnes comprenant pour chaque colonne (Cj) de la matrice un bloc individuel de commande de colonnes (BCCj), comprenant un moins un premier transistor de type MOS (T2), apte à émettre vers chaque colonne d'un ensemble de colonne désiré, un signal de changement d'état pour permettre le passage dudit ensemble d'un premier état vers un deuxième état, et un moyen de contrôle (MCj), caractérisé par le fait le premier transistor est apte à émettre les signaux de changement d'état qui comprennent un état transitionnel depuis un état bas vers un état haut, ledit moyen de contrôle comprenant un transistor de contrôle (TC) comprenant une électrode connectée directement à la borne d'alimentation et une autre électrode apte à délivrer une tension de contrôle sur l'électrode de commande du premier transistor, de façon à limiter la valeur du courant ( $I_{T2}$ ) traversant ledit premier transistor (T2) au cours de l'état transitionnel, de manière à réguler le temps de montée du signal de changement d'état.

- 6. Dispositif selon la revendication 5, dans lequel le temps de montée du signal de changement d'état est compris dans un intervalle s'étendant de 70 ns à 150 ns.

- **7.** Dispositif selon l'une des revendications 5 6, dans lequel ledit transistor de contrôle comprend :

- une électrode de commande apte à recevoir ledit signal de commande de changement d'état, et

- une première électrode connectée à l'électrode de commande du premier transistor et apte à délivrer une tension de contrôle ( $V_G$ ) ayant une transition depuis un état bas vers un état haut avec un temps de montée équivalent au temps de montée du signal de changement d'état.

- 8. Dispositif selon la revendication 7, dans lequel le moyen de contrôle comprend en outre une résistance de contrôle (R) connectée entre la borne d'alimentation et une deuxième électrode du transistor de contrôle, la valeur de laquelle étant déterminée en fonction du temps de montée du signal de changement d'état.

- 9. Dispositif selon la revendication 8, dans lequel la résistance de contrôle à une valeur de l'ordre de quelques dizaines de  $k\Omega$ .

- 10. Ecran à plasma, comprenant un écran à plasma matriciel et un dispositif de commande selon l'une des revendications 5 à 9.

7

55

40

45

Fig.1

Fig.2

Fig.3

Fig.4

Fig.5

Fig.7

# Office européen RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande EP 07 29 0067

| DO                   | CUMENTS CONSIDER                                                                                                                             | ES COMME PERTINENTS                   |                                                                                |                                   |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------|-----------------------------------|

| atégorie             | Citation du document avec i<br>des parties pertin                                                                                            | ndication, en cas de besoin,<br>entes | Revendication concernée                                                        | CLASSEMENT DE LA<br>DEMANDE (IPC) |

| X,D                  | WO 02/41292 A (STMI<br>MAS, CELINE; TROUSS<br>ERIC) 23 mai 2002 (<br>* page 7, ligne 20<br>1,3,4 *                                           | EL, GILLES; BENOIT,<br>2002-05-23)    | 1-10                                                                           | INV.<br>G09G3/28                  |

| Т                    | HOROWITZ, PAUL; HIL<br>of electronics"<br>1989, CAMBRIDGE UN<br>XP002400356<br>* page 72, alinéa 2                                           | •                                     | 8                                                                              |                                   |

| A,D                  | WO 02/15163 A (STMI<br>TROUSSEL, GILLES; M<br>ERIC) 21 février 20<br>* figure 5 *                                                            | AS, CELINE; BENOIT,                   | 1-10                                                                           |                                   |

|                      |                                                                                                                                              |                                       |                                                                                | DOMAINES TECHNIQUES               |

|                      |                                                                                                                                              |                                       |                                                                                | GO9G                              |

|                      |                                                                                                                                              |                                       |                                                                                |                                   |

| Le pre               | ésent rapport a été établi pour tou                                                                                                          | tes les revendications                |                                                                                |                                   |

|                      | Lieu de la recherche                                                                                                                         | Date d'achèvement de la recherche     |                                                                                | Examinateur                       |

| X : part<br>Y : part | Munich  ATEGORIE DES DOCUMENTS CITES iculièrement pertinent à lui seul iculièrement pertinent en combinaison e document de la même catégorie | E : document de b<br>date de dépôt d  | pipe à la base de l'ir<br>prevet antérieur, ma<br>ou après cette date<br>mande |                                   |

EPO FORM 1503 03.82 (P04C02)

### ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

EP 07 29 0067

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de Les dieserties au minées et minées de la fairnir de de la fairnir de de l'office européenne visé ci-dessus.

Les dits members sont contenus au fichier informatique de l'Office européen des brevets à la date du

Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

19-03-2007

|                |                                                 |   |                     |                      |                                                           | ,                                                    |

|----------------|-------------------------------------------------|---|---------------------|----------------------|-----------------------------------------------------------|------------------------------------------------------|

|                | Document brevet cité<br>au rapport de recherche |   | Date de publication |                      | Membre(s) de la<br>famille de brevet(s)                   | Date de<br>publication                               |

|                | WO 0241292                                      | Α | 23-05-2002          | EP<br>FR<br>JP<br>US | 1342228 A1<br>2816746 A1<br>2004514177 T<br>2003107327 A1 | 10-09-2003<br>17-05-2002<br>13-05-2004<br>12-06-2003 |

|                | WO 0215163                                      | Α | 21-02-2002          | EP<br>FR<br>US       | 1307874 A1<br>2812963 A1<br>2003057852 A1                 | 07-05-2003<br>15-02-2002<br>27-03-2003               |

|                |                                                 |   |                     |                      |                                                           |                                                      |

|                |                                                 |   |                     |                      |                                                           |                                                      |

|                |                                                 |   |                     |                      |                                                           |                                                      |

|                |                                                 |   |                     |                      |                                                           |                                                      |

|                |                                                 |   |                     |                      |                                                           |                                                      |

|                |                                                 |   |                     |                      |                                                           |                                                      |

|                |                                                 |   |                     |                      |                                                           |                                                      |

|                |                                                 |   |                     |                      |                                                           |                                                      |

| M P0460        |                                                 |   |                     |                      |                                                           |                                                      |

| EPO FORM P0460 |                                                 |   |                     |                      |                                                           |                                                      |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82

15

### EP 1 811 491 A1

### RÉFÉRENCES CITÉES DANS LA DESCRIPTION

Cette liste de références citées par le demandeur vise uniquement à aider le lecteur et ne fait pas partie du document de brevet européen. Même si le plus grand soin a été accordé à sa conception, des erreurs ou des omissions ne peuvent être exclues et l'OEB décline toute responsabilité à cet égard.

### Documents brevets cités dans la description

• WO 0215163 A [0006]

• WO 0241292 A [0014]