(11)

**EP 1 811 714 A8**

(12)

## KORRIGIERTE EUROPÄISCHE PATENTANMELDUNG

Hinweis: Bibliographie entspricht dem neuesten Stand

(15) Korrekturinformation:

**Korrigierte Fassung Nr. 1 (W1 A1)**

Bibliographie INID code(s) 54

(51) Int Cl.:

**H04L 7/033 (2006.01)**

(48) Corrigendum ausgegeben am:

**26.09.2007 Patentblatt 2007/39**

(43) Veröffentlichungstag:

**25.07.2007 Patentblatt 2007/30**

(21) Anmeldenummer: **06026973.5**

(22) Anmeldetag: **28.12.2006**

(84) Benannte Vertragsstaaten:

**AT BE BG CH CY CZ DE DK EE ES FI FR GB GR

HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI

SK TR**

Benannte Erstreckungsstaaten:

**AL BA HR MK YU**

(30) Priorität: **23.01.2006 DE 102006003281**

(71) Anmelder: **Micronas GmbH

79108 Freiburg (DE)**

(72) Erfinder: **Ritter, Joachim

79540 Lorräch (DE)**

(74) Vertreter: **Patentanwälte

Westphal, Mussgnug & Partner

Am Riettor 5

78048 Villingen-Schwenningen (DE)**

### (54) Integrierte Schaltung für eine asynchrone, serielle Datenübertragung mit einem Bitlängen Zähler

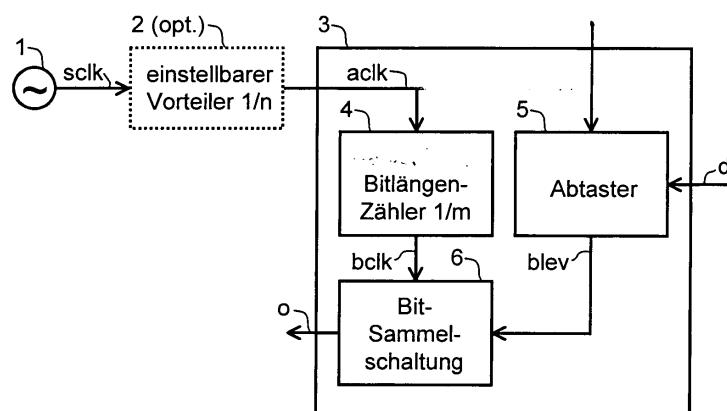

(57) Die Erfindung bezieht sich auf, eine integrierte Schaltung (7) für eine asynchrone, serielle Datenübertragung mit Strukturen zum Ausbilden

- eines Eingangsanschlusses (30) zum Anlegen asynchroner, serieller Daten (d),

- eines Abtasters (5) zum Abtasten der asynchronen, seriellen Daten (d) mittels eines daran anliegenden Abstakttes (aclk) und

- eines Bitlängen-Zählers (4) zum Bestimmen einer Bitdauer durch Zählen einer Anzahl (m) von Takten des Abstakttes (aclk) oder eines Bitlängen-Zähltaktes (xclk),

wobei

- ein Bitlängenanschluss (32) zum variablen Einstellen der Anzahl (m) der Takte des Bitlängen-Zählers (4) an der integrierten Schaltung (7) und/oder am Bitlängen-Zähler (4) ausgebildet ist.

**Fig. 1**