# (11) EP 1 845 508 A1

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

17.10.2007 Bulletin 2007/42

(51) Int Cl.:

G09G 3/20 (2006.01)

G09G 3/32 (2006.01)

(21) Application number: 06112633.0

(22) Date of filing: 13.04.2006

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI SK TR

**Designated Extension States:**

AL BA HR MK YU

(71) Applicant: Toppoly Optoelectronics Corp. Chu-Nan 350, Miao-Li County (TW) (72) Inventor: Lin, Ching-Wei 330 Taoyuan County (TW)

(74) Representative: Patentanwälte Kewitz & Kollegen Partnerschaft,

Corneliusstrasse 18 60325 Frankfurt a.M. (DE)

## (54) System and method of providing driving voltages to an RGBW display panel

(57) A representative system comprises a data driver with a reference voltage generation circuit that is operative to provide reference voltages according to a white component signal (W) extracted from three color input

signals (R,G,B), and a digital-to-analog (D/A) conversion unit that is operative to generate driving voltages according to the reference voltages, the three color input signals and the white component signal.

EP 1 845 508 A1

20

25

30

35

40

45

#### **BACKGROUND**

**[0001]** The invention relates to panel displays, and more particularly, to systems and methods for providing driving voltages to RGBW display panels.

1

[0002] Color image display devices are well known and are based upon a variety of technologies such as cathode ray tubes, liquid crystal modulators and solid-state light emitters such as Organic Light Emitting Diodes (OLEDs). In a common OLED color image display device, a pixel includes red, green and blue colored subpixels. These light emitting colored subpixels define a color gamut, and by additively combining the illumination from each of these three subpixels, i.e. with the integrative capabilities of the human visual system, a wide variety of colors can be achieved. OLEDs may be used to generate color directly using organic materials to emit energy in desired portions of the electromagnetic spectrum, or alternatively, broadband emitting (apparently white) OLEDs may be attenuated with color filters to achieve red, green and blue output.

**[0003]** Images and data displayed on a color display device are typically stored and/or transmitted in three channels, that is, having these signals corresponding to a standard (e.g. RGB). It is also important to recognize that data typically is sampled to assume a particular spatial arrangement of light emitting elements. In an OLED display device, these light emitting elements are typically arranged side by side on a plane. Therefore, if incoming data is sampled for display on a color display device, the data will also be resampled for display on an OLED display having four subpixels per pixel rather than the three subpixels used in a three channel display device.

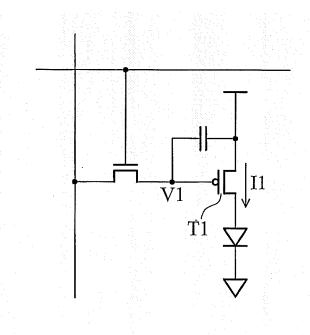

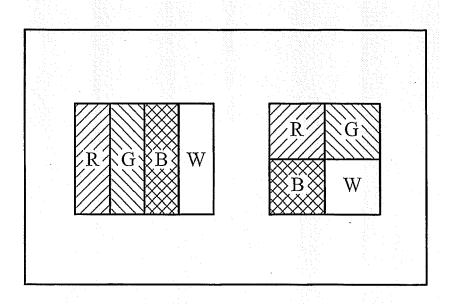

**[0004]** In this regard, Fig. 1A shows a conventional OLED subpixel driving circuit structure, and Fig. 1B shows RGBW subpixel arrangements of a conventional display panel. As shown in Fig. 1A, the subpixel is driven by the current 11 through the driving transistor T1. The driving transistor T1 outputs the current 11 according to the voltage V1.

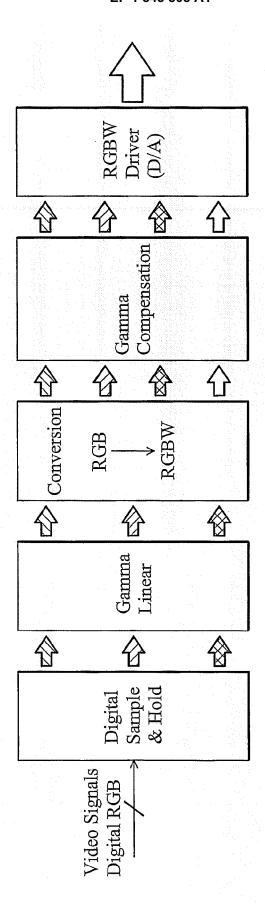

[0005] Fig. 1C shows a conventional digital signal processing (DSP) structure for driving RGBW subpixels. As shown in Fig. 1C, RGB digital signals are sampled and held and output to a Gamma linear control unit. The Gamma linear control unit adjusts RGB digital signals for Gamma linearity and outputs to the conversion unit. The conversion unit converts the adjusted RGB digital signals to RGBW digital signals and outputs to a Gamma compensation unit. The Gamma compensation unit executes a Gamma compensation of the RGBW digital signals from the conversion unit for Gamma correction and outputs to a RGBW driver. The RGBW driver converts the RGBW digital signals to RGBW analog signals to drive corresponding RGBW subpixels.

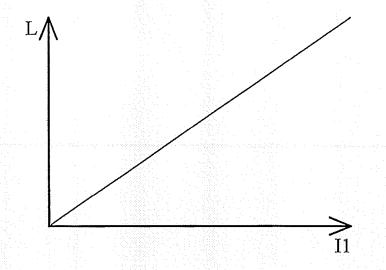

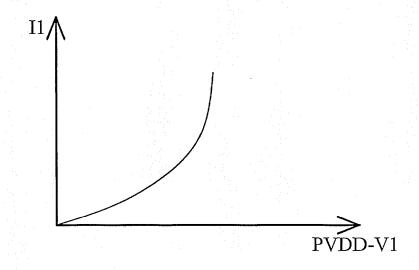

[0006] Fig. 2A shows the relationship between the luminance of the OLED subpixel and the current I1. As

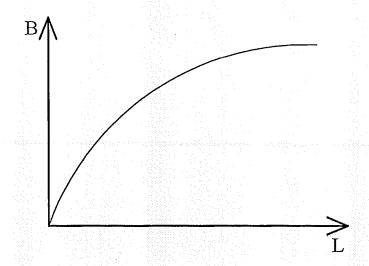

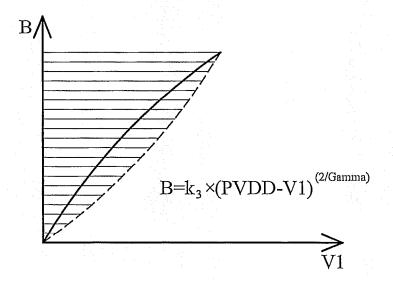

shown, there is a linear relationship between the luminance of the OLED subpixel and the current I1. Fig. 2B shows the relationship between the current I1 of the driving transistor T1 and the voltage V1 to be non-linear. Fig. 2C shows the relationship between luminance of the OLED subpixel and observable brightness (gamma). Fig. 2D shows the relationship between observable brightness and voltage V1 applied to the driving transistor T1. [0007] Thus, a gamma correction is required to compensate the non-linear relationship.

[0008] Conventionally, RGB data is converted to RG-BW data through digital data processing (DSP). However, due to different optical characteristics (gamma correction) for each RGBW color, DSP typically requires a complicated algorithm to execute such conversion. Further, it may be difficult to obtain a precise analog output corresponding to the gamma correction for each color after using the complicated conversion algorithm.

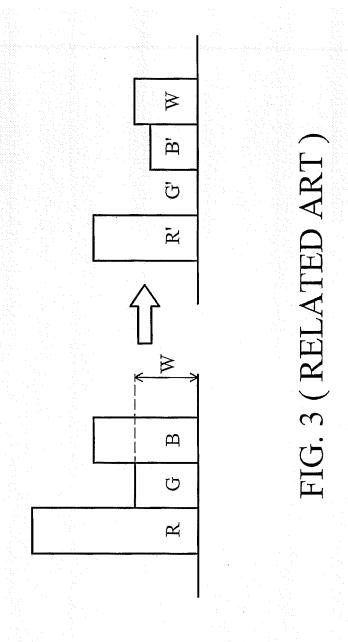

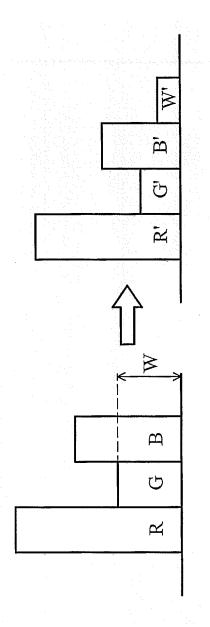

[0009] For example, Fig. 3 shows a conventional method for converting RGB data to RGBW data. As shown in Fig. 3, the Min(R,G,B) is assumed to be W data, and R'G'B' data (driving the display device) can be obtained by removing the W component from the R,G,B components respectively. Fig. 4 shows another conventional method for converting RGB data to RGBW data. As shown in Fig. 4, the Min(R,G,B) is assumed to be W data, and the W component is converted to W' data in accordance with a characteristic of  $\alpha$ \*W, where  $\alpha$  < 1. The R'G'B' data are obtained by removing the W' component from the RGB components respectively. However, these two simple methods typically cannot precisely provide gamma correction for each color because of the non-linear relationship between driving voltage and observable brightness.

### **SUMMARY**

**[0010]** Systems and method for providing driving voltages of RGBW display panels are disclosed. An exemplary embodiment of such a system comprises a data driver with a reference voltage generation circuit providing reference voltages according to a white component signal (W) extracted from three color input signals (R,G,B), and a digital-to-analog (D/A) conversion unit to generate driving voltages according to the reference voltages, the three color input signals and the white component signal.

**[0011]** An exemplary embodiment of a method for providing driving voltages of a RGBW display panel, comprises generating reference voltages according to a white component signal (W) extracted from three color input signals (R,G,B); and generating driving voltages according to the reference voltages, the three color input signals and the white component signal.

### **DESCRIPTION OF THE DRAWINGS**

[0012] The invention can be more fully understood by

55

the subsequent detailed description and examples with reference made to the accompanying drawings, wherein:

Fig. 1A shows a conventional OLED subpixel driving circuit structure;

Fig. 1B shows RGBW pixel arrangements of conventional display panel;

Fig. 1C shows a conventional digital signal processing (DSP) structure for driving RGBW pixels;

Fig. 2A shows the relationship between the luminance of OLED and current;

Fig. 2B shows the relationship between current through the control transistor and driving voltage thereof:

Fig. 2C shows the relationship between luminance of the OLED and observable brightness;

Fig. 2D shows the relationship between observable brightness and driving voltage of driving transistor; Fig. 3 shows a conventional method for converting RGB data to RGBW data;

Fig. 4 shows another conventional method for converting RGB data to RGBW data;

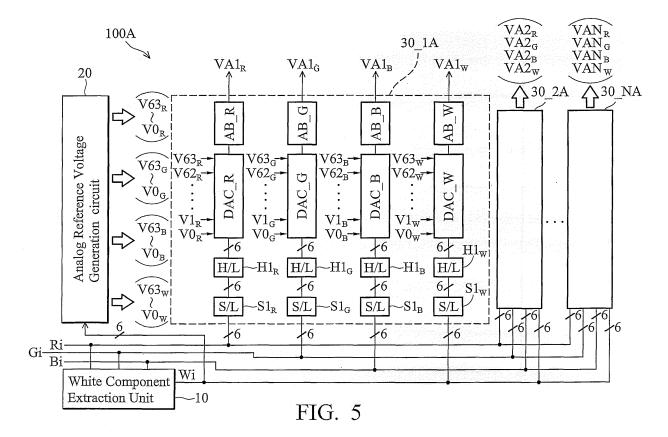

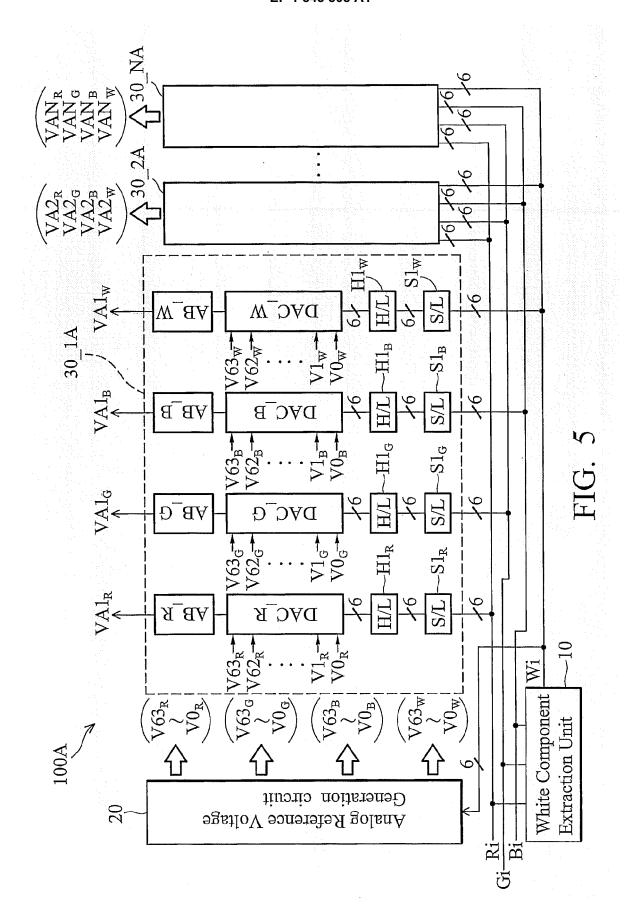

Fig. 5 shows an embodiment of a data driver;

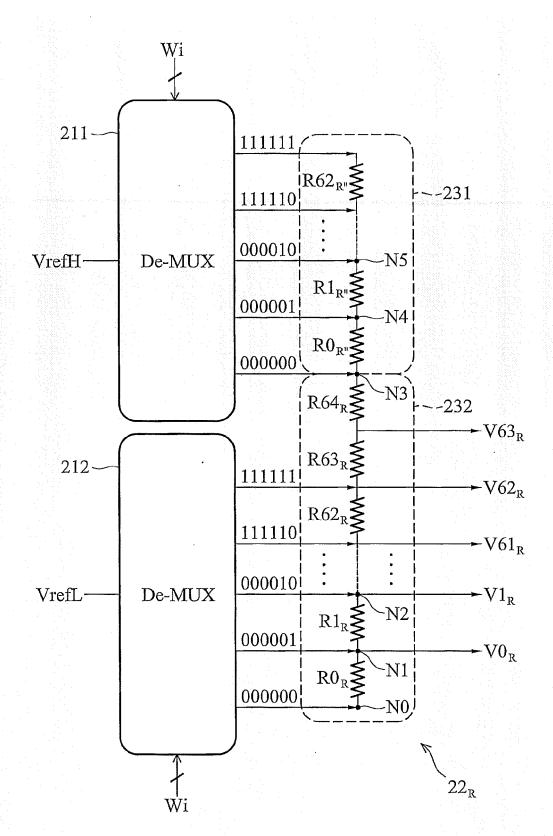

Figs. 6A~6D show embodiments of a voltage generator;

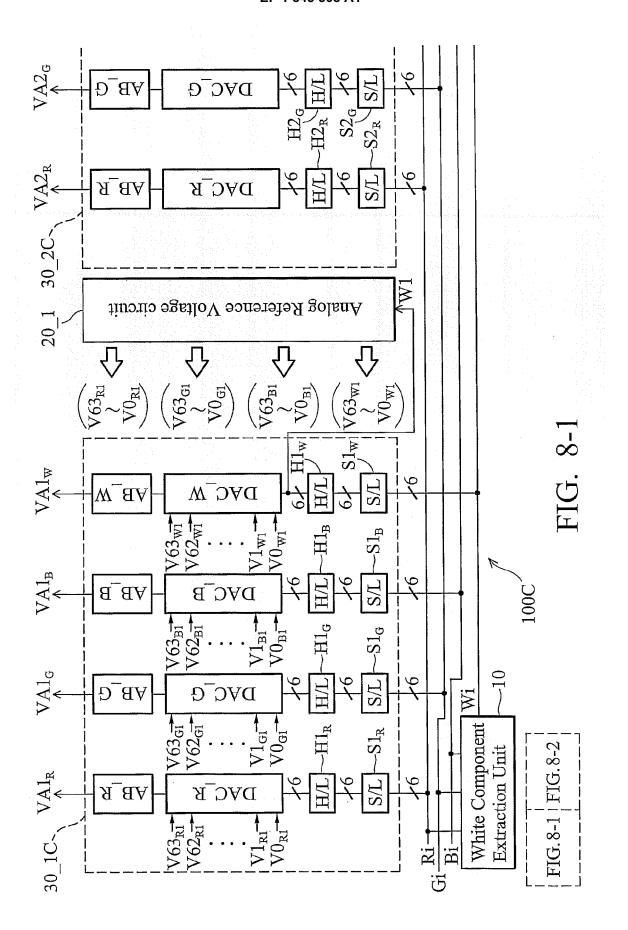

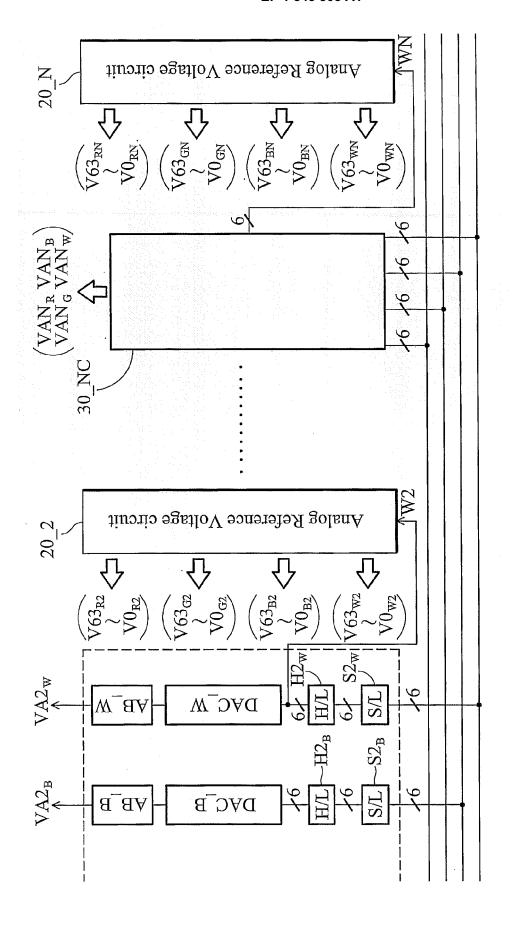

Fig. 7 shows another embodiment of a data driver; Figs. 8-1 and 8-2 show another embodiment of a data driver;

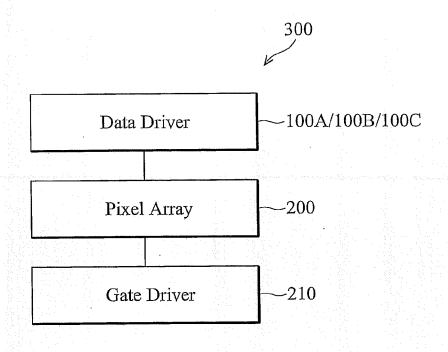

Fig. 9 is a schematic diagram of an embodiment of a display; and

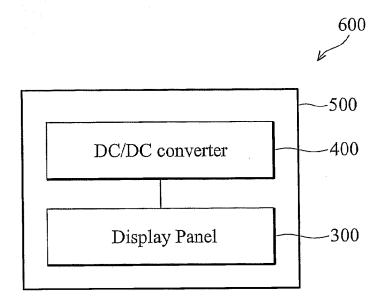

Fig. 10 is a schematic diagram of an embodiment of an electronic device employing the display panel shown in Fig. 9.

### **DETAILED DESCRIPTION**

[0013] Systems for providing driving voltages to display panels will now be described with reference to several exemplary embodiments. In this regard, an embodiment of a system providing driving voltages to an RGBW display panel is depicted in Fig. 5. As shown in Fig. 5, data driver 100A comprises a white component extraction unit 10, an analog reference voltage generation circuit 20 and N digital-to-analog (D/A) conversion units 30\_1A~30\_NA.

**[0014]** The white component extraction unit 10 extracts a white component signal Wi from three color input signals Ri, Gi and Bi. For example, three color input signals Ri, Gi and Bi can be 6 bit digital data, and the white component extraction unit 10 can be a minimum value detector. If color input signals R1, G1 and B1 are 110111, 010111 and 000111 respectively, the white component signal W1 can be 000111. Alternately, white component extraction unit 10 can output a suppressed white component signal W1 of 000011 according to the color input signal R1, G1 and B1.

[0015] Alternately, the white component signal Wi can

be obtained by executing an AND logic operation to the three color input signals Ri, Gi and Bi. For example, when the color input signals R1, G1 and B1 are 110111, 010111 and 000111 respectively, the white component signal W1 can be 000111.

[0016] Conversely, the white component signal Wi can be obtained by executing an AND logic operation to M bits of the three color input signals Ri, Gi, Bi, and 0 < M < 6. For example, when M=2, a suppressed white component signal W1 of 000011 can be obtained according to the color input signal R1, G1 and B1.

**[0017]** The analog reference voltage generation circuit 20 generates four sets of reference voltages  $V0_R \sim V63_R$ ,  $V0_G \sim V63_G$ ,  $V0_B \sim V63_B$  and  $V0_W \sim V63_W$  for color input signal Ri, Gi and Bi and the white component signal Wi respectively, the reference voltages  $V0_R \sim V63_R$ ,  $V0_G \sim V63_G$  and  $V0_B \sim V63_B$  are generated according to the white component signal Wi.

[0018] The D/A conversion units 30\_1A~30\_NA receive the reference voltages V0<sub>R</sub>~V63<sub>R</sub>, V0<sub>G</sub>~V63<sub>G</sub>, V0<sub>B</sub>~V63<sub>B</sub> and V0<sub>W</sub>~V63<sub>W</sub> from the analog reference voltage generation circuit 20 to generate corresponding voltages VA1<sub>R</sub>~VAN<sub>R</sub>, VA1<sub>G</sub>~VAN<sub>G</sub>, VA1<sub>B</sub>~VAN<sub>B</sub> and VA1<sub>W</sub>~VAN<sub>W</sub> according to the three color input signals Ri, Gi and Bi and the white component signal Wi. For example, the D/A conversion unit 30\_1A receives the reference voltages V0<sub>R</sub>~V63<sub>R</sub>, V0<sub>G</sub>~V63<sub>G</sub>, V0<sub>B</sub>~V63<sub>B</sub> and V0<sub>W</sub>~V63<sub>W</sub> and generates corresponding driving voltages  $VA1_R$ ,  $VA1_G$ ,  $VA1_B$  and  $VA1_W$  according to the three color input signals R1, G1 and B1 and the white component signal W1 during a first period. The D/A conversion unit 30\_2A receives the reference voltages  $V0_R$ ~ $V63_R$ ,  $V0_G$ ~ $V63_G$ ,  $V0_B$ ~ $V63_B$  and V0<sub>W</sub>~V63<sub>W</sub> and generates corresponding driving voltages VA2<sub>R</sub>, VA2<sub>G</sub>, VA2<sub>B</sub> and VA2<sub>W</sub> according to the three color input signals R2, G2 and B2 and the white component signal W2 during a second period, and so on. Namely, all D/A conversion units 30 1A~30 NA employ the same type of analog reference voltage circuit which can generate different reference voltages V0<sub>R</sub>~V63<sub>R</sub>, V0<sub>G</sub>~V63<sub>G</sub>, V0<sub>B</sub>~V63<sub>B</sub> and V0<sub>W</sub>~V63<sub>W</sub> according to different white component signals Wi during different peri-

[0019] The D/A conversion units  $30\_1A\sim30\_NA$  each comprise four sampling latches  $S1_R\sim S1_W$ , four holding latches  $H1_R\sim H1_W$ , four D/A converters DAC\_R~DAC\_W and four analog buffers AB\_R~AB\_W. The sampling latches  $S1_R\sim S1_W$  sample the color input signals Ri, Gi and Bi and the white component signal Wi at one time. The holding latches  $H1_R\sim H1_W$  hold the color input signals Ri, Gi and Bi and the white component signal Wi sampled by the sampling latches  $S1_R\sim S1_W$ . The D/A converters DAC\_R~DAC\_W convert the held color input signals Ri, Gi and Bi and the held white component signal Wi to corresponding analog voltages  $VA1_R\sim VA1_W$  according to the reference voltages  $V0_R\sim V63_R$ ,  $V0_G\sim V63_G$ ,  $V0_B\sim V63_B$  and  $V0_W\sim V63_W$ , and output the corresponding driving voltages  $VA1_R\sim VA1_W$  through the analog buff-

ers AB\_R~AB\_W. Operation and structure of the D/A conversion units 30\_2A~30\_NA are similar to those of the D/A conversion unit 30\_1A. In this embodiment, the data diver 100A can output four corresponding voltages to drive four data lines at one time.

[0020] The analog reference voltage generation circuit 20 comprises four voltage generators 22R, 22G, 22B and 22W shown in Figs. 6A~6D to generate reference volt- $V0_{R} \sim V63_{R}$ ,  $V0_{G} \sim V63_{G}$ , V0<sub>B</sub>~V63<sub>B</sub> V0<sub>W</sub>~V63<sub>W</sub>. As shown in Fig. 6A, the voltage generator 22R generates the reference voltages V0<sub>R</sub>~V63<sub>R</sub> to D/A converters DAC\_R of the D/A conversion units 30\_1A~30\_NA according to the white component signal Wi. The voltage generator 22R comprises two de-multiplexers 211 and 212 and two series-connected resistor strings 231 and 232. The resistor string 231 comprises resistors R0<sub>R"</sub>~R62<sub>R"</sub> connected in series, and the resistor string 232 comprises resistors R0<sub>R</sub>~R64<sub>R</sub> for red color grey level gamma correction. The de-multiplexer 211 selectively outputs a first power voltage VerfH to one node of the resistor string 231 according to the white component signals Wi, and the de-multiplexer 212 selectively outputs a second power voltage VrefL to one node of the resistor string 232 according to the white component signals Wi. The first power voltage VrefH exceeds the second power voltage VrefL, the resistors R0<sub>R"</sub> and R0<sub>R</sub> are the same, the resistors R1<sub>R"</sub> and R1<sub>R</sub> are the same, the resistors  $R2_{R''}$  and  $R2_R$  are the same, and so on.

[0021] For example, if the white component signal Wi extracted from the three color input signals Ri, Gi and Bi is 000000, the power voltage VrefL is forced to the node N0 of the resistor string 232, and the power voltage VrefH is forced to the node N3 of the resistor string 231. Alternately, if the white component signal Wi extracted from the three color input signals Ri, Gi and Bi is 000001, the power voltage VrefL is forced to the node N1 of the resistor string 232, and the power voltage VrefH is forced to the node N4 of the resistor string 231. Accordingly, the voltage level of the reference voltage V0<sub>R</sub>~V63<sub>R</sub> for the red input signal Ri can be lowered by a first voltage drop. [0022] Alternately, if the white component signal Wi extracted from the three color input signals Ri, Gi and Bi is 000010, the power voltage VrefL is forced to the node N2 of the resistor string 232, and the power voltage VrefH is forced to the node N5 of the resistor string 231. Accordingly, the voltage level of the reference voltage V0<sub>R</sub>~V63<sub>R</sub> for the red input signal Ri can be lowered by a second voltage drop exceeding the first voltage drop. Thus, the voltage level of the reference voltage V0<sub>R</sub>~V63<sub>R</sub> for the red input signal Ri can be adjusted based on the white component signal Wi.

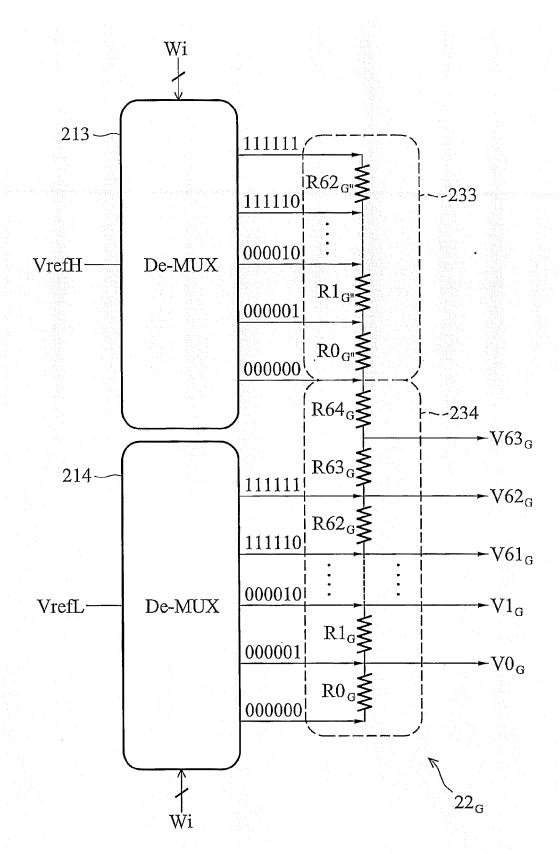

[0023] As shown in Fig. 6B, the voltage generator 22G generates the reference voltages V0<sub>G</sub>~V63<sub>G</sub> to D/A converters DAC\_G of the D/A conversion units 30\_1A~30\_NA according to the white component signal Wi. The voltage generator 22R comprises two de-multiplexers 213 and 214 and two series-connected resistor strings 233 and 234. The resistor string 233 comprises

resistors R0<sub>G"</sub>~R62<sub>G"</sub> connected in series, and the resistor string 234 comprises resistors R0<sub>G</sub>~R64<sub>G</sub> for green color grey level gamma correction. The de-multiplexer 213 selectively outputs the first power voltage VrefH to one node of the resistor string 233, and the de-multiplexer 214 selectively outputs the second power voltage VrefL to one node of the resistor string 234. The resistors R0<sub>G"</sub> and R0<sub>G</sub> are the same, the resistors R1<sub>G"</sub> and R1<sub>G</sub> are the same, the resistors R2<sub>G"</sub> and R2<sub>G</sub> are the same, and so on.

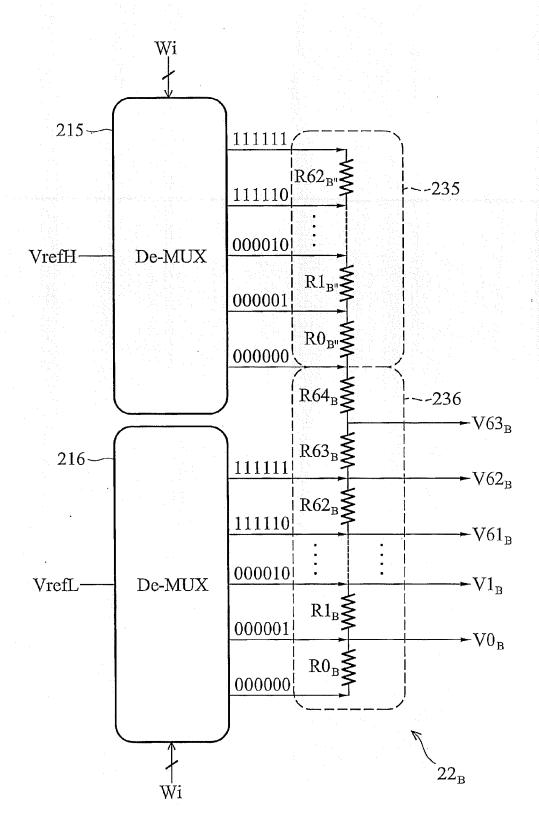

[0024] As shown in Fig. 6C, the voltage generator 22B generates the reference voltages V0<sub>B</sub>~V63<sub>B</sub> to D/A converters DAC\_B of the D/A conversion units 30 1A~30 NA according to the white component signal Wi. The voltage generator 22B comprises two de-multiplexers 215 and 216 and two series-connected resistor strings 235 and 236. The resistor string 235 comprises resistors R0<sub>B"</sub>~R62<sub>B"</sub> connected in series, and the resistor string 236 comprises resistors R0<sub>B</sub>~R64<sub>B</sub> for blue color grey level gamma correction. The de-multiplexer 215 selectively outputs the first power voltage VrefH to one node of the resistor string 235, and the de-multiplexer 216 selectively outputs the second power voltage VrefL to one node of the resistor string 236. The resistors RO<sub>R"</sub> and R0<sub>B</sub> are the same, the resistors R1<sub>B"</sub> and R1<sub>B</sub> are the same, the resistors R2<sub>B"</sub> and R2<sub>B</sub> are the same, and so on. Operation of the voltage generator 22G and 22B is similar to that of the voltage generator 22R., . The resistors  $R0_R \sim R64_R$ ,  $R0_G \sim R64_G$  and  $R0_B \sim R62_B$  can be different from others, depending on design.

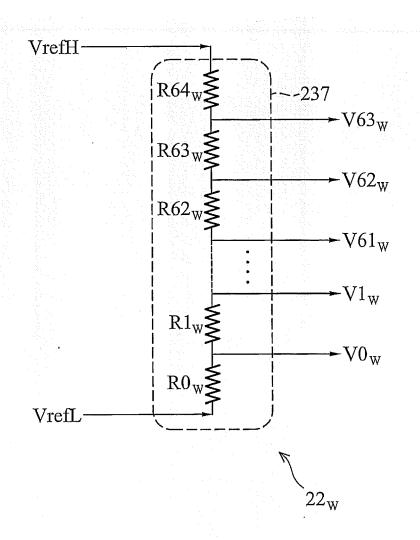

**[0025]** As shown in Fig. 6D, the voltage generator 22W comprises a resistor string 237 comprising a plurality of resistors  $R0_W \sim R63_W$  connected in series for white color grey level gamma correction. The power voltages VrefH and VrefL are forced to two ends of the resistor string 237, such that the reference voltages  $V0_W \sim V63_W$  are generated according to difference resistances of the resistors  $R0_W \sim R63_W$ .

[0026] In this embodiment, the voltage level of the ref-V0R~V63R, V0G~V63G erence voltages V0B~V63B for three color input signals Ri, Gi and Bi can be adjusted based on the white component signal Wi. The lower voltage level of the reference voltages  $V0_R$   $\sim$   $V63_R$ ,  $V0_G$   $\sim$   $V63_G$  and  $V0_B$   $\sim$   $V63_B$ , the lower driving voltage  $VA1_R$ - $VAN_R$ ,  $VA1_G$ - $VAN_G$  and  $VA1_B$ - $VAN_B$ generated by D/A conversion units 30\_1A~30\_NA. Namely, the voltage level of the driving voltages VA1<sub>R</sub>~VAN<sub>R</sub>, VA1<sub>G</sub>~VAN<sub>G</sub> and VA1<sub>B</sub>~VAN<sub>B</sub> generated by D/A conversion units 30\_1A~30\_NA can be adjusted according to the extracted white component signal Wi. When N-type transistors are used as driving devices of pixels, the RGB brightness of the subpixels on a display device is lowered as the driving voltage decreases based on the white component signal Wi. In some embodiments, when P-type transistors are used as driving devices of pixels, the RGB brightness of the pixels on a display device is lowered as the driving voltage increases based on the white component signal Wi. Thus, gamma

20

40

correction for RGBW brightness can be accurately controlled

[0027] Alternately, in some embodiments, the de-multiplexers 211, 213 and 215 selectively output the second power voltage VrefL to one node of the resistor string 231, 233 and 235, and the de-multiplexer 212, 214 and 216 selectively output the first power voltage VrefH to one node of the resistor string 232, 234 and 236.

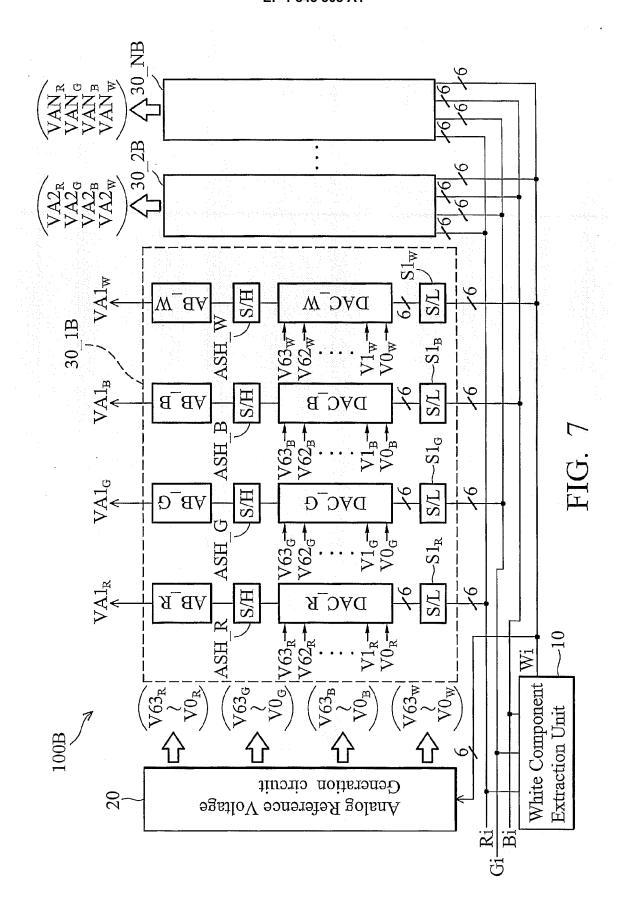

[0028] Fig. 7 shows another embodiment of a data driver. As shown, the data driver 100B is similar to the data driver 100A shown in Fig. 5, with the exception of analog sampling and holding latches ASH\_R~ASH\_W coupled between the analog buffers AB\_R~AB\_W and the D/A converters DAC\_R~DAC\_W in each D/A conversion unit  $30\_1B~30\_NB$ . Description of the same structure shown in Fig. 5 is omitted for simplification. In the data driver 100B, the driving voltages  $VA1_R~VAN_R$ ,  $VA1_G~VAN_G$ ,  $VA1_B~VAN_B$  and  $VA1_W~VAN_W$  generated by the D/A conversion units  $30\_1B~30\_NB$  during different periods can be sampled and held by the analog sampling and holding latches ASH\_R~ASH\_W. Thus, the data driver 100B can output the corresponding voltages to drive one row of data lines in one time.

[0029] Figs. 8-1 and 8-2 show another embodiment of a data driver. As shown, the data driver 100C is similar to the data driver 100A shown in Fig. 5, with the exception of N analog reference voltage generation circuits 20\_1~20\_N coupled to the D/A conversion units 30\_1C~30\_NC. Description of the same structure shown in Fig. 7 is omitted for simplification. In the data driver 100C, the N analog reference voltage generation circuits 20\_1~20\_N each correspond to one of the D/A conversion units 30\_1C~30\_NC. For example, the analog reference voltage generation circuit 20\_1 corresponds to the D/A conversion unit 30\_1C, the analog reference voltage generation circuit 20\_2 corresponds to the D/A conversion unit 30\_2C, and so on. The color input signals Ri, Gi, Bi and the extracted white component signal Wi are sampled by the sampling latches  $S1_R$   $\sim$   $S1_W$  and held by the holding latches  $\mathrm{H1}_{\mathrm{R}}\text{\sim}\mathrm{H1}_{\mathrm{W}}$  in the D/A conversion units 30\_1C~30\_NC during each period. For example, the color input signals R1, G1, B1 and the extracted white component signal W1 are sampled and held in the D/A conversion units 30\_1C during a first period, the color input signals R2, G2, B2 and the extracted white component signal W2 are sampled and held in the D/A conversion units 30\_2C during a second period, and so on. [0030] All held color input signals Ri, Gi, Bi and the white component signal Wi can be output to the corresponding D/A converters DAC\_R~DAC\_W and the corresponding analog reference voltage circuit at one time. For example, the white component signal W1 is output to analog reference voltage generation circuit 20\_1, such that the reference voltages V0<sub>R</sub>~V63<sub>R</sub>, V0<sub>G</sub>~V63<sub>G</sub>,  $V0_B$  ~  $V63_B$  and  $V0_W$  ~  $V63_W$  are output to the D/A converters DAC\_R~DAC\_W. Accordingly, the D/A converters DAC\_R~DAC\_W receive the reference voltages  $V0_R$ - $V63_R$ ,  $V0_G$ - $V63_G$ ,  $V0_B$ - $V63_B$  and  $V0_W$ - $V63_W$  and

generate the driving voltage  $VA1_R \sim VA1_W$  according to the three color input signals R1, G1, B1 and W1. Similarly, the D/A conversion units  $30\_2C \sim 30\_NC$  generate the driving voltages  $VA2_R \sim VAN_R$ ,  $VA2_G \sim VAN_G$  and  $VA2_B \sim VAN_B$  at the same time. Namely, the data driver 100C can output the corresponding voltages to drive one row of data lines in one time.

[0031] Fig. 9 is a schematic diagram of another embodiment of a system, in this case a display panel, for providing driving voltages. As shown in Fig. 9, the display device 300 comprises a data driver such as data drvier100A/100B/100C, a pixel array 200 and a gate driver 210. The pixel array 200 comprises RGBW color pixels arranged in matrix, a plurality of data lines and a plurality of scan lines. The data driver generates analog driving voltages to the pixel array 200, and the gate driver 210 provides scan signals to the pixel array 200 such that the scan lines are asserted or de-asserted. The pixel array 200 generates color images according to the analog driving voltages from the data driver. While the display panel can be an organic light emitting panel, an electroluminescent panel or a liquid crystal display panel for example, various other technologies can be used in other embodiments.

**[0032]** Fig. 10 schematically shows an embodiment of yet another system, in this case an electronic device for providing driving voltages. In particular, electronic device 600 employs a display panel such as display panel 600 shown in Fig. 9. The electronic device 600 may be a device such as a PDA, notebook computer, digital camera, tablet computer, cellular phone or a display monitor device, for example.

[0033] Generally, the electronic device 600 comprises a housing 500, a display panel 300 and a DC/DC converter 400, although it is to be understood that various other components can be included, such components not shown or described here for ease of illustration and description. In operation, the DC/DC converter 400 powers the display panel 300 so that the display panel 300 can display color images.

**[0034]** While the invention has been described by way of example and in terms of preferred embodiment, it is to be understood that the invention is not limited thereto. To the contrary, it is intended to cover various modifications and similar arrangements (as would be apparent to those skilled in the art). Therefore, the scope of the appended claims should be accorded the broadest interpretation so as to encompass all such modifications and similar arrangements.

## Claims

1. A system for displaying image, comprising:

a data driver comprising:

a reference voltage generation circuit oper-

55

15

30

35

45

50

55

ative to provide reference voltages according to a white component signal (W) extracted from three color input signals (R,G,B); and

a digital-to-analog (D/A) conversion unit operative to generate driving voltages according to the reference voltages, the three color input signals and the white component signal.

- 2. The system as claimed in claim 1, further comprising a white component extraction unit operative to extract the white component signal (W) from the three color input signals (R,G,B).

- 3. The system as claimed in claim 1, wherein the reference voltage generation circuit comprises first, second, third and fourth voltage generators, in which the first to third voltage generators are operative to generate the first to third sets of reference voltages according to the white component signal, and the fourth voltage generator is operative to generate the fourth set of reference voltage.

- 4. The system as claimed in claim 3, wherein the digital-to-analog conversion unit comprises first, second, third and fourth (D/A) converters operative to generate the driving voltages according to the first to fourth sets of reference voltages, the three color input signals and the white component signal.

- 5. The system as claimed in claim 4, wherein the digital-to-analog conversion unit further comprises a plurality of digital holding units coupled to the (D/A) converters and operative to hold the three color input signals and the white component signal.

- 6. The system as claimed in claim 4, wherein the digitalto-analog conversion unit further comprises a plurality of analog holding units operative to hold the driving voltages from the (D/A) converters.

- 7. The system as claimed in claim 1, further comprising a display panel comprising four color (R,G,B,W) pixels operative to generate color images according to the driving voltages.

- **8.** The system as claimed in claim 3, wherein the first to third voltage generators each comprise:

first and second resistor strings connected in series, each comprising a plurality of resistors and nodes:

first de-multiplexers coupled between the first resistor and a first power voltage; and a second de-multiplexer coupled between the second resistor string and a second power voltage, wherein, according to the white component signal, the first de-multiplexer selectively forces the first power voltage to one node of the first resistor string and the second de-multiplexer selectively forces the second power voltage to one node of the second resistor string, such that first to third sets of reference voltages are regulatable

- 9. The system as claimed in claim 8, wherein the fourth voltage generator comprises a third resistor string coupled between the first power voltage and the second power voltage.

- 10. The system as claimed in claim 8, wherein the first and second resistor strings of the first, the second and the third voltage generators exhibit different resistances.

- **11.** The system as claimed in claim 7, wherein the display panel is a liquid crystal display panel.

- **12.** The system as claimed in claim 7, wherein the display panel is an electroluminescent panel.

- 75 13. The system as claimed in claim 7, wherein the display panel is an organic light emitting panel.

- **14.** The system as claimed in claim 1, wherein the system is implemented as a PDA, a display monitor, a digital camera, a notebook computer, a tablet computer or a cellular phone.

- **15.** A method for providing driving voltages of a system for displaying images, comprising:

generating reference voltages according to a white component signal (W) extracted from three color input signals (R,G,B); and generating driving voltages according to the reference voltages, the three color input signals and the white component signal.

- **16.** The method as claimed in claim 15, further comprising extracting the white component signal (W) from the three color input signals (R,G,B).

- 17. The method as claimed in claim 16, wherein the reference voltages comprise first, second and third sets of reference voltages corresponding to the three color input signals respectively according to the white component signal, and a fourth set of reference voltages corresponding to the white component signal.

- **18.** The method as claimed in claim 17, wherein the driving voltage is generated according to the first to fourth sets of reference voltages, the three color input signals and the white component signal.

19. The method as claimed in claim 15, further comprising holding the white component signal (W) and the three color input signals (R,G,B) before generating the driving voltages.

20. The method as claimed in claim 16, wherein the white input signals (R,G,B).

component signal (W) and the three color input signals (R,G,B) each is a digital data comprising N bits, and the white component signal (W) is obtained by executing an AND logic operation to the three color

21. The method as claimed in claim 16, wherein the white component signal (W) and the three color input signals (R,G,B) each is a digital data comprising N bits, and the white component signal (W) is obtained by executing an AND logic operation to M bits of the three color input signals (R,G,B), and 0 < M < N.

22. The method as claimed in claim 15, further comprising holding the generated driving voltage.

23. The method as claimed in claim 15, wherein the system comprises a display device and the display device is an organic light emitting device, a liquid crystal display device or an electroluminescent device.

20

30

35

40

45

50

55

FIG. 1A ( RELATED ART )

FIG. 1B ( RELATED ART )

FIG. 1C (RELATED ART)

FIG. 2A ( RELATED ART )

FIG. 2B ( RELATED ART )

FIG. 2C ( RELATED ART )

FIG. 2D ( RELATED ART )

FIG. 4 (RELATED ART)

FIG. 6A

FIG. 6B

FIG. 6C

FIG. 6D

FIG. 9

FIG. 10

# **EUROPEAN SEARCH REPORT**

Application Number EP 06 11 2633

|                                                       | DOCUMENTS CONSID                                                                                                                                                                        | ERED TO BE RELEVANT                                                                                              |                                                                            |                                         |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------|--|

| Category                                              | Citation of document with ir of relevant passa                                                                                                                                          | ndication, where appropriate,<br>ages                                                                            | Relevant<br>to claim                                                       | CLASSIFICATION OF THE APPLICATION (IPC) |  |

| X                                                     | MA, MAY 24 - 27, 20<br>SYMPOSIUM, SAN JOSE                                                                                                                                              | ustable Gamma FT Circuit" NAL SYMPOSIUM. BOSTON, 105, SID INTERNATIONAL 1, CA: SID, US, 15-24), pages 1352-1355, | 1-19,22,<br>23                                                             | INV.<br>G09G3/20<br>G09G3/32            |  |

| X                                                     | EP 1 298 637 A (SAM<br>LTD) 2 April 2003 (<br>* paragraphs [0001]<br>[0053], [0057] - [                                                                                                 | , [0006], [0052],                                                                                                | 1-19,22,<br>23                                                             |                                         |  |

| 4                                                     | EP 0 547 603 A (TEX<br>INCORPORATED) 23 Ju<br>* page 2, line 42 -                                                                                                                       | ne 1993 (1993-06-23)                                                                                             | 1,15                                                                       |                                         |  |

| ,                                                     | US 2004/113875 A1 (<br>17 June 2004 (2004-<br>* paragraphs [0026]                                                                                                                       |                                                                                                                  | 1-23                                                                       | TECHNICAL FIELDS<br>SEARCHED (IPC)      |  |

| 4                                                     | US 6 593 934 B1 (LI<br>15 July 2003 (2003-<br>* figure 13 *                                                                                                                             |                                                                                                                  | 8-10                                                                       |                                         |  |

| _                                                     | The present search report has l                                                                                                                                                         | ·                                                                                                                |                                                                            |                                         |  |

|                                                       | Place of search Munich                                                                                                                                                                  | Date of completion of the search  4 August 2006                                                                  | Aur                                                                        | acher, S                                |  |

| X : parti<br>Y : parti<br>docu<br>A : tech<br>O : non | ATEGORY OF CITED DOCUMENTS cularly relevant if taken alone cularly relevant if combined with another ment of the same category nological background written disclosure mediate document | T : theory or principle<br>E : earlier patent doo<br>after the filing date                                       | underlying the ir<br>ument, but publis<br>the application<br>other reasons | ivention<br>hed on, or                  |  |

## ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 06 11 2633

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

04-08-2006

| Patent document cited in search report |            |    | Publication date | Patent family<br>member(s) |                                                             | Publication date |                                                          |

|----------------------------------------|------------|----|------------------|----------------------------|-------------------------------------------------------------|------------------|----------------------------------------------------------|

| EP                                     | 1298637    | A  | 02-04-2003       | CN<br>JP<br>KR<br>TW<br>US | 1414539<br>2003186455<br>2003027999<br>533399<br>2003058235 | A<br>A<br>B      | 30-04-20<br>04-07-20<br>08-04-20<br>21-05-20<br>27-03-20 |

| EP                                     | 0547603    | A  | 23-06-1993       | CA<br>DE<br>DE<br>JP<br>US | 2084948<br>69232507<br>69232507<br>5273673<br>5233385       | D1<br>T2<br>A    | 19-06-19<br>25-04-20<br>02-10-20<br>22-10-19<br>03-08-19 |

| US                                     | 2004113875 | A1 | 17-06-2004       | CN<br>EP<br>JP<br>WO       | 1726593<br>1573817<br>2006512732<br>2004061963              | A1<br>T          | 25-01-20<br>14-09-20<br>13-04-20<br>22-07-20             |

| US                                     | 6593934    | В1 | 15-07-2003       | NONE                       | ·                                                           |                  |                                                          |

FORM P0459

© For more details about this annex : see Official Journal of the European Patent Office, No. 12/82