# (11) EP 1 857 906 A1

(12)

## **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication:

21.11.2007 Bulletin 2007/47

(51) Int Cl.:

G05F 1/26 (2006.01)

(21) Numéro de dépôt: 07107883.6

(22) Date de dépôt: 10.05.2007

(84) Etats contractants désignés:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC MT NL PL PT RO SE SI SK TR

Etats d'extension désignés:

AL BA HR MK YU

(30) Priorité: 15.05.2006 FR 0651736

(71) Demandeur: ST MICROELECTRONICS S.A. 92120 Montrouge (FR)

(72) Inventeurs:

• Gicquel, Hugo 38000, GRENOBLE (FR)

Vogt, Lionel

12000, TEMARA (MA)

(74) Mandataire: Cabinet Plasseraud

52 rue de la Victoire

75440 Paris Cedex 09 (FR)

# (54) Régulateur de tension linéaire et procédé de limitation de courant dans un tel régulateur

(57) Un régulateur de tension linéaire (10) comprenant un circuit (11) de régulation de tension pilotant un transistor de puissance (M1) connecté à une charge (Q), comporte une boucle de limitation de courant (13) qui comprend un noeud d'entrée/sortie (O) couplé à une

électrode de commande du transistor de puissance et qui est adaptée pour, lorsqu'un courant représentant le courant passant dans le transistor de puissance est supérieur à un courant de référence, délivrer un courant de sortie (Igate) non nul et sinon ne délivrer aucun courant de sortie.

P 1 857 906 A1

# Description

20

30

35

40

45

50

55

**[0001]** La présente invention concerne les régulateurs de tension linéaires qui sont destinés à fournir une tension régulée à partir d'une tension de référence et d'une tension d'alimentation non stabilisée. Un régulateur de tension linéaire comporte généralement un élément de puissance qui opère dans sa zone de fonctionnement saturé et est connecté en série avec une charge, à laquelle il délivre une tension d'alimentation Vout stabilisée.

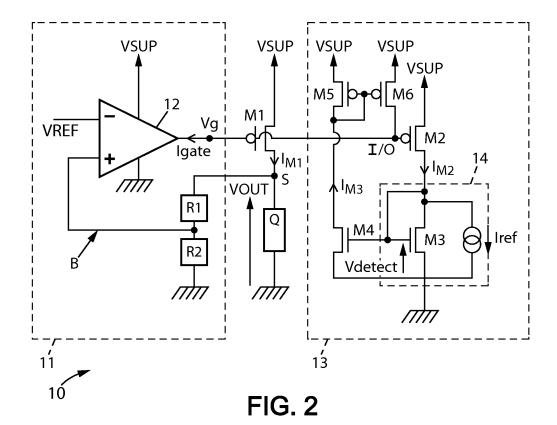

**[0002]** La figure 1 montre un exemple classique de régulateur linéaire. Un tel régulateur 1 est destiné à alimenter une charge Q. Il comporte généralement un transistor MOS de puissance, M, destiné à être connecté en série avec la charge Q. En général, le transistor M est un PMOS.

[0003] Le transistor M est commandé dans sa zone de fonctionnement saturé par un circuit de régulation AOP, par exemple basé sur un amplificateur différentiel qui pilote la tension de grille Vg appliquée au transistor M. Une première entrée, par exemple l'entrée inverseuse du circuit de régulation AOP, reçoit une tension de référence Vref et une deuxième entrée, dans le cas présent l'entrée non-inverseuse, reçoit la tension de sortie Vout (il s'agit de la tension régulée), prélevée entre le drain du transistor M et la charge Q. La tension Vref est par exemple fournie par un circuit de référence apte à délivrer une tension stable et précise. L'amplificateur AOP est généralement alimenté par une tension Vsup, par exemple fournie par une batterie.

**[0004]** La commande du transistor M est ajustée, par l'intermédiaire de la tension Vg appliquée sur sa grille par la sortie du circuit de régulation AOP, en fonction de la différence entre les valeurs reçues sur les deux entrées inverseuse et non inverseuse, de manière à garder la tension de sortie du régulateur Vout constante.

[0005] Il est utile dans les régulateurs de tension linéaires, de limiter la valeur du courant délivré par le transistor M. Ceci permet d'éviter que, lorsque le courant tiré par la charge augmente et que par conséquent la tension de sortie Vout diminue, la tension Vg de sortie de l'amplificateur opérationnel, pilotant le transistor, ne continue à baisser. En effet, la diminution de la tension Vg provoque une augmentation du courant délivré par le transistor M au-delà d'une valeur seuil risquant d'endommager la charge Q et le régulateur linéaire.

[0006] De façon classique, on dispose, comme représenté sur la figure 1, une résistance R entre la tension Vsup et la source du transistor. La tension aux bornes de la résistance R, qui est proportionnelle à la valeur du courant délivré par le transistor M, est mesurée et comparée par un circuit 3 avec un seuil de tension déterminé. Si le circuit 3 détecte que la tension mesurée est supérieure au seuil de tension, la tension de grille Vg appliquée au transistor M est modifiée afin de limiter le courant délivré par le transistor M.

[0007] Cette solution pour limiter le courant présente toutefois l'inconvénient de provoquer une chute de tension non souhaitée, et peut poser des problèmes d'intégration et de dégagement de chaleur.

[0008] Par ailleurs, il est décrit dans le document US 2004/0178778, une solution de limitation de courant ne provoquant pas une telle chute de tension indésirable. Cette solution comprend la mise en place au sein de l'amplificateur opérationnel d'un transistor, au niveau de l'étage d'entrée d'inversion, de moyens qui, à partir d'un certain niveau de courant délivré par le transistor, fixent à une valeur donnée la tension Vg de sortie de l'amplificateur AOP qui pilote le transistor, stoppant ainsi l'augmentation du courant délivré par le transistor M.

**[0009]** Cette solution présente cependant l'inconvénient d'être intégrée au sein du circuit de régulation de tension (dans le cas décrit : dans l'amplificateur). Elle convient donc uniquement aux circuits de régulation qui ont une architecture similaire à celle du document US 2004/0178778.

**[0010]** La présente invention vise à proposer une solution de limitation de courant dans un régulateur de tension linéaire ne présentant pas, ou de manière atténuée seulement, les inconvénients de l'art antérieur cités ci-dessus.

**[0011]** A cet effet, suivant un premier aspect, l'invention propose un régulateur de tension linéaire comprenant un circuit de régulation de tension et un transistor de puissance piloté par la sortie du circuit de régulation et destiné à être connecté en série à une charge à alimenter. Le régulateur comporte en outre une boucle de limitation de courant adaptée pour limiter le courant délivré dans la charge par dans le transistor de puissance.

[0012] La boucle de limitation de courant comporte un noeud d'entrée/sortie couplé à une électrode de commande du transistor de puissance. Elle est adaptée pour, lorsqu'un courant représentatif du courant délivré par le transistor de puissance est supérieur à un courant de référence, délivrer un courant de sortie non nul et pour, lorsque le courant représentatif du courant délivré par le transistor de puissance est inférieur au courant de référence, ne délivrer aucun courant de sortie.

**[0013]** Un régulateur linéaire de tension selon l'invention comporte ainsi une boucle de limitation de courant qui est dissociée du circuit de régulation de tension. Cette solution de limitation de courant peut donc être mise en oeuvre dans des régulateurs comportant des circuits de régulation d'architectures variées.

**[0014]** Dans un mode de réalisation, le circuit de régulation comporte un amplificateur de tension différentiel comprenant une sortie et une première et une seconde entrées et une boucle de régulation de tension comportant une entrée couplée à l'électrode du transistor de puissance connectée à la charge et une sortie couplée à une entrée de l'amplificateur de puissance.

[0015] Avantageusement, la boucle de limitation de courant est adaptée pour délivrer un courant dont la valeur est

#### EP 1 857 906 A1

égale à la différence entre le courant représentatif du courant délivré par le transistor de puissance et le courant de référence, multipliée par un facteur déterminé. Cette disposition permet de fixer l'intensité du courant injecté sur la liaison reliant la sortie du circuit de régulation et l'électrode de commande du transistor.

[0016] Dans un mode de réalisation, la boucle de limitation de courant comprend un second transistor monté en miroir avec le transistor de puissance et de largeur de grille plus petite que la largeur de grille du transistor de puissance, pour délivrer le courant représentatif du courant délivré par le transistor de puissance Ceci permet des opérations de comparaison relative au courant passant dans le transistor de puissance, en manipulant un courant de beaucoup plus petite intensité qui lui est proportionnel.

**[0017]** Avantageusement, la boucle de limitation de courant comporte un module de comparaison adapté pour comparer le courant représentatif du courant passant dans le transistor de puissance au courant de référence. Le module de comparaison comporte un transistor monté en diode et une source de courant de valeur le courant de référence, montés en parallèle.

[0018] Dans un mode de réalisation, la boucle de limitation de courant comporte en outre un transistor monté en miroir avec le transistor monté en diode et couplé à une entrée d'un circuit inverseur de courant comportant deux transistors montés en miroirs l'un de l'autre, la sortie dudit circuit inverseur étant couplée au noeud d'entrée/sortie du circuit de limitation de courant.

**[0019]** On obtient ainsi de façon simple l'effet d'empêcher la fourniture de courant par la sortie de la boucle de limitation de courant tant que la valeur du courant représentant le courant délivré par le transistor de puissance n'est pas supérieure à la valeur du courant de référence.

[0020] Suivant un second aspect, l'invention propose un circuit intégré comportant un régulateur suivant le premier aspect de l'invention.

**[0021]** Suivant un troisième aspect, l'invention propose un procédé de limitation du courant délivré, dans une charge à alimenter, par un transistor de puissance d'un régulateur de tension linéaire comprenant un circuit de régulation et un transistor de puissance piloté par la sortie du circuit de régulation de tension et destiné à être connecté en série à la charge à alimenter.

[0022] Un procédé selon l'invention comprend les étapes suivantes :

- si un courant représentatif d'un courant passant dans le transistor de puissance est supérieur à un courant de référence, délivrer un courant de sortie non nul ;

- sinon, ne délivrer aucun courant de sortie ;

20

30

40

45

50

55

les étapes étant mises en oeuvre par l'intermédiaire d'une boucle de limitation de courant comportant un noeud d'entrée/sortie couplé à une électrode de commande du transistor de puissance.

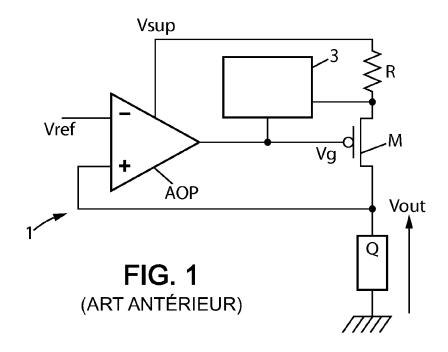

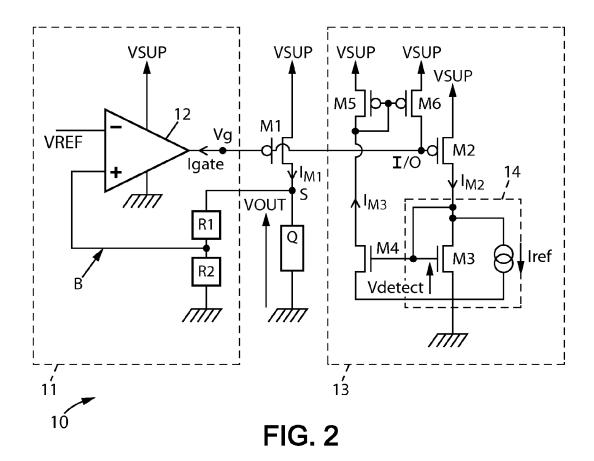

[0023] D'autres caractéristiques et avantages de l'invention apparaîtront encore à la lecture de la description qui va suivre. Celle-ci est purement illustrative et doit être lue en regard de la figure 2 annexée, qui représente un régulateur linéaire de tension dans un mode de réalisation de l'invention.

**[0024]** Sur la figure 2 est représenté un régulateur linéaire de tension 10 conçu pour introduire une faible chute de tension série (typiquement lorsque la différence entre la tension de référence et la tension de sortie du régulateur est inférieure à 2 Volts). Un tel régulateur est nommé régulateur de tension linéaire à faible chute de tension (« LDO » : « LowDropOut voltage regulator » en langue anglaise).

**[0025]** Le régulateur de tension 10 représenté sur la figure 2 est par exemple compris dans un circuit intégré. Il comporte un circuit de régulation de tension 11, qui comprend classiquement un amplificateur de tension différentiel 12, connecté entre une borne d'application d'une tension positive VSUP et la masse.

[0026] Le régulateur de tension 10 représenté sur la figure 2 comporte en outre un transistor de puissance M1, de type PMOS, dont la source est couplée à la borne VSUP et dont le drain est couplé à une borne S de sortie à laquelle est reliée une charge Q à alimenter à la tension régulée VOUT.

[0027] Le circuit de régulation de tension 11 est chargé de commander le transistor MOS de puissance M1 par l'intermédiaire de la tension VG en sortie du circuit de régulation 11 qui est appliquée sur l'électrode de commande, ici la grille, du transistor de puissance M1.

**[0028]** L'amplificateur de tension différentiel 12 reçoit sur une entrée, dans le cas présent l'entrée inverseuse, la tension de référence VREF fixant la valeur de la tension régulée souhaitée, et sur une entrée non inverseuse, la sortie d'une boucle B de retour en tension prenant en entrée la tension de sortie VOUT régulée du régulateur 11 prélevée sur le drain du transistor M1.

[0029] Dans le cas représenté, la boucle de retour B comprend en outre un pont diviseur résistif comprenant les résistances R1 et R2, introduit entre la borne S de sortie et l'entrée non inverseuse de l'amplificateur 12, afin d'obtenir sur l'entrée non inverseuse de l'amplificateur 12 une tension représentative de VOUT et supérieure à VREF.

[0030] Le régulateur de tension linéaire 10 dans le mode de réalisation considéré en référence à la figure 2 comporte

en outre une boucle de limitation de courant 13, adaptée pour limiter le courant de drain du transistor M1 à une valeur égale à Imax.

[0031] La boucle de limitation de courant 13 comprend un noeud d'entrée /sortie comprenant une entrée I et une sortie O confondues. Elle comprend en outre cinq transistors M2, M3, M4, M5 et M6 et une source de courant de référence Iref.

**[0032]** Le transistor M2, de type PMOS, est un miroir du transistor M1. Il consiste en une réplique proportionnelle du transistor M1. La source du transistor M2 est connectée à la borne VSUP. Les transistors M1 et M2 ont la même longueur de grille.

[0033] Le transistor M4 est un miroir du transistor M3. Ils ont la même longueur de grille et sont de type NMOS.

[0034] Le transistor M6 est un miroir du transistor M5. Ils ont la même longueur de grille et sont de type PMOS.

[0035] Les transistors M1, M2, M3, M4, M5 et M6 ont des largeurs de grille respectives W<sub>M1</sub>, W<sub>M2</sub>, W<sub>M3</sub>, W<sub>M4</sub>, W<sub>M5</sub>, W<sub>M6</sub>.

[0036] Le rapport entre la largeur d'un transistor, par exemple la largeur  $W_{M2}$  du transistor M2, et la largeur du transistor miroir, dans le cas du transistor M2 celle du transistor M1, est égal au rapport entre les courants de drain respectifs délivrés par chacun des deux transistors, dans le cas présent des transistors M1 et M2, lorsqu'ils opèrent en région de saturation.

**[0037]** L'entrée I, par l'intermédiaire du noeud d'entrée/sortie de la boucle de limitation de courant, est couplée à la grille du transistor de puissance M1. Elle relie la grille du transistor M1 à la grille du transistor M2.

[0038] Le drain du transistor M2 est couplé à l'entrée du circuit de comparaison 14 de la boucle de limitation de courant 13, qui comporte un transistor M3 monté en diode (source et drain sont reliées) et une source de courant de valeur l'ref montée en parallèle du transistor, connectée entre la source et le drain du transistor M3.

[0039] La valeur du courant l'ref est choisie telle que l'ref est égale à  $\text{Imax} \times \text{W}_{\text{M2}} / \text{W}_{\text{M1}}$ .

[0040] La source du transistor M3 est reliée à la masse.

20

30

35

40

45

50

55

[0041] La grille du transistor M3 est couplée à la sortie du circuit de comparaison 14 de la boucle de courant 13.

**[0042]** Les transistors M3 et M4 sont montés en recopie de courant. Ainsi la grille du transistor M3 est couplée à la grille du transistor M4, dont la source est couplée à la masse. Le drain de M4 est couplé au circuit d'inversion de courant comportant les transistors M5 et M6 montés en recopie de courant également.

**[0043]** Les sources des transistors M5 et M6 sont couplées à la borne VSUP. Les grilles des transistors M5 et M6 sont couplées. Le transistor M5 est monté en diode et le drain du transistor M5 est en outre couplé au drain du transistor M4 et le drain du transistor M6 est couplé à la sortie O, par le noeud d'entrée/sortie de la boucle de limitation de courant 13.

[0044] Le fonctionnement de la boucle de imitation de courant 13 décrit ci-après.

**[0045]** Le courant  $I_{M2}$  délivré par le transistor M2 miroir du transistor M1 et dont la valeur, égale à  $I_{M1} \times W_{M2} / W_{M1}$  représente le courant  $I_{M1}$ .

[0046] Tant que le courant  $I_{M1}$  délivré par le transistor M1 à la charge Q est inférieur à Imax, le courant  $I_{M2}$  est inférieur à Iref. Par conséquent, la tension V detect entre la source et la grille du transistor M3 est nulle. Le transistor M3 n'est donc pas passant. Les transistors M4 et M5, M6 étant des copies de M3, ne sont pas passants non plus.

[0047] Ainsi, tant que le courant I<sub>M1</sub> circulant dans le transistor M1 est inférieur à Imax, aucun courant n'est délivré par la sortie O de la boucle de limitation de courant 13.

[0048] Il n'y a donc aucune interférence avec le fonctionnement du circuit de régulation 11 et pas de consommation d'énergie indésirable, lorsque le courant  $I_{M1}$  circulant dans le transistor M1 est inférieur à Imax.

**[0049]** Lorsque le courant  $I_{M1}$  circulant dans le transistor M1 est supérieur à Imax, le courant  $I_{M2}$  représentatif du courant  $I_{M1}$ , est supérieur à Iref. Par conséquent, la tension entre la source et la grille du transistor M3 devient positive. Le transistor M3 est alors passant et le courant  $I_{M3}$  circulant dans le transistor M3 est égal à  $I_{M2}$ -Iref.

**[0050]** Les transistors M4 et M5, M6 étant des copies de M3, sont également passants. La boucle de limitation de courant 13 délivre alors en sortie 0 un courant Igate, de valeur positive égale à :

$$(I_{M1}\times W_{M2}/W_{M1} - Iref) \times ((W_{M4}\times W_{M6})/(W_{M3}\times W_{M5})).$$

[0051] L'impédance en sortie de l'amplificateur opérationnel qui était une impédance de valeur donnée, relativement haute (par exemple  $100 \text{ k}\Omega$ ), lorsque aucun courant n'était injecté par la boucle de limitation de courant 13, devient une impédance de valeur plus basse lorsque du courant est injecté par la boucle de courant (la transconductance de sortie de l'OTA devient alors négligeable par rapport à celle de la boucle de courant 13).

[0052] La valeur de l'impédance en sortie de l'amplificateur opérationnel est alors égale, lorsque la boucle de courant

injecte un courant depuis sa sortie O, à  $\frac{1}{G_{\rm mM1}} \times$  (W<sub>M1</sub>×W<sub>M3</sub> × W<sub>M5</sub>) /( W<sub>M2</sub>×W<sub>M4</sub> ×W<sub>M6</sub> ), où Gm<sub>M1</sub> est la trans-

conductance du transistor M1.

[0053] L'injection de courant de valeur positive par la boucle de limitation de courant a pour conséquence de figer la valeur de la tension appliquée à la grille du transistor M1 par le circuit de régulation 11, et limite ainsi la valeur du courant I<sub>M1</sub> délivré par le transistor M1.

[0054] Dans un mode de réalisation de l'invention, on a par exemple VSUP = 3,3 volts, VREF = 2,5 Volts,  $W_{M1}$  = 15 mm,  $W_{M2} = W_{M3} = W_{M5} = W_{M6} = 50 \mu m$ , Imax = 300 mA, Iref = 1 mA,  $Gm_{M1} = 1,5$  siemens (S).

[0055] Lorsque la valeur du courant circulant dans le transistor M1 dépasse Imax, l'impédance en sortie de l'amplificateur opérationnel devient alors égale à  $200 \Omega$ .

[0056] Le mode de réalisation décrit en référence à la figure 2 met en oeuvre une technologie de type semi-conducteur à oxyde de métal complémentaire (CMOS), toutefois l'invention pourrait également être mise en oeuvre avec la technologie bipolaire.

**[0057]** Le mode de réalisation décrit en référence à la figure 2 met en oeuvre un régulateur linéaire à faible chute de tension. Toutefois l'invention peut être appliquée pour tout type de régulateur linéaire de tension, comportant ou non un amplificateur différentiel. Par exemple, dans un autre mode de réalisation, le régulateur linéaire de tension comporte un amplificateur de classe D.

**[0058]** Bien sûr, les largeurs de grille W<sub>M1</sub>, W<sub>M2</sub>, W<sub>M3</sub>, W<sub>M4</sub>, W<sub>M5</sub>, W<sub>M6</sub> devront être choisies de manière à ce que le courant de sortie Igate, qui est défini en fonction de rapport entre ces largeurs, soit supérieur au courant maximum délivré en sortie de l'amplificateur opérationnel (correspondant par exemple au courant de court-circuit du régulateur, lorsque la borne S de la figure 2 est reliée à la masse).

20 [0059] La boucle de limitation de courant selon l'invention est ainsi dissociée du circuit de régulation de tension. Ainsi la fonction de limitation de courant est active même si le circuit de régulation est inactif ou non encore stabilisé, par exemple lors d'une mise sous tension. La solution de limitation de courant selon l'invention est en outre ainsi compatible avec diverses architectures de circuits de régulation.

La boucle de limitation de courant est par ailleurs plus courte que le circuit de limitation de courant de l'art antérieur décrit par exemple dans le document US 2004/0178778, ce qui a pour conséquence que l'action de limitation de courant de la boucle de limitation de courant selon l'invention est plus rapide que dans l'art antérieur.

#### Revendications

30

35

40

45

50

55

- Régulateur de tension linéaire (10) comprenant un circuit (11) de régulation de tension et un transistor de puissance (M1) piloté par la sortie du circuit de régulation de tension et destiné à être connecté en série à une charge à alimenter (Q), ledit régulateur comportant une boucle de limitation de courant (13) adaptée pour limiter le courant (I<sub>M1</sub>) délivré dans la charge par le transistor de puissance,

- la boucle de limitation de courant comportant un noeud d'entrée/sortie couplé à une électrode de commande du transistor de puissance,

- ladite boucle de limitation de courant étant adaptée pour, lorsqu'un courant  $(I_{M2})$  représentatif du courant  $(I_{M1})$  délivré par le transistor de puissance est supérieur à un courant de référence, délivrer un courant de sortie (Igate) non nul et pour, lorsque ledit courant représentatif du courant délivré par le transistor de puissance est inférieur audit courant de référence, ne délivrer aucun courant de sortie.

- 2. Régulateur de tension linéaire (10) selon la revendication 1, dans lequel le circuit de régulation (11) comporte :

- a. un amplificateur (12) de tension différentiel comprenant une sortie et une première et une seconde entrées; b. une boucle (B) de régulation de tension comportant une entrée couplée à l'électrode du transistor de puissance connectée à la charge (Q) et une sortie couplée à une entrée de l'amplificateur de puissance.

- 3. Régulateur de tension linéaire (10) selon la revendication 1 ou la revendication 2, dans lequel la boucle (13) de limitation de courant est adaptée pour délivrer un courant dont la valeur est égale à la différence entre le courant représentatif du courant délivré par le transistor de puissance et le courant de référence, multipliée par un facteur déterminé.

- **4.** Régulateur de tension linéaire (10) selon l'une quelconque des revendications 1 à 3, dans lequel la boucle de limitation de courant comprend un second transistor (M2) monté en miroir avec le transistor de puissance et de largeur de grille plus petite que la largeur de grille du transistor de puissance, pour délivrer le courant (I<sub>M2</sub>) représentatif du courant (I<sub>M1</sub>) délivré par le transistor de puissance (M1).

- 5. Régulateur de tension linéaire (10) selon l'une quelconque des revendications précédentes, dans lequel la boucle

#### EP 1 857 906 A1

de limitation de courant (13) comprend un module de comparaison (14) adapté pour comparer le courant ( $I_{M2}$ ) représentatif du courant ( $I_{M1}$ ) passant dans le transistor de puissance avec le courant de référence (Iref), et dans lequel le module de comparaison (14) comporte un transistor monté en diode (M3) et une source de courant de valeur le courant de référence (Iref), montés en parallèle.

5

6. Régulateur de tension linéaire (10) selon la revendication 5, comportant en outre un transistor (M4) monté en miroir avec le transistor monté en diode (M3) et couplé à une entrée d'un circuit inverseur de courant comportant deux transistors (M5, M6) montés en miroir l'un avec l'autre, la sortie dudit circuit inverseur étant couplée au noeud d'entrée/sortie du circuit de limitation de courant.

10

7. Circuit intégré comportant un régulateur de tension linéaire (10) selon l'une quelconque des revendications précédentes.

15

8. Procédé de limitation du courant (I<sub>M1</sub>) délivré, dans une charge (Q) à alimenter, par un transistor de puissance (M1) d'un régulateur de tension linéaire (10) comprenant un circuit de régulation de tension (11) et un transistor de puissance (M1) piloté par la sortie du circuit de régulation de tension et destiné à être connecté en série à la charge, comprenant les étapes suivantes mises en oeuvre par l'intermédiaire d'une boucle (13) de limitation de courant comportant un noeud d'entrée/sortie couplé à une électrode de commande du transistor de puissance:

20

a. délivrer un courant de sortie (Igate) non nul si un courant ( $I_{M2}$ ) représentatif d'un courant ( $I_{M1}$ ) délivré par le transistor de puissance (M1) est supérieur à un courant de référence (Iref) ;

b. sinon, ne délivrer aucun courant de sortie.

25

9. Procédé selon la revendication 8, selon lequel le circuit de régulation de tension (11) comporte un amplificateur (12) de tension différentiel comprenant une sortie et une première et une seconde entrées et une boucle (B) de régulation de tension comportant une entrée couplée à une électrode du transistor de puissance connectée à la charge et une sortie couplée à une entrée de l'amplificateur de puissance.

30

**10.** Procédé selon la revendication 8 ou la revendication 9, selon lequel la valeur du courant de sortie délivré(Igate) est égale à la différence entre le courant représentatif du courant passant dans le transistor de puissance et le courant de référence, multipliée par un facteur déterminé.

35

11. Procédé selon l'une quelconque des revendications 8 à 10, selon lequel la boucle de limitation de courant (13) comprend un second transistor (M2) monté en miroir du transistor de puissance, de largeur de grille plus petite que la largeur de grille du transistor de puissance, pour délivrer le courant (I<sub>M2</sub>) représentatif du courant (I<sub>M1</sub>) passant dans le transistor (M1) de puissance.

40

12. Procédé selon l'une des revendications 8 à 11, selon lequel une opération de comparaison entre le courant représentatif du courant passant dans le transistor de puissance (M1) et le courant de référence est effectuée à l'aide d'un transistor (M3) monté en diode et d'une source de courant (Iref) de valeur le courant de référence, montés en parallèle.

45

13. Procédé selon la revendication 12, selon lequel le courant de sortie (Igate) délivré est fourni par la sortie d'un circuit inverseur de courant comportant deux transistors (M5,M6) montés en miroirs l'un de l'autre, l'entrée dudit circuit inverseur étant couplée à un transistor (M4) monté en miroir du transistor (M3) monté en diode.

50

55

# Office européen RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande EP 07 10 7883

| DO                                           | CUMENTS CONSIDER                                                                                                                                                 |                                                                                                        |                                                          |                                         |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------|

| Catégorie                                    | Citation du document avec<br>des parties pertir                                                                                                                  | indication, en cas de besoin,<br>nentes                                                                | Revendication concernée                                  | CLASSEMENT DE LA<br>DEMANDE (IPC)       |

| X                                            | NV [NL]) 28 juin 20                                                                                                                                              |                                                                                                        |                                                          | INV.<br>G05F1/26                        |

| A                                            | * le document en er                                                                                                                                              | itier ^                                                                                                | 5,6,9-13                                                 |                                         |

| X                                            | WO 2005/008353 A (A<br>MARCO [IT]; MAZZUCO<br>27 janvier 2005 (20<br>* le document en er                                                                         | 005-01-27)                                                                                             | 1-13                                                     |                                         |

| x                                            | 17 novembre 2005 (2                                                                                                                                              | (SUGIURA MASAKAZU [JP])                                                                                | 1,2,8,9                                                  |                                         |

| A                                            | * le document en er                                                                                                                                              | tier *                                                                                                 | 3-7,<br>10-12                                            |                                         |

| x                                            | P 1 109 088 A (ST<br>[FR]) 20 juin 2001                                                                                                                          | MICROELECTRONICS SA<br>(2001-06-20)                                                                    | 1,2,8,9                                                  |                                         |

| A                                            | * le document en e                                                                                                                                               | tier *<br>                                                                                             | 3-7,<br>10-12                                            |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          | DOMAINES TECHNIQUES<br>RECHERCHES (IPC) |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          | G05F                                    |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          | 4001                                    |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

|                                              |                                                                                                                                                                  |                                                                                                        |                                                          |                                         |

| Le pré                                       | esent rapport a été établi pour tou                                                                                                                              | utes les revendications                                                                                |                                                          |                                         |

|                                              | ieu de la recherche                                                                                                                                              | Date d'achèvement de la recherche                                                                      |                                                          | Examinateur                             |

|                                              | La Haye                                                                                                                                                          | 7 septembre 2007                                                                                       | Sch                                                      | obert, Daniel                           |

| X : parti<br>Y : parti<br>autre<br>A : arriè | TEGORIE DES DOCUMENTS CITE<br>culièrement pertinent à lui seul<br>culièrement pertinent en combinaisor<br>document de la même catégorie<br>re-plan technologique | E : document de brev<br>date de dépôt ou a<br>lavec un D : cité dans la dema<br>L : cité pour d'autres | ret antérieur, mai<br>après cette date<br>nde<br>raisons | s publié à la                           |

|                                              | lgation non-écrite<br>ment intercalaire                                                                                                                          | & : membre de la mê                                                                                    | me famille, docui                                        | ment correspondant                      |

## ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

EP 07 10 7883

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Les dits members sont contenus au fichier informatique de l'Office européen des brevets à la date du Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

07-09-2007

| Document brevet cité<br>au rapport de recherche |            | Date de publication | Membre(s) de la<br>famille de brevet(s) |                | Date de publication                  |         |                                     |

|-------------------------------------------------|------------|---------------------|-----------------------------------------|----------------|--------------------------------------|---------|-------------------------------------|

| WO (                                            | 0146768    | Α                   | 28-06-2001                              | JP<br>US       | 2003518309<br>2001017537             | T<br>A1 | 03-06-200<br>30-08-200              |

| WO 2                                            | 2005008353 | Α                   | 27-01-2005                              | EP             | 1652018                              | A2      | 03-05-200                           |

| US 2                                            | 2005253569 | A1                  | 17-11-2005                              | CN<br>JP<br>KR | 1700129<br>2005327164<br>20060047972 | A       | 23-11-200<br>24-11-200<br>18-05-200 |

| EP :                                            | 1109088    | Α                   | 20-06-2001                              | FR<br>US       | 2802315<br>2001005129                |         | 15-06-200<br>28-06-200              |

**EPO FORM P0460**

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82

# EP 1 857 906 A1

### RÉFÉRENCES CITÉES DANS LA DESCRIPTION

Cette liste de références citées par le demandeur vise uniquement à aider le lecteur et ne fait pas partie du document de brevet européen. Même si le plus grand soin a été accordé à sa conception, des erreurs ou des omissions ne peuvent être exclues et l'OEB décline toute responsabilité à cet égard.

# Documents brevets cités dans la description

• US 20040178778 A [0008] [0009] [0059]