# (11) **EP 1 892 833 A2**

(12)

# **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

27.02.2008 Bulletin 2008/09

(21) Application number: **07114767.2**

(22) Date of filing: 22.08.2007

(51) Int Cl.:

**H03H 11/04** (2006.01) H03H 11/28 (2006.01) **H03H 11/12** (2006.01) H03H 11/32 (2006.01)

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC MT NL PL PT RO SE SI SK TR

Designated Extension States:

AL BA HR MK YU

(30) Priority: 24.08.2006 US 510443

(71) Applicant: ITT MANUFACTURING ENTERPRISES, INC.

Wilmington, Delaware 19801 (US)

(72) Inventor: Wyatt, Michael Clearwater, FL 33761 (US)

(74) Representative: Esser, Wolfgang ITT Industries Management GmbH Cannonstrasse 1 71384 Weinstadt (DE)

# (54) Transconductor and filter circuit

(57) A transconductor and filter circuit (101) is described in one embodiment, a front end module (102) within the transconductor and filter circuit converts a differential input voltage signal (111) into a differential output current (112) and supplies the output current at a

differential output. A filter module (103) coupled to the differential output of the front end module receives the differential output current, converts the output current into an intermediary differential voltage, and filters the differential voltage to obtain a filtered differential output voltage signal having low output impedance

7 IO1 7 IO1

FIG. 1

EP 1 892 833 A2

# Description

#### **TECHNICAL FIELD**

[0001] The invention relates generally to the field of electronic circuits, and more particularly, to a transconductor and filter circuit.

#### **BACKGROUND OF TUE INVENTION**

[0002] Numerous circuits are known, which are intended to provide conversion of a differential voltage input signal into an output current. These circuits have proven value in a variety of ever expanding communications applications. One example of such circuits is a triple differential amplifier that uses parallel- or series-connected sets of differential pairs of bipolar transistors whose inputs and outputs are connected in parallel, as described in detail in "The Multi-tanh Principle: A Tutorial Overview," by Sortie Gilbert, published in the IEEE Journal of Solid-State Circuits, Vol. 33, No. 1, January 1998.

**[0003]** Since the output impedance of such circuits is typically high, solutions have been proposed to lower the output impedance by, for example, buffering the output of the circuit with a pair of emitter followers. However, these solutions do not appear to offer low pass filtering capabilities within the circuit without an increase in power consumption. Thus, there is a need for a circuit that lowers the output impedance and merges the low pass filtering function in the circuit, without adding significant complexity or power consumption.

# **SUMMARY OF THE INVENTION**

**[0004]** A transconductor and filter circuit is described. In one embodiment, a front end module within the transconductor and filter circuit converts a differential input voltage signal into a differential output current and supplies the output current at a differential output. A filter module coupled to the differential output of the front end module receives the differential output current, converts the output current into an intermediary differential voltage, and filters the differential voltage to obtain a filtered differential output voltage signal having low output impedance.

**[0005]** Also included is a method to manufacture such a circuit as well as machine-readable media storing a description of a circuit and containing executable instructions, which, when executed, cause said circuit to perform a method comprising the steps of converting a differential input voltage signal into a differential output current; converting said output current into a differential voltage; and filtering said differential voltage to obtain a filtered differential output voltage signal having a low output impedance.

[0006] In a further preferred embodiment the invention is used within a multistage transconductor and filter circuit comprising a plurality of adjacently coupled stages. With each stage further comprising a front end module for converting a differential input voltage signal into a differential output current and for supplying said output current at a differential output; and a filter module coupled to said differential output of said front end module for receiving said output current converting said output current into a differential voltage and for filtering said differential voltage to obtain a filtered differential output voltage signal having a low output impedance.

# **BRIEF DESCRIPTION OF THE DRAWINGS**

#### [0007]

20

30

35

40

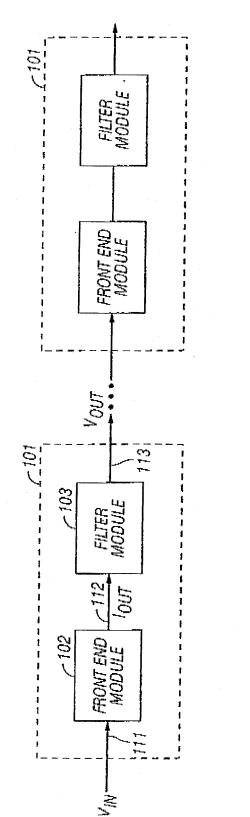

- Figure 1 is a block diagram illustrating a multistage transconductor and filter circuit according to an exemplary embodiment of the invention;

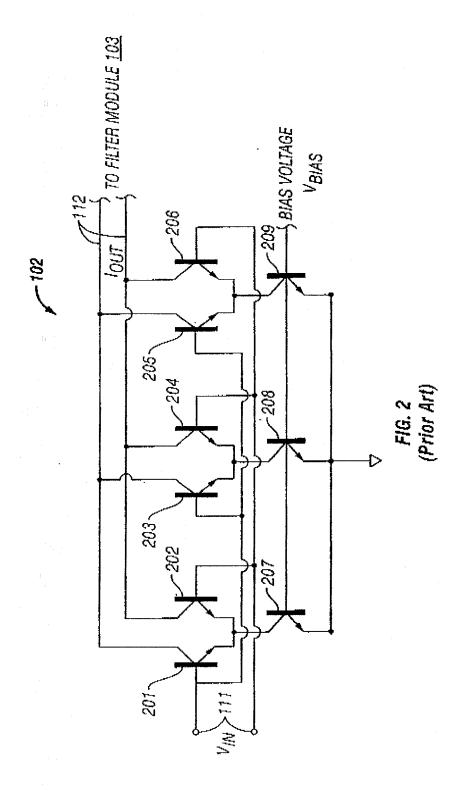

- Figure 2 is a circuit diagram illustrating an exemplary prior art front end module within one stage of the multistage transconductor and filter circuit

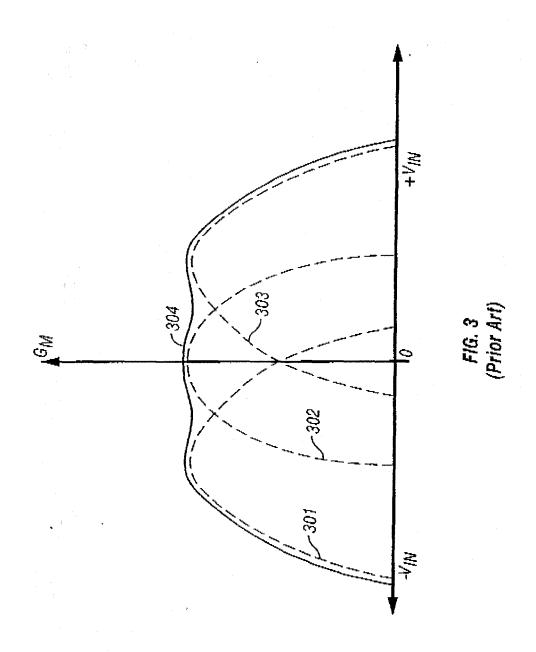

- Figure 3 is a graph illustrating the effective transconductance as a function of the differential input voltage for the prior art front end module;

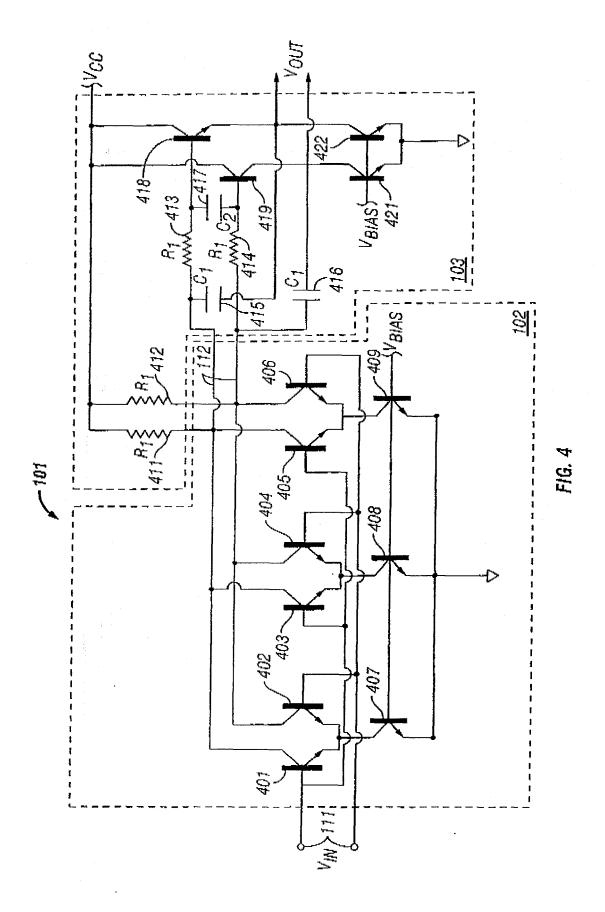

- Figure 4 is a circuit diagram illustrating a transconductor and filter circuit according to an exemplary embodiment of the invention;

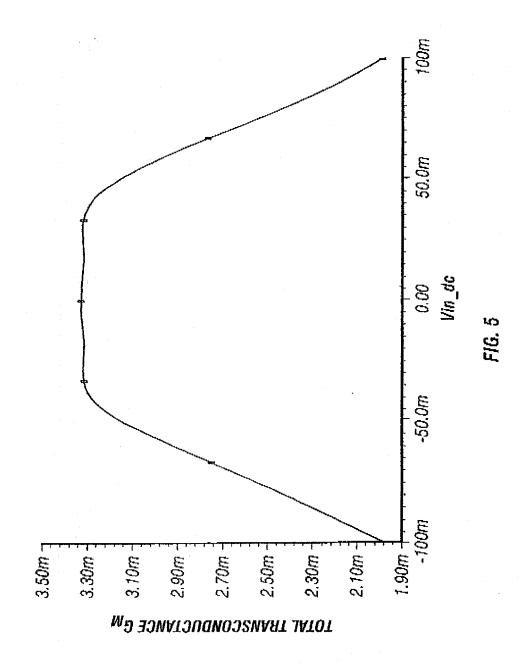

- Figure 5 is a graph illustrating the total transconductance for the transconductor and filter circuit according to an exemplary embodiment of the invention;

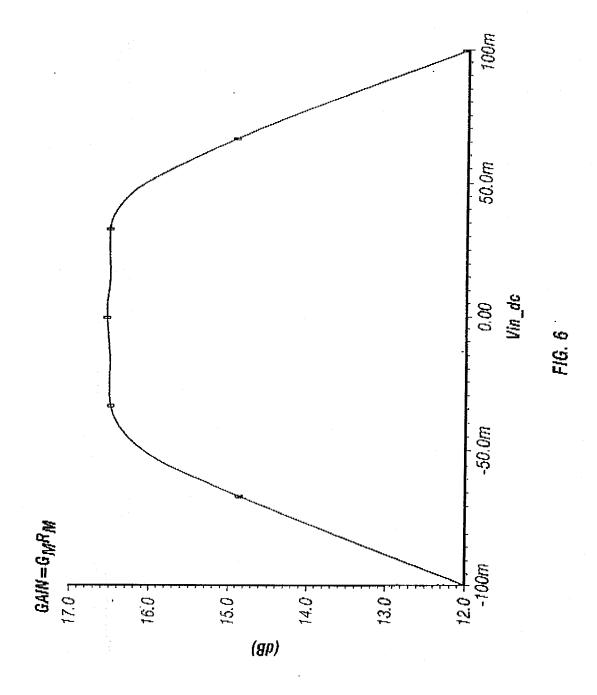

- Figure 6 is a graph illustrating the effective gain for the transconductor and filter circuit according to an exemplary embodiment of the invention;

- Figure 7 is a graph illustrating the voltage gain of a fourth order Butterworth filter for various values of a control current 'AGO according to an exemplary embodiment of the invention.

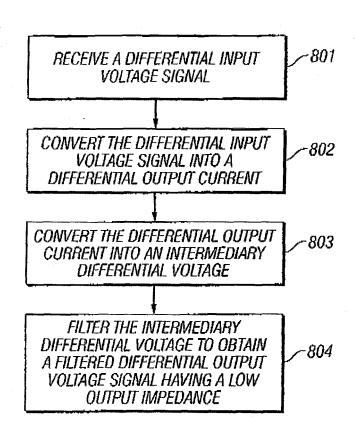

Figure 8 is a flow diagram illustrating a method for low pass filtering within the transconductor and filter circuit according to an exemplary embodiment of the invention.

#### **DETAILED DESCRIPTION**

5

20

30

35

40

45

50

55

**[0008]** Figure 1 is a block diagram illustrating a multistage transconductor and filter circuit 15 according to an exemplary embodiment of the invention. As illustrated in Figure 1, the multistage transconductor and filter circuit 100 includes multiple similar stages 101. In one embodiment, each stage 101 is a transconductor and filter circuit, which includes a front end module 102 coupled to a filter module 103, as described in further detail below. In an alternate embodiment the front end module 102 and the filter module 103 may be implemented on separate circuits.

**[0009]** The front end module 102 receives a differential input voltage signal ( $V_{IN}$ ) 111 and converts the differential input voltage signal 111 into a differential output current ( $I_{OUT}$ ) 112. The filter module 103 receives the differential output current 112 and outputs a differential output voltage signal ( $V_{OUT}$ ) 113, which is further supplied to a subsequent stage 101 within the multistage transconductor and filter circuit 100.

[0010] Figure 2 is a circuit, diagram illustrating an exemplary prior art front end module within one stage of the multistage transconductor and filter circuit. As illustrated in Figure 2, the front end module 102 is a differential amplifier, such as, for example, a triple differential amplifier or "triplet" circuit, as described in further detail in "The Multi-tanh Principle: A Tutorial Overview," by Barrie Gilbert, published in the IEEE Journal of Solid-State Circuits, Vol. 33, No. 1, January 1998. [0011] The front end module 102 includes one or more differential transistor pairs configured to convert  $V_{IN}$  111 into  $I_{OUT}$  112. The front end module 102 shown in Figure 2 includes three differential pairs of transistors 201-202, 203-204, and 205-206, having inputs and outputs coupled in parallel. The emitters of each differential transistor pair 201 -202, 203-204, 205-206 are coupled to corresponding collectors of transistors 207, 208, 209. The bases of transistors 207, 208, 209 are coupled to receive a bias voltage  $V_{BIAS}$ . In one embodiment the outer differential pairs 201-202 and 205-206 have opposing emitter-area ratios of A and operate at equal tail currents. The center differential pair 203-204 has equal emitter areas, such that a transconductance value  $g_M$  of the circuit 102 is centered at  $V_{IN}$ =0. The emitter bias current transmitted to this center pair 203-204 is set to K times the emitter bias current transmitted to the outer pairs, where K is a factor less than 1. For different values of A and K and in order to minimize distortion, the incremental transconductance  $g_M$  for the circuit 102 can be maintained at a nearly constant value over a wide range of the differential input voltage signal  $V_{IN}$  111. The  $g_M$  value for  $V_{IN}$ =0 can be determined as follows:

$$g_M = g_{m0} \ x \ \frac{1}{(2+K)} \ x \left\{ \frac{8A}{(1+A)^2} + K \right\}$$

where  $g_{M0}$  is the  $g_{M}$  that would result with A=1, that is using the total tail current in a single differential transistor pair.  $g_{M0}$  can be calculated as follows:

$$g_{M0} = \frac{q \, Ic}{kT}$$

where q is the election charge, lc is the total current, k is the Boltzmann constant, and T is the temperature in Kelvins (K). **[0012]** Figure 3 is a graph illustrating the effective transconductance  $g_M$  as a function of the differential input voltage  $V_{IN}$  111 for the prior art front end module 102. As illustrated in Figure 3, the graphic representations 301, 302, and 303 correspond to the differential transistor pairs 201-202, 203-204, and 205-206, respectively, and are offset due to the performance of each respective differential transistor pair. A composite graphic representation 304 illustrates the transconductance  $g_M$  of the front end module 102 as a function of the differential input voltage  $V_{IN}$  111.

**[0013]** Figure 4 is a circuit diagram illustrating a transconductor and filter circuit 101 according to an exemplary embodiment of the invention. As illustrated in Figure 4, in one embodiment, the transconductor and filter circuit 101 includes a front end module 102 similar to the front end module described in detail in connection with Figure 2, having three differential pairs of transistor devices 401-402, 403-404, and 405-406, having inputs and outputs coupled in parallel. Alternatively, the circuit 101 may include any number of differential transistor pairs. The emitters of each differential transistor pair 401-402, 403-404, 405-406 are coupled to corresponding collectors of transistor devices 401, 408, 409. The bases of transistor devices 407, 408, 409 are coupled to receive a bias voltage  $V_{\text{BIAS}}$ .

[0014] In one embodiment, the differential output current 112 is supplied to the filter module 103 at the output of the

front end module 102. The filter module 103 includes resistor devices ( $R_1$ ) 411, 412, 413 and 414. Each resistor device 411, 412 is coupled from  $V_{CC}$  to each output current 112. This arrangement converts the differential output current 112 into an intermediary differential voltage. Each resistor device 413, 414 is coupled in series to one line of the differential output of the front end module 102. In one embodiment the resistor devices 411, 412, 413 and 414 have an identical resistance value  $R_1$ . The filter module 103 further includes capacitor devices 415 and 416 coupled to the corresponding resistor devices 413 and 414. A further capacitor device 417 is coupled between the two resistor devices 413 and 414. In one embodiment, the capacitor devices 415 and 416 have an identical capacitance value  $C_1$  and the capacitor device 417 has a capacitance value  $C_2$ . In an alternate embodiment, the resistor devices 413, 414 and the capacitor devices 415, 416, and 417 may be implemented on a separate circuit coupled to the front end module 102. The differential voltage is further supplied to a pair of emitter followers 418, 419. The voltage gain of the emitter followers 418, 419 has a value of less than 1 and provides a low output impedance to drive a subsequent stage 101. The base of each transistor device 418, 419 is coupled to a corresponding collector of transistor devices 421, 422, which have their bases coupled to receive a bias voltage V11

[0015] In one embodiment the transfer function of the circuit 101 is calculated as follows:

$$T(S) = \left[\frac{g_{\rm M}}{\frac{S^2}{\omega_{0^2}} + \frac{aS}{\omega_{0^2}} + 1}\right] x R_1$$

where  $g_M$  is the effective transconductance of the circuit 101,  $\omega$ 0 is the corner frequency of the filter module 103; a is a coefficient determined by the selection of the resistance  $R_1$ , and of the capacitances  $C_1$ . and  $C_2$  and  $g_M R_1$  is the effective gain of the circuit 101. The low pass filter function can thus be implemented with a voltage gain of  $g_M R_1$ .

**[0016]** Figure 5 is a graph illustrating the total transconductance for the transconductor and filter circuit 101 according to an exemplary embodiment of the invention As shown in Figure 5, the total transconductance  $g_M$ . as a function of the differential input voltage  $V_{IN}$  111, is a composite of the transconductance values for the corresponding differential transistor pairs 401-402, 403-404, 405-406, which are displaced in center voltage. By broadening the transconductance over the differential input voltage  $V_{IN}$  111, the circuit 101 has a broader signal handling range before it becomes non-linear. **[0017]** Figure 6 is a graph illustrating the effective gain for the transconductor and fitter circuit 101 according to an exemplary embodiment of the invention. In one embodiment, the effective gain of the circuit 101. which is defined as the differential voltage across the two resistors 411 and 412 divided by the differential input voltage 111, is a function of the transconductance  $g_M$  times the value  $R_1$  of the resistors 411, 412.

**[0018]** Figure us a graph illustrating the voltage gain of a fourth order Butterworth filter for various values of a control current  $I_{AGC}$  according to an exemplary embodiment of the invention. As shown in Figure 7, in one embodiment, the voltage gain, in decibels (dB), varies for a control current  $I_{AGC}$  between 0 and 50 microAmpers ( $\mu$ A). However, the filter characteristics remain unchanged and are independent of the voltage gain.

[0019] In one embodiment, a fourth order Butterworth filter is implemented with two transconductor and filter circuits 101 cascaded together, as shown in the multistage circuit 100 of Figure 1. The two transconductor and filter circuits 101 are not identical, having different values for the capacitance of capacitors 415, 416 and 417. In an alternate embodiment, a Bessel filter may be implemented using the transconductor and filter circuit 101. In another alternate embodiment, an approximation of a Gaussian filter may be implemented using the transconductor and filter circuit 101. In yet another alternate embodiment, a transitional filter may be implemented using the transconductor and filter circuit 101. The transfer function of the fourth order Butterworth filter can be calculated according to the following equation:

$$T(S) = \frac{1}{S^4 + cS^3 + dS^2 + cS + 1}$$

Fore c = 2,61, d = 3,41, and if S =  $\omega$ j = j, then:

55

10

15

20

25

30

35

40

45

$$T(S) = \frac{1}{j^4 + cj^3 + dj^2 + cj + 1} = \frac{1}{1 - jc - d + jc + 1} = \frac{1}{2 - d} = \frac{1}{\sqrt{2}}$$

Further breaking the 4<sup>th</sup> order in to two 2<sup>nd</sup> order equations:

$$\frac{1}{S^2 + aS + 1} x \frac{1}{S^2 + bS + 1} = \frac{1}{S^4 + cS^3 + dS^2 + cS + 1}$$

Thus equating like terms in powers of S.

5

10

15

40

50

55

$$a + b = c$$

and  $2 + ab = d$

$$b = \frac{d-2}{d}$$

$$a + \frac{d-2}{a} = c$$

$$a^2 - ca + d - 2 = 0$$

$$a = \frac{c \pm \sqrt{c^2 - 4(d - 2)}}{2} = \frac{2.61 \pm \sqrt{(2.61)^2 - 4(3.41 - 2)}}{2} = 1.843 \text{ or } 0.7674$$

$$b = c - a = 0,7674$$

or 1,843

Note; 0,7674 is the high Q case and 1,843 is the low U case.

45 A 2<sup>nd</sup> order general Sallen-Key type low pass filter has the transfer function: (see Fig x):

$$T(S) = k \frac{1}{S^2 R_1 R_2 C_1 C_2 + S((1-k)R_1 C_1 + R_2 C_2 + R_1 C_2) + 1}$$

Where  $\rm R_1,\, R_2,\, C_1$  &  $\rm C_2$  are component values and k is the amplifier voltage gain.

Normalizing to

$$j\omega_0 = j$$

and  $R_1R_2C_1C_2 = \frac{1}{\omega_0^2} = 1$  let  $R_1 = R_2 = R$

$$R[(1-k)C_1+2C_2]=1,843 (or 0,7674)$$

$R^2C_1C_2=1$

Further normalize to R = 1

$[(1-k)C_1+2C_2]=1,843$

If  $C_1C_2 = 1$

5

$(1-k)C_1 + \frac{2}{C_1} = 1,843$

$(1-k)C_1^2 - 1.843C_1 + 2 = 0$

$C1 = \frac{\frac{1,843}{(1-k)} \pm \sqrt{\left[\frac{1,843}{1-k}\right]^2 - 4\left[\frac{2}{1-k}\right]}}{2}$

$\left[\frac{1,843}{1-k}\right]^2 \ge \frac{8}{1-k}$

$1,843^2 \ge 8(1-k)$

Thus,  $k \ge 0.5754$ . If the coefficient S is 0,17674, then  $k \ge 0.9264$ .

If the assumption is that k = 0.95 (emitter follower gain) and for S=1,843, then:

$C_{1} = \frac{\frac{1,843}{(1-0,95)} \pm \sqrt{\left[\frac{1,843}{1-0,95}\right]^{2} - 4\left[\frac{2}{1-0,95}\right]}}{2} = 1,119 (normalized low Q)$

$C_2 = \frac{1}{C_1} = 0.8935 (normalized low Q)$

If the assumption is that  $k \equiv 0.95$  and for S=0.7674, then:

$$C_{1} = \frac{0.7674}{(1-0.95)} \pm \sqrt{\left[\frac{0.7674}{1-0.95}\right]^{2} - 4\left[\frac{2}{1-0.95}\right]} = 3,328 (normalized high Q)$$

$$C_2 = \frac{1}{C_1} = 0,3005 (normalized \ high \ Q)$$

Let R=2,000 (circuit value) and desired corner frequency  $\omega_0 = 2\pi (15 \text{MHz})$ . For k $\geq 0,5754$ :

$$C_1 = \frac{C_1}{R\omega_0} = 5.936 pF \cdots (circuit\ value)$$

$$C_2 = \frac{C_2}{R\omega_0} = 4,74 \, pF \cdots (circuit \, value)$$

For  $k \ge 0.9264$ :

15

25

45

50

55

$$C_1 = \frac{C_1}{R\omega_0} = 17,66 \, pF \cdots (circuit \, value)$$

$$C_2 = \frac{C_2}{R\omega_0} = 1,594 \, pF \cdots (circuit \, value)$$

$$T(S) = \frac{1}{S^2 + aS + 1} \qquad |T(S)|_{S - j\omega_0 = j} = \left| \frac{1}{ja} \right| = \frac{1}{a} = 0,5426 = -5,31db \ (low \ Q \ case)$$

$$T(S) = \frac{1}{S^2 + bS + 1} \qquad |T(S)|_{S - j\omega_0 = j} = \left| \frac{1}{jb} \right| = \frac{1}{b} = 1,303 = +2,3db \text{ (high Q case)}$$

[0020] Note that the product of the above T(S) sections yields -3.01 dB, the requisite 3dB corner frequency.

**[0021]** The values of  $R_1$   $C_1$ ' and  $C_2$ ' are the values used in Figure x with two cascaded sections. These values directly map into the differential circuit of Figure 4 with the exception of  $C_2$ ' which maps into Figure 4 with a scale factor of ½ % due to the differential nature of Figure 4.

**[0022]** Figure 8 is a flow diagram illustrating a method for low pass filtering within the transconductor and filter circuit according to an exemplary embodiment of the invention. As shown in Figure 8, at processing block 801, a differential input voltage signal is received. At processing block 802, the differential input voltage signal is converted into a differential output current. At processing block 803, the differential output current is converted into an intermediary differential

voltage. Finally, at processing block 804, the intermediary differential voltage is filtered to obtain a filtered differential output voltage signal having low output impedance.

[0023] It is also to be understood that embodiments of the present invention may be implemented not only within a physical circuit (e.g. on a semiconductor chip), but also within machine-readable media. For example, the circuits and designs discussed above may be stored upon and/or embedded within machine-readable media associated with a design tool used for designing semiconductor devices. Examples include a netlist formatted in the VHSIC Hardware Description Language (VHDL). Verilog language, or Spice language. Some netlist examples include: a behavioral level netlist, a register transfer level (RTL) netlist, a gate level netlist, and a transistor level netlist. Machine-readable media also include media having layout information such as a GUS-II file. Furthermore, netlist files or other machine-readable media for semiconductor chip design may be used in a simulation environment to perform the methods of the teachings described above. Thus, it is also to be understood that embodiments of this invention may be used as or to support a software program executed upon some form of a processing core (such as the CPU of a computer) or otherwise implemented or realized upon or within a machine-readable medium, which includes any mechanism for storing or transmitting information in a form readable by a machine (e.g. a computer).

**[0024]** In the foregoing specification, the invention has been described with reference to specific exemplary embodiments thereto. It will, however, be evident that various modifications and changes may be made thereto without departing from the broader spirit and scope of the invention as set forth in the appended claims- The specification and drawings are, accordingly, to be regarded in an illustrative sense rather than a restrictive sense.

Claims

10

15

20

30

35

50

- 1. A circuit (101) comprising:

- a front end module (102) for converting a differential input voltage signal (111) into a differential output current (112) and for supplying said output current at a differential output; and a filter module (103) coupled to said differential output of said front end module (111) for receiving said output current, converting said output current into a differential voltage (113) and for filtering said differential voltage to obtain a filtered differential output voltage signal having a low output impedance.

2. The circuit (101) according to claim 1, wherein said filter module (103) is a low pass filter

- 3. The circuit (101) according to claim 1 or 2, wherein said front end module (102) further comprises at least one differential pair of transistor devices (201-202, 203-204, 205-206) having inputs and outputs coupled in parallel.

- 4. The circuit (101) according to claim 1, wherein a voltage gain value of said circuit less than unity.

- 5. The circuit (101) according to one of claims 1 to 4 wherein said filter module (103) further comprises:

- a plurality of resistor devices (411, 412, 413, 414), at least one resistor device being coupled in series to each line of said differential output (112) of said front end module (102).

- 6. The circuit (101) according to claim 5, wherein said filter module (103) further comprises:

- a plurality of capacitor devices (415, 416), each capacitor device being coupled to one line of said differential output (112) of said front end module; and a further capacitor device (417) coupled between said each line of said differential output.

- 7. The circuit (101) according to claim 6, wherein said filter module (103) further comprises:

- an emitter follower (418, 419) coupled to said at least one resistor device for providing said low output impedance.

- 8. The circuit (101) according to claim 7, wherein said emitter follower has a voltage gain value of less than unity.

- 55 **9.** The circuit (101) according to one of claims 5 to 8, wherein each resistor device of said plurality of resistor devices (411, 412, 413, 414) has an identical resistance value.

- 10. The circuit (101) according to one of claims 6 to 9, wherein said each capacitor device (415, 416) has an identical

capacitance value.

5

10

20

35

40

55

- 11. The circuit (101) according to one of claims 6 to 10 wherein said at least one resistor device (411, 412, 413, 414), said each capacitor device (415, 416), and said further capacitor device (417) are implemented on a separate circuit

- 12. A method to manufacture a circuit (101) comprising the steps of:

coupling a filter module (103) to a differential output of a front end module (102); said front end module (102) for converting a differential input voltage (111) signal into a differential output current (112) and for supplying said output current at said differential output; and said filter module (103) for receiving said output current, for converting said output current into a differential voltage, and for filtering said differential voltage to obtain a filtered differential output voltage signal having a low output impedance.

15 **13.** The method according to claim 12, further comprising the step of:

coupling in parallel inputs and outputs of at least one differential pair of transistor devices (201-202, 203-204, 205-206) within said front end module, said at least one differential pair of transistor devices to receive and convert said differential input voltage signal (111) into said output current (112).

- **14.** The method according to claim 12, wherein said filter module (103) is a low pass filter.

- **15.** The method according to claim 12, wherein said step of coupling said filter module further comprises the step of:

- coupling in series a plurality of resistor devices (411, 412, 413, 414), to said differential output (112) of said front end module, at least one resistor device being coupled to each line of said differential output

- 16. The method according to claim 15, wherein said step of coupling said filter module further comprises the step of:

- coupling a plurality of capacitor devices (415, 416 )to said differential output of said front end module, each capacitor device being coupled to one line of said differential output

- 17. The method according to claim 16 wherein said step of coupling said filter module further comprises the step of:

coupling a further capacitor device (417) between said each line of said differential output

- 18. The method according to claim 18, wherein said step of coupling said filter module further comprises the step of: coupling an emitter follower (418, 419) to said at least one resistor device for providing said low output impedance.

- 19. The method according to claim 18, wherein said emitter follower has a voltage gain value of less than unity.

- 20. A method comprising the steps of:

- converting a differential input voltage signal into a differential output current (802); converting said output current into a differential voltage (803); and filtering said differential voltage to obtain a filtered differential output voltage signal having a low output impedance (804).

- **21.** The method according to claim 20, wherein said step of converting said differential input voltage signal further comprises the steps of:

- receiving said differential output voltage signal at a front end module (801); and supplying said differential output current at a differential output of said front end module.

- 22. The method according to claim 21, wherein said step of converting said output current further comprises the steps of:

receiving said output current at a filter module coupled to said differential output of said front end module.

# 23. A circuit comprising:

5

10

15

20

25

30

35

means (102) for converting a differential input voltage signal into a differential output current means for converting said output current into a differential voltage; and means (103) for filtering said differential voltage to obtain a filtered differential output voltage signal having a low output impedance.

- **24.** A multistage transconductor and filter circuit comprising:

- a plurality of adjacently coupled stages (101), each stage further comprising:

a front end module (102) for converting a differential input voltage signal into a differential output current and for supplying said output current at a differential output; and

a filter module (103) coupled to said differential output of said front end module for receiving said output current converting said output current into a differential voltage and for filtering said differential voltage to obtain a filtered differential output voltage signal having a low output impedance.

- **25.** The multistage transconductor and filter circuit according to claim 24, wherein said filtered differential output voltage signal (103) is transmitted to a subsequent stage of said plurality of adjacently coupled stage.

- **26.** A machine-readable media storing a description of a circuit, said circuit comprising:

a front end module (102) for converting a differential input voltage signal into a differential output current and for supplying said output current at a differential output and

a filter module (103) coupled to said differential output of said front end module for receiving said output current, converting said output current into a differential voltage and for filtering said differential voltage to obtain a filtered differential output voltage signal having a low output impedance.

**27.** A machine-readable media storing a description of a circuit and containing executable instructions, which, when executed, cause said circuit to perform a method comprising the steps of:

converting a differential input voltage signal (111) into a differential output current (112); converting said output current into a differential voltage; and

filtering said differential voltage to obtain a filtered differential output voltage (113) signal having a low output impedance.

40

45

50

FIG

10G Active Filter 4th Order Butterworth Filter lage=0 to 50ua 100M √ Rgc 🗀 : fagc Active AGC Filter at 0,50,100c ⊃: lagc × lage ∆ lagc 3.1M ⇒ lagc +: lago lagc=50MG lagc = 0MG 串令 o : lage obaj : ∇ 5 中 ♦ 和财 ogel∵ N 100 - 02--50 -30 -10 었 5 50

(*gp*)

FIG. 8

# REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

# Non-patent literature cited in the description

- **SORTIE GILBERT.** The Multi-tanh Principle: A Tutorial Overview. *IEEE Journal of Solid-State Circuits*, January 1998, vol. 33 (1 [0002]

- BARRIE GILBERT. The Multi-tanh Principle: A Tutorial Overview. *IEEE Journal of Solid-State Circuits*, January 1998, vol. 33 (1 [0010]