## (11) EP 1 924 079 A2

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

21.05.2008 Bulletin 2008/21

(51) Int Cl.: H04N 3/15 (2006.01)

(21) Application number: 07022020.7

(22) Date of filing: 13.11.2007

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC MT NL PL PT RO SE SI SK TR

Designated Extension States:

AL BA HR MK RS

(30) Priority: 17.11.2006 JP 2006311161

(71) Applicant: Olympus Corporation Tokyo 151-0072 (JP) (72) Inventor: Nakajima, Shinichi Tokyo (JP)

(74) Representative: Winter, Brandl, Fürniss, Hübner Röss, Kaiser, Polte Partnerschaft Patent- und

Alois-Steinecker-Strasse 22 85354 Freising (DE)

Rechtsanwaltskanzlei

## (54) Solid-state imaging apparatus

(57)A solid-state imaging apparatus includes: a pixel section having two-dimensionally arranged pixels, each having a photoelectric conversion means, a memory means for storing a photoelectric conversion signal of the photoelectric conversion means, a transfer means for transferring the photoelectric conversion signal to the memory means, a first reset means for resetting the memory means, a second reset means driven independently from the first reset means for resetting the photoelectric conversion means, and a read means for reading the photoelectric conversion signal of the memory means; and a controller for effecting a control so that, after passage of a predetermined time subsequently to the rendering of a concurrent reset by the second reset means on the photoelectric conversion means of all pixels in a read subject region, a transfer of the photoelectric conversion signal is concurrently effected by the transfer means from the photoelectric conversion means to the memory means of all pixels in the read subject region, and a reading of the photoelectric conversion signal stored at the memory means is effected by the read means, wherein when the concurrent reset by the second reset means is effected in a period during which the reading by the read means is effected, the reading by the read means is temporarily halted at least at one or the other of timings of a start and a release of the concurrent reset by the second reset means.

FIG. 3

EP 1 924 079 A2

25

40

45

50

#### Background of the Invention

**[0001]** The present invention relates to solid-state imaging apparatus, and more particularly relates to a solid-state imaging apparatus adapted to be capable of avoiding an effect of fluctuation in power supply or GND occurring due to the rendering of a concurrent reset operation of all pixels in a readout pixel region.

1

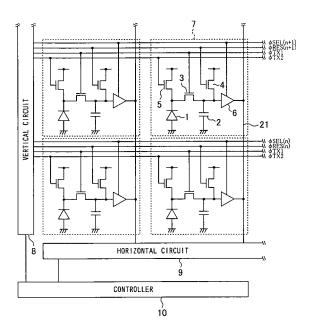

[0002] As a pixel of the pixel section to be used in a solid-state imaging apparatus having a concurrent shutter (also referred to as global shutter) function, one constructed as shown in Fig. 1 has been disclosed for example in Japanese Patent Application Laid-Open hei-11-261896. Fig. 1 includes: 1, a photoelectric conversion means such as a photodiode for receiving light for a predetermined time to accumulate photoelectric charge and effect its photoelectric conversion; 2, a memory means for retaining photoelectric charge of the photoelectric conversion means 1; 3, a transfer means for transferring photoelectric charge of the photoelectric conversion means 1 to the memory means 2; 4, a reset means for resetting the memory means 2 to the potential of a power supply; 5, a discharging means for resetting the photoelectric conversion means 1 to the potential of a power supply; and 6, a read means for reading electric charge of the memory means 2. These means constitute a unit pixel 7. A plurality of unit pixels 7 having such construction are then two-dimensionally arranged to constitute a pixel section. It should be noted that what is denoted by 21 is a vertical signal line for outputting signal read out by the read means 6.

**[0003]** Also referring to Fig. 1,  $\phi$  TX1,  $\phi$  RES(n),  $\phi$  TX2, and  $\phi$  SEL(n) are a transfer control signal, reset control signal, discharging control signal, and read control signal, respectively, for controlling ON/OFF of the transfer means 3, reset means 4, discharging means 5, and read means 6. It should be noted that suffix (n) of  $\phi$  RES (n) and  $\phi$  SEL (n) represents the location of row, and these control signals are outputted row by row of the pixel section from a vertical circuit (not shown).

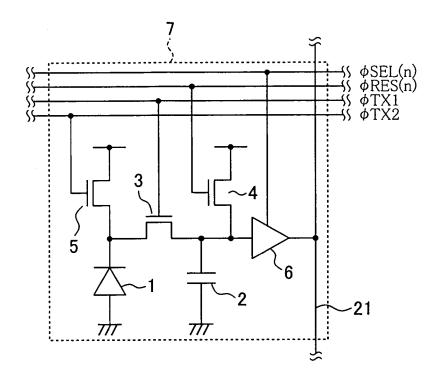

[0004] An operation of the pixel section using the pixel shown in Fig.1 will now be described with reference to a timing chart shown in Fig.2. As shown in Fig.2, the discharging control signal  $\phi$  TX2 is driven to H level concurrently for all pixels so that a concurrent discharging operation of all pixels is started by the discharging means 5. After passage of a predetermined time, the discharging control signal  $\phi$  TX2 is brought to L level concurrently for all pixels so that a concurrent discharging/reset operation of all pixels is completed by the discharging means 5 (time point  $t_1$ ) and exposure of all pixels is started.

**[0005]** After passage of a predetermined exposure time, at the timing of concurrent transfer of all pixels, the transfer means 3 of all pixels are concurrently turned ON by the transfer control signal  $\phi$  TX1. The photoelectric charges accumulated at the photoelectric conversion

means 1 are thereby concurrently transferred to the memory means 2 (time point t<sub>2</sub>). In other words, an exposure is ended. Here, in the timing chart shown in Fig. 2, a period indicated as Tint is an actual exposure period. Next after the end of the exposure, the read means 6 controlled by the read control signal φ SEL(n) is used to start read of signal level sequentially from the first row. It should be noted that, Vdd, Gnd in Fig.2 indicate fluctuation in power supply (Vdd) and Gnd at the time of the concurrent discharging/reset operation by the discharging control signal \( \psi \) TX2 and at the time of the concurrent transfer operation by the transfer control signal \( \psi \) TX1. [0006] Now with the solid-state imaging apparatus having a pixel section consisting of pixels constructed as the above, in order that the discharging/reset operation by the discharging control signal \$\phi\$ TX2 of the photoelectric conversion means of all pixels be concurrently effected within a read period based on the concurrent shutter method, it is necessary to concurrently drive a load capacitance of the order of several-ten thousand pF though it depends on the number of pixels and/or pixel size. When such drive is effected, the power supply (Vdd) and Gnd fluctuate as shown in Fig.2 and affect readout signal, deteriorating image quality by causing stripe-like noise. Further, it is technologically difficult to complete such a concurrently driven discharging/reset operation within a horizontal blanking period (several  $\mu$ s or less).

#### Summary of the Invention

[0007] To eliminate the above problems in the solidstate imaging apparatus having a prior-art concurrent shutter function, it is an object of the present invention to provide a solid-state imaging apparatus adapted to be capable of avoiding an effect for example on readout signal of the fluctuation in power supply or GND that occurs due to the rendering of reset operation concurrently for all pixels.

[8000] In a first aspect of the invention, there is provided a solid-state imaging apparatus including: a pixel section having two-dimensionally arranged pixels, each having a photoelectric conversion means, a memory means for storing a photoelectric conversion signal of the photoelectric conversion means, a transfer means for transferring the photoelectric conversion signal to the memory means, a first reset means for resetting the memory means, a second reset means driven independently from the first reset means for resetting the photoelectric conversion means, and a read means for reading the photoelectric conversion signal of the memory means; and a controller for effecting a control so that, after passage of a predetermined time subsequently to the rendering of a concurrent reset by the second reset means on the photoelectric conversion means of all pixels in a read subject region, a transfer of the photoelectric conversion signal is concurrently effected by the transfer means from the photoelectric conversion means to the memory means of all pixels in the read subject region, and a read-

15

20

25

30

35

40

45

ing of the photoelectric conversion signal stored at the memory means is effected by the read means, wherein when the concurrent reset by the second reset means is effected in a period during which the reading by the read means is effected, the reading by the read means is temporarily halted at least at one or the other of timings of a start or a release of the concurrent reset by the second reset means.

**[0009]** In a second aspect of the invention, the controller in the solid-state imaging apparatus according to the first aspect sets a period of the temporary halt by a unit of readout line of the pixel section.

**[0010]** In a third aspect of the invention, the controller in the solid-state imaging apparatus according to the first aspect causes reading by the read means to be effected in a period, after a predetermined period from the start of the concurrent reset by the second reset means, to the release of the concurrent reset by the second reset means.

**[0011]** In a fourth aspect of the invention, the controller in the solid-state imaging apparatus according to the third aspect sets the start of the concurrent reset by the second reset means within a vertical blanking period.

**[0012]** In a fifth aspect of the invention, the controller in the solid-state imaging apparatus according to the first aspect causes the concurrent reset by the second reset means to be effected with including a region not subjected to reading outside the read subject region.

**[0013]** In a sixth aspect of the invention, the solid-state imaging apparatus according to any one of the first to fifth aspects further includes an A/D converter for converting the photoelectric conversion signal into a digital signal, a line memory for effecting a delay of the digital signal for a period corresponding to the period of the temporary halt, and a select means for selecting between an output of the A/D converter and an output of the line memory, wherein the controller controls the select means so that an output of the line memory is selected and outputted until a release of the temporary halt and an output of the A/D converter after the release.

**[0014]** In a seventh aspect of the invention, the solid-state imaging apparatus according to any one of the first to fifth aspects further includes an A/D converter for converting the photoelectric conversion signal into a digital signal, and a buffer memory for transiently storing the digital signal, wherein the controller causes to halt the storing of the digital signal to the buffer memory for a period corresponding to the period of the temporary halt.

#### Brief Description of the Drawings

#### [0015]

Fig. 1 is a circuit diagram showing a pixel construction of pixel section in a prior-art solid-state imaging apparatus.

Fig.2 is a timing chart for explaining operation in the case where a concurrent shutter operation is effect-

ed in a solid-state imaging apparatus having a pixel section of the pixel construction shown in Fig.1.

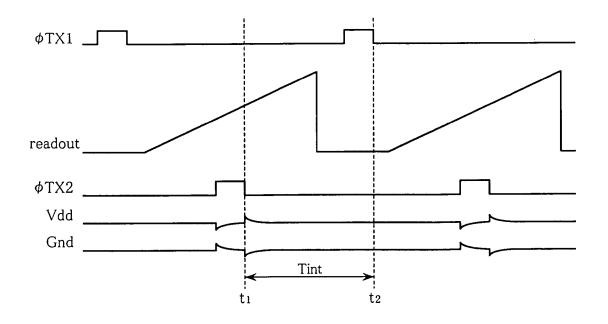

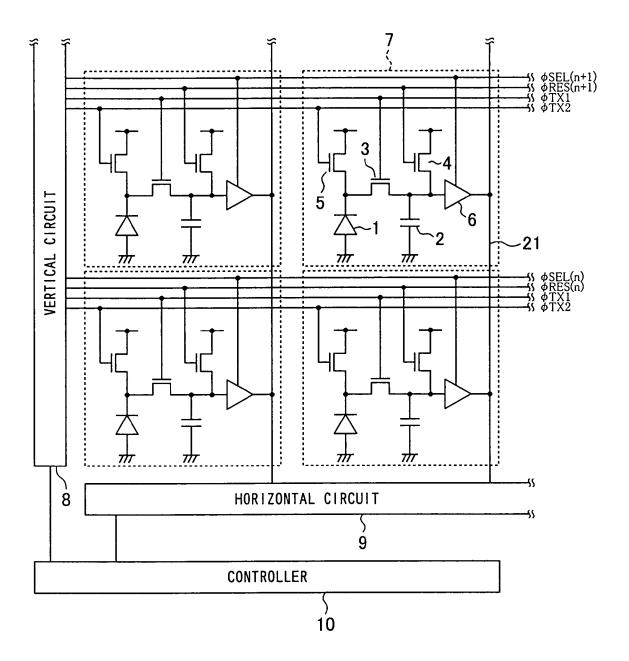

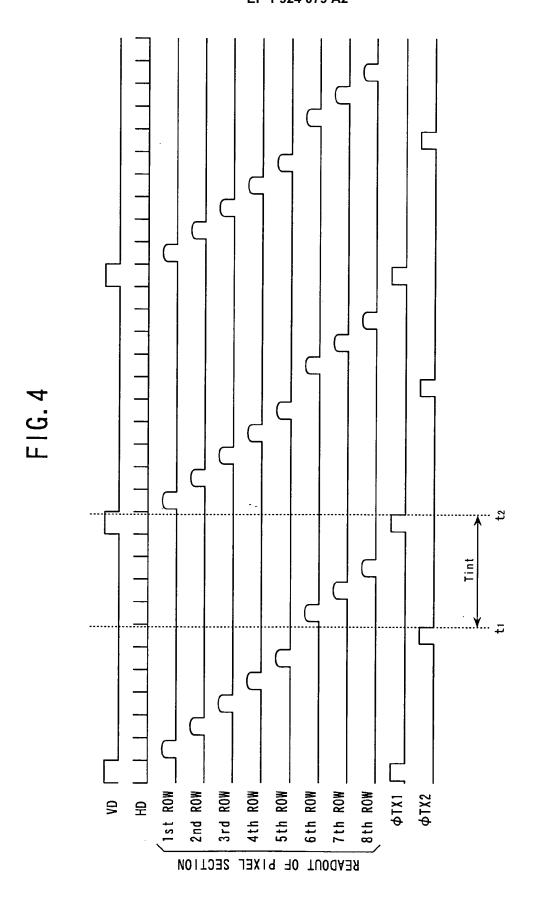

Fig.3 is a circuit diagram showing partially in blocks the construction of a first embodiment of the solid-state imaging apparatus according to the invention. Fig.4 is a timing chart for explaining operation of the solid-state imaging apparatus according to the first embodiment shown in Fig.3.

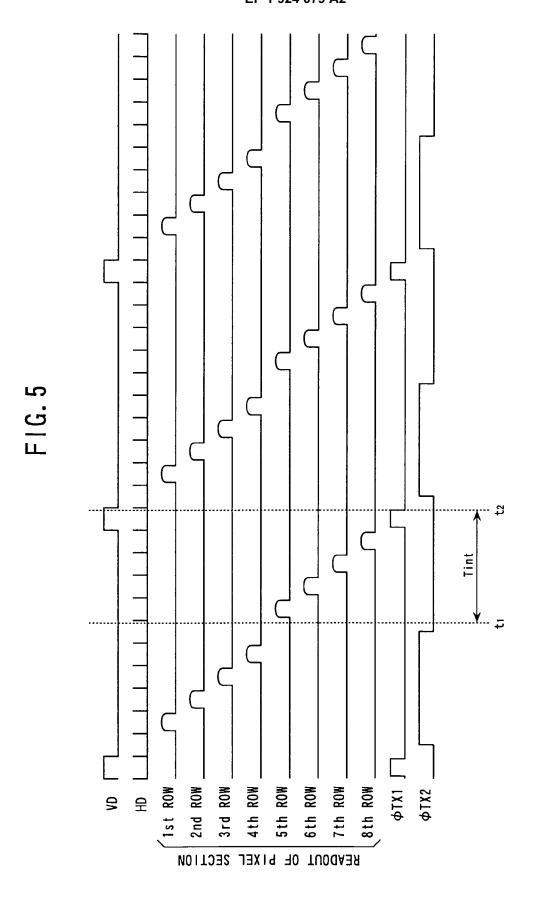

Fig.5 is a timing chart for explaining the conditions of temporary halt and restart of signal read operation from the pixel section in the first embodiment shown in Fig.3.

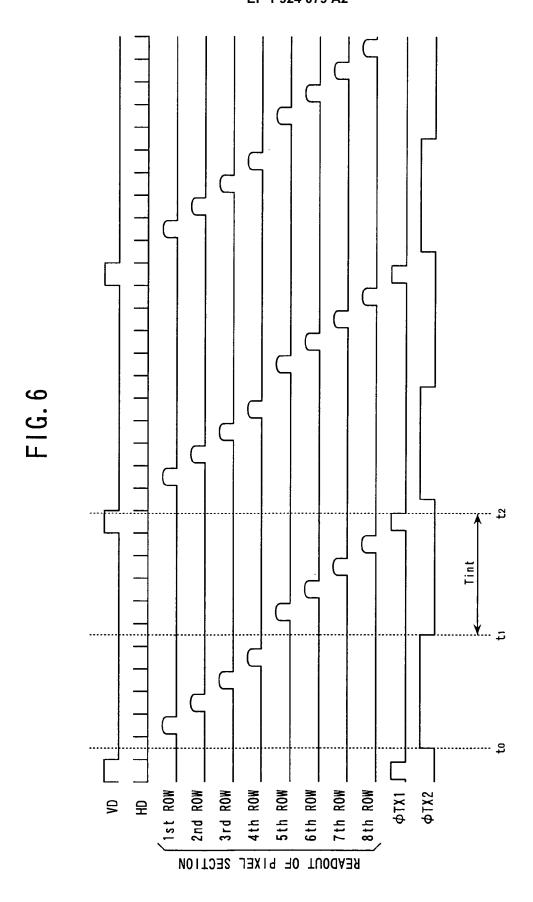

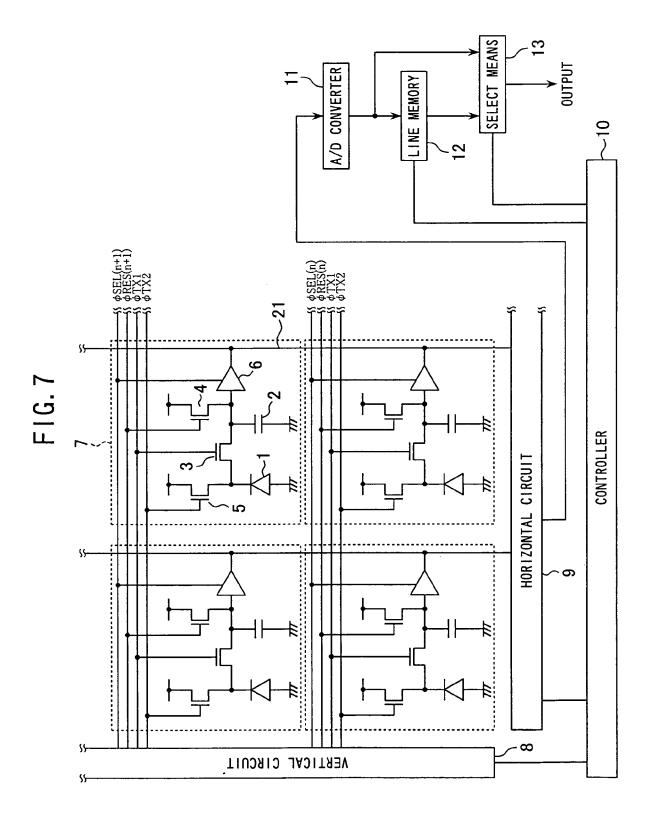

Fig.6 is a timing chart for explaining a modification of operation in the first embodiment shown in Fig.3. Fig.7 is a block diagram showing construction of the solid-state imaging apparatus according to a second embodiment of the invention.

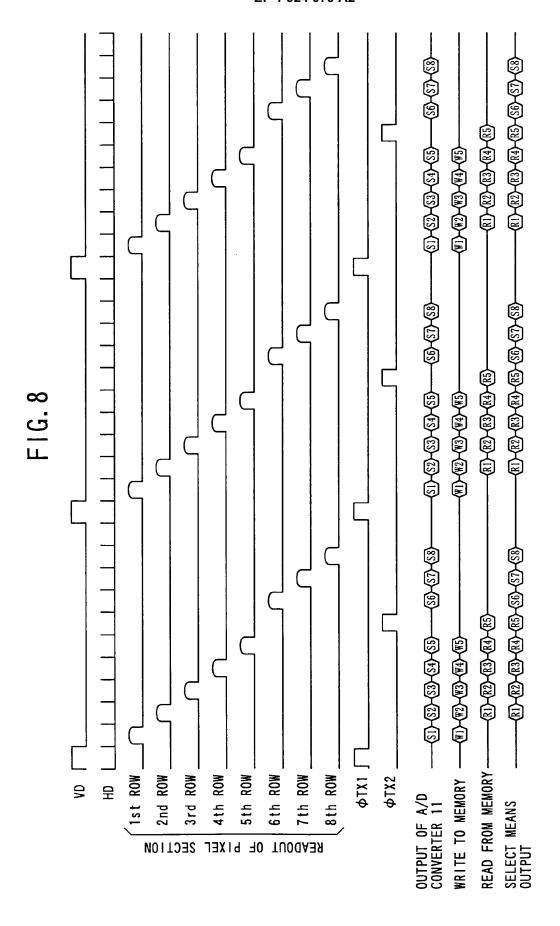

Fig.8 is a timing chart for explaining operation of the second embodiment shown in Fig.7.

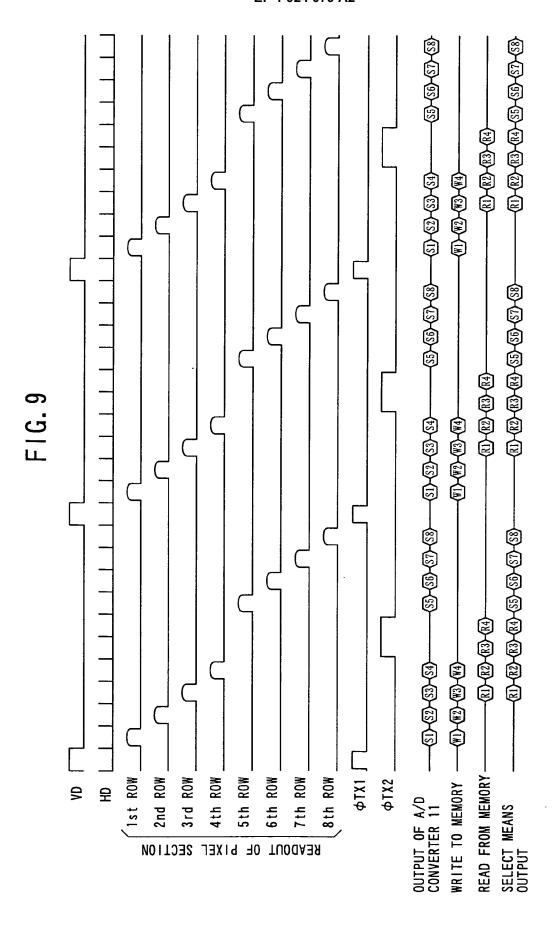

Fig.9 is a timing chart for explaining the conditions of temporary halt and restart of signal read operation from the pixel section in the second embodiment shown in Fig.7.

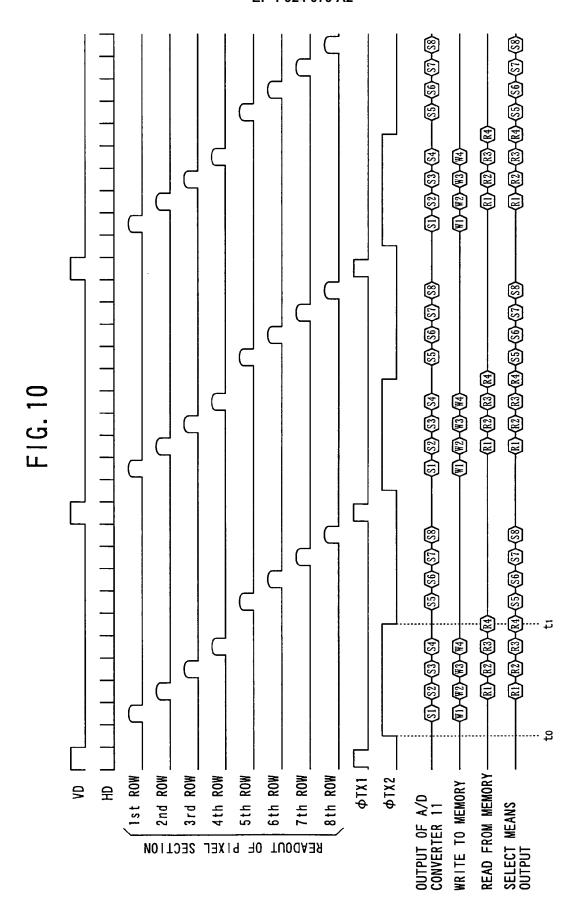

Fig. 10 is a timing chart for explaining a modification of operation in the second embodiment shown in Fig. 7.

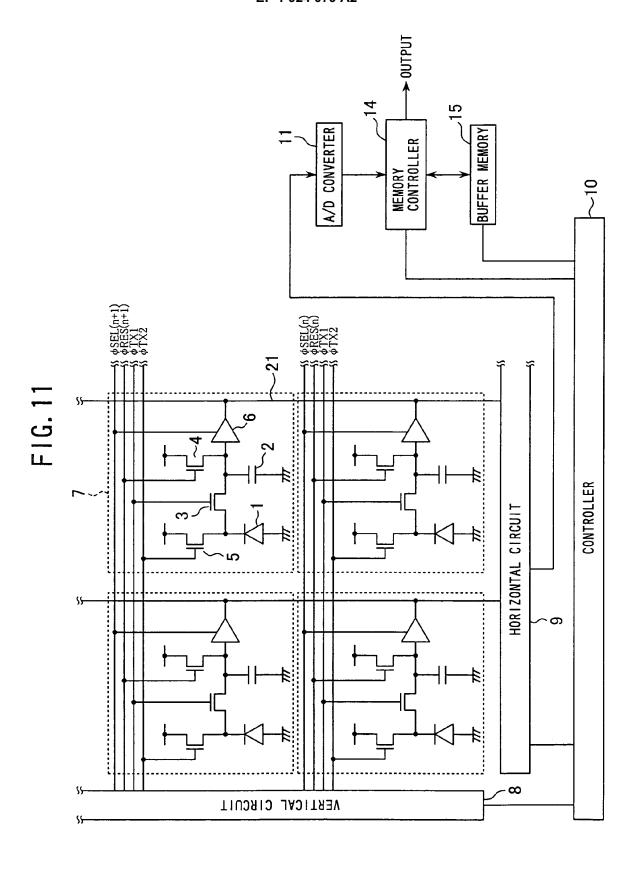

Fig.11 is a block diagram showing construction of the solid-state imaging apparatus according to a third embodiment of the invention.

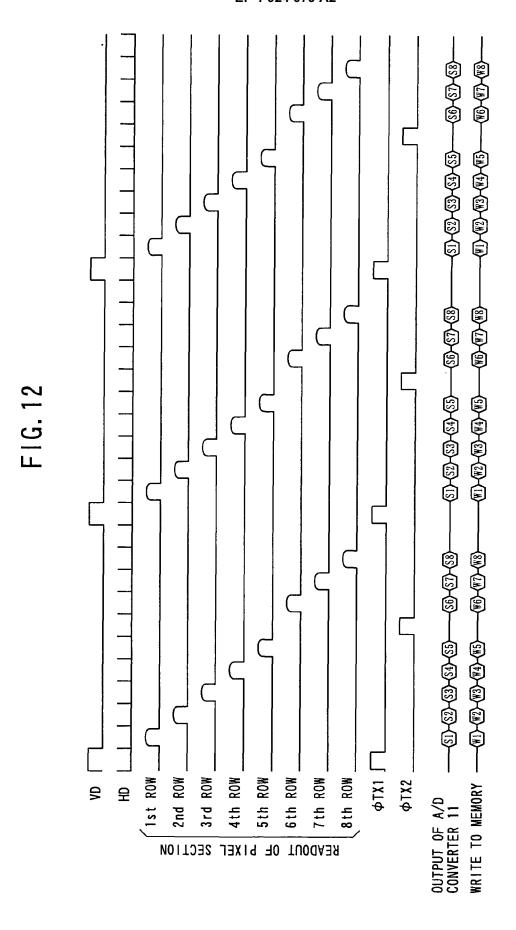

Fig.12 is a timing chart for explaining operation of the third embodiment shown in Fig.11.

Fig.13 explains a manner of thinned-out readout in the solid-state imaging apparatus according to a fourth embodiment of the invention.

Fig. 14 explains another manner of thinned-out readout in the fourth embodiment.

Fig.15 explains yet another manner of thinned-out readout in the fourth embodiment.

Fig.16 explains a manner of optional region readout in the fourth embodiment.

#### Description of the Preferred Embodiments

**[0016]** Some embodiments of the solid-state imaging apparatus according to the invention will be described below with reference to the drawings.

(Embodiment 1)

[0017] A first embodiment of the solid-state imaging apparatus according to the invention will now be described. Fig.3 is a schematic circuit block diagram of the solid-state imaging apparatus according to the first embodiment. Fig.3 includes: 1, a photoelectric conversion means such as a photodiode for receiving light for a predetermined time to accumulate photoelectric charge and effect its photoelectric conversion; 2, a memory means for retaining photoelectric charge of the photoelectric

20

35

40

45

50

conversion means 1; 3, a transfer means for transferring photoelectric charge of the photoelectric conversion means 1 to the memory means 2; 4, a reset means for resetting the memory means 2 to the potential of a power supply (corresponding to the first reset means of the above described aspects of the invention); 5, a discharging means for resetting the photoelectric conversion means 1 to the potential of a power supply (corresponding to the second reset means in the above described aspects of the invention); and 6, a read means for reading electric charge of the memory means 2. These means as described above constitute a unit pixel 7. A plurality of unit pixels each having such construction are two-dimensionally arranged to constitute a pixel section. Only a portion consisting of  $2 \times 2$  or 4 pixels is shown in the illustrated example. It should be noted that what is denoted by 21 in Fig.3 is a vertical signal line for outputting signal read out at the read means 6 of each unit pixel.

[0018] Also referring to Fig.3, what is denoted by 8 is a vertical circuit which outputs row by row of the pixel section a transfer control signal  $\phi$  TX1, reset control signal φ RES(n), discharging control signal φ TX2, and read control signal  $\phi$  SEL(n), respectively, for controlling ON/OFF of the transfer means 3, reset means 4, discharging means 5, and read means 6 of each unit pixel 7. [0019] It should be noted that suffix n in  $\phi$  RES(n) and φ SEL(n) represents the location of row. What is denoted by 9 is a horizontal circuit which selects a pixel column to be read for signal and outputs signal of the pixels associated with the pixel column. Denoted by 10 is a controller for applying to the vertical circuit 8, horizontal circuit 9, and other circuits the signals for controlling their operation, which is constructed so as to effect control in accordance with an externally set signal applied from an external section.

[0020] An operation of the solid-state imaging apparatus according to the first embodiment shown in Fig.3 will now be described with reference to a timing chart shown in Fig.4. As shown in Fig.4, the discharging control signal  $\phi$  TX2 is driven to H level concurrently for all pixels so that a concurrent reset operation of all pixels by the discharging means 5 is started. After passage of a predetermined time, the discharging control signal  $\phi$  TX2 is brought to low level concurrently for all pixels so that the concurrent reset operation of all pixels by the discharging means 5 is completed and exposure of all pixels is started (time point  $t_{\uparrow}$ ).

**[0021]** After passage of a predetermined exposure time, at the timing of a concurrent transfer of all pixels, the transfer means 3 of all pixels are concurrently turned ON by the transfer control signal  $\phi$  TX1. The photoelectric charges accumulated at the photoelectric conversion means 1 are thereby concurrently transferred to the memory means 2 so as to end the exposure (time point  $t_2$ ). Here, in the timing chart shown in Fig.4, a period indicated as Tint, i.e. period from  $t_1$  to  $t_2$  becomes an actual exposure period. Next after the end of the exposure, the read means 6 based on the read control signal

$\varphi$  SEL(n) is used to start read of signal level sequentially from the first row. The reset control signal  $\varphi$  RES(n) is used such as for the resetting of the memory means 2. It should be noted that, in Fig.4, VD represents a vertical synchronizing signal and HD horizontal synchronizing signal.

[0022] Here, in the present embodiment, the sequential read operation from the memory means 2 of each pixel 7 of the pixel section is temporarily halted by control of the controller 10 before the concurrent reset operation of all pixels by the discharging control signal of TX2. After completion of the concurrent reset operation of all pixels by the discharging control signal of TX2 i.e. after stabilization of fluctuation of the power supply side resulting from the concurrent reset operation, then, control is effected by the controller 10 so as to restart the read operation from the memory means 2 of the pixel section. In the illustrated example, after sequentially reading signal level up to the fifth row, the read operation is temporarily halted. After completion of the concurrent reset operation of all pixels by the discharging control signal of TX2, the read operation of signal level of the sixth row and after is restarted. It is possible with such operation to avoid a condition where fluctuation of power supply or GND resulting from the rendering of reset operation concurrently for all pixels affects readout signal from the memory means 2 of each pixel of the pixel section.

[0023] The conditions of temporary halt and restart of the signal read operation from the pixel section will now be described by way of a timing chart shown in Fig.5. The timing chart of Fig.5 shows the manner where the period of halting signal read from the pixel section exactly corresponds to 2 lines. Such line number may either be one line or be a plurality of lines. Control by the controller 10 is effected so that the period of halt becomes an integer multiple of 1 line period. In addition to the previously described advantage, there is an advantage that generation of synchronizing signal for driving the solid-state imaging apparatus becomes simpler and signal processing at subsequent stages is simplified.

[0024] A modification of operation in the first embodiment will now be described by way of a timing chart shown in Fig.6. The operation shown in the timing chart of Fig. 6 is different from the operation shown in Figs.4 and 5 in that, before reading signal from each pixel of the pixel section, the discharging control signal  $\phi$  TX2 is previously driven to H level concurrently for all pixels at time to within a vertical blanking period. In the operation of this modification, control by the controller 10 is effected so that reading of signal level with using the read means 6 based on the read control signal  $\phi$  SEL(n) is started sequentially from the first pixel row of the pixel section after completion of the rising operation of the discharging control signal  $\phi$ TX2. In addition, the read operation from the pixel section is temporarily halted before the falling operation of the discharging control signal of TX2. Control is then effected by the controller 10 so that, after time point t<sub>1</sub> where the concurrent discharging operation of all pixels by the fall-

ing operation of the discharging control signal  $\phi$  TX2 is complete, reading from the memory means 2 of the pixel section is started again.

[0025] It is possible with such operation to avoid a condition where fluctuation of power supply or GND resulting from the rendering of reset operation concurrently for all pixels affects readout signal from the memory means 2 of each pixel of the pixel section. In addition, the period of halting of read can be made to a minimum because it is possible to reduce the number of times of change in condition of the discharging control signal  $\phi$  TX2 in the period for halting read from the pixel section. Here, an advantage equivalent to the example of operation shown in Fig.5 is further obtained by making the delay time of start of read of the first row of the pixel section and/or halting period within the read period of the pixel section to 1 line period or an integer multiple of 1 line period.

#### (Embodiment 2)

[0026] A second embodiment of the solid-state imaging apparatus according to the invention will now be described by way of Fig.7. The difference in construction of the solid-state imaging apparatus according to the second embodiment from the solid-state imaging apparatus according to the first embodiment is as follows. In particular, there are additions of: A/D converter 11 for A/D conversion of signal read out from the read means 6 of each pixel through the horizontal circuit 9; a line memory 12 for delaying signal A/D-converted at the A/D converter 11; and a select means 13 for selecting between signals from the A/D converter 11 and the line memory 12. The operation of the line memory 12 and the select means 13 is controlled at the controller 10. The construction of the rest is identical to the first embodiment.

[0027] An operation of the solid-state imaging apparatus according to the second embodiment will now be described with reference to a timing chart shown in Fig.8. Referring to Fig.8, the blocks indicated as S1, S2, 53, ..., S8 in the section of "output of A/D converter 11" represent timings of the outputting of signals which are read out from the read means 6 of each pixel through each vertical signal line 21 and the horizontal circuit 9 and converted into digital signals at A/D converter 11. This timing chart shows the manner where the halting period of signal readout from the pixel section exactly corresponds to 1 line. Further, the line memory 12 is constructed so as to cause a delay corresponding to 1 line.

**[0028]** In the timing chart of Fig.8, the section of "write to memory" indicates the timings for writing output of the A/D converter 11 to the line memory 12 by W1, W2,  $\cdots$ , W5, and the section of "read from memory" indicates the timings of signal output delayed by the line memory 12 by R1, R2,  $\cdots$ , R5. Since control is effected by the controller 10 so that the delay time of the line memory 12 becomes 1 line period, the memory readout is outputted as shifted exactly corresponding to one line with respect to the memory write.

**[0029]** Here, the select means 13 is controlled by the controller 10 so that it selects signal of the line memory 12 until completion of the operation of the discharging control signal  $\phi$  TX2, and selects an output signal of the A/D converter 11 after completion of the operation of the discharging control signal  $\phi$  TX2. With such selecting operation, the timings of output of the select means 13 become consecutive R1, R2,  $\cdots$ , R5, S6, S7, S8. Accordingly, consecutiveness of signals is maintained so that it is possible to achieve simplification of signal processing at subsequent stages.

[0030] The conditions of temporary halt and restart of the signal read operation from the pixel section in the second embodiment will now be described by way of a timing chart shown in Fig.9. The timing chart of Fig.9 shows the manner where the period of halting the signal readout from the pixel section exactly corresponds to 2 lines. Such line number may either be one line or be a plurality of lines. Control by the controller 10 is effected so that the period of halt becomes an integer multiple of 1 line period, and the delay time of the line memory 12 is adjusted to be the same as the period during which signal readout is halted. In addition to the previously described advantage, it is thereby possible to obtain an advantage that a generation of synchronizing signal for driving the solid-state imaging apparatus becomes simpler and a signal processing at subsequent stages is further simplified.

[0031] A modification of operation in the second embodiment will now be described by way of a timing chart shown in Fig. 10. The difference of the operation shown in the timing chart of Fig. 10 from the operation shown in Figs.8 and 9 is in that, before reading signal from each pixel of the pixel section, the discharging control signal φ TX2 is previously driven to H level concurrently for all pixels at time to. In the operation of this modification, control by the controller 10 is effected so that read of signal level with using the read means 6 based on the read control signal  $\phi$  SEL(n) is started sequentially from the first pixel row of the pixel section after completion of the rising operation of the discharging control signal  $\phi$ TX2. In addition, the read operation from the pixel section is temporarily halted before the falling operation of the discharging control signal  $\phi$  TX2: The readout from the memory means 2 of the pixel section is then started again after time t<sub>1</sub> where the concurrent reset operation of all pixels by the falling operation of the discharging control signal  $\phi$  TX2 is complete, and control of write and read to and from the line memory 12 is effected by the controller 10.

**[0032]** It is possible with such operation to avoid a condition where fluctuation of power supply or GND resulting from the rendering of reset operation concurrently for all pixels affects readout signal from the memory means 2 of each pixel of the pixel section. In addition, the period of halting of read can be made to a minimum because it is possible to reduce the number of times of change in condition of the discharging control signal  $\phi$  TX2 in the

40

45

50

55

20

40

45

period for halting read from the pixel section. Here, an advantage equivalent to the example of operation shown in Fig.9 is further obtained by making the delay time of start of read of the first row of the pixel section and/or halting period within the read period of the pixel section to 1 line period or an integer multiple of 1 line period.

#### (Embodiment 3)

**[0033]** A third embodiment of the solid-state imaging apparatus according to the invention will now be described by way of Fig.11. The difference in construction of the solid-state imaging apparatus according to the third embodiment from the solid-state imaging apparatus according to the first embodiment is as follows. In particular, there are additions of: A/D converter 11 for A/D conversion of signal read out from the read means 6 of each pixel through the horizontal circuit 9; a buffer memory 15 for temporarily storing signals A/D-converted at the A/D converter 11; and a memory controller 14 for controlling the buffer memory 15. The operation of the memory controller 14 is controlled at the controller 10. The construction of the rest is identical to the first embodiment.

**[0034]** An operation of the solid-state imaging apparatus according to the third embodiment will now be described with reference to a timing chart shown in Fig.12. Referring to Fig.12, the blocks indicated as S1, S2, S3, ..., S8 in the section of "output of A/D converter 11" represent timings of the outputting of signals which are read out from the read means 6 of each pixel through the horizontal circuit 9 and converted into digital signal at A/D converter 11. This timing chart shows the manner where the halting period of signal readout from the pixel section exactly corresponds to 1 line.

**[0035]** In Fig.12, the section of "write to memory" indicates the timings of writing output of A/D converter 11 to the buffer memory 15 as W1, W2, · · · , W8, and the write to the buffer memory 15 is effected by the memory controller 14. Here, control is effected by the controller 10 so that the memory controller 14 effects the write to the buffer memory 15 within the period of signal readout from the pixel section while, on the other hand, stops the write to the buffer memory 15 in the period during which the signal readout is halted, and starts the write to the buffer memory 15 again upon restart of the signal readout.

[0036] With such operation, in addition to the previously described advantage according to the first embodiment, the consecutiveness of signals written to the buffer memory 15 is maintained so that it is possible to achieve simplification of the signal processing at subsequent stages. It should be noted that, while the second and third embodiments have been shown as those where A/D conversion is effected by A/D converter 11 on the output from the horizontal circuit 9, it is naturally also possible to obtain an equivalent advantage for example by construction where A/D conversion is effected with a column-by-column correspondence within the horizontal circuit 9.

(Embodiment 4)

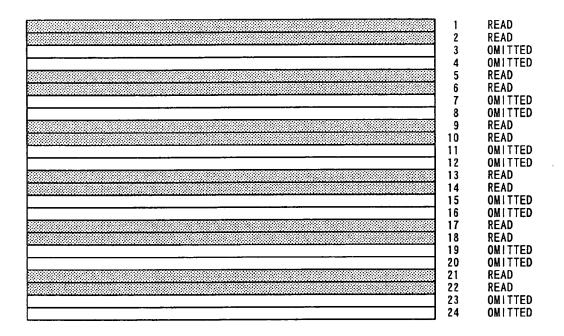

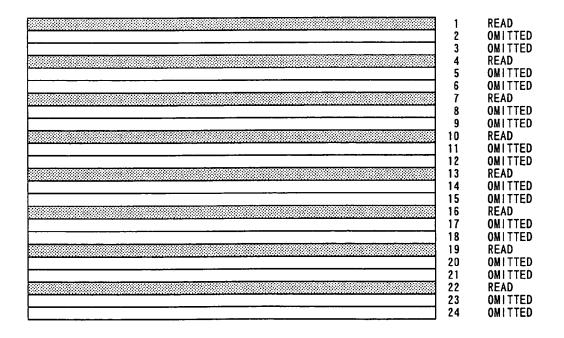

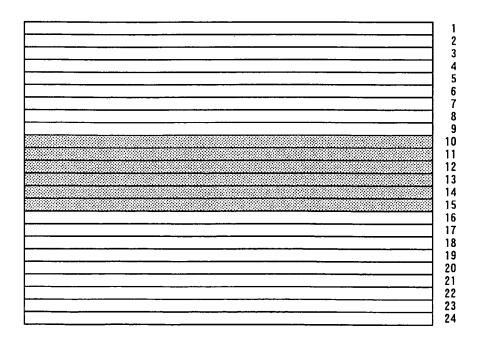

[0037] In the above described embodiments, the examples have been shown of construction where the invention is applied to one using a concurrent shutter method in readout of the entire region of a pixel section. The high-speed read methods of pixels, now, include thinned-out read and method of reading an optional partial region. In a fourth embodiment, the invention is applied to one using such read methods. It should be noted that the construction itself of the solid-state imaging apparatus in this embodiment is identical to those in the foregoing embodiments.

**[0038]** Fig. 13 explains the manner where the pixel section is read out with thinning out every other two rows. When such thinned-out read is effected, a reset operation of the unread pixel rows is usually also omitted. For this reason, the electric charges accumulated at the photoe-lectric conversion means such as photodiode sooner or later reach a saturation charge amount. The electric charges occurring in excess of the saturation charge amount flow for example into photoelectric conversion means of adjacent pixels and causes an occurrence of spurious signal at the adjacent pixels. To solve this problem, the reset operation by the discharging control signal Ø TX2 of the photoelectric conversion means is concurrently effected also for those pixel rows which are not read out in the thinned-out read operation.

**[0039]** Also in the case where the reset operation for a concurrent shutter operation is concurrently effected also for these pixel rows which are not read out in the thinned-out read operation as described, the present embodiment is constructed so that the read operation by the read means is temporarily halted in the manner shown in the above first to third embodiments when a concurrent reset operation is to be effected by the discharging control signal  $\phi$  TX2 during a read operation of signal based on the above concurrent shutter method. It is thereby possible to avoid an effect of fluctuation of power supply on readout signal so as to prevent deterioration of image quality.

**[0040]** Further, also in the case of thinned-out read of every third pixel as shown in Fig. 14 or of thinned-out read of combining every third pixel and every fifth pixel as shown in Fig. 15, the read operation by the read means is similarly halted so as to effect a concurrent reset operation by the discharging control signal  $\phi$  TX2 with including those pixel rows which are not read out.

**[0041]** Furthermore, also when an optionally selected partial region is to be read out as shown in Fig.16, a reset of the unread pixel rows usually is not effected, whereby the electric charges accumulated at photoelectric conversion means of such unread pixel rows reach a saturation electric charge amount sooner or later after photoelectric conversion. The electric charges occurring in excess of the saturation charge amount then flow for example into adjacent photoelectric conversion means and causes an occurrence of spurious signal in adjacent pix-

55

30

35

40

45

50

55

els.

**[0042]** To prevent this, the reset operation by the discharging control signal  $\phi$  TX2 of the photoelectric conversion means is effected also on the unread pixel rows or on peripheral pixels rows of the optional readout region (for example lines 8~9 and lines 16~17 in the illustrated example where the readout region is determined as lines 10 to 15).

[0043] Also in the case where the reset operation for concurrent shutter operation is concurrently effected as the above also on those pixel rows which are not read out in the optional region read operation or on peripheral pixel rows of an optional region to be read, the present embodiment is constructed to temporarily halt the read operation by the read means in the manner shown in the above first to third embodiments when a concurrent reset operation is effected by the discharging control signal  $\phi$  TX2 during a read operation of signals based on the above concurrent shutter method. It is thereby possible to similarly avoid an effect of fluctuation of power supply on readout signal so as to prevent deterioration of image quality.

[0044] According to the invention as has been described by way of the above embodiments, when a concurrent reset by the second reset means is to be effected in a period for read by the read means, a control by the controller is effected so that a read by the read means is temporarily halted at least at one or the other of the timings of start and release of the concurrent reset by the second reset means. An effect on readout signal caused by fluctuation of power supply and/or GND occurring due to the rendering of the reset operation concurrently for all pixels is thereby avoided to prevent a deterioration of an image quality.

#### Claims

1. A solid-state imaging apparatus comprising:

a pixel section having two-dimensionally arranged pixels, each having a photoelectric conversion means, a memory means for storing a photoelectric conversion signal of said photoelectric conversion means, a transfer means for transferring said photoelectric conversion signal to said memory means, a first reset means for resetting said memory means, a second reset means driven independently from the first reset means for resetting said photoelectric conversion means, and a read means for reading the photoelectric conversion signal of said memory means; and

a controller for effecting a control so that, after passage of a predetermined time subsequently to the rendering of a concurrent reset by said second reset means on said photoelectric conversion means of all pixels in a read subject region, a transfer of said photoelectric conversion signal is concurrently effected by said transfer means from said photoelectric conversion means to said memory means of all pixels in said read subject region, and a reading of said photoelectric conversion signal stored at said memory means is effected by said read means, wherein when said concurrent reset by said second reset means is effected in a period during which the reading by said read means is effected, the reading by said read means is temporarily halted at least at one or the other of timings of a start and a release of the concurrent reset by said second reset means.

- The solid-state imaging apparatus according to claim 1, wherein said controller sets a period of said temporary halt by a unit of readout line of said pixel section.

- 3. The solid-state imaging apparatus according to claim 1, wherein said controller causes reading by said read means to be effected in a period, after a predetermined period from the start of the concurrent reset by said second reset means, to the release of the concurrent reset by said second reset means.

- 4. The solid-state imaging apparatus according to claim 3, wherein said controller sets the start of the concurrent reset by the second reset means within a vertical blanking period.

- **5.** The solid-state imaging apparatus according to claim 1, wherein said controller causes the concurrent reset by said second reset means to be effected with including a region not subjected to reading outside the read subject region.

- 6. The solid-state imaging apparatus according to any one of claims 1 to 5 further comprising an A/D converter for converting said photoelectric conversion signal into a digital signal, a line memory for effecting a delay of said digital signal for a period corresponding to the period of said temporary halt, and a select means for selecting between an output of said A/D converter and an output of said line memory, wherein said controller controls said select means so that an output of said line memory is selected and outputted until a release of said temporary halt and an output of said A/D converter after the release.

- 7. The solid-state imaging apparatus according to any one of claims 1 to 5 further comprising an A/D converter for converting said photoelectric conversion signal into a digital signal, and a buffer memory for transiently storing said digital signal, wherein said controller causes to halt the storing of said digital signal to said buffer memory for a period

corresponding to the period of said temporary halt.

FIG. 1

FIG. 2

FIG. 3

## FIG. 13

# FIG. 14

FIG. 15

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | READ OMITTED OMITTED READ OMITTED OMITTED OMITTED OMITTED COMITTED OMITTED OMITTED OMITTED OMITTED OMITTED OMITTED OMITTED |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 12<br>13<br>14<br>15                      | READ<br>OMITTED<br>OMITTED<br>OMITTED<br>OMITTED                                                                           |

| 17<br>18<br>19                            | READ<br>OMITTED<br>OMITTED                                                                                                 |

| 20<br>21<br>22<br>23<br>24                | READ<br>OMITTED<br>OMITTED<br>OMITTED<br>OMITTED                                                                           |

FIG. 16

### EP 1 924 079 A2

#### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

### Patent documents cited in the description

• JP HEI11261896 A [0002]