# (11) **EP 1 990 699 A1**

(12)

### **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

12.11.2008 Bulletin 2008/46

(51) Int Cl.: **G05F** 3/24 (2006.01)

(21) Application number: 07009255.6

(22) Date of filing: 08.05.2007

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC MT NL PL PT RO SE SI SK TR

**Designated Extension States:**

AL BA HR MK RS

(71) Applicant: austriamicrosystems AG 8141 Unterpremstätten (AT)

(72) Inventor: Taylor, Robert 8042 Graz (AT)

(74) Representative: Epping - Hermann - Fischer Patentanwaltsgesellschaft mbH Ridlerstrasse 55 80339 München (DE)

### (54) Current generation circuit and current generation method

(57) A current generation circuit comprises a reference unit (10) providing a reference voltage (VREF), and a current control unit (20) comprising a first and the second current terminal (201, 202). The current control unit (20) is configured to control a current (IC) between a first and a second current terminal (201, 202) depending on the reference voltage (VREF). A first and a second charge store (C1, C2) each have a first and a second

terminal (311, 312, 321, 322), wherein the first terminals (311, 321) can be coupled to the first current terminal (201) or to the second terminal (312, 322) of the respective charge store (C1, C2) depending on a switching signal. The current mirror (40) comprises an input (401) which is coupled to the second current terminal (202) and an output (402) which is coupled to an output (1) of the current generation circuit.

Fig. 1

EP 1 990 699 A

#### Description

20

30

35

40

45

50

55

[0001] The invention relates to a current generation circuit and a current generation method.

**[0002]** In many electronic applications it is desirable to have currents which are largely independent of temperature. For example, an electrical sensor in a measuring application can be supplied with such a current to achieve a measurement result being largely temperature independent. A temperature dependency can be expressed by a temperature coefficient which denotes the relative change of the respective value when the temperature is changed.

**[0003]** To generate temperature independent currents, for example electronic circuits are used which comprise an external resistor having a low temperature coefficient. Such a resistor usually cannot be integrated into an integrated circuit. Furthermore, such a resistor increases the costs of the electronic circuit. Other resistors which are integrable into an integrated circuit typically have a high temperature coefficient.

**[0004]** It is an object of the invention to provide a current generation circuit which has a low temperature dependency and can be produced with less effort. It is a further object of the invention to provide a method for generating a current with a low temperature dependency and less effort.

[0005] The object is achieved with the subject matter of the independent patent claims.

[0006] In one embodiment of a current generation circuit, the circuit comprises a reference unit, a current control circuit, a first and a second charge store and a current mirror. The reference unit comprises a first reference output configured to provide a first reference voltage. The current control unit comprises a first and a second current terminal and is configured to control a current between the first and the second current terminal depending on the first reference voltage. The first and the second charge store each have a first and a second terminal. Said first terminals can be individually coupled to the first current terminal or to the second terminal of the respective charge store depending on a switching signal. The current mirror comprises an input and an output, wherein the input is coupled to the second current terminal and the output is coupled to a current output of the current generation circuit.

[0007] During operation of the current generation circuit, the reference unit generates the reference voltage which controls a current between the first and the second current terminal of the current control unit. The first and the second charge store are alternately coupled to the first current terminal depending on the switching signal for alternately charging the first charge store or the second charge store. During charging one of the first and the second charge stores, the other one of the charge stores is at least partially discharged by coupling its first terminal to its respective second terminal. For example, the current between the first and the second current terminal is controlled such that the first and the second charge store are charged to the first reference voltage or to a voltage depending on the first reference voltage. In one embodiment the current control unit comprises a regulated cascode circuit for controlling the current between the first and the second current terminal. In another embodiment the current control unit comprises a voltage regulator controlling the voltage at the first current terminal.

**[0008]** The charging current for the first and the second charge store is also provided to the current mirror which on its input side is coupled to the second current terminal. The current mirror amplifies the charging current and provides the amplified current as the output current of the current generation circuit.

**[0009]** The first and the second charge store can each comprise a first temperature dependency. In other words, a capacitance value of the first and the second charge store can depend on the temperature. For example, the first and the second charge store each comprise a first temperature coefficient. In this case, the reference unit can be configured to generate the reference voltage with a second temperature dependency which is opposite to the first temperature dependency or has a temperature coefficient which has an opposite value of the temperature coefficient of the first and the second charge store. As the charging current for the first and the second charge store depends on the reference voltage, variations of the capacitance values of the charge stores are compensated for by the variations of the reference voltage. Therefore, the charging current and the amplified output current which both depend on the reference voltage and the capacitance of the charge stores are basically temperature independent.

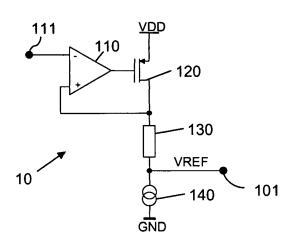

**[0010]** Possible ripples in the charging current resulting from switching between charging and discharging the charge stores can be filtered out by the current mirror which usually comprises transistors having resistive and capacitive properties or elements which result in a low pass filtering.

**[0011]** Therefore, with an embodiment of a current generation circuit, a current with a low temperature dependency can be generated. As the elements of the current generation circuit can easily be integrated into an integrated circuit, the current generation circuit can be produced with little effort.

[0012] In an embodiment of a current generation method, a reference voltage is generated. During a first time period, a charging current is generated by charging a first charge store depending on the reference voltage, whereas a second charge store is discharged. During a second time period, the charging current is generated by charging a second charge store depending on the reference voltage, whereas the first charge store is discharged. The charging current is amplified and provided as an output current. According to an embodiment the first and the second time period alternate periodically.

[0013] As the reference voltage, for example, can be generated with a temperature dependency, a temperature dependency of the charge stores can be compensated for. Therefore, the output current comprises a low or zero temperature

dependency.

20

30

35

40

45

50

55

**[0014]** In one embodiment, charging and discharging of the charge stores can be performed according to a switched capacitor principle, resulting in the temperature independent output current. In other words, the first and the second charge store can be switched capacitors. In this case a temperature dependency of the reference voltage is selected such that a temperature dependency of the switched capacitors can be compensated for.

**[0015]** In another embodiment the reference unit comprises a second reference output configured to provide a second reference voltage which is basically temperature independent. For example, a voltage generated by a sensor which is driven by the temperature independent output current provided by the current generation circuit can be compared to the second reference voltage, making also the comparison result basically temperature independent.

[0016] The text below explains the invention in detail using exemplary embodiments with reference to the drawings, in which:

- Figure 1 shows a first embodiment of a current generation circuit,

- 15 Figure 2 shows an exemplary timing diagram of a switching signal,

- Figure 3 shows an embodiment of a clock generator,

- Figure 4 shows an embodiment of a reference unit,

- Figure 5 shows a second embodiment of a current generation circuit, and

- Figure 6 shows an embodiment of a current mirror.

- [0017] Like reference numerals designate corresponding similar parts or elements.

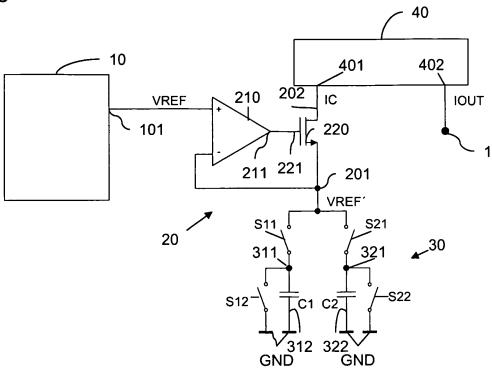

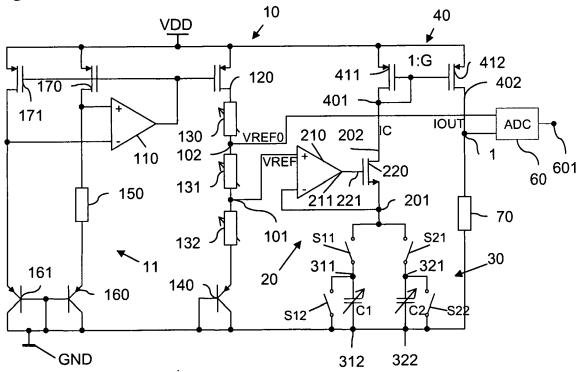

[0018] Figure 1 shows an embodiment of a current generation circuit comprising a reference unit 10 which comprises a first reference output 101 configured to provide a first reference voltage VREF. A current control unit 20 comprises a differential amplifier 210 having a first, non-inverting input (+) which is coupled to the first reference output 101. An output 211 of the differential amplifier 210 is coupled to a control input 221 of a cascode transistor 220. The current path of the cascode transistor 220 is coupled between a first current terminal 201 and a second current terminal 202. The first current terminal 201 is furthermore coupled to a second, inverting input (-) of the differential amplifier 210. In other words, the current control unit 20 comprises a regulated cascode circuit for controlling the current between the first and the second current terminal 201, 202. The regulated cascode circuit is formed by the differential amplifier 210 and the cascode transistor 220. The current control unit 20 can be utilized as a voltage regulator controlling the voltage at the first current terminal 201.

**[0019]** A charge store arrangement 30 comprises a first and a second charge store C1, C2 and switching elements S11, S12, S21, S22. A first terminal 311 of the first charge store C1 is coupled to the first current terminal 201 via the switching element S11. The first terminal 311 is further coupled to the second terminal 312 of the first charge store C1 via a switching element S12 by means of a ground potential terminal GND. Accordingly, the first terminal 321 of the second charge store C2 is coupled to the first current terminal 201 via the switching element S21 and to its second terminal 322 via the switching element S22 and the ground potential terminal GND.

**[0020]** The current generation circuit further comprises a current mirror 40 comprising an input 401 coupled to the second current terminal 202. An output 402 of the current mirror 40 is coupled to the current output 1 of the current generation circuit.

**[0021]** The reference unit 10 generates the reference voltage VREF which is provided to the current control unit 20. The differential amplifier 210 generates an output signal which controls a current through the cascode transistor 220 such that a voltage VREF' at the first current terminal 201 which is provided to the inverting input (-) of the differential amplifier 210 is basically identical to the first reference voltage VREF. In other words the voltage VREF' is controlled by the current control unit 20. This is also the case if a voltage across the cascode transistor 220 changes, for example caused by a variation of a supply voltage.

**[0022]** During a first time period, the switching elements S11 and S22 are in a closed state, whereas the switching elements S12 and S21 are in an open state. As a result, the first charge store C1 is provided with a charging current IC through the cascode transistor 220 for charging the first charge store C1 up to the first reference voltage VREF. The second charge store C2 is discharged through the closed switching element S22.

**[0023]** For a second time period the switching elements S11, S12, S21, S22 change their state such that during said second time period the switching elements S11 and S22 are in an open state and the switching elements S12 and S21 are in a closed state. Accordingly, the second charge store C2 is provided with the charging current IC and charged up to the first reference voltage VREF, whereas the first charge store C1 is discharged through the switching element S12.

A further, following time period can be similar to the first time period.

**[0024]** By alternately charging and discharging the first and the second charge store, the charging current IC is generated both during the first and the second time period. In other words, a continuous charging current IC is generated by the switched charging and discharging of the charge stores C1, C2.

**[0025]** The charging current IC is amplified by the current mirror 40 and provided as an output current IOUT at the current output 1. The current mirror 40 usually comprises transistors having as well resistive and capacitive properties. Therefore, the current mirror 40 can perform a filtering of the charging current IC together with the amplification, wherein the filtering is comparable to a RC-low pass filtering. In other words, the current mirror 40 also smoothes the charging current IC which can comprise ripples because of the switching operations.

**[0026]** In one embodiment, the charge stores C1, C2 can comprise capacitors which can be integrated into an integrated circuit. For example, the capacitors can be metal-insulator-metal (MIM) capacitors or other capacitors having polysilicon as an insulator. Also varactors, especially MOS varactors, can be used for the charge stores. In this case, the capacitance value of the first and the second charge store C1, C2 can be adjusted. Usually, the capacitance of the first and the second charge store has the same nominal value.

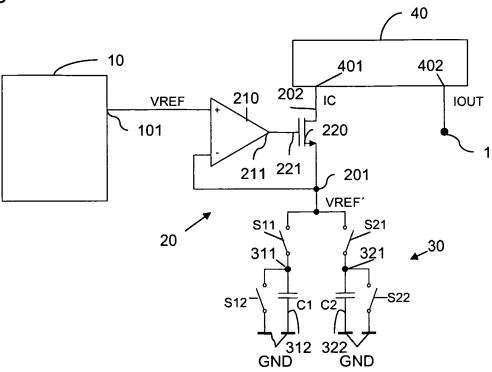

[0027] Figure 2 shows a timing diagram of a switching signal which can be used in the embodiment shown in Figure 1. The upper signal shows a first component of the switching signal for controlling the switching elements S11, S22 whereas the lower signal corresponds to a second component for controlling the switching elements S12, S21. Accordingly, during a first time period T1, the first component is in a high state and the second component is in a low state. During a second time period T2, the first component is in a low state and the second component is in a high state. Further time periods correspond to the first and the second time period T1, T2. In other words, the first time period T1 and the second time period T2 temporally alternately succeed one another. In this embodiment, the first and the second time period T1, T2 have the same length. Therefore, a clock frequency f of the switching signal corresponds to f = 1/(T1+T2). In one embodiment the switching signals have a non-overlapping high state such that only one of the charge stores C1, C2 is being charged at the same time. In other words it is possible that both switching signals are in a low state at the same time.

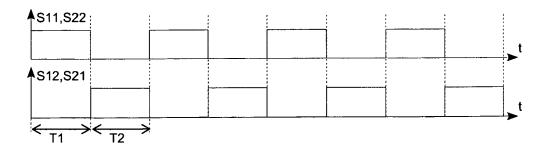

**[0028]** Figure 3 shows an embodiment of a clock generator 50 comprising a generator circuit 500 having a control input 501 and a clock output 502, at which a square wave clock signal CLK is generated. Furthermore, a synchronizer 503 is provided which is coupled to the clock output 502 and used for generating the switching signal component for controlling the switching elements S11, S22 and the switching signal component for controlling the switching elements S12, S21 from the clock signal CLK. As mentioned before, the switching signals can have a non-overlapping waveform. **[0029]** For example, the generator circuit 500 can be any kind of oscillator like a voltage controlled oscillator or a digitally controlled oscillator or even an uncontrolled oscillator. By using a controlled oscillator, a clock frequency of the switching signal can be programmed, for example by a control signal or a control word at the control input 501.

[0030] In another embodiment the clock generator 50 can be any kind of non-overlapping clock waveform generator.

[0031] The switching signal can also be derived from the clock signal of a reference oscillator like a crystal oscillator.

[0032] Referring back to Figure 1, the output current IOUT can be calculated by

$$10UT = 2 \cdot C \cdot VREF \cdot f \cdot G, \tag{1}$$

wherein C is the capacitance value of the first and the second charge store C1, C2, f is the clock frequency of the switching signal and G is the current gain of the current mirror circuit 40.

**[0033]** The capacitance value C of the first and the second charge store C1, C2 can comprise a temperature dependency which can be expressed by a temperature coefficient  $TC_{CAP}$  which in one embodiment has a positive value. In other words, the capacitance value C increases with an increasing temperature.

[0034] Accordingly, the reference unit 10 can comprise a bandgap circuit in one embodiment for providing a bandgap voltage. The reference voltage VREF also having a temperature dependency can be derived from said bandgap voltage. The temperature coefficient  $TC_{VREF}$  of the reference voltage VREF is opposite to the temperature coefficient  $TC_{CAP}$  of the charge stores C1, C2. For example, if the temperature coefficient  $TC_{CAP}$  has a positive value, the temperature coefficient  $TC_{VREF}$  of the reference voltage VREF has a negative value. As the output current IOUT according to equation (1) depends both on the capacitance C and the reference voltage VREF, a temperature coefficient of the output current  $TC_{IOUT}$  can be calculated as

55

10

20

25

30

35

45

50

$$TC_{IOUT} = TC_{VREF} + TC_{CAP}.$$

(2)

5

20

30

35

40

45

50

55

**[0035]** It is desirable to adapt or trim the temperature coefficient  $TC_{VREF}$  of the reference unit 10 such that the output current temperature coefficient  $TC_{IOUT}$  becomes basically zero. In other words, the temperature coefficient  $TC_{CAP}$  of the charge stores C1, C2 can be compensated for by the temperature coefficient  $TC_{VREF}$  of the reference unit 10 such that the output current IOUT is basically independent of the temperature.

**[0036]** With reference to Figure 3 and equation (1), a value for the output current IOUT can also be adjusted by varying the clock frequency f of the switching signal in the clock generator 50.

[0037] Figure 4 shows an exemplary embodiment of a reference unit 10. The reference unit 10 comprises an operational amplifier 110 which on its output side is coupled to a transistor 120. An inverting input (-) is coupled to a reference input 111 and a non-inverting input (+) is coupled to a source connection of the transistor 120. A drain connection of the transistor 120 is coupled to a supply voltage terminal VDD. The reference unit 10 further comprises a resistor 130 and a temperature dependent current source 140 which are connected in series between the source connection of the transistor 120 and a ground potential terminal GND. The first reference output 101 is coupled to a connection node of the resistor 130 and the current source 140.

**[0038]** At the reference input 111 a temperature independent voltage is provided, that means having a temperature coefficient being basically equal to zero. The operational amplifier 110 controls a current through the transistor 120 such that a voltage at its source connection is equal to the voltage at the reference input 111.

[0039] The current source 140 can be a Proportional To Absolute Temperature (PTAT) current source having a negative temperature coefficient. The reference voltage VREF at the first reference output 101 depends on the voltage drop across the resistor 130. Because of the temperature dependent current through the PTAT current source 140, said voltage drop and therefore the reference voltage VREF are also depending on the temperature. In other words, as the voltage at the upper side of the resistor 130 is kept at a constant voltage value which has a temperature coefficient basically being equal to zero, the voltage across the resistor 130 is a PTAT voltage which has a negative temperature coefficient that can be altered by varying the resistance of the resistor 130. As a consequence, by varying the resistance of the resistor 130, the temperature coefficient  $TC_{VREF}$  of the reference voltage VREF can be selected or adjusted such that the temperature coefficient  $TC_{CAP}$  of the charge stores C1, C2 can be compensated for. The voltage at the reference input 111 can, for example, be generated by a bandgap circuit.

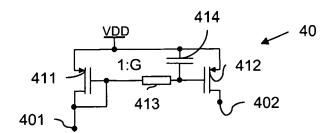

[0040] Figure 5 shows another embodiment of a current generation circuit. According to the embodiment shown in Figure 1, the current generation circuit comprises a current control unit 20, a charge store arrangement 30 and a current mirror 40. The current mirror 40 comprises a first transistor 411 which is used as an input transistor coupled to the current input 401. A second transistor 412 is used as an output transistor coupled to the current output 402. For example, a channel width-length ratio between the first and the second transistor 411, 412 is 1:G, that means the output current IOUT is larger than the input current IC by the factor G.

**[0041]** The current generation circuit further comprises a reference unit 10. The reference unit 10 comprises a bandgap circuit 11, the transistor 120, resistive elements 130, 131, 132 and a PTAT current source which is formed by the transistor 140. The bandgap circuit 11 comprises transistors 160, 161, a resistor 150, the operational amplifier 110 and transistors 170, 171. The transistors 170, 171 are controlled together with the transistor 120 by the operational amplifier 110 and act as current sources for the transistors 160, 161 which generate a bandgap voltage at the inputs (+, -) of the operational amplifier 110.

[0042] Through the resistive elements 130, 131, 132 and the PTAT current source 140, the first reference voltage VREF at the first reference output 101 and a second reference voltage VREF0 at a second reference output 102 are generated or derived from the bandgap voltage respectively. In this embodiment, the first reference voltage VREF has a negative temperature coefficient  $TC_{VREF}$  for compensating the temperature coefficient  $TC_{CAP}$  of the charge stores C1, C2. The second reference voltage VREF0 is generated temperature independent, in other words with a temperature coefficient being basically equal to 0. A different number of resistive elements can be provided in the reference unit 10 for deriving the first and/or the second reference voltage VREF, VREF0.

[0043] In the circuit shown in Figure 5, additionally a sensor element 70 and an analog-to-digital converter 60 are provided which are not part of the current generation circuit but are used as an application example for the current generation circuit. The sensor element 70, for example, comprises a resistive element which is coupled between the current output 1 of the current generation circuit and the ground potential terminal GND. A resistance of the sensor element 70, for example, depends on the respective value to be sensed. Accordingly, a voltage drop across the sensor element 70 is generated employing the output current IOUT generated by the current generation circuit. As the output current IOUT is independent of the temperature, said voltage drop basically depends on the value to be sensed, namely the respective sensor resistance. The potential or voltage at the current output 1 is compared to the second reference

voltage VREF0 within the analog-to-digital converter 60 and converted into a digital output word at an output 601 of the analog-to-digital converter 60.

[0044] In this embodiment, the capacitance values of the charge stores C1, C2 can be adjusted, for example for fine-tuning the charging current IC or the output current IOUT, respectively.

**[0045]** Furthermore, in this embodiment, the resistive elements 130, 131, 132 can be adjusted or trimmed regarding their respective resistance to adapt the reference voltages VREF, VREF0 which also results in an adaptation of the respective temperature coefficients of the reference voltages VREF, VREF0.

**[0046]** The transconductance (gm) of the transistor 411 of the current mirror 40 and the gate-source-capacitance of the transistor 412 form an RC filter which can inherently be used for smoothing possible ripples in the charging current IC. Therefore, the transconductance of the transistor 411 and the gate-source-capacitance of the transistor 412 act as filtering elements comprised by the current mirror 40.

[0047] Figure 6 shows an embodiment of a current mirror circuit 40 comprising the first and the second transistor 411, 412. In this embodiment, the gate connection of the second transistor 412 is coupled to the supply voltage terminal VDD via a capacitor 414. Furthermore, an additional resistive element 413 is coupled between the gate connections of the first and the second transistor 411, 412. The resistor 413 and the capacitor 414 act as filtering elements which increase a filtering or smoothing effect provided by the transconductance and the gate-source-capacitance of the transistors 411, 412 as mentioned above. Furthermore, a cutoff frequency of the low pass filter comprised by the current mirror 40 can be adjusted or determined according to the clock frequency f of the switching signal controlling the charge store arrangement 30.

[0048] A temperature dependency of the charge stores C1, C2 is usually smaller than a temperature dependency of an on-chip resistor used in a conventional current generation circuit. Therefore, the temperature coefficient TC<sub>CAP</sub> of the charge stores C1, C2 can be compensated for by the reference voltage VREF also having a small temperature coefficient TC<sub>VRFF</sub> which has an opposite value to the temperature coefficient TC<sub>CAP</sub>.

**[0049]** It may be desirable that the reference voltage VREF is generated with a linear temperature dependency by the reference unit 10 or, in other words, that the reference voltage VREF increases linearly with increasing temperature. For example the reference unit 10 comprises a circuit for a curvature correction for providing the linear temperature dependency.

**[0050]** A current generation circuit according to one of the embodiments described above can easily be integrated into an integrated circuit without the need for any external elements. Therefore, such integrated circuits can be produced with little effort.

List of references

#### [0051]

20

30

35

|    | 1                  | current output              |

|----|--------------------|-----------------------------|

|    | 10                 | reference unit              |

| 40 | 20                 | current control unit        |

|    | 30                 | charge store arrangement    |

| 45 | 40                 | current mirror              |

| 40 | 50                 | clock generator             |

|    | 60                 | analog-to-digital converter |

| 50 | 70                 | sensor                      |

|    | 101, 102           | reference output            |

| 55 | 110                | operational amplifier       |

| 33 | 120                | transistor                  |

|    | 130, 131, 132, 150 | resistive element           |

|    | 140                | current source            |

|----|--------------------|---------------------------|

|    | 160, 161, 170, 171 | transistor                |

| 5  | 201, 202           | current terminal          |

|    | 210                | differential amplifier    |

| 40 | 211                | output                    |

| 10 | 220                | cascode transistor        |

|    | 221                | control input             |

| 15 | 311, 312, 321, 322 | charge store terminals    |

|    | 401                | current input             |

| 20 | 402                | current output            |

| 20 | 411, 412           | transistor                |

|    | 413, 414           | filtering element         |

| 25 | 500                | generator circuit         |

|    | 501                | control input             |

| 30 | 502                | clock output              |

| 30 | 503                | synchronizer              |

|    | 601                | data output               |

| 35 | C1, C2             | charge store              |

|    | S11, S12, S21, S22 | switching element         |

| 40 | VREF, VREF', VREF0 | reference voltage         |

| 70 | IC                 | charging current          |

|    | IOUT               | output current            |

| 45 | VDD                | supply voltage terminal   |

|    | GND                | ground potential terminal |

| 50 | T1, T2             | time period               |

|    | G                  | amplification factor      |

|    |                    |                           |

#### Claims

55

1. A current generation circuit, comprising

- a reference unit (10) comprising a first reference output (101) configured to provide a first reference voltage

(VREF);

5

10

15

30

40

55

- a current control unit (20) comprising a first and a second current terminal (201, 202), the current control unit (20) configured to control a current (IC) between the first and the second current terminal (201, 202) depending on the first reference voltage (VREF);

- a first and a second charge store (C1, C2) each having a first and a second terminal (311, 312, 321, 322), wherein the first terminals (311, 321) can be coupled to the first current terminal (201) or to the second terminal (312, 322) of the respective charge store (C1, C2) depending on a switching signal;

- a current mirror (40) comprising an input (401) and an output (402), the input (401) coupled to the second current terminal (202); and

- a current output (1) coupled to the output (402) of the current mirror (40).

- 2. The current generation circuit of claim 1, wherein the first and the second charge store (C1, C2) each comprise a first temperature dependency and wherein the reference unit (10) is configured to generate the reference voltage (VREF) with a second temperature dependency being opposite to the first temperature dependency.

- **3.** The current generation circuit of claim 1 or 2, wherein the current mirror (40) comprises at least one filtering element (413, 414).

- 20 4. The current generation circuit of one of claims 1 to 3, wherein the reference unit (10) comprises a bandgap circuit (11) configured to provide a bandgap voltage from which the first reference voltage (VREF) is derived.

- 5. The current generation circuit of one of claims 1 to 4, wherein the reference unit (10) comprises a second reference output (102) configured to provide a second reference voltage (VREF0) which is temperature independent.

- 6. The current generation circuit of one of claims 1 to 5, wherein the reference unit (10) comprises at least one resistive element (130, 131, 132) configured to derive the first reference voltage (VREF).

- 7. The current generation circuit of one of claims 1 to 6, wherein the current control unit (20) comprises a differential amplifier (210) and a cascode transistor (220), the differential amplifier (210) having a first input (+) coupled to the first reference output (101), a second input (-) coupled to the first or to the second current terminal (201, 202) and an output (211) coupled to a control input (221) of the cascode transistor (220), a current path of the cascode transistor (220) being coupled between the first and the second current terminal (201, 202).

- **8.** The current generation circuit of one of claims 1 to 7, wherein a capacitance value of the first and the second charge store (C1, C2) is adjustable.

- **9.** The current generation circuit of one of claims 1 to 8, further comprising a clock generator (50) for providing the switching signal.

- **10.** The current generation circuit of claim 9, wherein the clock generator (50) is configured to provide the switching signal with a programmable clock frequency.

- 11. A current generation method, comprising

- generating a reference voltage (VREF);

- generating a charging current (IC) during a first time period (T1) by charging a first charge store (C1) depending on the reference voltage (VREF);

- discharging a second charge store (C2) during the first time period (T1);

- generating the charging current (IC) during a second time period (T2) by charging the second charge store (C2) depending on the reference voltage (VREF);

- discharging the first charge store (C1) during the second time period (T2);

- amplifying the charging current (IC); and

- providing the amplified charging current as an output current (IOUT).

|    | 12. | The current generation method of claim 11, wherein the first and the second charge store (C1, C2) each comprise a first temperature dependency, and wherein the reference voltage (VREF) is generated with a second temperature dependency being opposite to the first temperature dependency. |

|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5  | 13. | The current generation method of claim 11 or 12,                                                                                                                                                                                                                                               |

|    |     | wherein amplifying the charging current (IC) comprises filtering the charging current (IC).                                                                                                                                                                                                    |

| 10 |     |                                                                                                                                                                                                                                                                                                |

|    |     |                                                                                                                                                                                                                                                                                                |

| 15 |     |                                                                                                                                                                                                                                                                                                |

| 20 |     |                                                                                                                                                                                                                                                                                                |

|    |     |                                                                                                                                                                                                                                                                                                |

| 25 |     |                                                                                                                                                                                                                                                                                                |

|    |     |                                                                                                                                                                                                                                                                                                |

| 30 |     |                                                                                                                                                                                                                                                                                                |

|    |     |                                                                                                                                                                                                                                                                                                |

| 35 |     |                                                                                                                                                                                                                                                                                                |

| 10 |     |                                                                                                                                                                                                                                                                                                |

| 40 |     |                                                                                                                                                                                                                                                                                                |

| 45 |     |                                                                                                                                                                                                                                                                                                |

|    |     |                                                                                                                                                                                                                                                                                                |

| 50 |     |                                                                                                                                                                                                                                                                                                |

|    |     |                                                                                                                                                                                                                                                                                                |

| 55 |     |                                                                                                                                                                                                                                                                                                |

|    |     |                                                                                                                                                                                                                                                                                                |

Fig. 1

Fig. 2

Fig. 4

Fig. 5

Fig. 6

# **EUROPEAN SEARCH REPORT**

Application Number EP 07 00 9255

|                                                     | DOCUMENTS CONSIDER                                                                                                                                                                                                                   | ED IO RE KELEANI                                                                                                                                           |                                                        |                                         |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------|

| Category                                            | Citation of document with indic<br>of relevant passage                                                                                                                                                                               |                                                                                                                                                            | Relevant<br>to claim                                   | CLASSIFICATION OF THE APPLICATION (IPC) |

| Х                                                   | US 6 784 725 B1 (WADH<br>ET AL) 31 August 2004<br>* column 2, line 30 -<br>figures 1,2,6 *<br>* column 4, lines 51-                                                                                                                  | 1-13                                                                                                                                                       | INV.<br>G05F3/24                                       |                                         |

| X                                                   | KHAN Q A ET AL: "A l switched-capacitor cu circuit with low depe voltage and temperatu VLSI DESIGN, 2003. PR INTERNATIONAL CONFERE PISCATAWAY, NJ, USA, I 4 January 2003 (2003-504-506, XP010629122 ISBN: 0-7695-1868-0 * figure 4 * | rrent reference<br>ndence on process,<br>re"<br>OCEEDINGS. 16TH<br>NCE ON 4-8 JAN. 2003,<br>EEE,                                                           | 1,3,4,6,<br>7,9,11,<br>13                              |                                         |

| Х                                                   | US 2006/082410 A1 (KH<br>AL) 20 April 2006 (20<br>* paragraphs [0021] -<br>*                                                                                                                                                         | 06-04-20)                                                                                                                                                  | 1,3,7,9,<br>11,13                                      | TECHNICAL FIELDS<br>SEARCHED (IPC)      |

| Х                                                   | US 4 374 357 A (OLESI<br>15 February 1983 (198<br>* column 2, line 6 -<br>figure *                                                                                                                                                   | 3-02-15)                                                                                                                                                   | 1,3,4,6,<br>9,11,13                                    | G05F                                    |

|                                                     |                                                                                                                                                                                                                                      |                                                                                                                                                            |                                                        |                                         |

|                                                     | The present search report has been                                                                                                                                                                                                   | n drawn up for all claims                                                                                                                                  |                                                        |                                         |

|                                                     | Place of search                                                                                                                                                                                                                      | Date of completion of the search                                                                                                                           |                                                        | Examiner                                |

|                                                     | Munich                                                                                                                                                                                                                               | 4 July 2007                                                                                                                                                | Mol                                                    | l, Peter                                |

| X : part<br>Y : part<br>docu<br>A : tech<br>O : non | ATEGORY OF CITED DOCUMENTS icularly relevant if taken alone icularly relevant if combined with another iment of the same category inological background written disolosure rmediate document                                         | T: theory or principle E: earlier patent doo<br>after the filing date<br>D: document cited in<br>L: document cited for<br>&: member of the sar<br>document | ument, but publis<br>the application<br>rother reasons | hed on, or                              |

### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 07 00 9255

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

04-07-2007

| cit | Patent document<br>ed in search report |    | Publication<br>date        |      | Patent family member(s) | Publication date |

|-----|----------------------------------------|----|----------------------------|------|-------------------------|------------------|

| US  | 6784725                                | В1 | 31-08-2004                 | NONE |                         |                  |

| US  | 2006082410                             | A1 | 20-04-2006                 | NONE |                         |                  |

| US  | 4374357                                | Α  | 15-02-1983                 | NONE |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |

|     |                                        |    | ficial Journal of the Euro |      |                         |                  |

|     |                                        |    |                            |      |                         |                  |