EP 2 037 509 A1

(12)

EUROPEAN PATENT APPLICATION

(43) Date of publication:

18.03.2009 Bulletin 2009/12

(51) Int Cl.:

*H01L 33/00 (2006.01)*

(21) Application number: 08160129.6

(22) Date of filing: 10.07.2008

(84) Designated Contracting States:

**AT BE BG CH CY CZ DE DK EE ES FI FR GB GR

HR HU IE IS IT LI LT LU LV MC MT NL NO PL PT

RO SE SI SK TR**

Designated Extension States:

**AL BA MK RS**

(30) Priority: 14.09.2007 US 900952

(71) Applicant: **Cree Inc.**

Durham,

North Carolina 27703 (US)

(72) Inventor: **Chakraborty, Arpan**

Goleta, CA 93117 (US)

(74) Representative: **Turner, Craig Robert**

A.A. Thornton & Co.

235 High Holborn

London WC1V 7LE (GB)

(54) **Polarization doping in nitride based light emitting diodes**

(57) A light emitting device comprising a three-dimensional polarization-graded (3DPG) structure (108) that improves lateral current spreading within the device without introducing additional dopant impurities in the epitaxial structures. The 3DPG structure can include a repeatable stack unit (110) that may be repeated several times within the 3DPG. The stack unit includes a compositionally graded layer and a silicon (Si) delta-doped layer (112). The graded layer is compositionally graded

over a distance from a first material to a second material, introducing a polarization-induced bulk charge into the structure. The (Si) delta-doped layer compensates for back-depletion of the electron gas at the interface of the graded layers and adjacent layers. The 3DPG facilitates lateral current spreading so that current is injected into the entire active region (106), increasing the number of radiative recombination events in the active region and improving the external quantum efficiency and the wall-plug efficiency of the device.

**FIG. 1a**

## Description

**[0001]** This invention was made with Government support under Contract No. USAF 05-2-5507. The Government has certain rights in this invention.

### BACKGROUND OF THE INVENTION

#### Field of the Invention

**[0002]** The invention relates generally to materials used in polar and semi-polar semiconductor devices and, more particularly, to polarization-induced bulk doping techniques to reduce the series resistance of light emitting diodes (LEDs) and improve lateral current spreading.

#### Description of the Related Art

**[0003]** Light emitting diodes (LED or LEDs) are solid state devices that convert electric energy to light, and generally comprise one or more active layers of semiconductor material sandwiched between oppositely doped layers. A bias is applied across the doped layers, injecting holes and electrons into the active layer where they recombine to generate light. Light is emitted from the active layer and from all surfaces of the LED. A typical high efficiency LED comprises an LED chip mounted to an LED package, wire-bonded to make electrical contacts, and encapsulated by a transparent medium. The efficient extraction of light is a major concern in the fabrication of LEDs.

**[0004]** A useful measure of the efficiency of an LED is the wall-plug efficiency. This is a measure of the electrical-to-optical power conversion. Much effort has been devoted to improving the wall-plug efficiency of LEDs. One way to do this is to decrease the series resistance of the LED which in turn lowers the operating voltage. Each internal component or layer of the LED contributes to the total series resistance. Thus, reducing the resistance of any component or layer would also reduce the total series resistance of the LED. Lowering the resistance of the p- and the n-cladding layers of an LED improves lateral current spreading, especially when the lateral current spreading is entirely due to a semiconductor layer rather than a high conductivity metal contact layer.

**[0005]** A known method for reducing resistance is by bulk doping an electronic material with impurities. With impurity doping the carrier concentration and transport properties are determined by temperature, dopant concentration and scattering mechanisms such as impurity doping and phonon scattering. The carrier mobility is always diminished by the ionized impurity scattering. The carrier concentration is reduced as temperature decreases. These problems led to research in the area of modulation doping which has been shown to improve low temperature carrier mobility in quantum-confined structures by many orders of magnitude.

**[0006]** Recently, group III-nitrides (e.g., AlN, BN, GaN,

InN) have emerged as important materials for high-power microwave electronic and LED applications. Crystals such as group-III nitrides, when grown along the [0001] or the [000-1] direction of the wurtzite structure, exhibit large embedded electronic polarization fields owing to the lack of inversion symmetry in the crystal structure. This suggests the existence of a dipole in each unit cell of the crystal. For a homogeneous bulk crystal surface, dipoles inside the crystal cancel and leave net opposite charges on the opposing crystal surface, which is characterized by spontaneous polarization. Dipoles can also be created when a crystal is under strain, characterized by piezoelectric polarization. Both spontaneous polarization and piezoelectric polarization have been exploited for applications in communications, radar, infrared imaging, tunnel junction diodes, high-electron mobility transistors, memories, integrated optics, and in many other fields.

**[0007]** In one of the most popular nitride electronic devices, high-electron mobility transistors (HEMTs), the strong spontaneous and piezoelectric polarization fields in AlGaN and GaN have been used to make nominally undoped two-dimensional electron gases (2DEGs) in AlGaN/GaN heterostructures. [See Mishra et al., United States Patent Application Publication No. US 2006/0231860 A1 (Oct. 19, 2006)]. These devices can yield excellent power and efficiency performance at microwave frequencies.

**[0008]** Research in polarization doping in HEMT devices recently led to the development of three dimensional electron slabs that are usable as bulk doped carriers. This is done by grading the heterojunction of a material system such as AlGaN/GaN over a distance to spread the positive polarization charge into a bulk three-dimensional polarization background charge. The removal of ionized impurity scattering results in higher mobilities and better operation at lower temperatures. Experimental results have shown more than an order of magnitude improvement of carrier mobility at low temperatures for the polarization doped system over comparable donor-doped system. [See Jena et al., Realization of wide electron slabs by polarization bulk doping in graded III-V nitride semiconductor alloys, Applied Physics Letters, Vol. 81, No. 23 (Dec. 2002)].

45

### SUMMARY OF THE INVENTION

**[0009]** An embodiment of a light emitting device comprises an n-type semiconductor layer, a p-type semiconductor layer, and an active region interposed between the n-type layer and the p-type layer. A three-dimensional polarization-graded (3DPG) structure is disposed on the n-type layer the active region.

**[0010]** An embodiment of a three-dimensional polarization-graded (3DPG) lateral current spreading device, grown along the [0001] direction of a wurtzite crystal structure, comprises a retrograded layer that is compositionally graded from a first material to a second material

over a grading distance and a silicon (Si) delta-doped layer disposed adjacent to the retrograded layer, such that the first material is proximate to the Si delta-doped layer.

**[0011]** An embodiment of a three-dimensional polarization-graded (3DPG) lateral current spreading device, grown along the [000-1] direction of a wurtzite crystal structure, comprises a graded layer that is compositionally graded from a second material to a first material over a grading distance and a silicon (Si) delta-doped layer disposed adjacent to the graded layer, such that the first material is proximate to the Si delta-doped layer.

#### BRIEF DESCRIPTION OF THE DRAWINGS

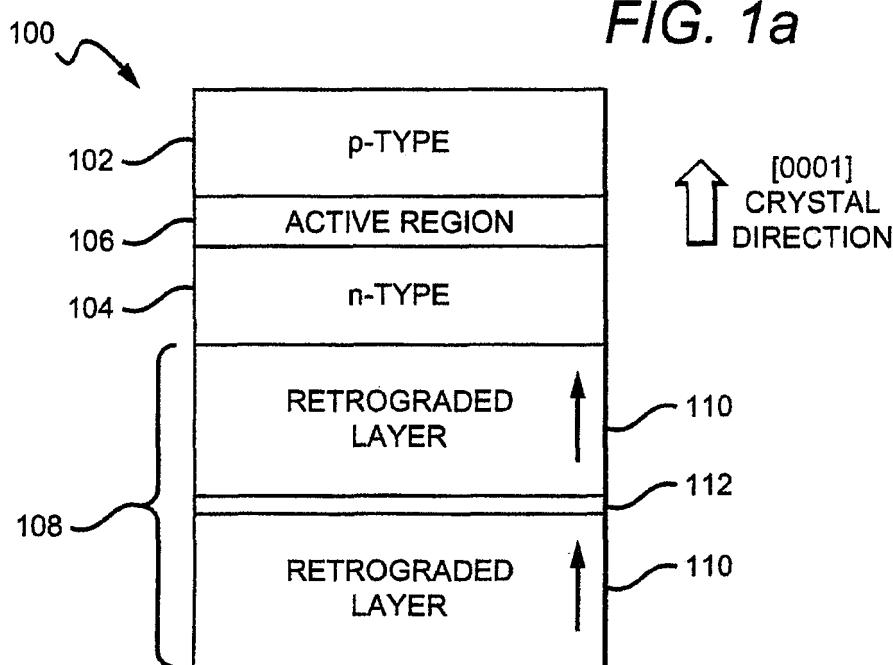

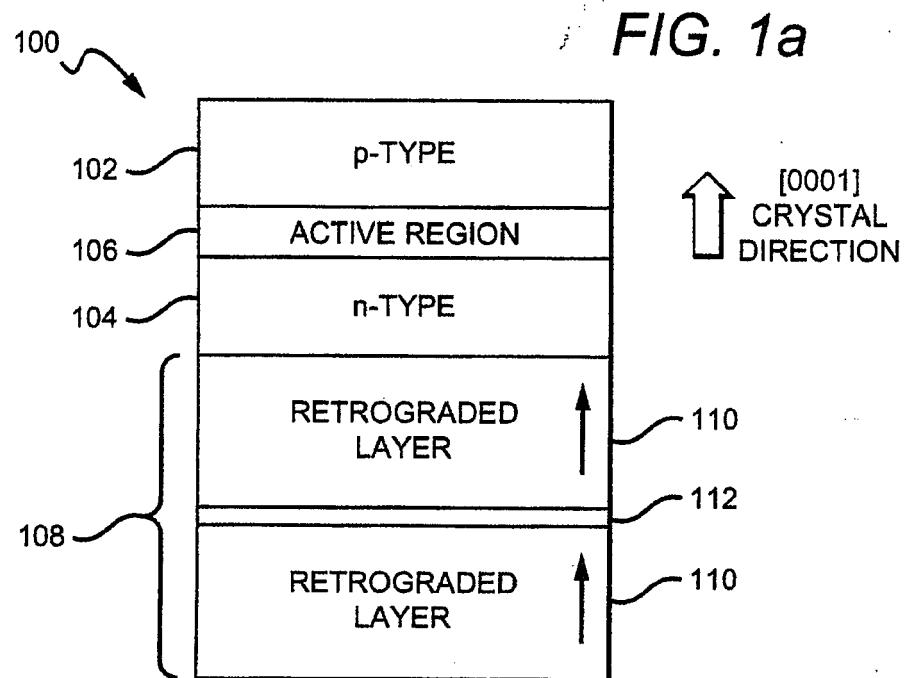

**[0012]** FIG.1a is a cross-sectional view of a light emitting device according to an embodiment of the present invention, grown along the [0001] direction or on Ga-face.

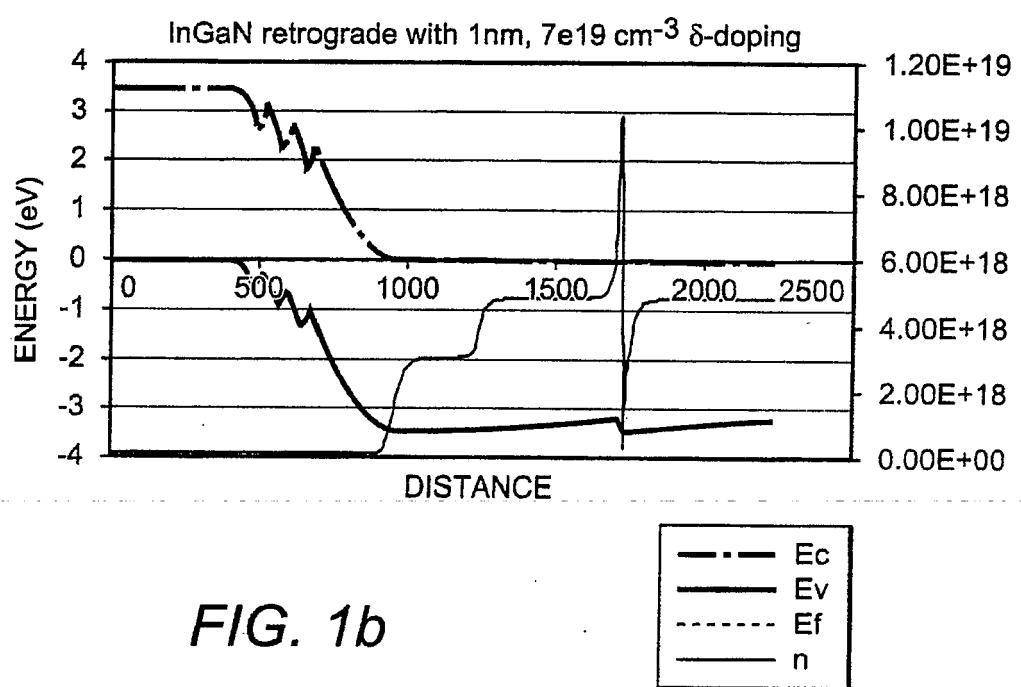

**[0013]** FIG.1b is a graph of a computer simulation that corresponds to the device of FIG.1a.

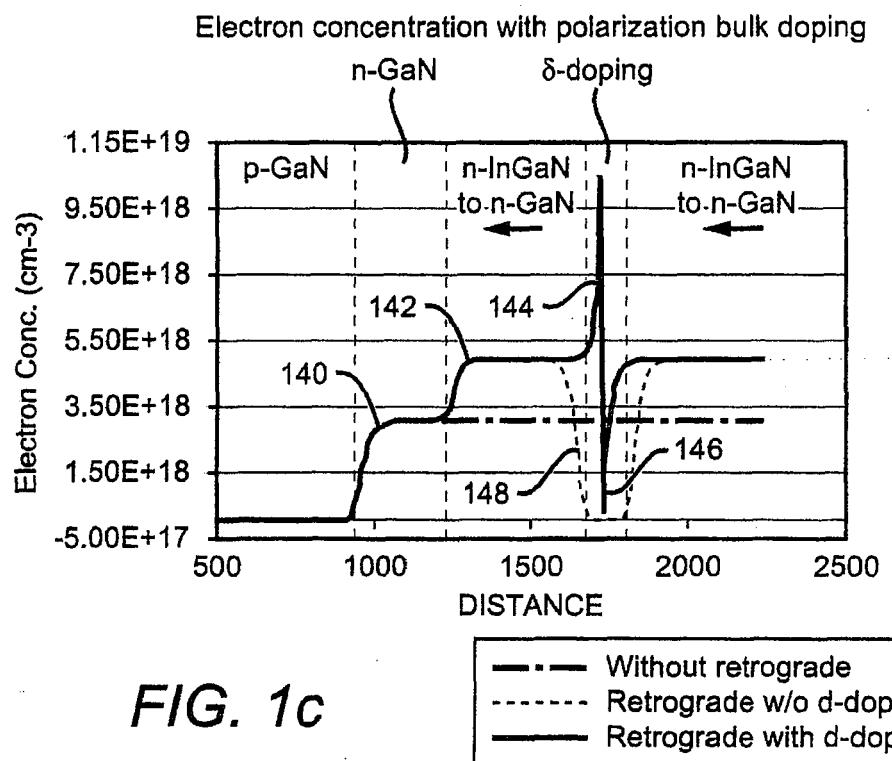

**[0014]** FIG.1c is a graph of another computer simulation that corresponds to the device of FIG.1a.

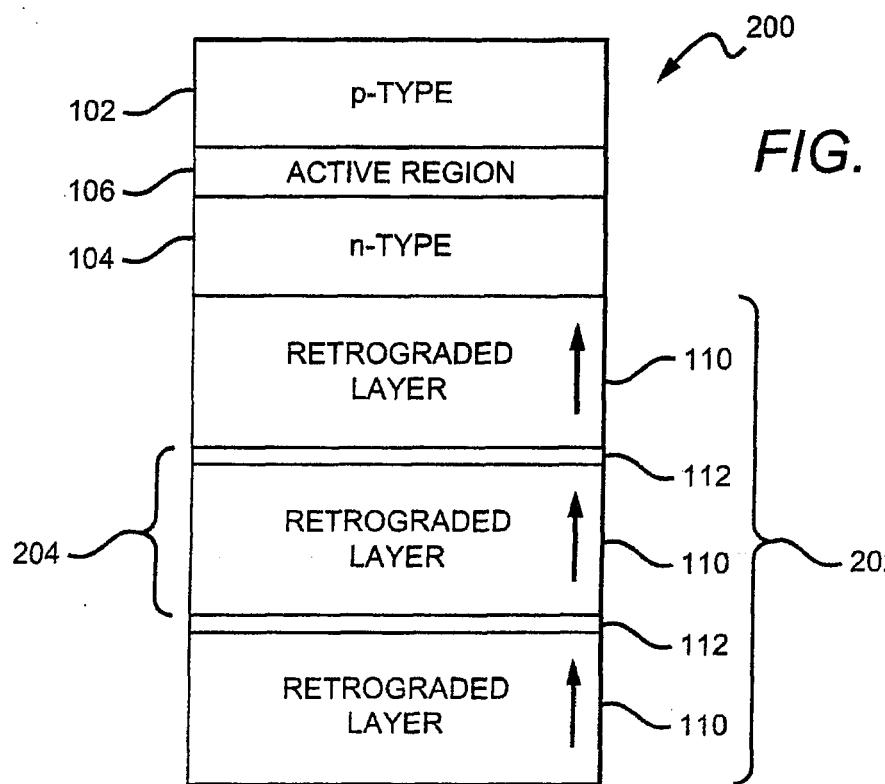

**[0015]** FIG.2a is a cross-sectional view of a light emitting device according to an embodiment of the present invention, grown along the [0001] direction or on Ga-face.

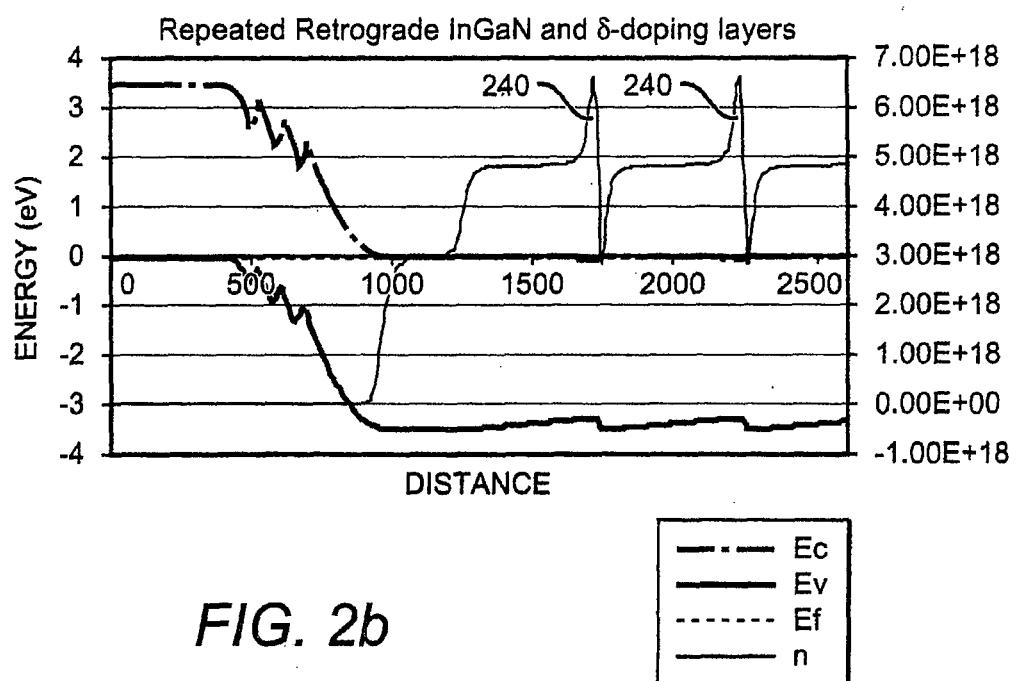

**[0016]** FIG.2b is a graph of a computer simulation that corresponds to the device of FIG.2a.

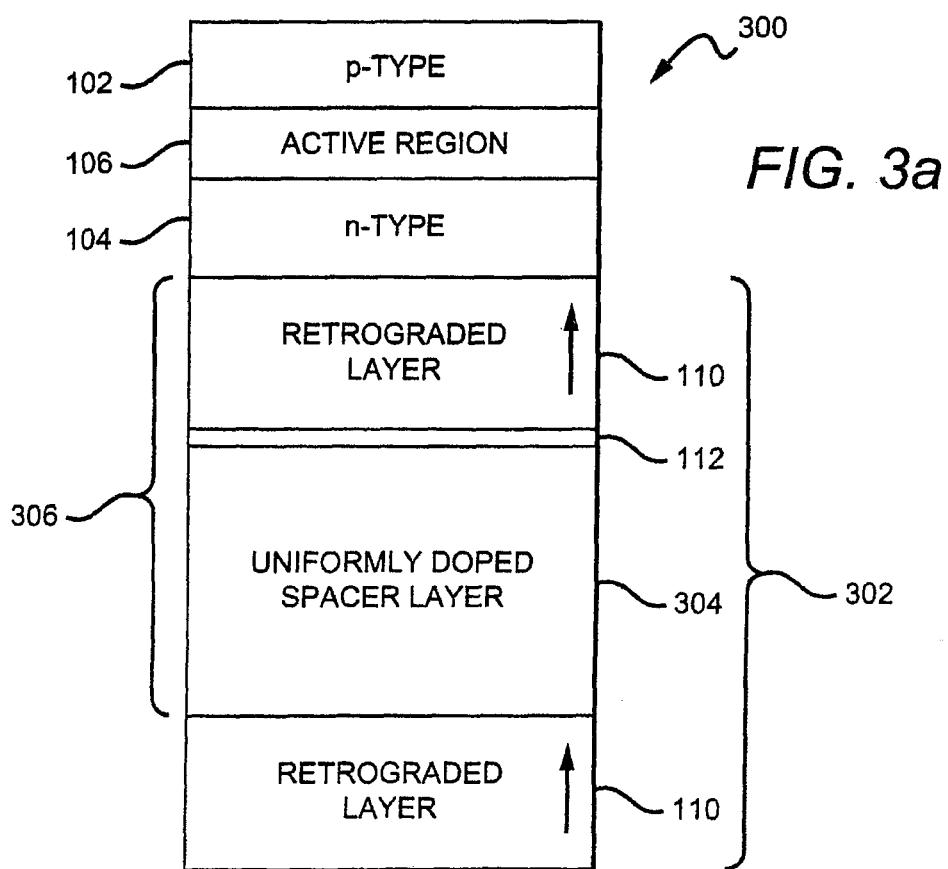

**[0017]** FIG.3a is a cross-sectional view of a light emitting device, grown along the [0001] direction or on Ga-face, according to an embodiment of the present invention.

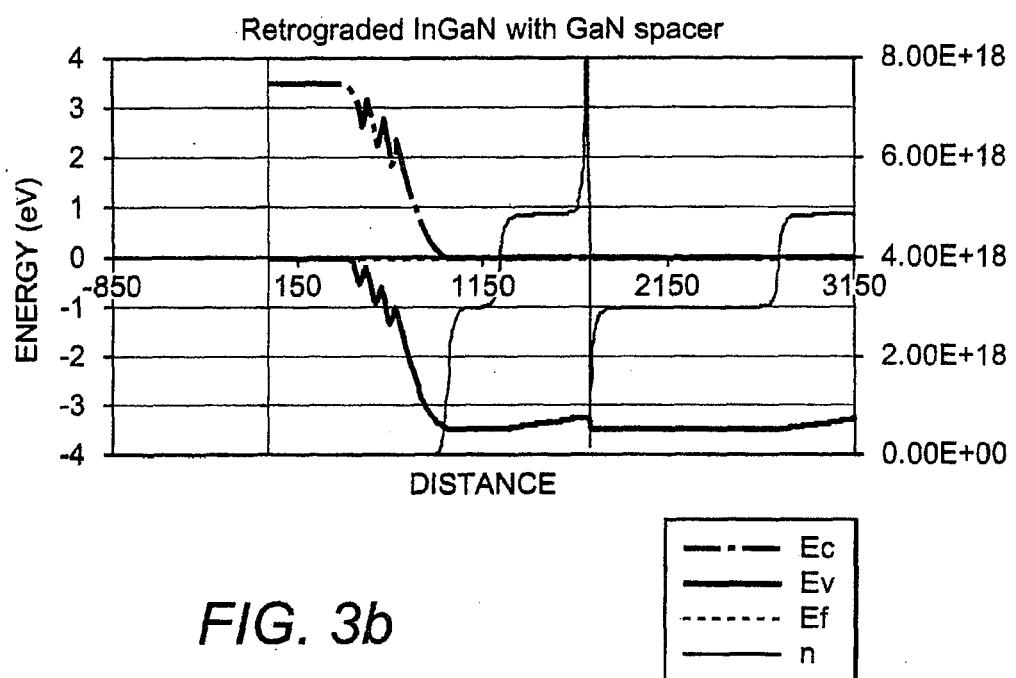

**[0018]** FIG.3b is a graph of a computer simulation that corresponds to the device of FIG.3a.

**[0019]** FIG.4a is a cross-sectional view of a light emitting device, grown along the [0001] direction or on Ga-face, according to an embodiment of the present invention.

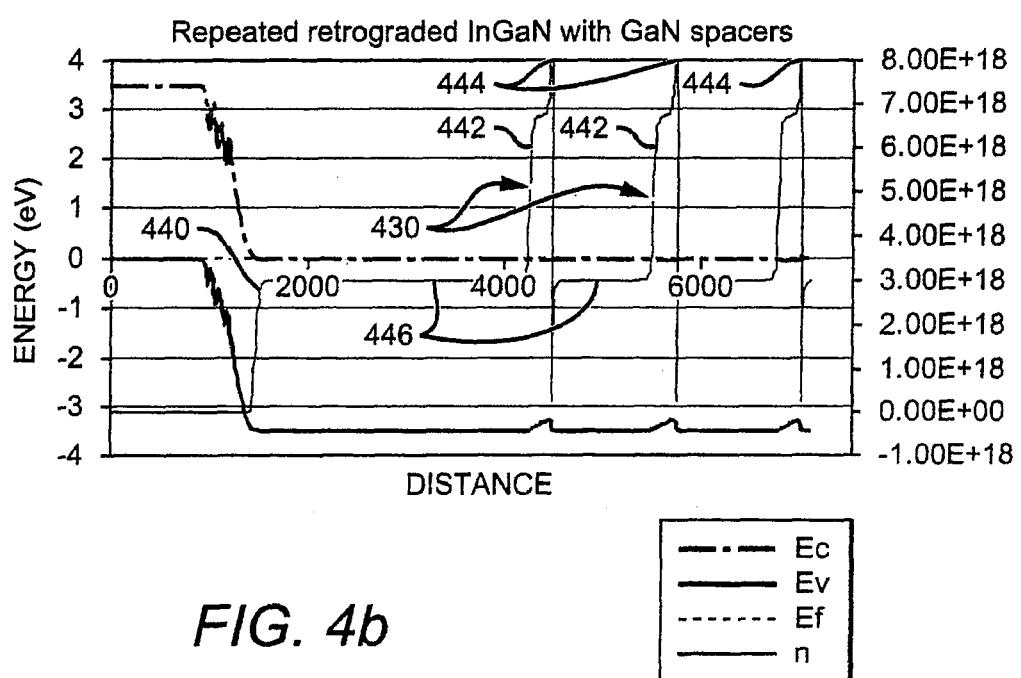

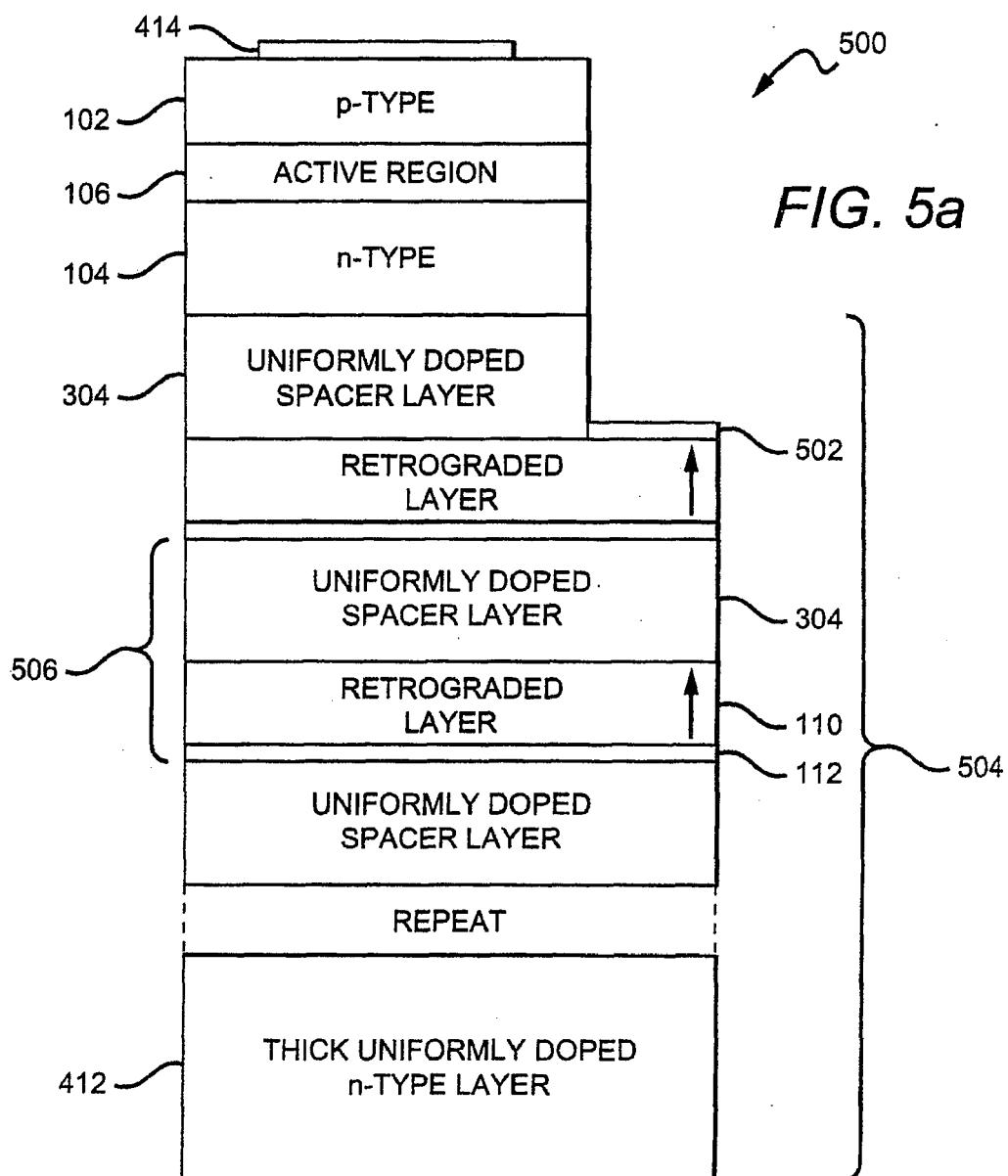

**[0020]** FIG.4b is a graph of a computer simulation that corresponds to the device of FIG.4a.

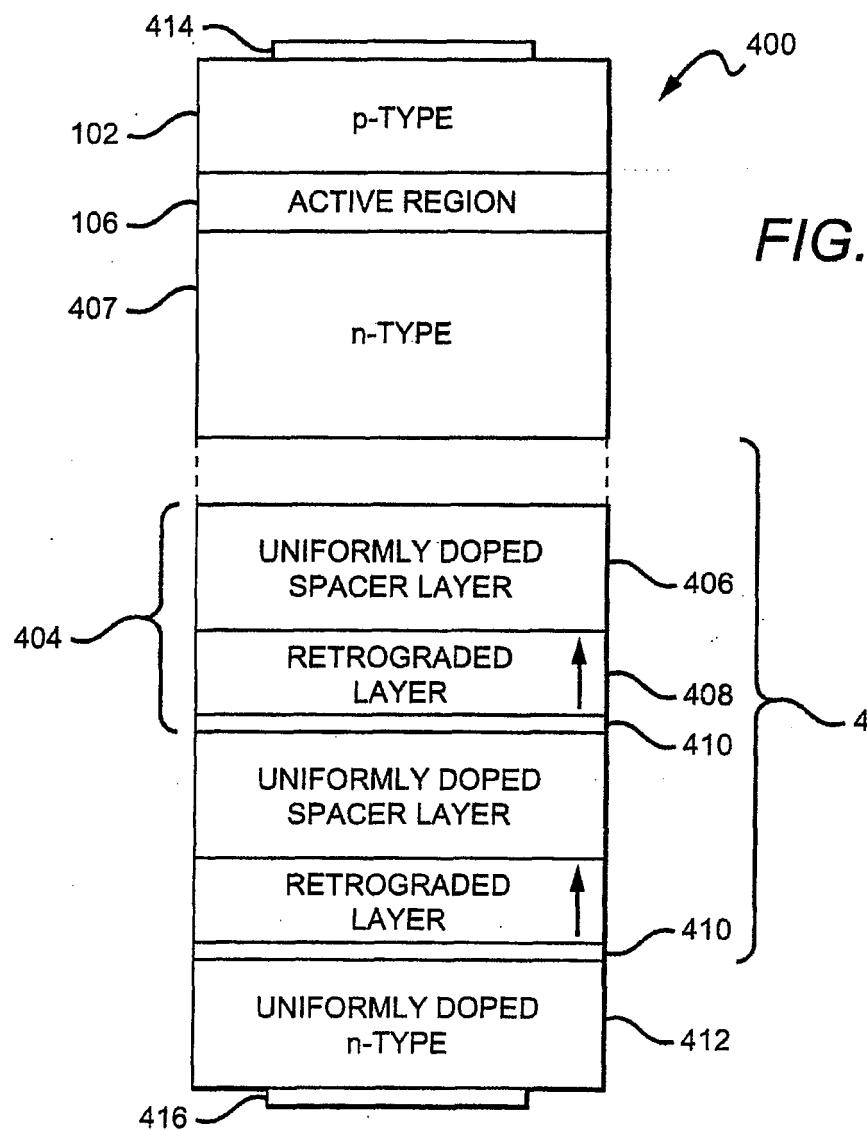

**[0021]** FIG.5a is a cross-sectional view of a light emitting device, grown along the [0001] direction or on Ga-face, according to an embodiment of the present invention.

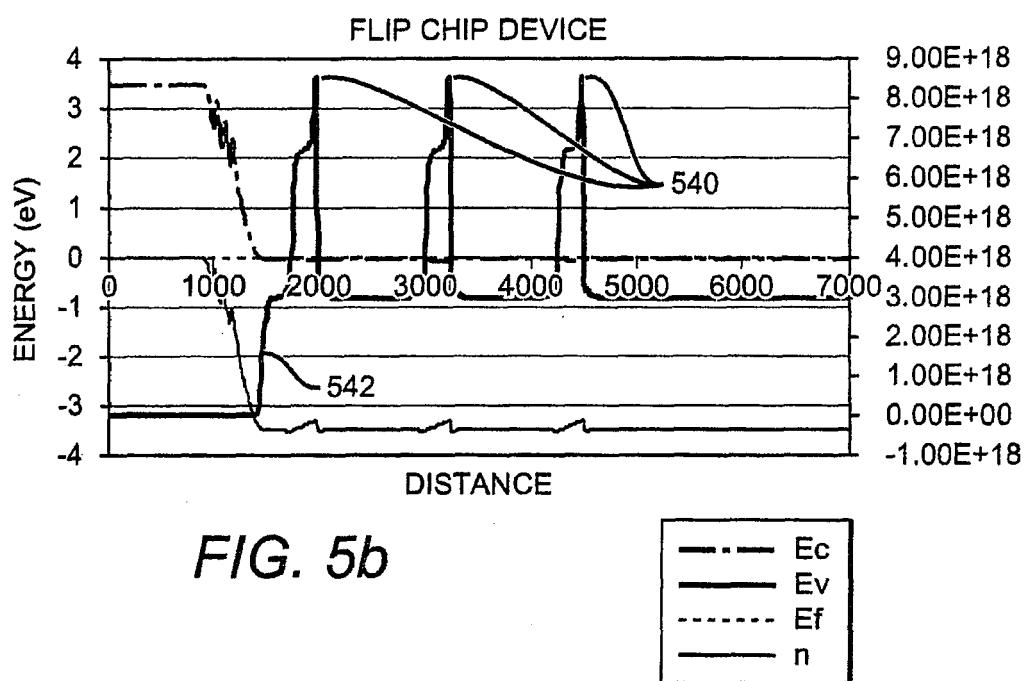

**[0022]** FIG.5b is a graph of a computer simulation that corresponds to the device of FIG.5a.

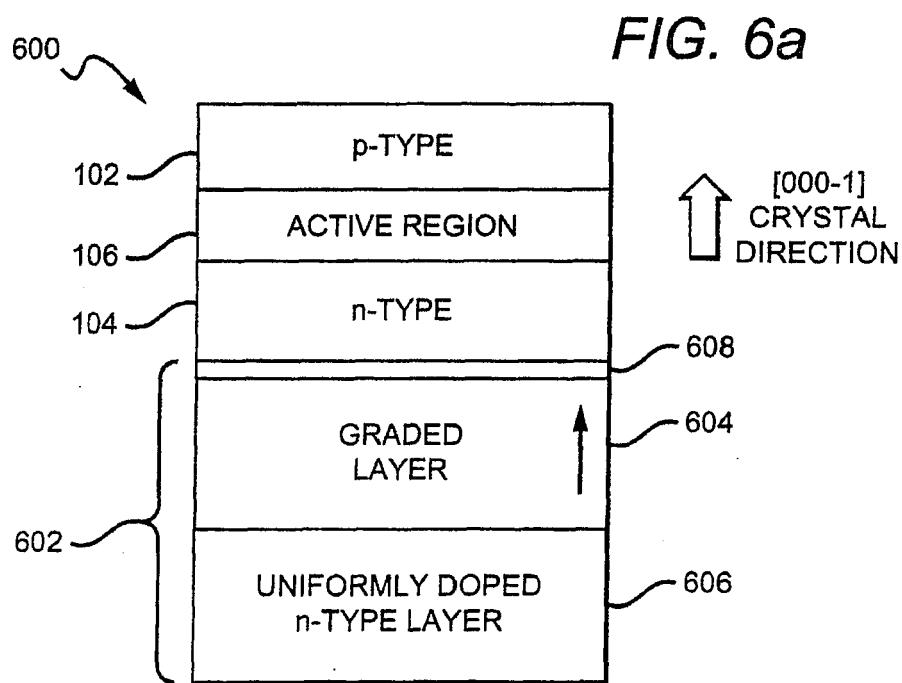

**[0023]** FIG.6a is a cross-sectional view of a light emitting device according to an embodiment of the present invention, grown along the [000-1] direction or on N-face.

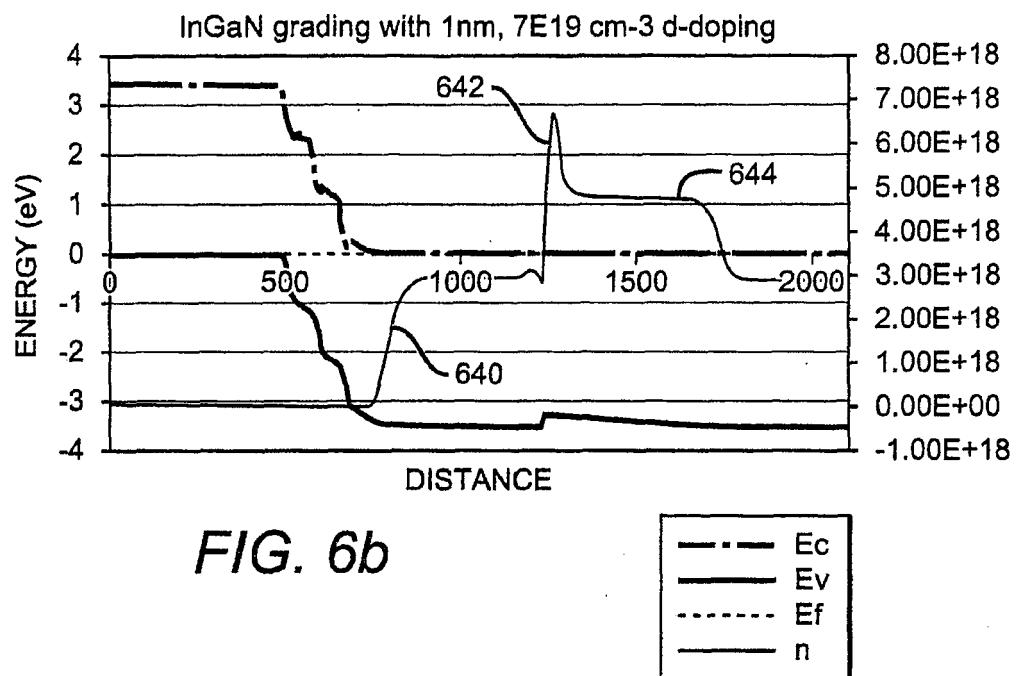

**[0024]** FIG.6b is a graph of a computer simulation that corresponds to the device of FIG.6a.

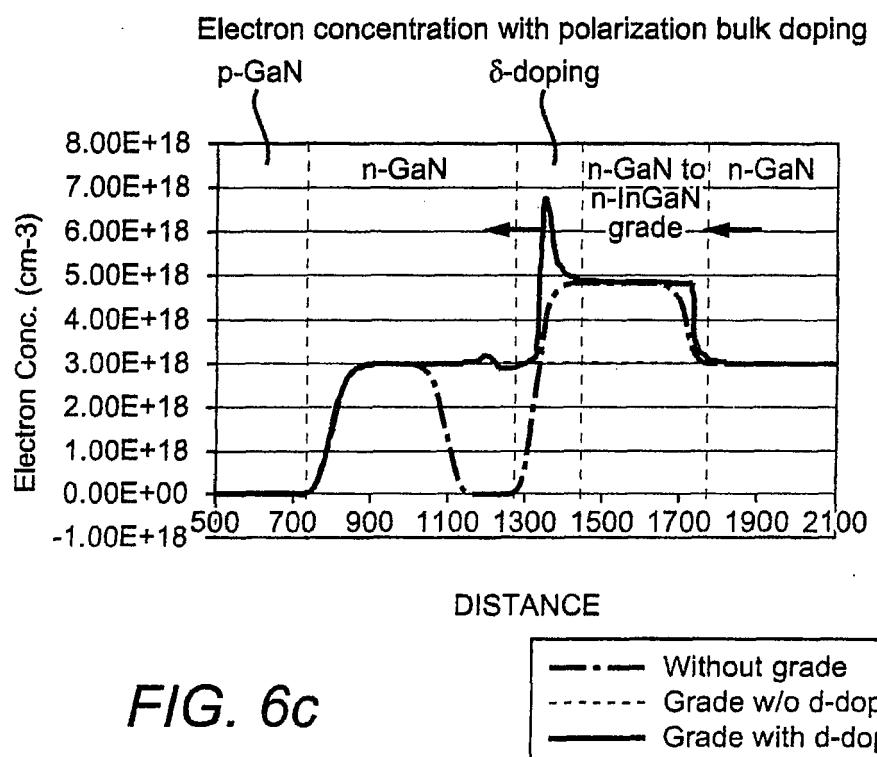

**[0025]** FIG.6c is a graph of another computer simulation that corresponds to the device of FIG.6a.

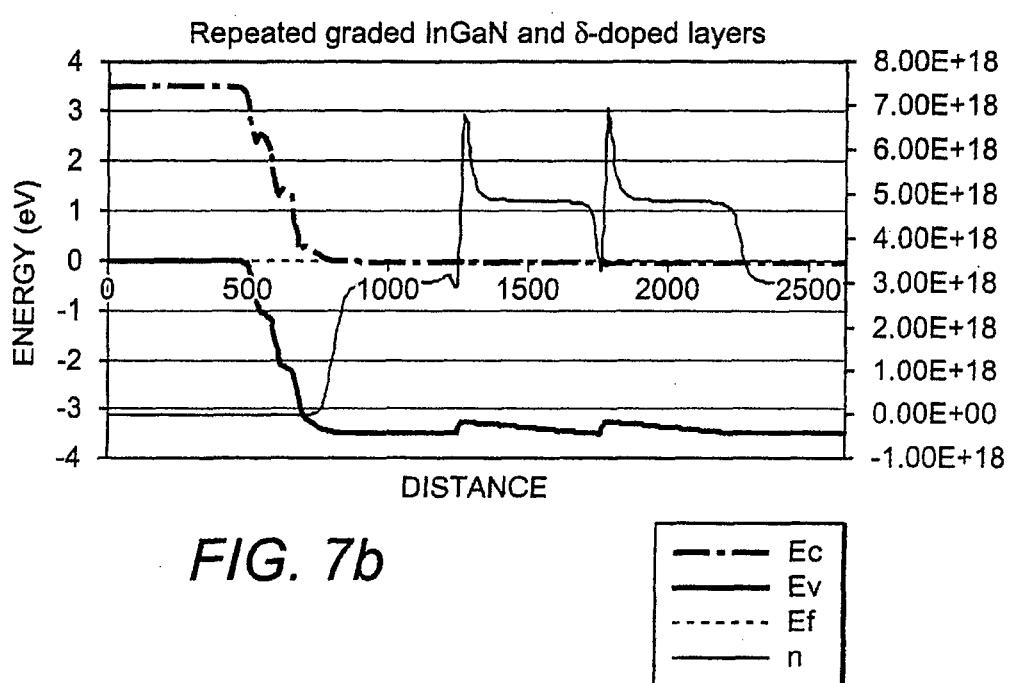

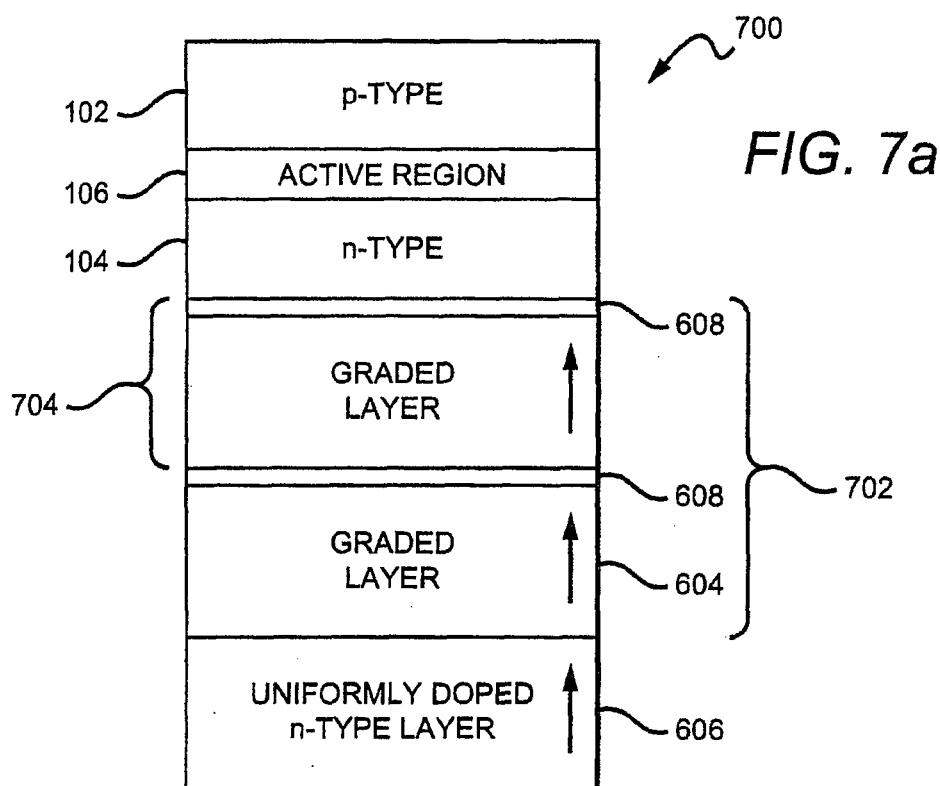

**[0026]** FIG.7a is a cross-sectional view of a light emitting device according to an embodiment of the present invention, grown along the [000-1] direction or on N-face.

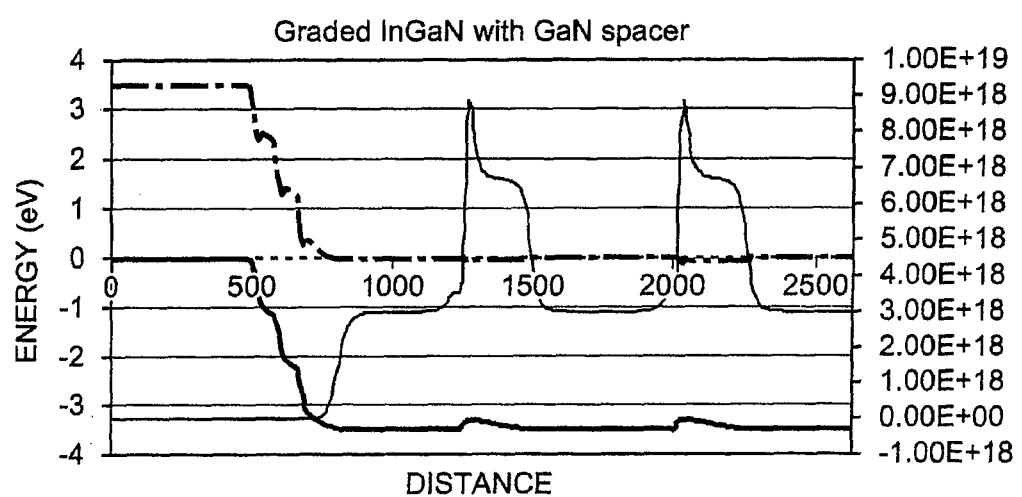

**[0027]** FIG.7b is a graph of a computer simulation that corresponds to the device of FIG.7a.

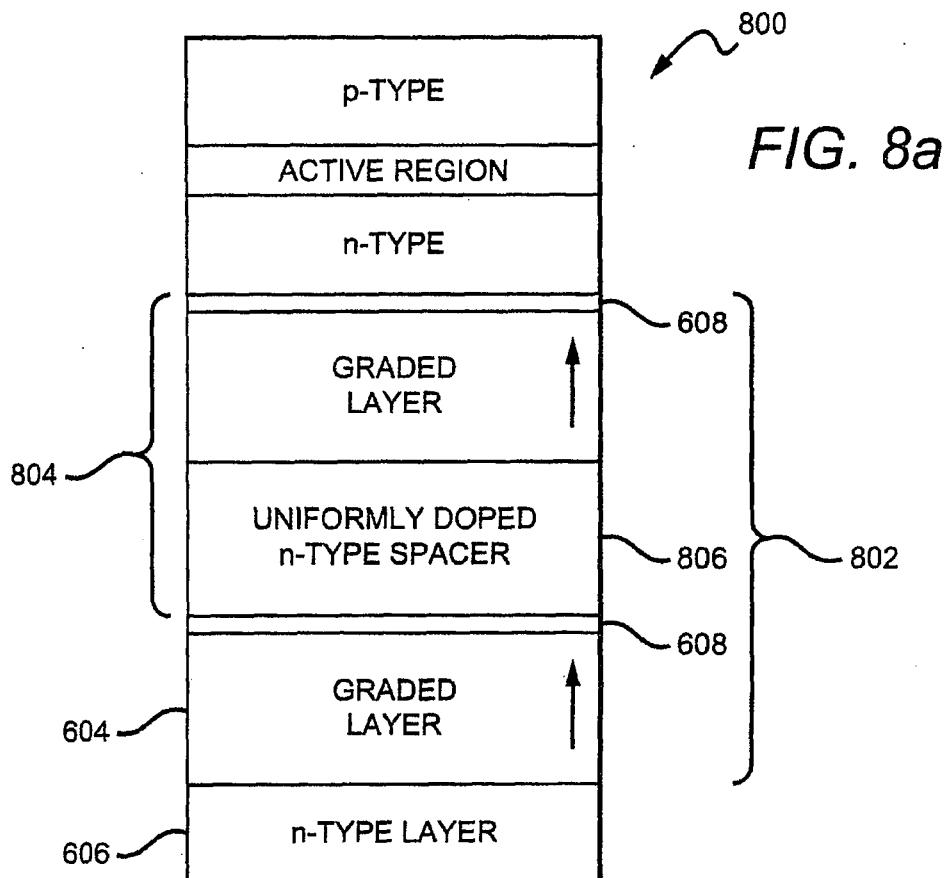

**[0028]** FIG.8a is a cross-sectional view of a light emit-

ting device, grown along the [000-1] direction or on N-face, according to an embodiment of the present invention.

**[0029]** FIG.8b is a graph of a computer simulation that corresponds to the device of FIG.8a.

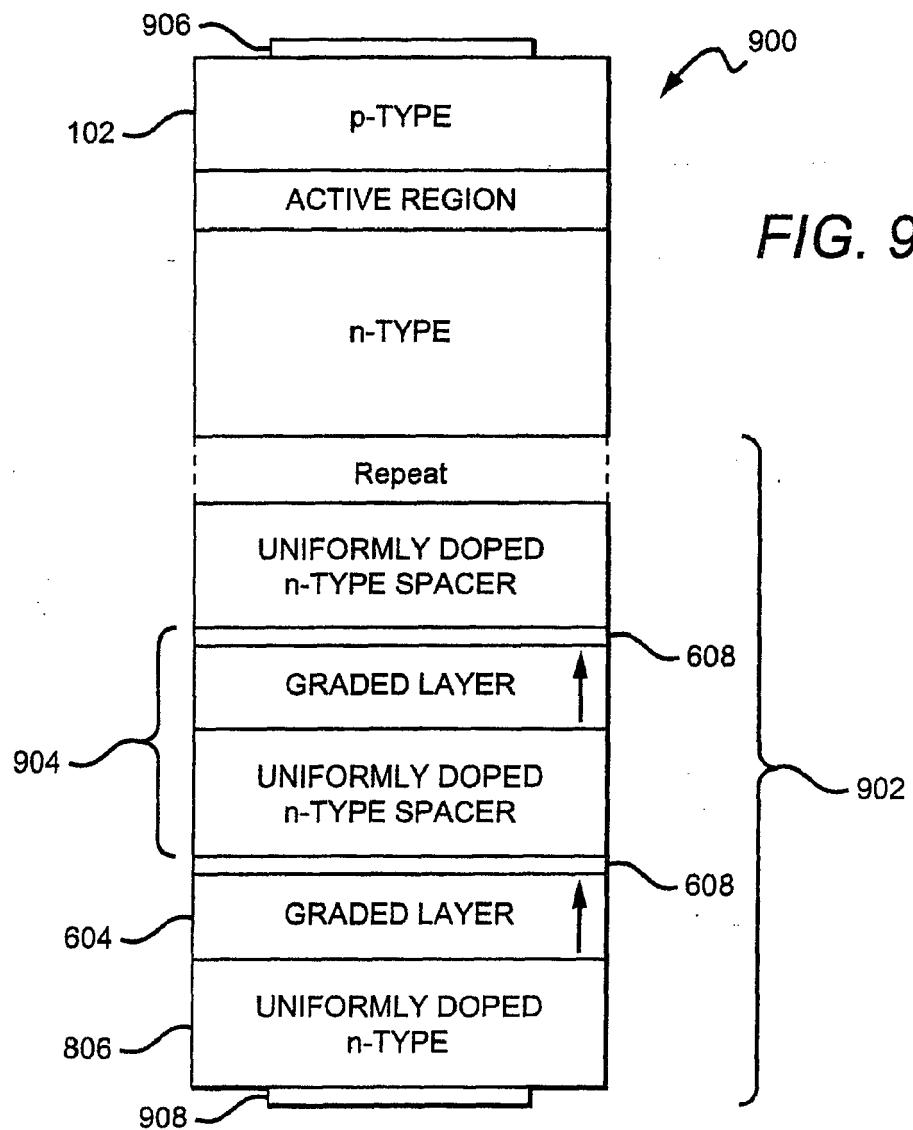

**[0030]** FIG.9a is a cross-sectional view of a light emitting device, grown along the [000-1] direction or on N-face, according to an embodiment of the present invention.

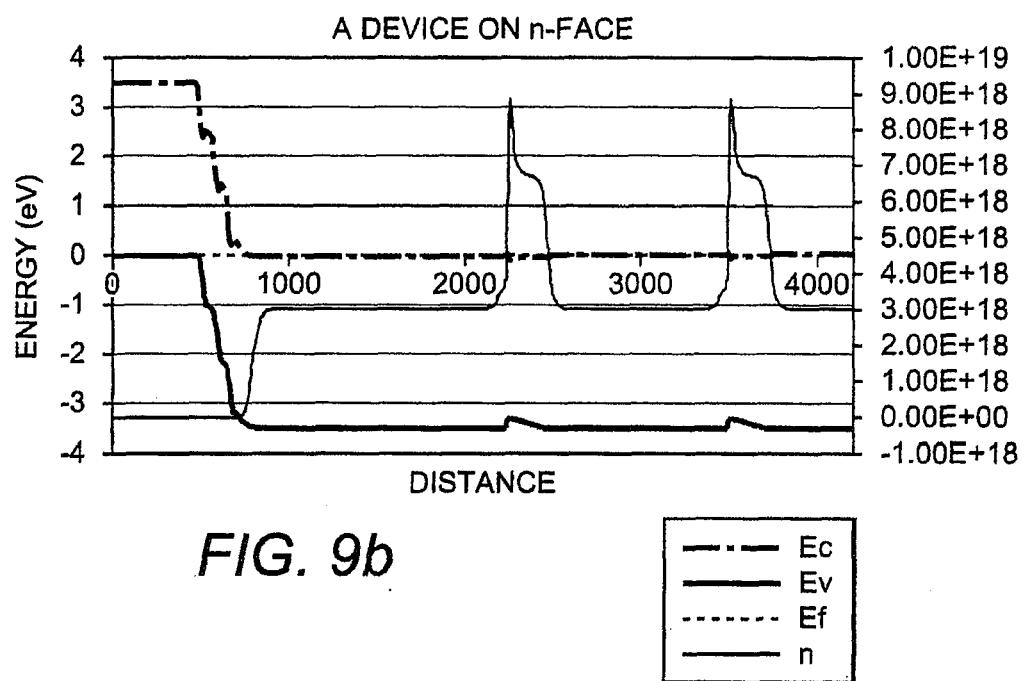

**[0031]** FIG.9b is a graph of a computer simulation that corresponds to the device of FIG.9a.

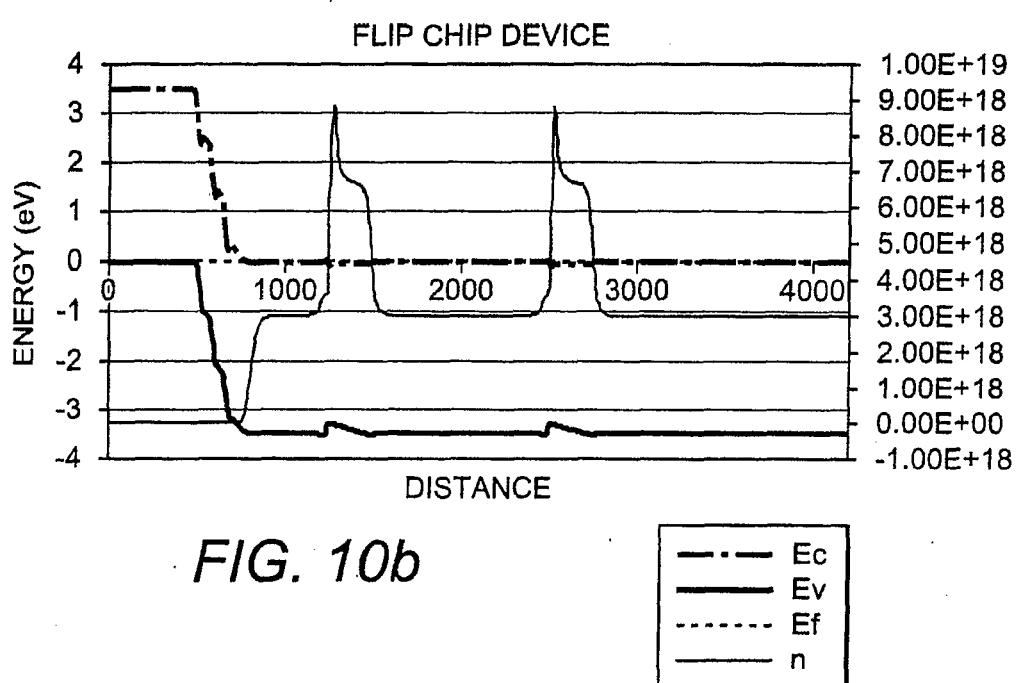

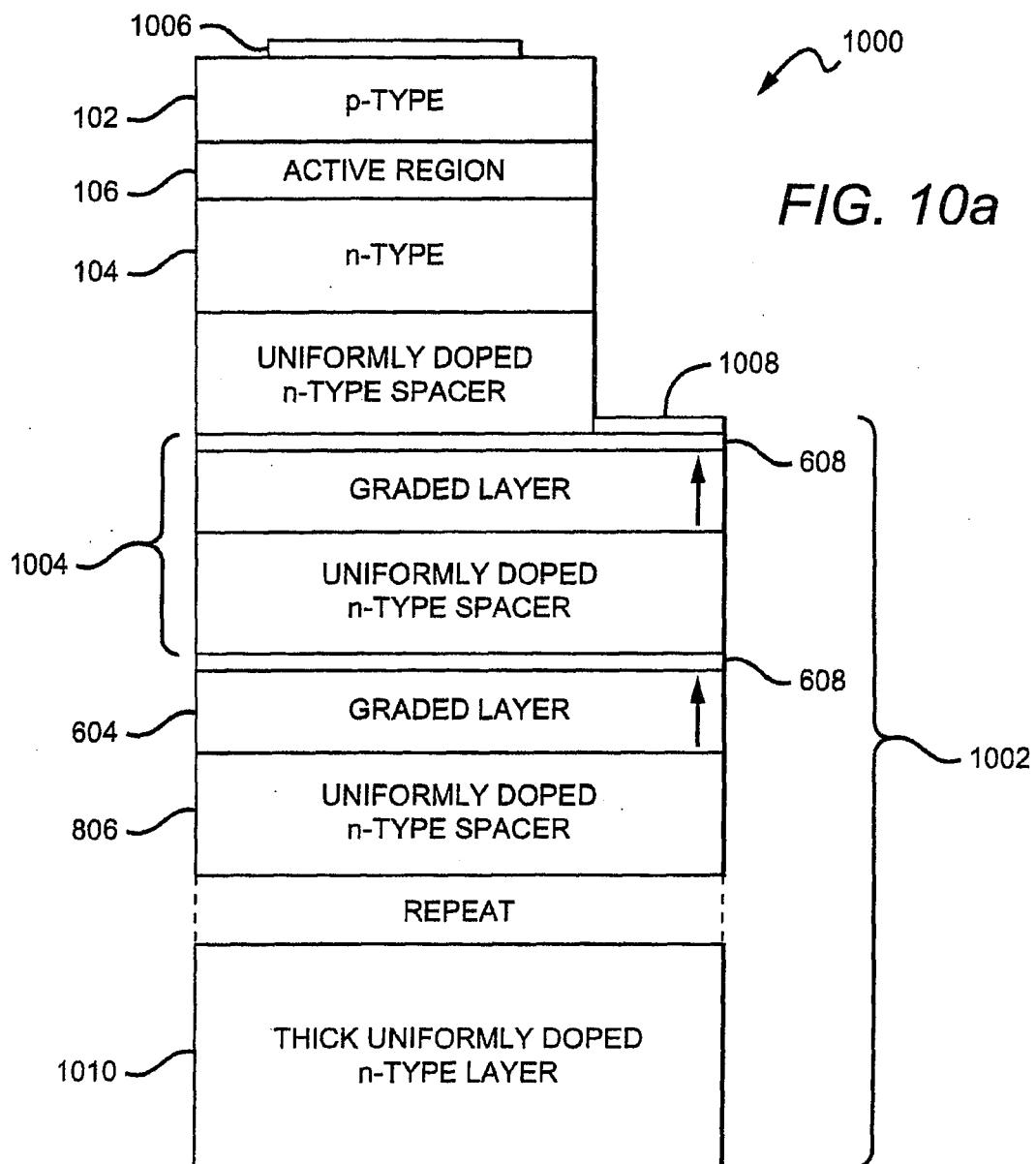

**[0032]** FIG.10a is a cross-sectional view of a light emitting device, grown along the [000-1] direction or on N-face, according to an embodiment of the present invention.

**[0033]** FIG.10b is a graph of a computer simulation that corresponds to the device of FIG.10a.

#### DETAILED DESCRIPTION OF THE INVENTION

**[0034]** The present invention as embodied in the claims provides improved materials and material configurations for use in semiconductor devices. Although the novel structures and methods presented are useful in many different semiconductor applications, they are particularly well-suited for use in polar or semi-polar nitride-based LED systems to reduce the series resistance and the operating voltage of these devices.

**[0035]** The series resistance  $R_s$  of an LED can be modeled by the equation:

$$R_s = R_c(n) + R_c(p) + R_b(n) + R_b(p)$$

where  $R_c(n)$  and  $R_c(p)$  represent the contact resistances for n- and p-contacts, respectively, and  $R_b(n)$  and  $R_b(p)$  represent the bulk resistance of the n- and p-type epitaxial layers, respectively. For example, a nominal 460nm

GaN LED has a bandgap of 2.7eV. Assuming a lossless system, the LED would also have an operating voltage of 2.7eV. However, in reality there are voltage penalties associated with each component contributing to the series resistance. This voltage penalty can be described as an "excess voltage" above the nominal bandgap voltage. Thus, by reducing the series resistance of the individual components, the excess voltage can be reduced, resulting in a significant improvement in the wall-plug efficiency of the device and lateral current spreading in the LEDs.

**[0036]** The largest contribution to the overall excess voltage required by a nitride-based LED comes from the bulk resistivity of the n-type layers. The excess voltage required by these layers also increases with higher operating currents of the LED. This makes the improvement potential even greater as solid state lighting devices trend toward operation at higher currents in order to reduce cost. Higher bulk n-resistance also prevents lateral cur-

rent spreading, resulting in current crowding near the electrical contacts and resulting non-uniform illumination of the LEDs.

**[0037]** Traditionally, semiconductor materials in LEDs have been doped by introducing impurities into the crystal lattice of the various semiconductor layers. As a result of the impurities in the lattice, the mobility of carriers is reduced by impurity scattering as the carriers move through the lattice. Donor-doped materials also suffer from reduced carrier mobility as temperature decreases. The thermally activated carriers "freeze out" with lowering temperatures which results in less energetic carriers and less effective screening. And this in turn leads to significant ionized impurity scattering. Further, heavy doping often results in cracking, deterioration of the surface morphology, etc. Growing thicker layers is another way of reducing the bulk resistivity, but in most circumstances, thicker layers result in wafer bowing, cracking, etc., due to the strains associated with heteroepitaxy.

**[0038]** Embodiments of the present invention reduce the resistance of one or more of the epitaxial layers by engineering the band structure of polar nitride devices to induce excess free carriers in the bulk. Instead of additional impurity doping to increase the charge, the layers feature polarization-induced bulk doping. The discontinuity in the polarization across a heterojunction, for example, InGaN/GaN, forms a fixed polarization sheet charge at the heterojunction. By grading the heterojunction over a distance the sheet charge can be spread into a bulk three-dimensional (3D) polarization background charge.

**[0039]** The fixed background charge attracts free carriers from remote donor-like states to satisfy Poisson's equation and neutralize charge. The polarization bulk charge acts as a local donor with zero activation energy. Thus, a mobile 3D electron slab is formed and can be used just like bulk doped carriers without the associated impurity scattering and performance degradation at low temperatures. The carriers exhibit high mobilities, and the resistance of the epitaxial layers is reduced.

**[0040]** Lower resistance in the epitaxial layers allows electrons to move more easily through the crystal lattice, vertically and laterally, on their way to the active region. Good lateral movement in the lattice is important as it allows the current to spread out across the entire width of the device before the carriers reach the active region. Thus, the entire area of the active region is available for recombination and emission.

**[0041]** It is understood that when an element such as a layer, region or substrate is referred to as being "on" another element, it can be directly on the other element or intervening elements may also be present. Furthermore, relative terms such as "inner", "outer", "upper", "above", "lower", "beneath", and "below", and similar terms, may be used herein to describe a relationship of one layer or another region. It is understood that these terms are intended to encompass different orientations of the device in addition to the orientation depicted in the

figures.

**[0042]** Although the terms first, second, etc. may be used herein to describe various elements, components, regions, layers and/or sections, these elements, components, regions, layers and/or sections should not be limited by these terms. These terms are only used to distinguish one element, component, region, layer or section from another region, layer or section. Thus, a first element, component, region, layer or section discussed below could be termed a second element, component, region, layer or section without departing from the teachings of the present invention.

**[0043]** It is noted that the terms "layer" and "layers" are used interchangeably throughout the application. A person of ordinary skill in the art will understand that a single "layer" of semiconductor material may actually comprise several individual layers of material. Likewise, several "layers" of material may be considered functionally as a single layer. In other words the term "layer" does not denote an homogenous layer of semiconductor material. A single "layer" may contain various dopant concentrations and alloy compositions that are localized in sub-layers. Such sub-layers may function as buffer layers, contact layers or etch-stop layers, for example. These sub-layers may be formed in a single formation step or in multiple steps. Unless specifically stated otherwise, the Applicant does not intend to limit the scope of the invention as embodied in the claims by describing an element as comprising a "layer" or "layers" of material.

**[0044]** Embodiments of the invention are described herein with reference to cross-sectional view illustrations that are schematic illustrations of idealized embodiments of the invention. As such, variations from the shapes of the illustrations as a result, for example, of manufacturing techniques and/or tolerances are expected. Embodiments of the invention should not be construed as limited to the particular shapes of the regions illustrated herein but are to include deviations in shapes that result, for example, from manufacturing. A region illustrated or described as square or rectangular will typically have rounded or curved features due to normal manufacturing tolerances. Thus, the regions illustrated in the figures are schematic in nature and their shapes are not intended to illustrate the precise shape of a region of a device and are not intended to limit the scope of the invention.

**[0045]** FIG.1a illustrates an epitaxial device 100, grown along the [0001] crystal direction, according to an embodiment of the present invention. A bias can be applied across the layers with contacts (not shown) on both ends of the structure, for example. In response to the bias, charge carriers are transported through a p-type layer 102 and an n-type layer 104 to the active region 106 where radiative recombination takes place, causing light within a specific wavelength range to be emitted from the device 100. The device 100 can be included in many different LED packages that include elements such as reflectors, secondary optics, wavelength conversion materials, and many others.

**[0046]** The device 100 includes a three-dimensional polarization-graded structure (3DPG) 108 which is disposed adjacent to the n-type layer 104 opposite the active region 106 as shown. In this particular embodiment the 3DPG comprises two polarization-graded layers 110 with a silicon (Si) delta-doped layer 112 interposed between them. The graded layers 110 can comprise various materials including  $\text{Al}_x\text{Ga}_{1-x}\text{N}$ ,  $\text{In}_x\text{Ga}_{1-x}\text{N}$ ,  $\text{Al}_x\text{In}_{1-x}\text{N}$  and  $\text{Al}_x\text{Ga}_y\text{In}_{1-x-y}\text{N}$  (where,  $x+y=1$ ), or any material like  $\text{Al}_x\text{B}_y\text{Ga}_z\text{In}_{(1-x-y-z)}\text{N}$  (where,  $x+y+z=1$ ), for use in a (Al, B, Ga, In)N system. For purposes of convenience only the InGaN/GaN system and Si-delta-doped layer, grown along

[0001] and [000-1] direction, will be referred to throughout the application as an exemplary system. It is understood that other material systems (for example AlGaN/GaN, AlInN/GaN, etc.), other delta-doped elements (for example Mg, Be, Zn, etc.), other crystal growth directions (for example [10-1-1], [10-11], [10-1-3], [10-13], [11-2-2], etc.) and other nitride systems are also possible.

**[0047]** Here, the graded layers 110 are retrograded from InGaN to GaN (for growth along [0001] direction or Ga-face) over a distance that is equal to the width of the graded layer 110 in the growth direction. Because the layers 110 are retrograded, InGaN having the highest concentration of In is disposed farthest from the junction with the n-type layer 104. In the figures a higher concentration of In is indicated by the darker shaded regions. The arrow in FIG.1a indicates the direction of decreasing In concentration. In a preferred embodiment, the graded layers 110 are retrograded from  $\text{In}_{0.1}\text{Ga}_{0.9}\text{N}$  to GaN over the grading distance (i.e., the width of the layer in the growth direction) for each graded layer 110. Grading the heterojunction spreads the positive polarization sheet charge into a bulk three-dimensional polarization background charge. As free electrons are induced in the retrograded layer, the polarization-induced electrons add to the existing electrons obtained by doping, and together they reduce the overall resistance of the structure 108. The 3DPG structure 108 allows the charge carriers be injected at various points on the bottom surface 114 of the 3DPG. Because the carriers move easily in a lateral direction, by the time the current reaches the active region 106, it is spread more evenly across the entire face of the active region 106. Using more of active region for recombination significantly improves the illumination uniformity, the wall-plug efficiency, and the overall performance of a device.

**[0048]** The charge profile of the device is given by the divergence of the polarization field, which changes only along the growth direction of the layers. In a preferred embodiment a linear retrograde is used. A linear retrograde will yield an approximately uniform charge profile. However, it is possible to create non-uniform charge profiles using more exotic gradients, such as a parabolic gradient, for example.

**[0049]** As shown, it is possible to stack multiple graded layers 110 on to create a larger 3DPG structure. Howev-

er, the negative sheet charge at the interface between the high concentration InGaN of one graded layer and the GaN portion of the adjacent graded layer causes a back-depletion of the electron gas and a discontinuity of the electron profile at the interface. This creates a hump-like barrier in the conduction band that results in electrical isolation. In order to compensate for the back-depletion a thin Si delta-doped layer 112 is interposed between the graded layers 110. The Si delta-doped layer 112 reduces the conduction band barrier nearly to flat-band. Si delta-doped GaN layers are known in the art and can be grown using known metalorganic chemical vapor deposition (MOCVD) processes. The Si delta-doped GaN layer compensates for the back-depletion, and provides free charges for continuity in vertical conductivity, without deteriorating the surface morphology of the device.

**[0050]** FIG.1b and FIG.1c are graphs of computer simulations illustrating the electron concentration profile along the height (i.e., in the growth direction which is [0001] in this case) of the device 100, where n represents the number of electrons at a given distance. FIG.1b shows the valence band ( $E_v$ ) and conduction band ( $E_c$ ) energies measured in eV on the same graph for convenience. FIG.1c shows the electron profile along the growth direction of the device 100 with the material interfaces delineated on the graph for reference. Three simulated data sets are shown on the graph: a device without retrograded layers; a device with retrograded layers but without a Si delta-doped layer; and a device with retrograded layers and with a Si delta-doped layer. The first rise in electron concentration 140 occurs at the interface of the p-type layer 102 (e.g., p-GaN) and the n-type layer 104 (e.g., n-GaN) somewhere within the active region 106. The second rise in electron concentration 142, which is a result of the polarization-induced bulk doping in the graded layers 110, appears at the interface of the n-type layer 104 and one of the graded layers 110.

**[0051]** After the second rise, a sharp positive spike in electron concentration 144 is noticeable followed by a sharp negative spike 146. These sharp features are due to the Si delta-doped layer 112 which is interposed between the two graded layers 110. The device having the retrograded layer but not having a Si delta-doped layer exhibits a large trough-like drop 148 in electron concentration at the interface between the graded layers. This is due to the back-depletion of carriers as discussed above. The low concentration of carriers over this distance introduces a great resistance to current flowing across the interface, or vertically along the structure, and is undesirable. Juxtaposed with the trough 148, the negative spike 146 exhibited by the device featuring a Si delta-doped region is much narrower (i.e., on the order of a single nanometer) and provides a much less resistive current path. There is no discontinuity in electron flow or path. The device 100 that features the retrograded layers and the Si delta-doped region exhibits a superior electron concentration profile, allowing for current to flow easily to the active region.

**[0052]** FIG.2a shows an epitaxial device 200 according to an embodiment of the present invention. The device 200, grown along the [0001] direction, functions similar to the device 100 and shares several common elements. In this particular embodiment the 3DPG structure 202 features an additional graded layer and Si delta-doped layer pair. The graded layers 110 in this embodiment are retrograded. Because total charge must be conserved, it is not possible to attain a high charge density over a thick graded layer. In order to achieve a higher bulk charge several graded layers 110 can be stacked on top of each other. The graded layers 110 are coupled together with Si delta-doped layers 112 in between to compensate for the back-depletion of charge carriers at the respective interfaces. The graded layer/delta-doped layer pair forms a repeatable stack unit 204. Additional stack units can be easily added to the structure in order to add thickness while retaining a desired charge density. The resulting stacked structure has a higher free electron concentration without the use of excessive external dopants which can raise the resistance of the device and cause cracking and other irregularities in surface morphology.

**[0053]** FIG.2b is a graph of a computer simulation showing the electron concentration profile ( $n$  = number of electrons) over a distance (nm) in the growth direction of the device 200. The graph also shows the valence band ( $E_v$ ) and conduction band ( $E_c$ ) energies measured in eV on the same graph for convenience. Similarly as shown in FIG.1b, the first and second rises in the electron concentration occur at the material interfaces on either side of the n-type layer 102. The thin spiked discontinuities 240 are due to the multiple Si delta-doped layers 112 that are interposed between the graded layers 110. The small negative spikes indicating a sharp drop in electron concentration are narrow enough that they do not introduce any significant resistance to the current path from the graded layers 110 to the active region 106.

**[0054]** FIG.3a illustrates an epitaxial device 300 according to an embodiment of the present invention. The device 300, grown along the [0001] direction, functions similar to the device 100 and shares many common elements. In this particular embodiment, the 3DPG structure 302 features a uniformly doped spacer layer 304 interposed between a Si delta-doped layer 112 and a graded layer 110. The graded layer 110, the Si delta-doped layer 112 and the spacer layer 304 form a repeatable stack unit 306. The stack unit may be repeated many times within the 3DPG structure 302. Each stack unit that is included adds thickness and charge to the device 300.

**[0055]** The spacer layer is doped uniformly with impurities at the same concentration as the graded layers 110. In the InGaN/GaN system, for example, the spacer layer 304 can comprise a GaN layer. The spacer layer 304 allows thicker devices to be grown. Thick layers can provide needed mechanical support to the device 300. Also, as thickness of the growth layers increases, the defect density in the crystal structure is reduced. Because GaN

layers can be grown much faster than InGaN layers and under much more moderate growth conditions, it is more time-efficient to grow GaN layers to improve the morphology and add thickness to the devices.

**[0056]** FIG.3b shows a computer simulation of the electron concentration profile along the growth direction of the device 300. The profile is similar to those in FIG. 1b and FIG.2b. After the Si delta-doped spike the electron concentration drops down to the level of the normally doped n-type layer 104. This is because the spacer layer 304 does not have polarization-induced doping. The level again rises at the interface of the spacer layer 304 and another graded layer 110.

**[0057]** FIG.4a depicts an epitaxial device 400 according to an embodiment of the present invention. The device 400, grown along the [0001] direction, is similar to device 300 and shares several common elements. In this particular embodiment, the 3DPG structure 402 comprises a series of repeatable stack units 404. Each stack unit 404 comprises a spacer layer 406, a graded layer 408 and a Si delta-doped layer 410. The first stack unit 404 is disposed such that the spacer layer 406 is adjacent to the n-type layer 407. A terminal layer 412 is adjacent to the Si delta-doped layer 410 in the stack unit 404 that is distal to the active region 106. In the InGaN/GaN system, the terminal layer 412 can comprise a InGaN layer or a GaN layer, for example. A p-contact 414 is disposed on the p-type layer 102. An n-contact 416 is disposed on the terminal layer 412 opposite the p-contact 414. Together the contacts 414, 416 provide a connection to a bias source (not shown).

**[0058]** A preferred embodiment of the device 400 is now described. FIG.4a only shows two full stack units 404; however, the dashed lines along the sides of the device are meant to indicate that additional stack units may be repeated up to the interface with the n-type layer 407. A preferred embodiment of the device 400 comprises a stack unit 404 that is repeated 15-20 times within the 3DPG structure 402. Each stack unit 404 comprises: a linearly retrograded layer 408 ( $n\text{-In}_{0.1}\text{Ga}_{0.9}\text{N} \rightarrow n\text{-GaN}$ ), approx. 25nm thick; a Si delta-doped layer 410, approx. 1nm thick; and an n-GaN spacer layer 406, approx. 100nm thick with  $3\text{e}18\text{cm}^{-3}$  donor doping. In the preferred embodiment, the terminal layer 412 comprises an approx. 50nm thick n-GaN layer with  $3\text{e}18\text{cm}^{-3}$  donor doping, and the n-type layer 407 comprises a  $1\mu\text{m}$  thick n-GaN layer with  $3\text{e}18\text{cm}^{-3}$  doping.

**[0059]** FIG.4b shows the results of a computer simulation of the device 400 using the parameters of the preferred embodiment described above. The graph shows the electron concentration ( $n$ ) along the growth direction (nm). The graph also shows the valence band ( $E_v$ ) and conduction band ( $E_c$ ) energies measured in eV on the same graph for convenience. The first rise in electron concentration 440 on the left-hand side of the graph is due to the interface at the n-type layer 407 which is doped with donor impurities to yield an n-type layer. The three tower-like structures 430 on the right side of the graph

represent the increase in electron concentration due to three consecutive stack units 404. Although only two stack units 404 are shown in FIG.4a, it is understood that additional stack units 404 may be added.

**[0060]** Each of the three structures 430 includes an initial rise 442 that corresponds with the graded layer 408, a spike feature 444 that corresponds with the Si delta-doped layer 410, and a leveled-off region 446 that corresponds with the spacer layer 406. The graph has been condensed for viewing convenience. Although three tower-like structures 430 appear in FIG.4b, it is understood that, in the preferred embodiment, 15-20 of the tower-like structures would appear on the graph corresponding with each stack unit 404 within the 3DPG structure 402.

**[0061]** FIG.5a illustrates an epitaxial structure 500 according to an embodiment of the present invention. The device 500, grown along the [0001] direction, is similar to the devices 300, 400 in some aspects and shares several common elements. The 3DPG structure 504 may contain several stack units 506. Each stack unit 506 comprises a spacer layer 304, a graded layer 110, and a Si delta-doped layer 112. In one embodiment there may be 15-20 stack units 506 within the 3DPG structure 504. A terminal layer 412 is disposed adjacent to the stack unit 506 farthest from the active region 106.

**[0062]** This particular embodiment features a top-side n-contact 502. The top-side n-contact 502 may be used to simplify the manufacturing process when devices are grown using a flip-chip process, for example. Flip-chip processes are known in the art. In this embodiment, the n-contact 502 contacts one of the graded layers 110 within the 3DPG structure 504. It is also possible to contact any of the other layers within the 3DPG structure 504 with the n-contact 502. The device may be etched down to the appropriate layer as shown in FIG.5a. Alternatively, a hole may be formed from the top surface with a via providing a connection to the n-contact below, or the n-contact may be contacted from the side of the device. Other methods of connection may also be used.

**[0063]** Current enters the device at n-contact 502 and spreads laterally through the layers in the 3DPG structure 504. Thus, current may initially travel away from the active region 106 to spread laterally before traveling vertically toward the active region 106. The 3DPG structure 504 provides effective channels for the current to move laterally so that the current is spread across the entire area of the active region 106, increasing the radiative recombination and improving the illumination uniformity.

**[0064]** FIG.5b shows a graph of a computer simulation of device 500. Like the previous graphs, the graph shows the electron concentration (n) along the growth direction (nm). The graph also shows the valence band ( $E_v$ ) and conduction band ( $E_c$ ) energies measured in eV on the same graph for convenience. The graph features three tower-like features 540 that correspond to three stack units 506 within the 3DPG structure 504 and an initial rise 542 at the p-n interface. It is understood that more

or fewer stack units can be included within the 3DPG structure 504 according to design needs. The tower-like features 540 are close to the initial rise in electron concentration at the n-type layer 104. A thick terminal layer 412 is disposed adjacent to the stack unit 506 which is farthest from the active region 106. The terminal layer 412 can be uniformly doped and can provide mechanical support to the device 500 as well as improve the overall conductivity of the n-layer.

**[0065]** FIG.6a shows an epitaxial semiconductor device 600 according to an embodiment of the present invention. The device 600 is similar to device 100 in some aspects and shares several common elements. However, unlike the device 100, the device 600 is grown along the [000-1] crystal direction. In the GaN material system, for example, the [000-1] direction represents the N-face of the crystal. The device features a 3DPG 602 that is disposed adjacent to the n-type layer 104. In this embodiment, the 3DPG 602 comprises a graded layer 604, a uniformly doped n-type layer 606, and a Si delta-doped layer 608.

**[0066]** The graded layer 604 can comprise various materials including  $Al_xGa_{1-x}N$ ,  $In_xGa_{1-x}N$ ,  $Al_xIn_{1-x}N$  and  $Al_xGa_yIn_{1-x-y}N$  (where,  $x+y=1$ , or any material like  $Al_xByGa_zIn_{(1-x-y-z)}N$  (where,  $x+y+z=1$ ), for use in a (Al, B, Ga, In)N system. Here, using the GaN/InGaN system, for example, the graded layer 604 is compositionally graded from GaN to InGaN over a grading distance (as indicated by the arrow in FIG.6a) along the [000-1] crystal direction. In one embodiment, the graded layer is linearly graded from GaN to  $In_{0.1}Ga_{0.9}N$  over the grading distance. Other compositions may also be used. The layer can be graded non-linearly as well. As discussed above, a Si delta-doped layer 608 is interposed between the graded layer 604 and the n-type layer 104 to compensate for the back-depletion of the electron gas at this interface. The Si delta-doped layer 608 is disposed on the InGaN side of the graded layer 604, and because the graded layer 604 is graded, rather than retrograded as in FIG.

**[0067]** FIG.6b is a graph of a computer simulation of device 600. The graph shows a first rise 640 in electron concentration at the p-n junction. The Si delta-doped layer 608 yields a sharp spike 642 in electrons followed by an increased level 644 of electrons in the graded layer 604. FIG.6c is another graph of a computer simulation of the device 600. The graph includes data sets for: a device without a graded layer or Si delta-doped layer; a device with a graded layer but without a Si delta-doped layer; and a device with both a graded layer and a Si delta-doped layer. Vertical dashed lines demarcate the various layers within the device for ease of reference.

**[0068]** FIG.7a is a cross-section of a semiconductor device 700 according to one embodiment of the present invention. The device 700 is similar to the device 200 and shares several common elements. The device 700 comprises a 3DPG 702. In this embodiment, the graded layer

604 (graded along the [000-1] crystal direction) and Si delta-doped layer 608 form a repeatable stack unit 704. Although only two stack units are shown, it is understood that more or fewer stack units can be incorporated in the 3DPG 702. The device also includes a uniformly doped n-type terminal layer 606. FIG.7b is a graph of a computer simulation of the device 700 similar to those discussed above which shows the expected electron levels in the device. The graph shows two periods of simulation, each of which corresponds to one of the stack units 704 shown in FIG.7a.

**[0069]** FIG.8a illustrates the cross-section of a semiconductor device 800 according to an embodiment of the present invention. The device 800 is similar to the device 300 and shares several common elements. The device features a 3DPG 802. In this embodiment, the 3DPG comprises multiple stack units each of which includes a Si delta-doped layer 608, a graded layer 604 (graded along the [000-1] crystal direction), and a uniformly doped n-type spacer layer 806. Although only two stack units are shown, it is understood that more or fewer stack units can be incorporated into the 3DPG 802. FIG.8b is a computer simulation of the device 800. The graph shows two periods of simulation, each of which corresponds to one of the stack units 804 shown in FIG.8a.

**[0070]** FIG.9a shows the cross-section of a semiconductor device 900. The device 900 is similar to the device 400 and shares several common elements. The device 900 includes a 3DPG 902. In this embodiment, the 3DPG 902 comprises multiple stack units 904 each of which includes a Si delta-doped layer 608, a graded layer 604, and a uniformly doped n-type spacer layer 806. Although only two stack units 904 are shown, it is understood that stack unit 904 can be repeated many times within the 3DPG 902. In a preferred embodiment the stack unit 904 is repeated 15-20 times within the 3DPG 902. The device 900 also comprises p- and n-contacts 906, 908 disposed on the ends of the device 900 such that the p-contact 906 provides a connection to the p-type layer 102 and the n-contact 908 provides a connection to the n-type side of the device 900. The contacts 906, 908 are connected to an external voltage device (not shown) to bias the device during operation. FIG.9b is a graph of a computer simulation of the device 900. The graph shows two periods of simulation, each of which corresponds to one of the stack units 904 shown in FIG.9a. A full graph of the preferred embodiment would show between 15 and 20 similar periods, one for each stack unit included in the device.

**[0071]** FIG.10a illustrates a cross-section of a semiconductor device 1000 according to an embodiment of the present invention. The device 1000 is similar to device 500 and shares several common elements. The device 1000 comprises a 3DPG 1002 which has several repeatable stack units 1004, each of which includes a Si delta-doped layer 608, a graded layer 604 (graded along the [000-1] crystal direction), and a uniformly doped n-type spacer layer 806. Although only two stack units 1004 are

shown, a preferred embodiment has 15-20 stack units within the 3DPG 1002. The device 1000 was formed by a flip-chip process with both the p-contact 1006 and the n-contact 1008 disposed on the top side of the device 1000 as shown. Flip-chip processes are known in the art.

**[0072]** In this embodiment, the n-contact 1008 contacts one of the graded layers 604 within the 3DPG structure 1002 from the top side. Thus, the current moves laterally through the device 1000. It is also possible to contact any of the other layers within the 3DPG structure 1002 with the n-contact 1008. The device may be etched down to the appropriate layer as shown in FIG.10a. Alternatively, a hole may be formed from the top surface with a via providing a connection to the n-contact below, or the 3DPG layers may be contacted from the side of the device. Other methods of connection may also be used. A thick uniformly doped n-type layer 1010 is disposed on the end of the device 1000 opposite the p-type layer 102. The thick layer 1010 can provide mechanical support for the device 1000.

**[0073]** FIG.10b is a graph of a computer simulation of the device 1000. Only two periods are shown which correspond to the two stack units 1004 in FIG.10a. It is understood that additional periods would be shown for each additional stack unit included in the 3DPG 1002.

**[0074]** Although the present invention has been described in detail with reference to certain preferred configurations thereof, other versions are possible. Therefore, the spirit and scope of the invention should not be limited to the versions described above.

## Claims

35. 1. A light emitting device, comprising:

- an n-type semiconductor layer;

- a p-type semiconductor layer;

- an active region interposed between said n-type layer and said p-type layer; and

- a three-dimensional polarization-graded (3DPG) structure disposed on said n-type layer opposite said active region.

45. 2. The light emitting device of claim 1, said 3DPG structure comprising at least one repeatable stack unit and a terminal layer disposed such that said at least one stack unit is interposed between said n-type layer and said terminal layer.

3. The light emitting device of claim 2, wherein said 3DPG structure has a wurtzite crystal structure and is grown along the [0001] crystal direction.

55. 4. The light emitting device of claim 3, said repeatable stack unit comprising:

- a retrograded layer that is compositionally ret-

rograded from a first material to a second material over a grading distance, said retrograded layer disposed proximate to said n-type layer such that said second material is closest to said n-type layer; and

5

a silicon (Si) delta-doped layer disposed adjacent to said retrograded layer opposite said n-type layer.

5. The light emitting device of claim 4, wherein said 10

retrograded layer has a linear compositional grading.

6. The light emitting device of claim 4, wherein said 15

retrograded layer has a nonlinear compositional

grading.

7. The light emitting device of claim 4, said repeatable 20

stack unit further comprising an n-type spacer layer

disposed adjacent to said Si delta-doped layer op-

posite said retrograded layer.

8. The light emitting device of claim 2, wherein said 25

repeatable stack unit is repeated 15 to 20 times with-

in said 3DPG structure.

9. The light emitting device of claim 2, wherein said 30

3DPG structure has a wurtzite crystal structure and

is grown along the [000-1] crystal direction.

10. The light emitting device of claim 9, said repeatable 35

stack unit comprising:

a graded layer that is compositionally graded

from a first material to a second material over a

grading distance, said graded layer disposed 40

proximate to said n-type layer such that said first

material is closest to said n-type layer; and

a silicon (Si) delta-doped layer interposed be-

tween said graded layer and said n-type layer.

11. The light emitting device of claim 10, wherein said 45

graded layer has a linear compositional grading.

12. The light emitting device of claim 10, wherein said 50

graded layer has a nonlinear compositional grading.

13. The light emitting device of claim 10, said repeatable

stack unit further comprising an n-type spacer layer

disposed adjacent to said graded layer opposite said

Si delta-doped layer.

FIG. 1c

FIG. 2b

FIG. 3b

FIG. 4b

FIG. 5b

FIG. 6b

FIG. 6c

FIG. 8b

FIG. 9b

FIG. 10b

## EUROPEAN SEARCH REPORT

Application Number

EP 08 16 0129

| DOCUMENTS CONSIDERED TO BE RELEVANT                        |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                       | CLASSIFICATION OF THE APPLICATION (IPC) |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Category                                                   | Citation of document with indication, where appropriate, of relevant passages                                                                                                                                                                                                                           | Relevant to claim                                                                                                                                                                                                                                                                     |                                         |

| X                                                          | US 6 046 464 A (SCHETZINA JAN FREDERICK [US]) 4 April 2000 (2000-04-04)                                                                                                                                                                                                                                 | 1,2,8                                                                                                                                                                                                                                                                                 | INV.<br>H01L33/00                       |

| Y                                                          | * column 10, line 29 - column 11, line 31; figure 3 *                                                                                                                                                                                                                                                   | 3-7,9-13                                                                                                                                                                                                                                                                              |                                         |

| Y                                                          | ASBECK P M ET AL: "Enhancement of base conductivity via the piezoelectric effect in AlGaN/GaN HBTs"<br>SOLID STATE ELECTRONICS, ELSEVIER SCIENCE PUBLISHERS, BARKING, GB, vol. 44, no. 2, 1 February 2000 (2000-02-01), pages 211-219, XP004186190<br>ISSN: 0038-1101<br>* page 213, left-hand column * | 3-7,9-13                                                                                                                                                                                                                                                                              |                                         |

| Y                                                          | US 2005/173728 A1 (SAXLER ADAM W [US] SAXLER ADAM WILLIAM [US]) 11 August 2005 (2005-08-11)<br>* paragraphs [0082], [0083] *                                                                                                                                                                            | 4-7,<br>10-13                                                                                                                                                                                                                                                                         |                                         |

| Y                                                          | US 2003/085409 A1 (SHEN YU-CHEN [US] ET AL) 8 May 2003 (2003-05-08)<br>* paragraph [0019]; figures 1,3 *                                                                                                                                                                                                | 7,13                                                                                                                                                                                                                                                                                  | TECHNICAL FIELDS<br>SEARCHED (IPC)      |

| X                                                          | JOHNSON M A L ET AL: "New UV light emitter based on AlGaN heterostructures with graded electron and hole injectors"<br>MATERIALS RESEARCH SOCIETY SYMPOSIUM - PROCEEDINGS 2002 MATERIALS RESEARCH SOCIETY US, vol. 743, 2002, pages 481-486, XP002505432<br>* abstract; figure 2 *                      | 1,2                                                                                                                                                                                                                                                                                   | H01L                                    |

|                                                            |                                                                                                                                                                                                                                                                                                         | -/-                                                                                                                                                                                                                                                                                   |                                         |

| The present search report has been drawn up for all claims |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                       |                                         |

| 3                                                          | Place of search                                                                                                                                                                                                                                                                                         | Date of completion of the search                                                                                                                                                                                                                                                      | Examiner                                |

|                                                            | Munich                                                                                                                                                                                                                                                                                                  | 25 November 2008                                                                                                                                                                                                                                                                      | Marani, Roberta                         |

| CATEGORY OF CITED DOCUMENTS                                |                                                                                                                                                                                                                                                                                                         | T : theory or principle underlying the invention<br>E : earlier patent document, but published on, or after the filing date<br>D : document cited in the application<br>L : document cited for other reasons<br>.....<br>& : member of the same patent family, corresponding document |                                         |

| EPO FORM 1503 03.82 (P04C01)                               |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                       |                                         |

## EUROPEAN SEARCH REPORT

Application Number

EP 08 16 0129

| DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                       | CLASSIFICATION OF THE APPLICATION (IPC) |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Category                            | Citation of document with indication, where appropriate, of relevant passages                                                                                                                                                                                                                           | Relevant to claim                                                                                                                                                                                                                                                                                     |                                         |

| X                                   | <p>SIMON J ET AL: "Polarization-induced 3-dimensional electron slabs in graded AlGaN layers"<br/>MATERIALS RESEARCH SOCIETY SYMPOSIUM PROCEEDINGS 2006 MATERIALS RESEARCH SOCIETY US, vol. 892, 28 November 2005 (2005-11-28), pages 417-422, XP002505433<br/>* abstract *<br/>1 and 4</p> <p>-----</p> | 1,2                                                                                                                                                                                                                                                                                                   |                                         |

|                                     |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                       | TECHNICAL FIELDS SEARCHED (IPC)         |

| 3                                   | <p>The present search report has been drawn up for all claims</p>                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                       |                                         |

|                                     | Place of search                                                                                                                                                                                                                                                                                         | Date of completion of the search                                                                                                                                                                                                                                                                      | Examiner                                |

|                                     | Munich                                                                                                                                                                                                                                                                                                  | 25 November 2008                                                                                                                                                                                                                                                                                      | Marani, Roberta                         |

| CATEGORY OF CITED DOCUMENTS         |                                                                                                                                                                                                                                                                                                         | <p>T : theory or principle underlying the invention<br/>E : earlier patent document, but published on, or after the filing date<br/>D : document cited in the application<br/>L : document cited for other reasons<br/>.....<br/>&amp; : member of the same patent family, corresponding document</p> |                                         |

| <p>EPO FORM 1503 03.82 (P04C01)</p> |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                       |                                         |

ANNEX TO THE EUROPEAN SEARCH REPORT

ON EUROPEAN PATENT APPLICATION NO.

EP 08 16 0129

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on. The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

25-11-2008

| Patent document cited in search report |    | Publication date |    | Patent family member(s) |  | Publication date |

|----------------------------------------|----|------------------|----|-------------------------|--|------------------|

| US 6046464                             | A  | 04-04-2000       | US | 5670798 A               |  | 23-09-1997       |

|                                        |    |                  | US | 5679965 A               |  | 21-10-1997       |

| -----                                  |    |                  |    |                         |  |                  |

| US 2005173728                          | A1 | 11-08-2005       | CA | 2554942 A1              |  | 09-09-2005       |

|                                        |    |                  | EP | 1714325 A1              |  | 25-10-2006       |

|                                        |    |                  | JP | 2007535138 T            |  | 29-11-2007       |

|                                        |    |                  | KR | 20070003906 A           |  | 05-01-2007       |

|                                        |    |                  | US | 2006255364 A1           |  | 16-11-2006       |

|                                        |    |                  | WO | 2005083793 A1           |  | 09-09-2005       |

| -----                                  |    |                  |    |                         |  |                  |

| US 2003085409                          | A1 | 08-05-2003       | DE | 10250445 A1             |  | 15-05-2003       |

|                                        |    |                  | JP | 2003152219 A            |  | 23-05-2003       |

|                                        |    |                  | TW | 283932 B                |  | 11-07-2007       |

| -----                                  |    |                  |    |                         |  |                  |

EPO FORM P0459

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

**REFERENCES CITED IN THE DESCRIPTION**

*This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.*

**Patent documents cited in the description**

- US 20060231860 A1 [0007]

**Non-patent literature cited in the description**

- **JENA et al.** Realization of wide electron slabs by polarization bulk doping in graded III-V nitride semiconductor alloys. *Applied Physics Letters*, December 2002, vol. 81 (23 [0008])