#

# (11) **EP 2 056 286 A1**

(12)

# **EUROPEAN PATENT APPLICATION**

published in accordance with Art. 153(4) EPC

(43) Date of publication: 06.05.2009 Bulletin 2009/19

(21) Application number: 07792475.1

(22) Date of filing: 13.08.2007

(51) Int Cl.:

G09G 3/36 (2006.01) G02F 1/1343 (2006.01)

G02F 1/133 (2006.01) G09G 3/20 (2006.01)

(86) International application number:

PCT/JP2007/065832

(87) International publication number:

WO 2008/023601 (28.02.2008 Gazette 2008/09)

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC MT NL PL PT RO SE SI SK TR

**Designated Extension States:**

AL BA HR MK RS

(30) Priority: 24.08.2006 JP 2006228476

(71) Applicant: Sharp Kabushiki Kaisha Osaka-shi, Osaka 545-8522 (JP)

(72) Inventors:

SHIMOSHIKIRYOH, Fumikazu Matsusaka-shi, Mie 515-0043 (JP)

KITAYAMA, Masae Tsu-shi, Mie 514-0063 (JP)

IRIE, Kentaro Tsu-shi, Mie 514-0112 (JP)

(74) Representative: Müller - Hoffmann & Partner

Patentanwälte

Innere Wiener Strasse 17 81667 München (DE)

# (54) LIQUID CRYSTAL DISPLAY DEVICE

(57) A liquid crystal display device according to the present invention includes a plurality of pixels, each including first and second subpixels. When a predetermined grayscale tone is displayed continuously through four or more consecutive even number of vertical scanning periods, the first and second subpixels have different luminances in at least two of the even number of vertical scanning periods, first polarity periods that are included in the vertical scanning periods and that maintain a first

polarity are as long as second polarity periods that are also included in the vertical scanning periods and that maintain a second polarity for each of the first and second subpixels, and in each of the first and second polarity periods, the difference between the average of effective voltages applied to the liquid crystal layer of the first subpixel and that of effective voltages applied to the liquid crystal layer of the second subpixel is substantially equal to zero.

#### Description

20

30

35

40

50

#### **TECHNICAL FIELD**

**[0001]** The present invention relates to a liquid crystal display device and more particularly relates to a liquid crystal display device that can reduce the viewing angle dependence of the r characteristic thereof.

# **BACKGROUND ART**

**[0002]** A liquid crystal display (LCD) is a flat-panel display that has a number of advantageous features including high resolution, drastically reduced thickness and weight, and low power dissipation. The LCD market has been rapidly expanding recently as a result of tremendous improvements in its display performance, significant increases in its productivity, and a noticeable rise in its cost effectiveness over competing technologies.

**[0003]** A twisted-nematic (TN) mode liquid crystal display device, which used to be used extensively in the past, is subjected to an alignment treatment such that the major axes of its liquid crystal molecules, exhibiting positive dielectric anisotropy, are substantially parallel to the respective principal surfaces of upper and lower substrates and are twisted by about 90 degrees in the thickness direction of the liquid crystal layer between the upper and lower substrates. When a voltage is applied to the liquid crystal layer, the liquid crystal molecules change their orientation directions into a direction that is parallel to the electric field applied. As a result, the twisted orientation disappears. The TN mode liquid crystal display device utilizes variation in the optical rotatory characteristic of its liquid crystal layer due to the change of orientation directions of the liquid crystal molecules in response to the voltage applied, thereby controlling the quantity of light transmitted.

**[0004]** The TN mode liquid crystal display device allows a broad enough manufacturing margin and achieves high productivity. However, the display performance (e.g., the viewing angle characteristic, in particular) thereof is not fully satisfactory. More specifically, when an image on the screen of the TN mode liquid crystal display device is viewed obliquely, the contrast ratio of the image decreases significantly. In that case, even an image, of which the grayscales ranging from black to white are clearly observable when the image is viewed straightforward, loses much of the difference in luminance between those grayscales when viewed obliquely. Furthermore, the grayscale characteristic of the image being displayed thereon may sometimes invert itself. That is to say, a portion of an image, which looks darker when viewed straight, may look brighter when viewed obliquely. This is a so-called "grayscale inversion phenomenon".

**[0005]** To improve the viewing angle characteristic of such a TN mode liquid crystal display device, an inplane switching (IPS) mode liquid crystal display device, a multi-domain vertical aligned (MVA) mode liquid crystal display device, an axisymmetric aligned (ASM) mode liquid crystal display device, and other types of liquid crystal display devices were developed recently. Liquid crystal displays employing any of the novel modes described above (wide viewing angle modes) solve the concrete problems with viewing angle characteristics, specifically, the problems that the display contrast ratio decreases considerably or the grayscales invert when the display surface of the display is viewed obliquely.

**[0006]** Although the display qualities of LCDs have been further improved nowadays, a viewing angle characteristic problem in a different phase has arisen just recently. Specifically, the  $\gamma$  characteristic of LCDs would vary with the viewing angle. That is to say, the r characteristic when an image on the screen is viewed straight is different from the characteristic when it is viewed obliquely. As used herein, the " $\gamma$  characteristic" refers to the grayscale dependence of display luminance. That is why if the  $\gamma$  characteristic when the image is viewed straight is different from the characteristic when the same image is viewed obliquely, then it means that the grayscale display state changes according to the viewing direction. This is a serious problem particularly when a still picture such as a photo is presented or when a TV program is displayed. **[0007]** According to a known method, such viewing angle dependence of the  $\gamma$  characteristic can be reduced by providing two or more subpixels for each single pixel and by making the luminance of one of the two subpixels different from that of the other when a moderate luminance is displayed (see Patent Documents Nos. 1 and 2, for example).

[0008] Specifically, the liquid crystal display device disclosed in Patent Document No.1 applies a different effective voltage to the liquid crystal layer of a second subpixel from the one applied to the liquid crystal layer of a first subpixel when a moderate luminance is displayed, thereby making the luminances of the first and second subpixels different from each other and reducing the viewing angle dependence of the r characteristic. The transmittance of the liquid crystal layer changes with the absolute value of the effective voltage irrespective of the direction of the electric field applied to the liquid crystal layer (i.e., the direction of the electric line of force). Thus, the liquid crystal display device disclosed in Patent Document No. 1 inverts the direction of the electric field applied to the liquid crystal layer alternately every vertical scanning period, thereby flattening the uneven distribution of DC levels and overcoming residual image and other reliability-related problems.

**[0009]** Meanwhile, the liquid crystal display device disclosed in Patent Document No. 2 inverts the brightness levels of first and second subpixels every vertical scanning period (e.g., makes the luminance of the first subpixel higher than that of the second subpixel in a first vertical scanning period but makes the luminance of the second subpixel higher

than that of the first subpixel in a second vertical scanning period). In addition, the device also inverts the direction of the electric field applied to the liquid crystal layer every vertical scanning period, too. If one of multiple subpixels were always bright, then the image on the screen would look non-smooth. However, the liquid crystal display device disclosed in Patent Document No. 2 minimizes such non-smoothness of the image on the screen by inverting the brightness levels of the first and second subpixels one vertical scanning period after another.

**[0010]** It should be noted that such a display or driving method that reduces the viewing angle dependence of the  $\gamma$  characteristic by making the luminances of multiple subpixels different from each other will be referred to herein as a "multi-pixel display", a "multi-pixel drive", an "area grayscale display" or an "area grayscale drive".

Patent Document No. 1: Japanese Patent Application Laid-Open Publication No. 2004-62146

Patent Document No. 2: Japanese Patent Application Laid-Open Publication No. 2003-295160 (corresponding to United States Patent No. 6,958,791)

#### **DISCLOSURE OF INVENTION**

10

15

20

30

35

50

#### PROBLEMS TO BE SOLVED BY THE INVENTION

**[0011]** In the liquid crystal display device disclosed in Patent Document No. 1, as the luminance of the first subpixel is always higher than that of the second subpixel when a moderate luminance is displayed, the difference in brightness level between those subpixels may be quite sensible and the image presented may sometimes look non-smooth.

**[0012]** On the other hand, in the liquid crystal display device disclosed in Patent Document No. 2, as the direction of the electric field applied to the liquid crystal layer and the brightness levels of the subpixels are inverted every vertical scanning period, the direction of the electric field applied to the liquid crystal layer is always the same when one of the two subpixels is brighter than the other subpixel.

[0013] For example, in the liquid crystal display device disclosed in Patent Document No. 2, if the absolute value of the effective voltage applied to the first subpixel is greater than that of the effective voltage applied to the second subpixel to make the first subpixel look brighter than the second one in a vertical scanning period, the electric field applied to the liquid crystal layer is directed from a subpixel electrode toward a counter electrode. The electric field with such a direction is supposed to have a first polarity. In the next vertical scanning period, as the absolute value of the effective voltage applied to the second subpixel becomes greater than that of the effective voltage applied to the first subpixel to make the second subpixel look brighter than the first one, the electric field applied to the liquid crystal layer is directed from the counter electrode toward the subpixel electrode. The electric field with such a direction is supposed to have a second polarity. In the next vertical scanning period, as the absolute value of the effective voltage applied to the first subpixel becomes greater than that of the effective voltage applied to the second subpixel to make the first subpixel look brighter than the second subpixel, the electric field has the first polarity. And in the next vertical scanning period, as the absolute value of the effective voltage applied to the second subpixel becomes greater than that of the effective voltage applied to the first subpixel to make the second subpixel look brighter than the first one, the electric field has the second polarity. [0014] In this manner, in the liquid crystal display device disclosed in Patent Document No. 2, the electric field always has the first polarity when the effective voltage applied to the first subpixel has the greater absolute value and always has the second polarity when the effective voltage applied to the second subpixel has the greater absolute value. That is why the average effective voltages applied to the first and second subpixels have the first and second polarities,

**[0015]** In a normal liquid crystal display device, if the same image continues to be presented for a long time with the average of the voltages applied to a pixel kept unequal to zero (i.e., with a DC voltage component left in the voltage applied to the pixel), then that image that has been presented for a long time will still remain on the screen even when the images on the screen are changed after that. That is to say, a so-called "residual image" phenomenon will occur. To avoid such a residual image phenomenon, a normal liquid crystal display device performs an AC drive on (i.e., applies voltages with two different polarities but with the same absolute value to) pixels, thereby making the average of the voltages applied to the liquid crystal layer equal to zero. Furthermore, if the average of the voltages applied does not become equal to zero even by the AC drive, then the normal liquid crystal display device further regulates the counter voltage, thereby setting the average voltage equal to zero.

**[0016]** In the liquid crystal display device disclosed in Patent Document No. 2, however, the respective effective voltages applied to the first and second subpixels have mutually different averages. That is why even if the counter voltage is regulated, only the average voltage applied to one of the two subpixels can be made equal to zero and the average voltage applied to the other subpixel cannot be zero. In that case, the residual image phenomenon will occur in the subpixel with the non-zero average voltage. As a result, the residual image phenomenon cannot be eliminated from the overall display device. Consequently, in the liquid crystal display device disclosed in Patent Document No. 2, not both of the average voltages applied to the first and second subpixels can be equal to zero, and therefore, the

residual image and other reliability-related problems should arise.

**[0017]** In order to overcome the problems described above, the present invention has an object of providing a liquid crystal display device that can resolve those reliability-related problems such as non-smoothness of the image on the screen and the residual image phenomenon.

#### MEANS FOR SOLVING THE PROBLEMS

5

10

20

30

35

40

50

[0018] A liquid crystal display device according to the present invention includes a plurality of pixels, each including a first subpixel and a second subpixel. Each of the first and second subpixels includes: a counter electrode; a subpixel electrode; and a liquid crystal layer interposed between the counter electrode and the subpixel electrode. The subpixel electrodes of the first and second subpixels are provided separately from each other as first and second subpixel electrodes, respectively, while the first and second subpixels share the same counter electrode with each other. When a predetermined grayscale tone is displayed continuously through four or more consecutive even number of vertical scanning periods, the first and second subpixels have mutually different luminances in at least two of the even number of vertical scanning periods, first polarity periods that are included in the even number of vertical scanning periods and that maintain a first polarity are as long as second polarity periods that are also included in the even number of vertical scanning periods and that maintain a second polarity for each of the first and second subpixels, and in each of the first and second polarity periods, the difference between the average of effective voltages applied to the liquid crystal layer of the second subpixel is substantially equal to zero.

**[0019]** In one preferred embodiment, if the effective voltages applied to the respective liquid crystal layers of the first and second subpixels of each said pixel are represented by VLspa and VLspb, respectively, then two of the four consecutive vertical scanning periods are the first polarity periods and the other two vertical scanning periods are the second polarity periods. In at least one of the first polarity periods and the second polarity periods, one of the two vertical scanning periods thereof satisfies VLspa | > | VLspb | and the other vertical scanning period satisfies | VLspa | < | VLspb |.

**[0020]** In another preferred embodiment, if the effective voltages applied to the respective liquid crystal layers of the first and second subpixels of each said pixel are represented by VLspa and VLspb, respectively, then two of the four consecutive vertical scanning periods are the first polarity periods and the other two vertical scanning periods are the second polarity periods. In at least one of the first polarity periods and the second polarity periods, the | VLspa | and | VLspb | values of one of the two vertical scanning periods thereof are equal to those of the other vertical scanning period.

**[0021]** In this particular preferred embodiment, of the four vertical scanning periods, the number of vertical scanning periods that satisfy | VLspa | > | VLspb | is equal to that of vertical scanning periods that satisfy VLspa | < | VLspb |.

**[0022]** In still another preferred embodiment, the plurality of the pixels are arranged in column and row directions so as to form a matrix pattern, and in each of the plurality of the pixels, the first and second subpixels are arranged in the column direction.

**[0023]** In yet another preferred embodiment, in each of the plurality of the pixels, voltages applied to the first and second subpixel electrodes change as voltages on their associated storage capacitor lines vary.

**[0024]** In this particular preferred embodiment, in each of the plurality of the pixels, a voltage on a storage capacitor line associated with the first subpixel electrode and a voltage on a storage capacitor line associated with the second subpixel electrode change mutually differently.

**[0025]** In yet another preferred embodiment, a voltage applied to the second subpixel electrode of a particular one of the plurality of the pixels and a voltage applied to the first subpixel electrode of another pixel that is adjacent to the particular pixel in the column direction change as the voltage on their common storage capacitor line varies.

**[0026]** In an alternative preferred embodiment, a voltage applied to the second subpixel electrode of a particular one of the plurality of the pixels and a voltage applied to the first subpixel electrode of another pixel that is adjacent to the particular pixel in the column direction change as voltages on their associated storage capacitor lines vary.

**[0027]** In yet another preferred embodiment, in each of the plurality of the pixels, the first and second subpixel electrodes are connected to the same signal line by way of their associated switching element.

**[0028]** In yet another preferred embodiment, in each of the plurality of the pixels, the first and second subpixel electrodes are respectively connected to first and second signal lines by way of first and second switching elements, respectively.

[0029] In yet another preferred embodiment, in each of the first and second polarity periods, one of the two vertical scanning periods satisfies | VLspa | > | VLspb | and the other vertical scanning period satisfies VLspa | < | VLspb |.

**[0030]** In yet another preferred embodiment, in each of the plurality of the pixels, | VLspa | and | VLspb | switch their magnitudes every vertical scanning period and the polarities of the first and second subpixels are inverted every other vertical scanning period.

**[0031]** In yet another preferred embodiment, the frame frequency is 60 Hz.

**[0032]** In yet another preferred embodiment, in each of the plurality of the pixels, | VLspa | and | VLspb | switch their magnitudes every other vertical scanning period and the polarities of the first and second subpixels are inverted every

vertical scanning period.

[0033] In yet another preferred embodiment, the frame frequency is 120 Hz.

**[0034]** In yet another preferred embodiment, in each of the plurality of the pixels, | VLspa | and | VLspb | switch their magnitudes every other vertical scanning period and the polarities of the first and second subpixels are inverted every other vertical scanning period. | VLspa | and | VLspb | switch their magnitudes non-synchronously with the inversion of the polarities of the first and second subpixels.

**[0035]** In yet another preferred embodiment, in either the first polarity periods or the second polarity periods, one of the two vertical scanning periods satisfied | VLspa | > | VLspb | and the other vertical scanning period satisfies | VLspa | < | VLspb |. In the other polarity periods, VLspa is equal to VLspb in each of the two vertical scanning periods.

[0036] In this particular preferred embodiment, voltages on storage capacitor lines associated with the first and second subpixel electrodes change between a first level, a second level that is higher than the first level, and a third level that is higher than the second level.

[0037] In yet another preferred embodiment, the first and second subpixel electrodes have the same display area.

#### 15 EFFECTS OF THE INVENTION

**[0038]** The present invention provides a liquid crystal display device that can minimize the occurrence of reliability problems such as non-smoothness of image displayed or residual images.

#### BRIEF DESCRIPTION OF DRAWINGS

# [0039]

20

25

30

35

40

50

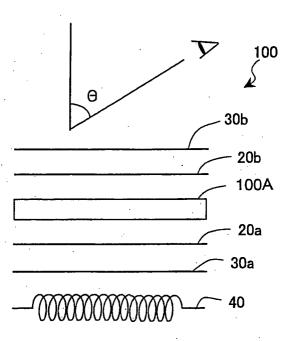

- FIG. 1 is a schematic representation illustrating the structure of a liquid crystal display device as a first preferred embodiment of the present invention.

- FIG. 2 is a schematic block diagram illustrating a liquid crystal panel for the liquid crystal display device of the first preferred embodiment.

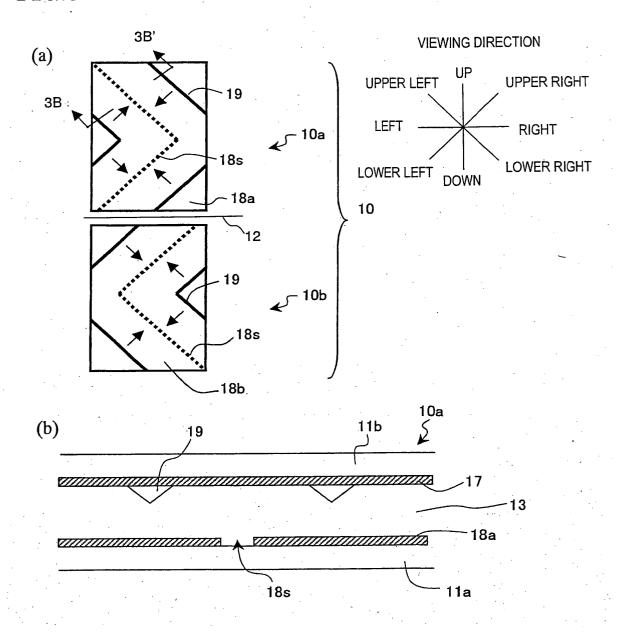

- FIG. **3(a)** is a schematic plan view illustrating a single pixel in the liquid crystal display device of the first preferred embodiment and FIG. **3(b)** is a schematic cross-sectional view illustrating a single subpixel thereof.

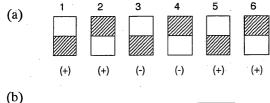

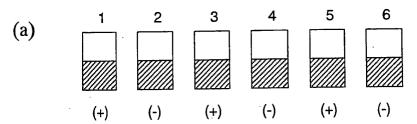

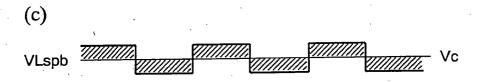

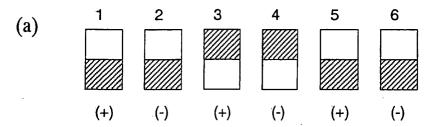

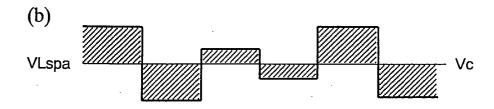

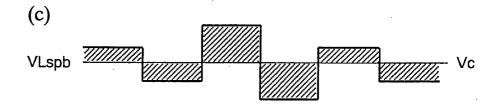

- FIG. 4 schematically shows how first and second subpixels change their brightness levels, polarities and effective voltages in a conventional liquid crystal display device, wherein portion (a) schematically shows how the first and second subpixels change their brightness levels and polarities and portions (b) and (c) schematically show how the effective voltages applied to the respective liquid crystal layers of the first and second subpixels change.

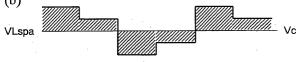

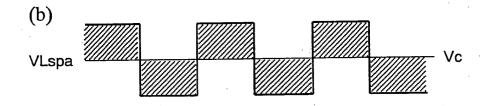

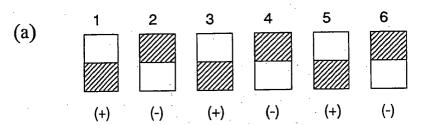

- FIG. 5 schematically shows how first and second subpixels change their brightness levels, polarities and effective voltages in another conventional liquid crystal display device, wherein portion (a) schematically shows how the first and second subpixels change their brightness levels and polarities and portions (b) and (c) schematically show how the effective voltages applied to the respective liquid crystal layers of the first and second subpixels change.

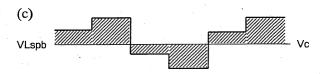

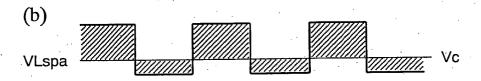

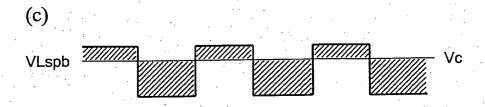

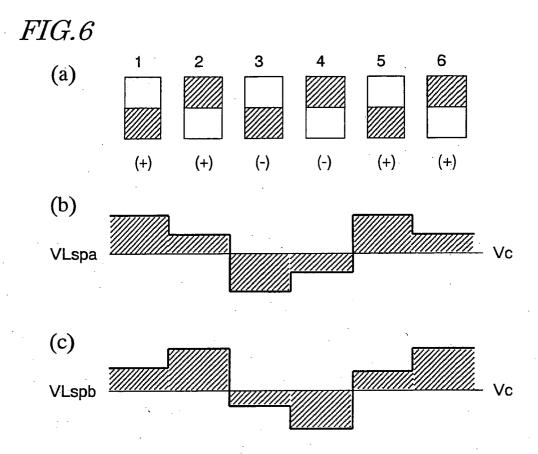

- FIG. 6 schematically shows how first and second subpixels change their brightness levels, polarities and effective voltages in the liquid crystal display device as the first preferred embodiment of the present invention, wherein portion (a) schematically shows how the first and second subpixels change their brightness levels and polarities and portions (b) and (c) schematically show how the effective voltages applied to the respective liquid crystal layers of the first and second subpixels change.

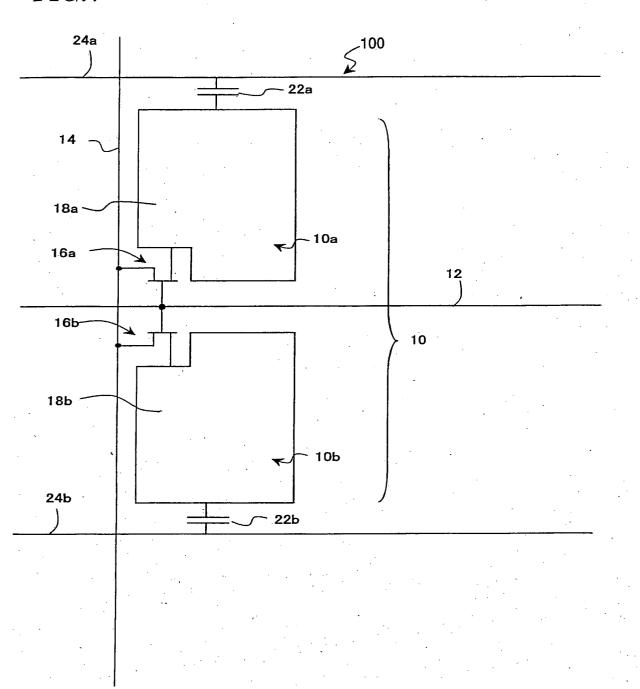

- FIG. **7** is a schematic representation illustrating an exemplary pixel structure for the liquid crystal display device of the first preferred embodiment.

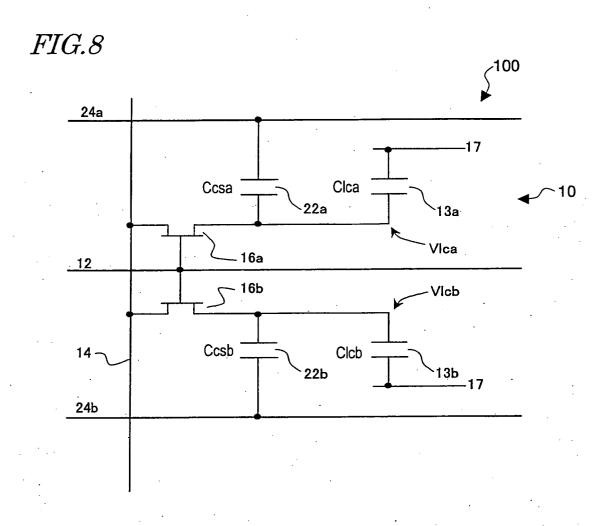

- FIG. **8** is an equivalent circuit diagram of a single pixel in the liquid crystal display device of the first preferred embodiment.

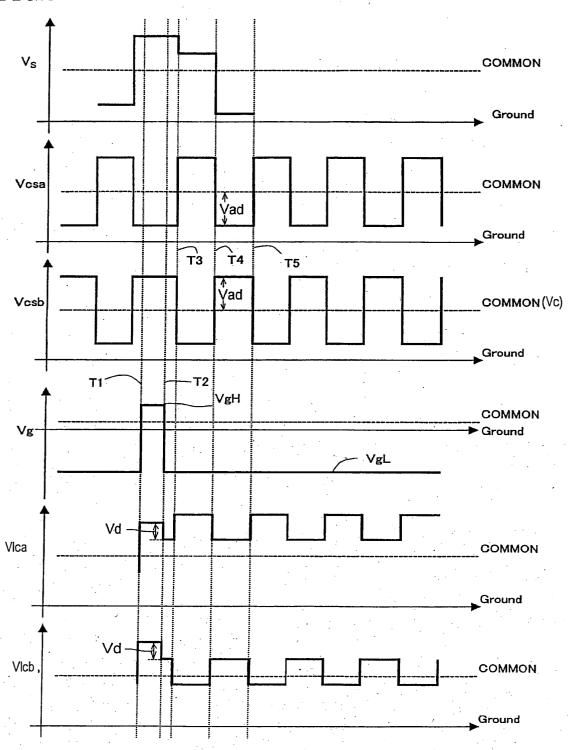

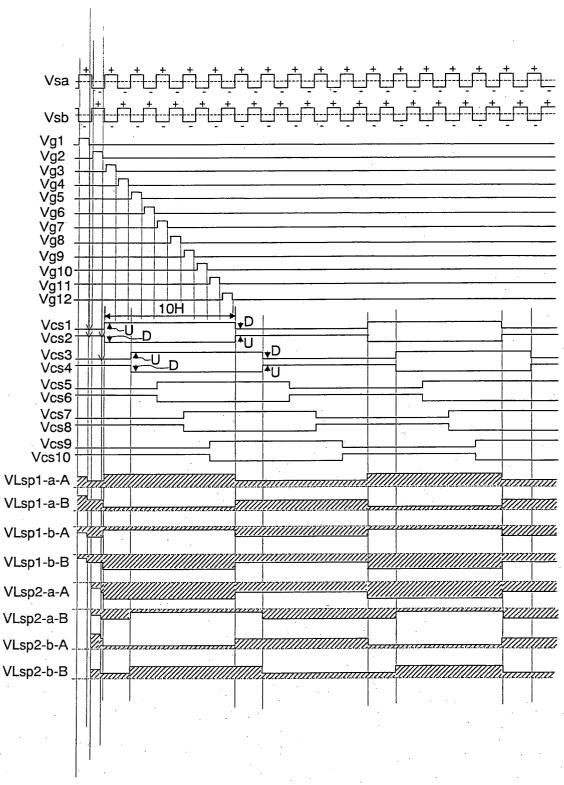

- FIG. **9** shows exemplary waveforms of voltages that are applied to drive the liquid crystal display device of the first preferred embodiment.

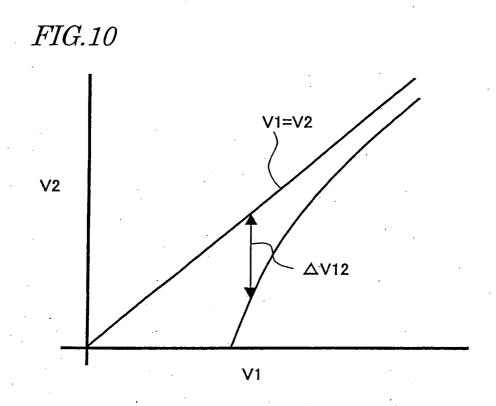

- FIG. **10** shows a relation between the effective voltages applied to the respective liquid crystal layers of subpixels in the liquid crystal display device of the first preferred embodiment.

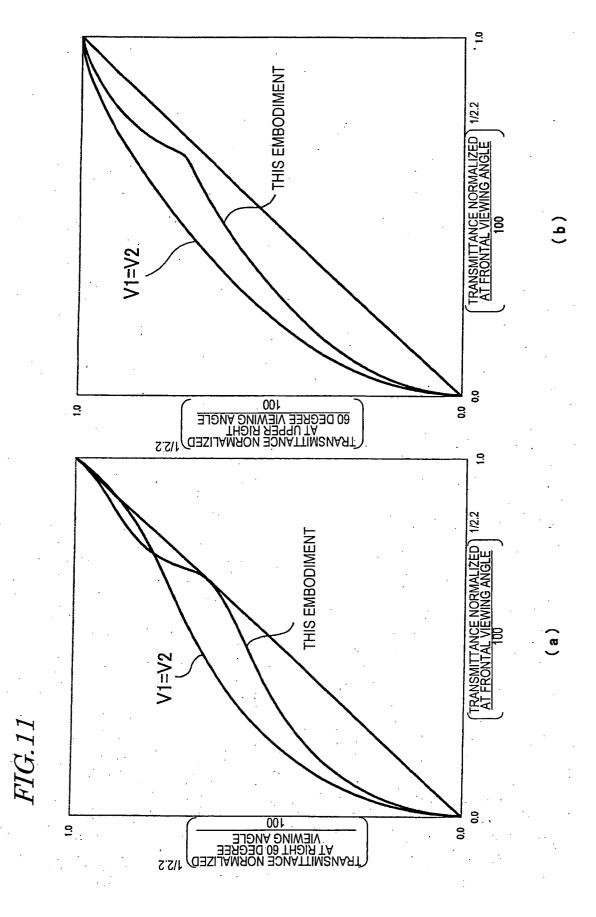

- FIGS. **11(a)** and **11(b)** show the  $\gamma$  characteristics of the liquid crystal display device of the first preferred embodiment at a right 60 degree viewing angle and at an upper right 60 degree viewing angle, respectively.

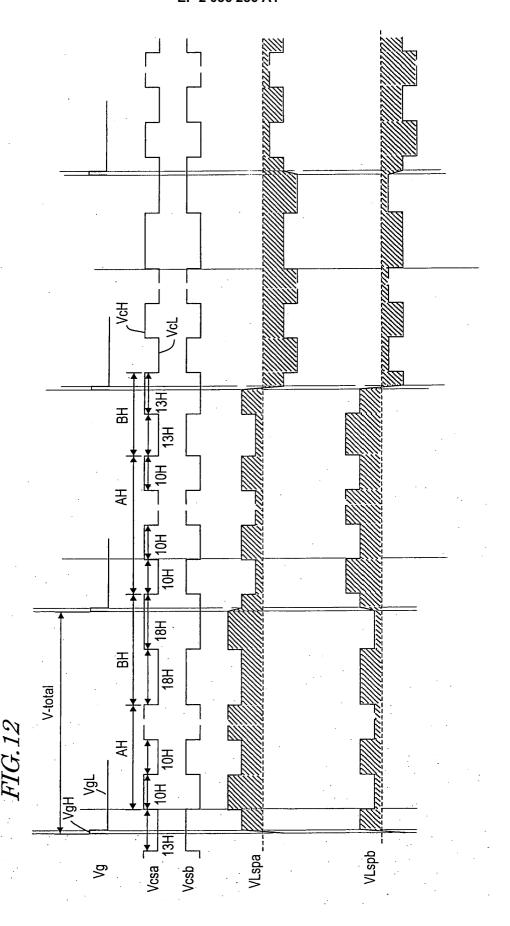

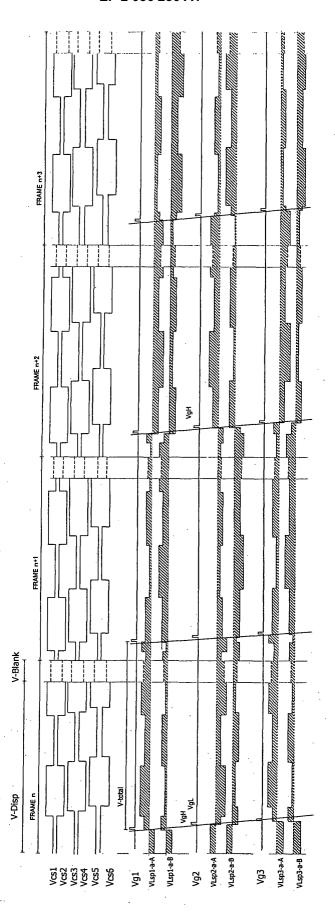

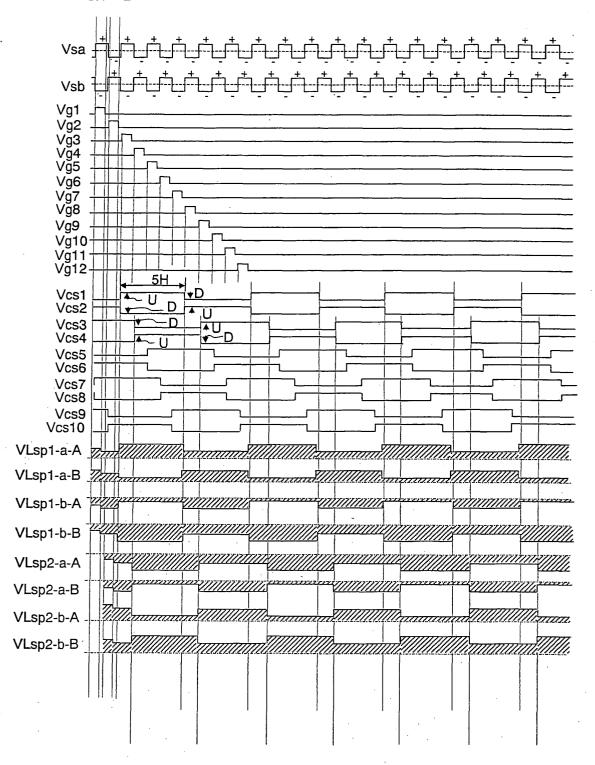

- FIG. **12** shows exemplary waveforms of various voltages to be applied over a number of vertical scanning periods to the liquid crystal display device of the first preferred embodiment.

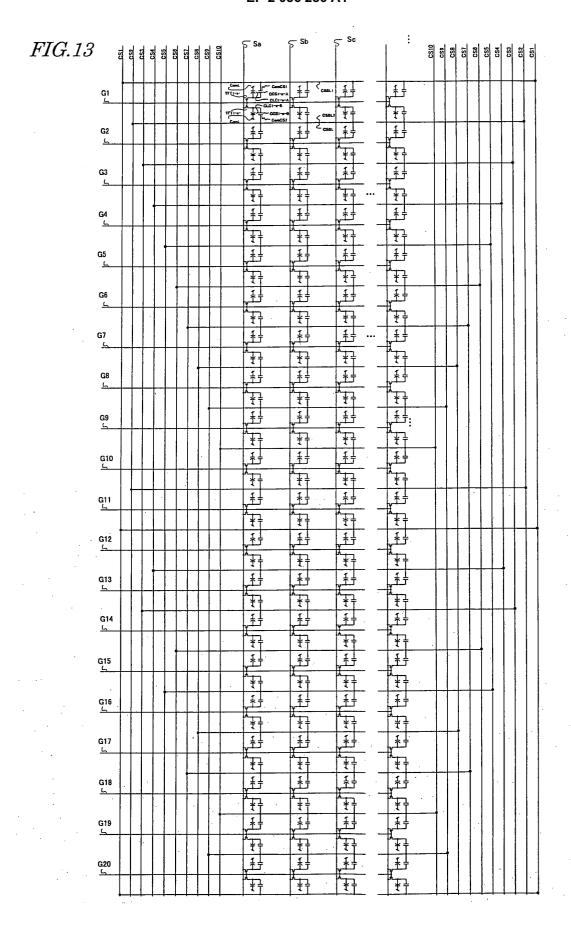

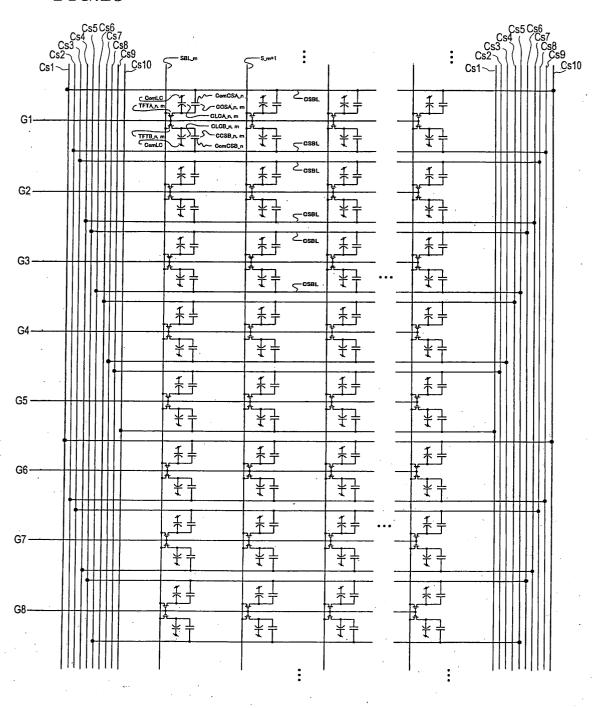

- FIG. **13** shows an exemplary equivalent circuit diagram of the liquid crystal display device of the first preferred embodiment.

- FIG. **14** is a schematic representation illustrating the arrangement, brightness levels and polarities of multiple subpixels in the liquid crystal display device of the first preferred embodiment.

- FIG. 15 shows exemplary waveforms of various voltages to be applied to the liquid crystal display device of the first preferred embodiment.

- FIG. **16** shows exemplary waveforms of various voltages to be applied over a number of vertical scanning periods to the liquid crystal display device of the first preferred embodiment.

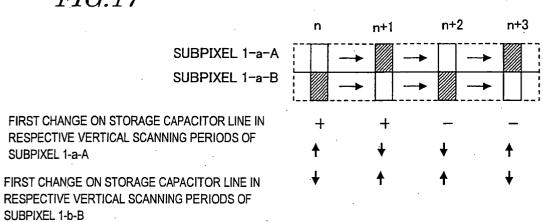

- FIG. 17 is a schematic representation illustrating the brightness levels and polarities of respective subpixels and the first change of storage capacitor voltages in respective vertical scanning periods of each subpixel in the liquid crystal display device of the first preferred embodiment.

5

15

20

35

45

50

55

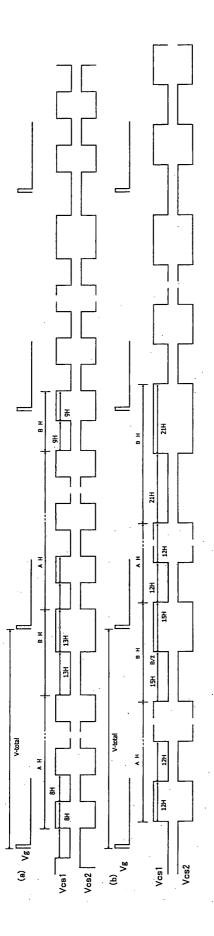

- Portions (a) and (b) of FIG. 18 show exemplary waveforms of various voltages to be applied over a number of vertical scanning periods to the liquid crystal display device of the first preferred embodiment.

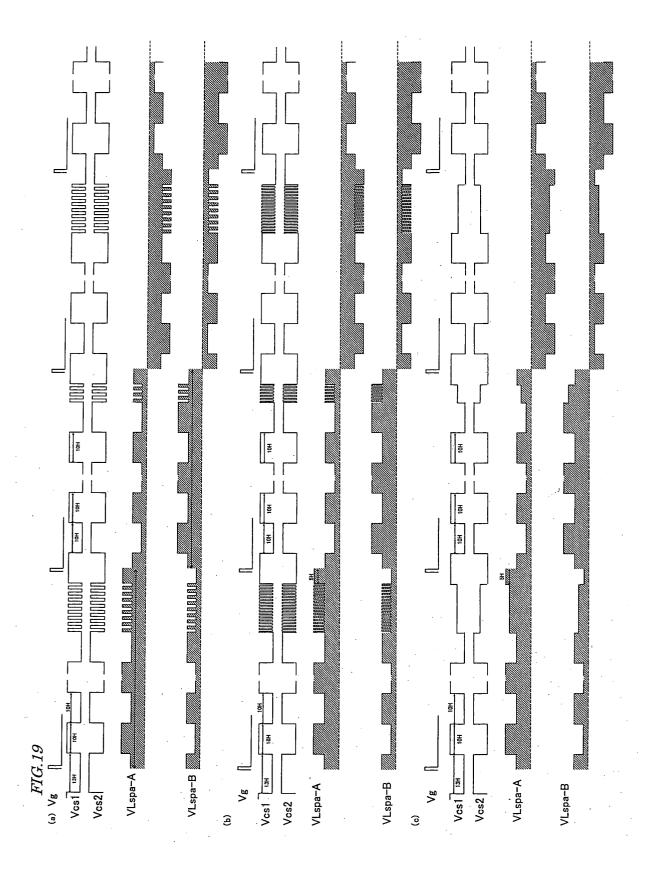

- Portions (a) to (c) of FIG. 19 show exemplary waveforms of various voltages to be applied over a number of vertical scanning periods to the liquid crystal display device of the first preferred embodiment.

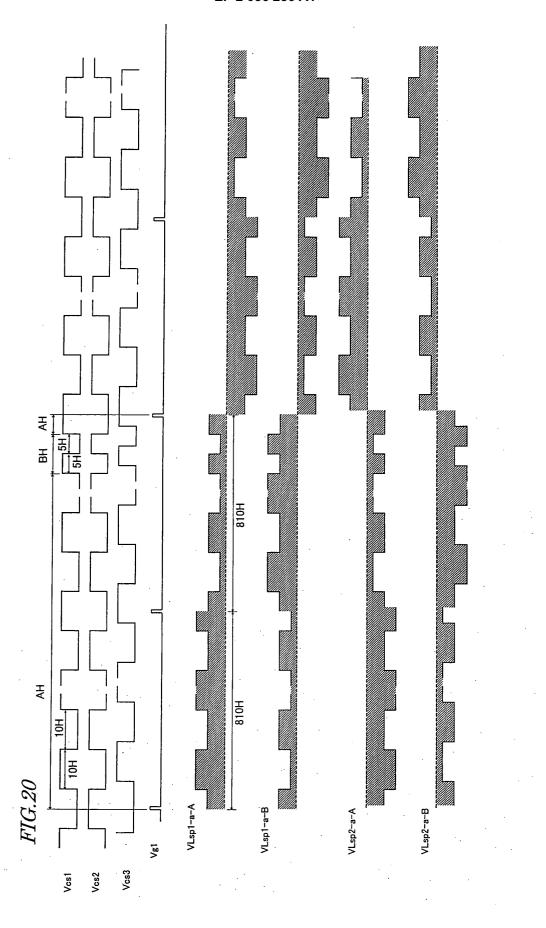

- FIG. **20** shows exemplary waveforms of various voltages to be applied over a number of vertical scanning periods to the liquid crystal display device of the first preferred embodiment.

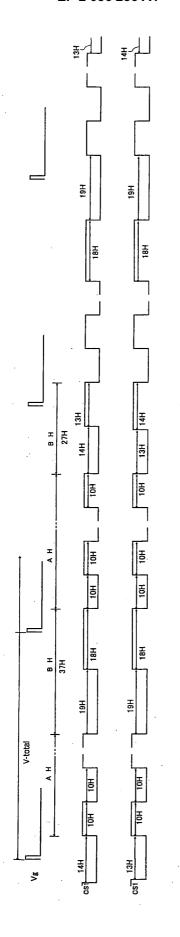

- FIG. **21** shows exemplary waveforms of various voltages to be applied over a number of vertical scanning periods to the liquid crystal display device of the first preferred embodiment.

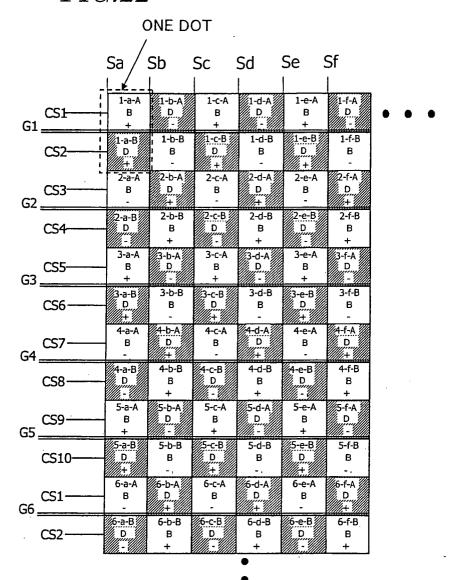

- FIG. 22 is a schematic representation illustrating the brightness levels and polarities of respective subpixels and the first change of storage capacitor voltages in respective vertical scanning periods of each subpixel in the liquid crystal display device of the first preferred embodiment.

- FIG. 23 shows an exemplary equivalent circuit diagram of the liquid crystal display device of the first preferred embodiment.

- FIG. **24** shows exemplary waveforms of various voltages to be applied to the liquid crystal display device of the first preferred embodiment.

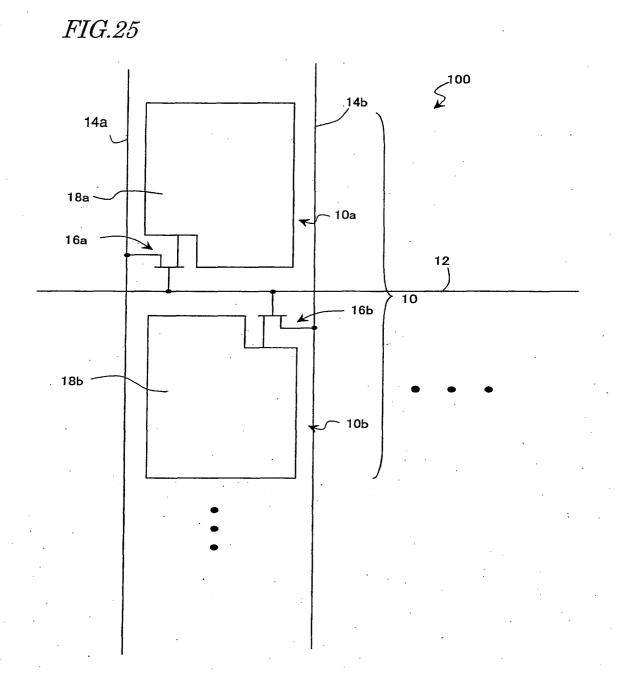

- FIG. **25** is a schematic representation illustrating an exemplary pixel structure for the liquid crystal display device of the first preferred embodiment.

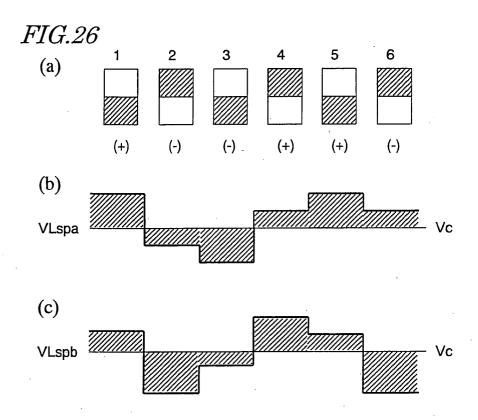

- FIG. **26** schematically shows how first and second subpixels change their brightness levels, polarities and effective voltages in a liquid crystal display device as a second preferred embodiment of the present invention, wherein portion (a) schematically shows how the first and second subpixels change their brightness levels and polarities and portions (b) and (c) schematically show how the effective voltages applied to the respective liquid crystal layers of the first and second subpixels change.

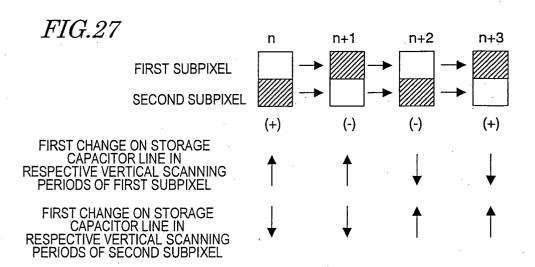

- FIG. **27** is a schematic representation illustrating the brightness levels and polarities of respective subpixels and the first change of storage capacitor voltages in respective vertical scanning periods of each subpixel in the liquid crystal display device of the second preferred embodiment.

- FIG. 28 schematically shows how first and second subpixels change their brightness levels, polarities and effective voltages in a liquid crystal display device as a third preferred embodiment of the present invention, wherein portion (a) schematically shows how the first and second subpixels change their brightness levels and polarities and portions (b) and (c) schematically show how the effective voltages applied to the respective liquid crystal layers of the first and second subpixels change.

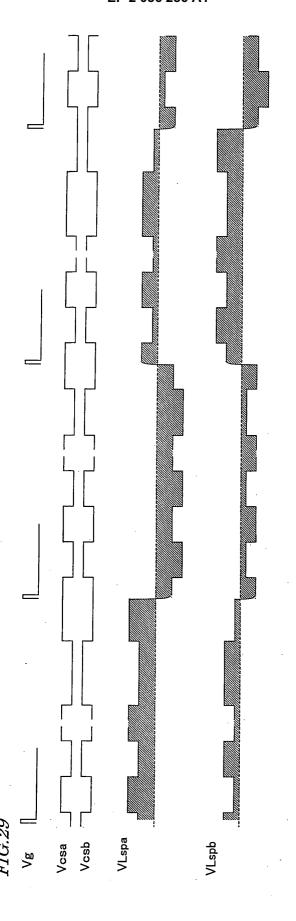

- FIG. 29 shows exemplary waveforms of various voltages to be applied to the liquid crystal display device of the third preferred embodiment.

- FIG. **30** is a schematic representation illustrating the brightness levels and polarities of respective subpixels and the first change of storage capacitor voltages in respective vertical scanning periods of each subpixel in the liquid crystal display device of the third preferred embodiment.

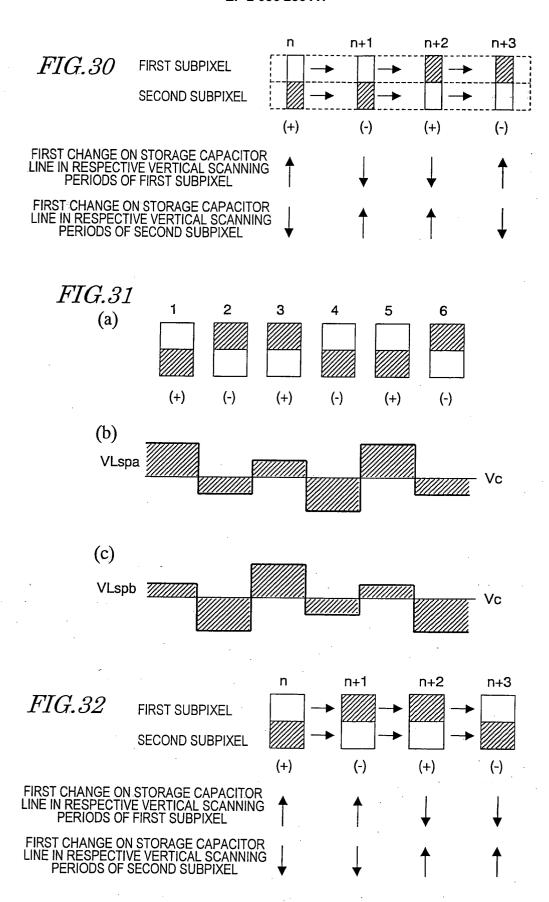

- FIG. 31 schematically shows how first and second subpixels change their brightness levels, polarities and effective voltages in a liquid crystal display device as a fourth preferred embodiment of the present invention, wherein portion (a) schematically shows how the first and second subpixels change their brightness levels and polarities and portions (b) and (c) schematically show how the effective voltages applied to the respective liquid crystal layers of the first and second subpixels change.

- FIG. 32 is a schematic representation illustrating the brightness levels and polarities of respective subpixels and the first change of storage capacitor voltages in respective vertical scanning periods of each subpixel in the liquid crystal display device of the fourth preferred embodiment.

- FIG. 33 schematically shows how first and second subpixels change their brightness levels, polarities and effective voltages in a liquid crystal display device as a fifth preferred embodiment of the present invention, wherein portion (a) schematically shows how the first and second subpixels change their brightness levels and polarities and portions (b) and (c) schematically show how the effective voltages applied to the respective liquid crystal layers of the first and second subpixels change.

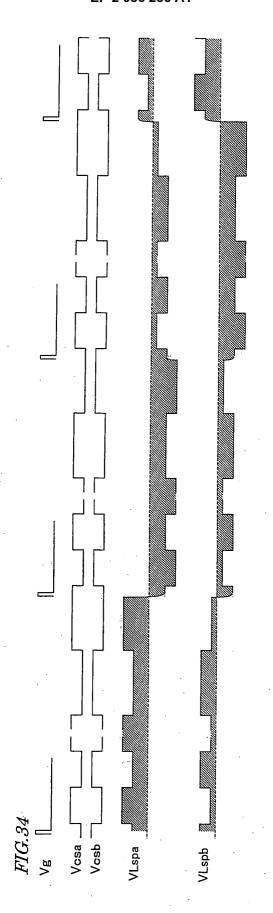

- FIG. **34** shows exemplary waveforms of various voltages to be applied to the liquid crystal display device of the fifth preferred embodiment.

- FIG. 35 is a schematic representation illustrating the brightness levels and polarities of respective subpixels and

the first change of storage capacitor voltages in respective vertical scanning periods of each subpixel in the liquid crystal display device of the fifth preferred embodiment.

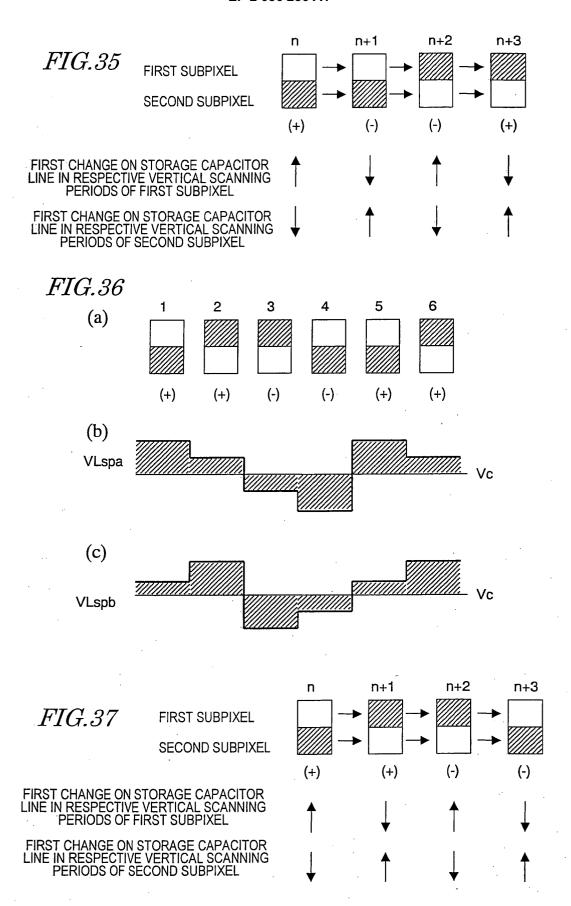

FIG. 36 schematically shows how first and second subpixels change their brightness levels, polarities and effective voltages in a liquid crystal display device as a sixth preferred embodiment of the present invention, wherein portion (a) schematically shows how the first and second subpixels change their brightness levels and polarities and portions (b) and (c) schematically show how the effective voltages applied to the respective liquid crystal layers of the first and second subpixels change.

FIG. 37 is a schematic representation illustrating the brightness levels and polarities of respective subpixels and the first change of storage capacitor voltages in respective vertical scanning periods of each subpixel in the liquid crystal display device of the sixth preferred embodiment.

FIG. 38 schematically shows how first and second subpixels change their brightness levels, polarities and effective voltages in a liquid crystal display device as a seventh preferred embodiment of the present invention, wherein portion (a) schematically shows how the first and second subpixels change their brightness levels and polarities and portions (b) and (c) schematically show how the effective voltages applied to the respective liquid crystal layers of the first and second subpixels change.

FIG. **39A** is a schematic representation illustrating the brightness levels and polarities of respective subpixels and the first change of storage capacitor voltages in respective vertical scanning periods of each subpixel in one frame for the liquid crystal display device of the seventh preferred embodiment.

FIG. **39B** is a schematic representation illustrating the brightness levels and polarities of respective subpixels and the first change of storage capacitor voltages in respective vertical scanning periods of each subpixel in the next frame for the liquid crystal display device of the seventh preferred embodiment.

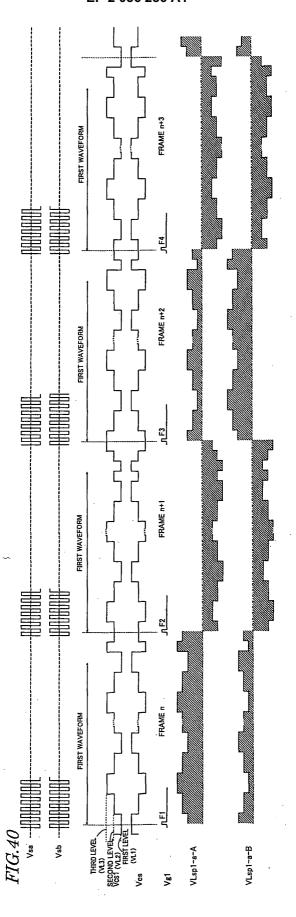

FIG. **40** shows exemplary waveforms of various voltages to be applied to the liquid crystal display device of the seventh preferred embodiment.

#### 25 DESCRIPTION OF REFERENCE NUMERALS

#### [0040]

5

10

15

20

35

40

50

10 pixel30 10a, 10b subpixel

13 liquid crystal layer17 counter electrode18a, 18b subpixel electrode

100 liquid crystal display device

100A liquid crystal panel

# **BEST MODE FOR CARRYING OUT THE INVENTION**

# **EMBODIMENT 1**

**[0041]** Hereinafter, a first preferred embodiment of a liquid crystal display device according to the present invention will be described with reference to the accompanying drawings.

[0042] First of all, the configuration of a liquid crystal display device 100 as the first preferred embodiment of the present invention will be outlined with reference to FIGS. 1 to 3. FIG. 1 illustrates the liquid crystal display device 100 of this preferred embodiment. The liquid crystal panel 100A of the liquid crystal display device 100 includes a display section 110 in which a number of pixels are arranged in columns and rows to define a matrix pattern and a driver 120 for driving the display section 110 as shown in FIG. 2. In the display section 110, each pixel includes a liquid crystal layer and a plurality of electrodes for applying a voltage to the liquid crystal layer. The driver 120 generates a drive signal based on an input video signal.

[0043] FIG. 3(a) is a schematic plan view illustrating the electrode structure of a single pixel, while FIG. 3(b) is a schematic cross-sectional view of a single subpixel as viewed on the plane 3B-3B' shown in FIG. 3(a). As shown in FIG. 3 (a), each pixel 10 includes first and second subpixels 10a and 10b that are arranged in the column direction. As shown in FIG. 3(b), the first subpixel 10a includes a liquid crystal layer 13, a first subpixel electrode 18a, and a counter electrode 17 that faces the first subpixel electrode 18a with the liquid crystal layer 13 interposed between them. Although FIG. 3(b) illustrates the configuration of only the first subpixel 10a, the second subpixel 10b has the same configuration as the one illustrated in FIG. 3(b). The counter electrode 17 is typically provided as a single common electrode for every pixel 10. In the liquid crystal display device 100 of this preferred embodiment, mutually different voltages are applicable to the first and second subpixel electrodes 18a and 18b, thus making the effective voltage applied to the liquid crystal

layer of the first subpixel 10a different from the one applied to that of the second subpixel 10b.

10

20

30

35

40

50

[0044] Next, it will be described with reference to FIGS. 4 through 6 and in comparison with the liquid crystal display devices disclosed in Patent Documents Nos. 1 and 2 how the brightness levels of the subpixels and the directions of the electric field (or electric line of force) change in the liquid crystal display device 100 of this preferred embodiment. In the following description, each pixel is supposed to display a predetermined grayscale tone for several frames on end for the sake of simplicity.

[0045] First of all, it will be described with reference to FIG. 4 how the brightness levels of the subpixels and the directions of the electric field change and how the effective voltages applied to the respective liquid crystal layers of the first and second subpixels change in the liquid crystal display device disclosed in Patent Document No. 1. In portion (a) of FIG. 4, the reference numerals 1 through 6 denote respective vertical scanning periods. As used herein, one "vertical scanning period" is defined to be an interval between a point in time when one scan line is selected to write a display signal voltage and a point in time when that scan line is selected to write the next display signal voltage. Also, each of one frame period of a non-interlaced drive input video signal and one field period of an interlaced drive input video signal will be referred to herein as "one vertical scanning period of the input video signal". Normally, one vertical scanning period of a liquid crystal display device corresponds to one vertical scanning period of the input video signal. In the example to be described below, one vertical scanning period of the liquid crystal panel is supposed to correspond to that of the input video signal for the sake of simplicity. However, the present invention is in no way limited to that specific preferred embodiment. The present invention is also applicable to a so-called "2x drive" with a vertical scanning frequency of 120 Hz in which two vertical scanning periods of the liquid crystal panel (that lasts  $2\times1/120$  sec, for example) are allocated to one vertical scanning period of the input video signal (that lasts 1/60 sec, for example). Also, in this example, the lengths of the respective vertical scanning periods are supposed to be equal to each other. Furthermore, in each vertical scanning period, the interval between a point in time when one scan line is selected and a point in time when the next scan line is selected will be referred to herein as one horizontal scanning period (1H).

[0046] In portion (a) of FIG. 4, the upper and lower rectangles represent the first and second subpixels, respectively. Of these two subpixels, the one with the higher luminance is plain, while the other with the lower luminance is shadowed. Also, in portion (a) of FIG. 4, "+" and "-" represent the polarities of the display signal voltages when the associated scan line is selected with respect to the common voltage applied to the counter electrode. In this case, "+" indicates that the potential at the first and second subpixel electrodes is higher than the one at the counter electrode and that the electric field is directed from the subpixel electrodes toward the counter electrode. On the other hand, "-" indicates that the potential at the first and second subpixel electrodes is lower than the one at the counter electrode and that the electric field is directed from the counter electrode toward the subpixel electrodes. In the following description, "+" and "-" will be referred to herein as a "first polarity" and a "second polarity", respectively, and will also be collectively referred to herein as a "first polarities". Also, a period with the "+" polarity and a period with the "-" polarity will be referred to herein as a "first polarity period" and a "second polarity period", respectively.

[0047] As shown in portion (a) of FIG. 4, the first, third and fifth periods are first polarity periods, the second, fourth and sixth periods are second polarity periods, and the polarity inverts every vertical scanning period in the liquid crystal display device disclosed in Patent Document No. 1. As also shown in portion (a) of FIG. 4, in any of the first through sixth periods, the first subpixel has a higher luminance than the second subpixel in the device of Patent Document No. 1. [0048] Portions (b) and (c) of FIG. 4 show the effective voltages VLspa and VLspb that are applied to the respective liquid crystal layers of the first and second subpixels in the respective vertical scanning periods in the liquid crystal display device of Patent Document No. 1. The levels of these voltages are indicated by the bold lines. The effective voltages VLspa and VLspb applied to the respective liquid crystal layers of the first and second subpixels are the effective values of the differences between the voltages applied to the first and second subpixel electrodes and the voltage Vc applied to the counter electrode. In this example, the voltage Vc applied to the counter electrode is shown as being constant. Although not shown in portions (b) and (c) of FIG. 4, the voltages applied to the respective liquid crystal layers of the first and second subpixels may also be changed within the same vertical scanning period by varying the voltage on the storage capacitor line as disclosed in Patent Document No. 1.

[0049] In the first period, the voltages applied to the first and second subpixel electrodes are higher than the voltage applied to the counter electrode, and the absolute value of the effective voltage applied to the liquid crystal layer of the first subpixel is greater than that of the effective voltage applied to that of the second subpixel ( | VLspa | > | VLspb |). For that reason, as shown in portion (a) of FIG. 4, the first period is a first polarity period and the first subpixel is brighter than the second subpixel. However, on the transition from the first period into the second period, the effective voltages VLspa and VLspb applied to the respective liquid crystal layers of the first and second subpixels change. In the second period, the voltages applied to the first and second subpixel electrodes are lower than the voltage applied to the counter electrode, and the absolute value of the effective voltage applied to the liquid crystal layer of the first subpixel is greater than that of the effective voltage applied to that of the second subpixel ( | VLspa | > | VLspb |). For that reason, as shown in portion (a) of FIG. 4, the second period is a second polarity period and the first subpixel is brighter than the second subpixel.

**[0050]** From the third period on, the same brightness levels and polarities of the first and second subpixels as those of the first and second periods just appear repeatedly. Consequently, in the liquid crystal display device disclosed in Patent Document No. 1, the luminance of the first subpixel is always higher than that of the second subpixel, the difference in brightness level between those subpixels is quite sensible, and the image on the screen looks non-smooth as can be seen from portion (a) of FIG. 4.

**[0051]** Next, it will be described with reference to FIG. **5** how the brightness levels of the subpixels, the directions of the electric field, and the effective voltages applied to the respective liquid crystal layers of the first and second subpixel change in the liquid crystal display device disclosed in Patent Document No. 2.

**[0052]** As shown in portion **(a)** of FIG. **5,** in the liquid crystal display device disclosed in Patent Document No. 2, the first, third and fifth periods are also first polarity periods, the second, fourth and sixth periods are second polarity periods, and the polarity inverts every vertical scanning period. Meanwhile, in the liquid crystal display device of Patent Document No. 2, the luminance of the first subpixel is higher than that of the second subpixel in the first, third and fifth periods but the luminance of the second subpixel is higher than that of the first subpixel in the second, fourth and sixth periods.

10

20

30

35

40

50

55

[0053] Portions (b) and (c) of FIG. 5 show the effective voltages VLspa and VLspb that are applied to the respective liquid crystal layers of the first and second subpixels in the respective vertical scanning periods. The levels of these voltages are indicated by the bold lines. Although not shown in portions (b) and (c) of FIG. 5, the voltages applied to the respective liquid crystal layers of the first and second subpixels may also be changed within the same vertical scanning period by varying the voltage on the storage capacitor line as disclosed in Patent Document No. 1.

[0054] In the first period, the voltages applied to the first and second subpixel electrodes are higher than the voltage applied to the counter electrode, and the absolute value of the effective voltage applied to the liquid crystal layer of the first subpixel is greater than that of the effective voltage applied to that of the second subpixel ( | VLspa | > | VLspb | ). For that reason, as shown in portion (a) of FIG. 5, the first period is a first polarity period and the first subpixel is brighter than the second subpixel. However, on the transition from the first period into the second period, the effective voltages VLspa and VLspb applied to the respective liquid crystal layers of the first and second subpixels change. In the second period, the voltages applied to the first and second subpixel electrodes are lower than the voltage applied to the counter electrode, and the absolute value of the effective voltage applied to the liquid crystal layer of the second subpixel is greater than that of the effective voltage applied to that of the first subpixel ( | VLspa | < | VLspb |). For that reason, as shown in portion (a) of FIG. 5, the second period is a second polarity period and the second subpixel is brighter than the first subpixel.

[0055] From the third period on, the same brightness levels and polarities of the first and second subpixels as those of the first and second periods just appear repeatedly. In the liquid crystal display device disclosed in Patent Document No. 2, since not only the polarity but also the brightness levels of the subpixels are inverted every vertical scanning period, the first subpixel is sometimes brighter, but sometimes less bright, than the second subpixel unlike the liquid crystal display device disclosed in Patent Document No. 1. Consequently, the degree of non-smoothness on the screen can be reduced. In the liquid crystal display device disclosed in Patent Document No. 2, however, the period in which the first subpixel is brighter than the second subpixel is always the first polarity period and the period in which the second subpixel is brighter than the first subpixel is always the second polarity period. That is why as can be seen from portions (b) and (c) of FIGS. 5, the average of the effective voltages VLspa applied to the liquid crystal layer of the first subpixel over multiple vertical scanning periods (e.g., the first through fourth periods) is higher than the voltage Vc applied to the counter electrode, and the average of the effective voltages VLspb applied to the liquid crystal layer of the second subpixel over multiple vertical scanning periods (e.g., the first through fourth periods) is lower than the voltage Vc applied to the counter electrode. Thus, in the liquid crystal display device disclosed in Patent Document No. 2, the uneven distribution of DC levels among the respective subpixels still remains to produce residual image and other reliability-related problems.

**[0056]** Next, it will be described with reference to FIG. **6** how the brightness levels of the subpixels, the directions of the electric field, and the effective voltages applied to the respective liquid crystal layers of the first and second subpixel change in the liquid crystal display device 100 of this preferred embodiment.

[0057] As shown in portion (a) of FIG. 6, in the liquid crystal display device 100 of this preferred embodiment, the first, second, fifth and sixth periods are first polarity periods, while the third and fourth periods are second polarity periods. As described above, the first polarity period is a period in which the voltages applied to the first and second subpixel electrodes are higher than the one applied to the counter electrode, while the second polarity period is a period in which the voltages applied to the first and second subpixel electrodes are lower than the one applied to the counter electrode. Look at four consecutive vertical scanning periods, and it can be seen that two out of the four periods are first polarity periods and the other two are second polarity periods. For example, in the first through fourth periods shown in portion (a) of FIG. 6, the first and second periods are first polarity periods and the third and fourth periods are second polarity periods.

[0058] Portions (b) and (c) of FIG. 6 show the effective voltages VLspa and VLspb that are applied to the respective liquid crystal layers of the first and second subpixels in the respective vertical scanning periods. The levels of these

voltages are indicated by the bold lines. In this preferred embodiment, the voltages applied to the respective liquid crystal layers of the first and second subpixels may also be changed within the same vertical scanning period by varying the voltage on the storage capacitor line just as disclosed in Patent Documents Nos. 1 and 2. Also, since the voltage Vc applied to the counter electrode is used as a reference voltage in portions (b) and (c) of FIG. 6, the voltage Vc applied to the counter electrode is illustrated as being constant irrespective of time. However, the voltage Vc applied to the counter electrode may also vary with time.

[0059] In the first period, the voltages applied to the first and second subpixel electrodes are higher than the voltage applied to the counter electrode, and the absolute value of the effective voltage applied to the liquid crystal layer of the first subpixel is greater than that of the effective voltage applied to that of the second subpixel ( | VLspa | > | VLspb |). For that reason, as shown in portion (a) of FIG. 6, the first period is a first polarity period and the first subpixel is brighter than the second subpixel.

**[0060]** However, on the transition from the first period into the second period, the effective voltages **VLspa** and **VLspb** applied to the respective liquid crystal layers of the first and second subpixels change. In the second period, the voltages applied to the first and second subpixel electrodes are higher than the voltage applied to the counter electrode, and the absolute value of the effective voltage applied to the liquid crystal layer of the second subpixel is greater than that of the effective voltage applied to that of the first subpixel ( | VLspa | < | VLspb |). For that reason, as shown in portion (a) of FIG. **6**, the second period is a first polarity period and the second subpixel is brighter than the first subpixel.

[0061] In the third period, the voltages applied to the first and second subpixel electrodes are lower than the voltage applied to the counter electrode, and the absolute value of the effective voltage applied to the liquid crystal layer of the first subpixel is greater than that of the effective voltage applied to that of the second subpixel ( | VLspa | > | VLspb | ) For that reason, as shown in portion (a) of FIG. 6, the third period is a second polarity period and the first subpixel is brighter than the second subpixel.

20

30

35

40

50

**[0062]** In the fourth period, the voltages applied to the first and second subpixel electrodes are lower than the voltage applied to the counter electrode, and the absolute value of the effective voltage applied to the liquid crystal layer of the second subpixel is greater than that of the effective voltage applied to that of the first subpixel ( | VLspa | < | VLspb |). For that reason, as shown in portion **(a)** of FIG. 6, the fourth period is a second polarity period and the second subpixel is brighter than the first subpixel. After that, from the fifth period on, the brightness levels and polarities of the first and second subpixels just repeat those of the first and second subpixels in the first through fourth periods.

[0063] As described above, in the liquid crystal display device 100 of this preferred embodiment, two out of four consecutive vertical scanning periods are first polarity periods, one of which satisfies | VLspa | > | VLspb | (e.g., the first period) and the other of which satisfies VLspa | | < | VLspb | (e.g., the second period). The two other ones of the four consecutive vertical scanning periods are second polarity periods, one of which satisfies | VLspa | > | VLspb | (e.g., the third period) and the other of which satisfies VLspa | < | VLspb | (e.g., the fourth period). As can be seen from portion (a) of FIG. 6, in the liquid crystal display device 100 of this preferred embodiment, the brightness levels of the subpixels are inverted every vertical scanning period and the polarity is inverted every other vertical scanning period. Specifically, the (brightness, polarity) combination of the first subpixel changes in the order of (B(right), +), (D(ark), +), (B, -) and (D, -), while the (brightness, polarity) combination of the second subpixel changes in the order of (D, +), (B, +), (D, -) and (B, -), where "B" indicates that the pixel is brighter than the other pixel and "D" indicates that the pixel is darker than the other. Since the effective voltages of the subpixels change in this manner, the difference between the average of the effective voltage applied to the liquid crystal layer of the first subpixel and that of the effective voltages applied to that of the second subpixel in each of the first and second polarity periods becomes substantially equal to zero.

[0064] Unlike the liquid crystal display device of Patent Document No. 1, the liquid crystal display device 100 of this preferred embodiment inverts the brightness levels of the subpixels every vertical scanning period, thus minimizing the degree of non-smoothness of the image on the screen. Also, in the liquid crystal display device 100 of this preferred embodiment, each pair of first and second polarity periods has a period that satisfies | VLspa | VLspb | and a period that satisfies | VLspa | < | VLspb | unlike the liquid crystal display device disclosed in Patent Document No. 2. Thus, as can be seen from portions (b) and (c) of FIG. 6, the average of the effective voltages VLspa and that of the effective voltages VLspb over multiple vertical scanning periods (e.g., the first through fourth periods) can be both equal to zero. Furthermore, even if the averages of the effective voltages VLspa and VLspb do not become equal to zero, the averages of the effective voltages VLspa and VLspb can be both controlled to zero by adjusting the counter voltage because the average of the effective voltages **VLspa** is approximately equal to that of the effective voltages **VLspb**. By controlling the averages of the effective voltages to zero in this manner, the residual image and other reliability-related problems can be overcome. It should be noted that various configurations could be used to apply mutually different voltages to the respective liquid crystal layers of the first and second subpixels such that the relations described above are satisfied. [0065] This preferred embodiment is preferably applied to a liquid crystal display device that uses a vertical alignment liquid crystal layer including a nematic liquid crystal material with negative dielectric anisotropy. Specifically, the liquid crystal layer of each subpixel preferably has four domains in which the liquid crystal molecules tilt in respective azimuth directions that are different from each other by approximately 90 degrees under a voltage applied (i.e., may operate in

the MVA mode). Alternatively, the liquid crystal layer of each subpixel may also have axisymmetric alignment at least when a voltage is applied thereto (i.e., may operate in the ASM mode).

[0066] Hereinafter, an MVA mode liquid crystal display device 100 according to this preferred embodiment will be described in further detail.

[0067] As shown in FIG. 1, the liquid crystal display device 100 includes a liquid crystal panel 100A, a pair of phase compensators (typically phase plates) 20a and 20b arranged on both sides of the liquid crystal panel 100A, a pair of polarizers 30a and 30b arranged to sandwich these members between them, and a backlight 40. The polarizers 30a and 30b are arranged as crossed Nicols such that their axes of transmission (which will also be referred to herein as "axes of polarization") cross each other at right angles. While no voltage is applied to the liquid crystal layer 13 of the liquid crystal panel 100A (see FIG. 3(b)), i.e., in a vertical alignment state, this device conducts black display. That is to say, this liquid crystal display device 100 is a normally black mode liquid crystal display device. The phase compensators 20a and 20b are provided to improve the viewing angle characteristic of the liquid crystal display device and may be designed as best ones by known technologies. Specifically, the phase compensators 20a and 20b may be optimized such that the difference in luminance between when the image is viewed obliquely and when the image is viewed straight in the black display mode (i.e., the difference in black luminance) is minimized in every azimuth direction.

[0068] As shown in FIG. 3(a), a scan line 12 is arranged between the first and second subpixel electrodes 18a and 18b. Naturally, scan lines 12, signal lines, TFTs (not shown in FIG. 3) and circuits for driving them are arranged on the substrate 11a to apply predetermined voltages to the first and second subpixel electrodes 18a and 18b at prescribed timings. On the other substrate 11b, color filters and other members are arranged as needed.

**[0069]** Next, the structure of a single pixel in the MVA mode liquid crystal display device 100 will be described with reference to FIGS. **3(a)** and **3(b)**. The basic configuration and operation of an MVA mode liquid crystal display device are disclosed in Japanese Patent Application Laid-Open Publication No. 11-242225.

20

30

35

50

[0070] As shown in FIG. 3(b), the subpixel electrode 18a on the glass substrate 11a has a slit 18s, and the subpixel electrode 18a and the counter electrode 17 together generate an oblique electric field in the liquid crystal layer 13. On the other hand, on the surface of the glass substrate 11b with the counter electrode 17, arranged are ribs 19 that protrude toward the liquid crystal layer 13, which is made of a nematic liquid crystal material with negative dielectric anisotropy. And by providing a vertical alignment film (not shown) that covers the counter electrode 17, the ribs 19 and the subpixel electrodes 18a and 18b, the liquid crystal layer 13 exhibits a substantially vertically aligned state when no voltages are applied thereto. That is to say, the vertically aligned liquid crystal molecules can be tilted toward a predetermined direction with stability by using the sloped side surfaces of the ribs 19 and the oblique electric field in combination.

[0071] As shown in FIG. 3(b), the ribs 19 have sloped side surfaces that are raised toward their center, and the liquid crystal molecules are aligned substantially perpendicularly to those tilted side surfaces. Consequently, the ribs 19 produce a distribution of tilt angles of the liquid crystal molecules. As used herein, the tilt angle of a liquid crystal molecule means the angle defined by the long axis of the molecules with respect to the surface of the substrate. Also, the slit 18s changes the directions of the electric field applied to the liquid crystal layer regularly. Due to the combined effects of these ribs 19 and the slit 18s, when an electric field is applied, the liquid crystal molecules are aligned in the four directions indicated by the arrows in FIG. 3(a), i.e., upper rightward, upper leftward, lower rightward and lower leftward. As a result, a good viewing angle characteristic that is symmetrical both vertically and horizontally is realized. The rectangular display area of the liquid crystal panel 100A is typically arranged such that its longitudinal direction is defined horizontally and the transmission axis of the polarizer 30a is defined to be parallel to the longitudinal direction. On the other hand, the pixels 10 are arranged such that the longitudinal direction of the pixels 10 intersects with that of the liquid crystal panel 100A at right angles.

[0072] As shown in FIG. 3(a), the first and second subpixels 10a and 10b preferably have the same area. Each of these subpixels preferably has a first rib that runs in a first direction and a second rib that runs in a second direction that intersects with the first direction substantially at right angles, and the first and second ribs are preferably arranged symmetrically to each other within each subpixel with respect to a centerline that is defined parallel to the scan line 12. And the arrangement of the ribs in one of the two subpixels and that of the ribs in the other subpixel are preferably symmetrical to each other with respect to a centerline that is drawn perpendicularly to the scan line 12. By adopting such an arrangement, the liquid crystal molecules are aligned upper rightward, upper leftward, lower rightward and lower leftward within each subpixel and the respective liquid crystal domains come to have substantially the same area in the entire pixel including the first and second subpixels. As a result, a good viewing angle characteristic that is symmetrical both vertically and horizontally is realized. This effect is achieved particularly significantly when a pixel has a small area. Furthermore, it is preferred to adopt a configuration in which the interval between the respective centerlines of the two subpixels that are drawn parallel to the scan line is approximately equal to a half of the arrangement pitch of the scan lines. [0073] Next, the specific structure of each pixel 10 in the liquid crystal display device 100 of this preferred embodiment and application of mutually different voltages to the respective liquid crystal layers of the two subpixels 10a and 10b included in this pixel 10 will be described with reference to FIGS. 7 through 9.

[0074] As shown in FIG. 7, the pixel 10 includes two subpixels 10a and 10b. To the subpixel electrodes 18a and 18b

of the subpixels 10a and 10b, connected are their associated TFTs 16a and 16b and their associated storage capacitors (CS) 22a and 22b, respectively. The gate electrodes of the TFTs 16a and 16b are both connected to the same scan line 12. And the source electrodes of the TFTs 16a and 16b are connected to the same signal line 14. The storage capacitors 22a and 22b are connected to their associated storage capacitor lines (CS bus lines) 24a and 24b, respectively. The storage capacitor 22a includes a storage capacitor electrode that is electrically connected to the subpixel electrode 18a, a storage capacitor counter electrode that is electrically connected to the storage capacitor line 24a, and an insulating layer (not shown) arranged between the electrodes. The storage capacitor counter electrode that is electrically connected to the storage capacitor line 24b, and an insulating layer (not shown) arranged between the electrodes. The respective storage capacitor counter electrodes of the storage capacitors 22a and 22b are independent of each other and can receive mutually different storage capacitor counter voltages from the storage capacitor lines 24a and 24b, respectively.

[0075] FIG. 8 schematically shows the equivalent circuit of one pixel 10 of the liquid crystal display device 100. In this electrical equivalent circuit, the liquid crystal layers of the subpixels 10a and 10b are identified by the reference numerals 13a and 13b, respectively. A liquid crystal capacitor formed of the subpixel electrode 18a, the liquid crystal layer 13a, and the counter electrode 17 will be identified by Clca. On the other hand, a liquid crystal capacitor formed of the subpixel electrode 18b, the liquid crystal layer 13b, and the counter electrode 17 will be identified by Clcb. The same counter electrode 17 is shared by these two subpixels 10a and 10b. The liquid crystal capacitors Clca and Clcb are supposed to have the same electrostatic capacitance CLC (V). The value of CLC (V) depends on the effective voltages (V) applied to the liquid crystal layers of the respective subpixels 10a and 10b. Also, the storage capacitors 22a and 22b that are connected independently of each other to the liquid crystal capacitors of the respective subpixels 10a and 10b will be identified herein by Ccsa and Ccsb, respectively, which are supposed to have the same electrostatic capacitance CCS. [0076] In the subpixel 10a, one electrode of the liquid crystal capacitor Clca and one electrode of the storage capacitor Ccsa are connected to the drain electrode of the TFT 16a, which functions as a switching element for the subpixel 10a. The other electrode of the liquid crystal capacitor Clca is connected to the counter electrode 17. And the other electrode of the storage capacitor Ccsa is connected to the storage capacitor line 24a. In the subpixel 10b, one electrode of the liquid crystal capacitor Clcb and one electrode of the storage capacitor Ccsb are connected to the drain electrode of the TFT 16b, which functions as a switching element for the subpixel 10b. The other electrode of the liquid crystal capacitor Clcb is connected to the counter electrode 17. And the other electrode of the storage capacitor Ccsb is connected to the storage capacitor line 24b. The gate electrodes of the TFTs 16a and 16b are both connected to the scan line 12 and the source electrodes thereof are both connected to the signal line 14.

[0077] FIG. 9 schematically shows how the respective voltages that are applied to drive the liquid crystal display device 100 of this preferred embodiment vary within a vertical scanning period. Specifically, in FIG. 9, Vs represents the voltage on the signal line 14; Vcsa represents the voltage on the storage capacitor line 24a; Vcsb represents the voltage on the storage capacitor line 24b; Vg represents the voltage on the scan line 12; Vlca represents the voltage to the first subpixel electrode 18a; and Vlcb represents the voltage to the second subpixel electrode 18b. In FIG. 9, the dashed line indicates the voltage COMMON (Vc) to the counter electrode 17. The voltage Vcsa on the storage capacitor line 24a varies periodically within the range of Vc - Vad to Vc + Vad. Likewise, the voltage Vcsb on the storage capacitor line 24b also varies periodically within the range of Vc-Vad to Vc+ Vad. The waveform of the voltage Vcsb on the storage capacitor line 24b has a phase that is different by 180 degrees from that of the voltage Vcsa on the storage capacitor line 24a.

[0078] Hereinafter, it will be described with reference to FIG. 9 how the equivalent circuit shown in FIG. 8 operates.

[0079] First, at a time T1, the voltage Vg on the scan line 12 rises from VgL to VgH to turn the TFTs 16a and 16b ON simultaneously. As a result, the voltage Vs on the signal line 14 is transmitted to the subpixel electrodes 18a and 18b of the subpixels 10a and 10b to charge the liquid crystal capacitors Clca and Clcb of the subpixels 10a and 10b. In the same way, the storage capacitors Csa and Csb of the respective subpixels are also charged with the voltage on the signal line 14

[0080] Next, at a time T2, the voltage Vg on the scan line 12 falls from VgH to VgL to turn the TFTs 16a and 16b OFF simultaneously and electrically isolate the liquid crystal capacitors Clca and Clcb of the subpixels 10a and 10b and the storage capacitors Ccsa and Ccsb from the signal line 14. It should be noted that immediately after that, due to the feedthrough phenomenon caused by a parasitic capacitance of the TFTs 16a and 16b, for example, the voltages Vlca and Vlcb applied to the first and second subpixel electrodes 18a and 18b decrease by approximately the same voltage Vd to:

55

50

20

30

35

40

Vlcb=Vs-Vd

5 respectively. Also, in this case, the voltages **Vcsa** and **Vcsb** on the storage capacitor lines are:

Vcsa=Vc-Vad

10

Vcsb=Vc+Vad

15

20

respectively.

[0081] Next, at a time T3, the voltage Vcsa on the storage capacitor line 24a connected to the storage capacitor Ccsa rises from Vc-Vad to Vc+Vad and the voltage Vcsb on the storage capacitor line 24b connected to the storage capacitor Ccsb falls from Vc+Vad to Vc-Vad. That is to say, these voltages Vcsa and Vcsb both change twice as much as Vad. As the voltages on the storage capacitor lines 24a and 24b change in this manner, the voltages Vica and Vicb applied to the first and second subpixel electrodes change into:

$Vlca=Vs-Vd+2\times K\times Vad$

25

$Vlcb=Vs-Vd-2\times K\times Vad$

30

35

respectively, where K=CCS/(CLC(V)+CCS).

[0082] Next, at a time T4, the voltage Vcsa on the storage capacitor line 24a falls from Vc+Vad to Vc-Vad and the voltage Vcsb on the storage capacitor line 24b rises from Vc-Vad to Vc+Vad. That is to say, these voltages Vcsa and Vcsb both change twice as much as Vad again. In this case, the voltages Vlca and Vlcb applied to the first and second subpixel electrodes also change from

40

45

$$Vlcb=Vs-Vd-2\times K\times Vad$$

into

Vlca=Vs-Vd

55

50

Vlcb=Vs-Vd

respectively.

[0083] Next, at a time T5, the voltage Vcsa on the storage capacitor line 24a rises from Vc-Vad to Vc+Vad and the voltage Vcsb on the storage capacitor line 24b falls from Vc +Vad to Vc-Vad. That is to say, these voltages Vcsa and Vcsb both change twice as much as Vad again. In this case, the voltages Vlca and Vlcb applied to the first and second subpixel electrodes also change from

Vlca=Vs-Vd

Vlcb=Vs-Vd

into

5

10

15

20

30

35

50

55

$Vlca = Vs - Vd + 2 \times K \times Vad$

Vlcb=Vs-Vd-2×K×Vad

respectively.

[0084] After that, every time a period of time that is an integral number of times as long as one horizontal scanning period 1H has passed, the voltages Vcsa, Vcsb, Vlca and Vlcb alternate their levels at the times T4 and T5. The alternation interval between T4 and T5 may be appropriately determined to be one, two, three or more times as long as 1H according to the driving method of the liquid crystal display device (such as the polarity inversion method) or the display state (such as the degree of flicker or non-smoothness of the image displayed). This alternation is continued until the pixel 10 is rewritten next time, i.e., until the current time becomes equivalent to T1. Consequently, the average voltages Vlca and Vlcb applied to the first and second subpixel electrodes become:

respectively.

[0085] Therefore, the effective voltages V1 (=VLspa) and V2 (=VLspb) applied to the liquid crystal layers 13a and 13b of the subpixels 10a and 10b become the difference between the voltage at the first subpixel electrode 18a and the voltage at the counter electrode 17 and the difference between the voltage at the second subpixel electrode 18b and the voltage at the counter electrode 17. That is to say,

That is to say,

$$V1 = Vs - Vd + K \times Vad - Vc$$

$V2 = Vs - Vd - K \times Vad - Vc$

5

10

20

30

35

40

45

50

55

FIG. 9 is not shown in FIG. 12.

respectively. As a result, the difference  $\Delta V$  (=V1-V2) between the effective voltages applied to the liquid crystal layers **13a** and **13b** of the subpixels **10a** and **10b** becomes  $\Delta V = 2 \times K \times Vad$  (where K=CCS/(CLC(V)+CCS)). Thus, mutually different voltages can be applied to the liquid crystal layers **13a** and **13b**.

**[0086]** FIG. **10** schematically shows the relation between V1 and V2 in the liquid crystal display device **100** of this preferred embodiment. As can be seen from FIG. **10**, the smaller the V1 value, the bigger  $\Delta V$  in the liquid crystal display device **100** of this preferred embodiment. The  $\Delta V$  value varies with V1 or V2 because the static capacitance CLC(V) of the liquid crystal capacitor varies with the voltage.

[0087] FIG. 11(a) shows the  $\gamma$  characteristic of the liquid crystal display device 100 of this preferred embodiment at a right 60 degree viewing angle, and FIG. 11(b) shows the  $\gamma$  characteristic of the liquid crystal display device 100 of this preferred embodiment at an upper right 60 degree viewing angle. FIGS. 11(a) and 11(b) also show the  $\gamma$  characteristics that were observed when the same voltage was applied to the subpixels 10a and 10b for the purpose of comparison. As can be seen from FIGS. 11(a) and 11(b), the grayscale characteristic of the liquid crystal display device 100 of this preferred embodiment is closer to the grayscale characteristic in the frontal viewing direction in which the ordinate is equal to the abscissa (and in which  $\gamma$ =2.2) than the situation where the same voltage was applied to the two subpixel electrodes. That is to say, the  $\gamma$  characteristic is improved by this preferred embodiment. As described above, by varying the respective voltages as shown in FIG. 9 within a single vertical scanning period, mutually different effective voltages are applicable to the respective liquid crystal layers of different subpixels, and the  $\gamma$  characteristic in an oblique viewing direction is improved as a result.

[0088] Hereinafter, it will be described with reference to FIG. 12 how the voltage applied to the single pixel 10 that has already been described with reference to FIGS. 7 and 8 changes through a number of vertical scanning periods.

[0089] In FIG. 12, Vg represents the voltage on the scan line 12, Vcsa and Vcsb represent the voltages on the first and second storage capacitor lines 24a and 24b, respectively, and VLspa and VLspb represent the effective voltages applied to the respective liquid crystal layers 13a and 13b of the first and second subpixel electrodes 10a and 10b. As described above, one vertical scanning period is an interval between a point in time when a scan line is selected and a point in time when the next scan line is selected, and is represented by V-Total in FIG. 12. It should be noted that the variation in the voltage Vd caused by the feedthrough phenomenon that has already been described with reference to

[0090] Also, the voltages Vcsa and Vcsb on the first and second storage capacitor lines each have display periods AH and regulation periods BH. Each of these voltages Vcsa and Vcsb on the first and second storage capacitor lines varies periodically in different cycles through the display and regulation periods AH and BH. In this example, the voltages Vcsa and Vcsb vary in regular cycles of 20H through the display periods AH and in different regular cycles of either 36H or 26H through the regulation periods BH. The sum of one display period AH and one regulation period BH is equal to one vertical scanning period (V-Total). Furthermore, in this example, the display period AH begins when the voltages Vcsa and Vcsb on the first and second storage capacitor lines change after a vertical scanning period for a certain frame has started. On the other hand, the regulation period BH ends when the voltages Vcsa and Vcsb on the first and second storage capacitor lines change after the vertical scanning period for that frame has terminated. In this preferred embodiment, the frame frequency may be 60 Hz, for example.

[0091] FIG. 12 shows how the voltages change through four vertical scanning periods. In the following description, those four vertical scanning periods will be referred to herein as first, second, third and fourth vertical scanning periods, respectively, and the display periods AH and regulation periods BH associated with those vertical scanning periods will be referred to herein as first, second, third and fourth display periods AH and first, second, third and fourth regulation periods BH, respectively. Also, in this example, when the voltage Vcsa on the storage capacitor line 24a rises to a higher voltage VcH, the voltage VcSb on the storage capacitor line 24b falls to a lower voltage VcL. Conversely, when Vcsa falls to a lower voltage VcL, Vcsb rises to a higher voltage VcH. The difference between VcH and VcL is equal to  $2 \times Vad$  that has already been described with reference to FIG. 9.

[0092] At a time when the voltage Vcsa on the first storage capacitor line 24a is VcL and when the voltage Vcsb on the second storage capacitor line 24b is VcH, the voltage Vg on the scan line 12 changes from VgL into VgH. In response to the change of the voltage Vg into VgH, the first vertical scanning period begins and the first and second subpixel electrodes 18a and 18b are charged. While the voltage Vg on the scan line 12 is VgH, the voltage Vs on the signal line 14 is higher than the voltage Vc at the counter electrode 17. That is why as a result of the charge, the voltages at the

first and second subpixel electrodes **18a** and **18b** become higher than the voltage **Vc** at the counter electrode **17**. Thereafter, when the voltage **Vg** on the scan line **12** falls from VgH to VgL again, the first and second subpixel electrodes **18a** and **18b** finish being charged.

[0093] After that, the voltage Vcsa on the first storage capacitor line 24a rises to VcH and the voltage Vcsb on the second storage capacitor line 24b falls to VcL. In this example, it is when the voltage Vcsa on the first storage capacitor line 24b decreases and the voltage Vcsb on the second storage capacitor line 24b decreases that the first display period AH begins. Through the first display period AH, the voltages Vcsa and Vcsb on the first and second storage capacitor lines 24a and 24b increase or decrease every 10H period and vary periodically in regular cycles of 20H. When the first display period AH ends, the first regulation period BH begins. Through the first regulation period BH, the voltages Vcsa and Vcsb on the first and second storage capacitor lines 24a and 24b increase or decrease every 18H period. The voltages at the first and second subpixel electrodes 18a and 18b change as the voltages Vcsa and Vcsb on the first and second storage capacitor lines 24a and 24b vary. That is why in the first vertical scanning period, the absolute value of the effective voltage applied to the liquid crystal layer 13a of the first subpixel 10a becomes greater than that of the effective voltage applied to the liquid crystal layer 13b of the second subpixel 10b and the first subpixel 10a becomes brighter than the second subpixel 10b.