# (11) **EP 2 151 758 A2**

(12)

# **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

10.02.2010 Bulletin 2010/06

(51) Int Cl.:

G06F 9/46 (2006.01)

G06F 15/80 (2006.01)

(21) Application number: 09175954.8

(22) Date of filing: 18.12.1996

(84) Designated Contracting States:

DE FR GB IT NL SE

(30) Priority: 20.12.1995 GB 9526009

(62) Document number(s) of the earlier application(s) in accordance with Art. 76 EPC: 96943202.0 / 0 880 740

(71) Applicant: MBDA UK Limited Stevenage

Hertfordshire SG1 2DA (GB)

(72) Inventors:

Simpson, H.R. Stevenage, Hertfordshire SG1 2DA (GB) Campbell, E.R..

Stevenage, Hertfordshire SG1 2DA (GB)

(74) Representative: BAE SYSTEMS plc

**Group IP Department**

P.O. Box 87

**Warwick House**

**Farnborough Aerospace Centre**

**Farnborough**

Hampshire GU14 6YU (GB)

# Remarks:

This application was filed on 13-11-2009 as a divisional application to the application mentioned under INID code 62.

# (54) Integrated circuits for multi-tasking support in single or multiple processor networks

(57) An integrated circuit (7A) for multitasking support for processing unit (1A) holds control variables for each task (or activity) to run on its associated processor (1A) and identifies the next task that should run. The cir-

cuit (7A) employs level-driven, clock free ripple logic and is configured as a two-dimensional array of "tiles", each tile being composed of simple logic gates and performing a dedicated function. The circuit has particular application to asynchronous multiple processor networks.

EP 2 151 758 A2

# Description

**[0001]** This invention relates to integrated circuits and particularly, though not exclusively to integrated circuits for use in single or multi-processor systems.

**[0002]** One object of the invention is to provide an integrated circuit, (to be referred to herein as a "Butler Chip") which is capable of directly supporting the shared data and multi-tasking concepts of real-time networks in the context of single or multi-processor systems.

**[0003]** A further object is to provide a more deterministic (in the temporal sense) execution environment so as to eliminate some aspects of pessimistic timing analysis at the fundamental level of computer operation.

**[0004]** For a better understanding of an application of the "Butler Chip" to be described herebelow, reference is made to our co-pending Patent Application WO91/16681. Therein, two Central Processing Units (CPU) are able to interact through an Asynchronous Dual Port Memory (ADPM). The ADPM can carry many communications routes (spatially multiplexed) such that there is no temporal interference between these routes, and where the temporal interaction between operations at the two sides of the same route is confined entirely to that interaction which is implicit in the protocol which characterises the dynamics of the route.

**[0005]** The latter property is dependent upon the fact that the ADPM has two completely independent access paths to every memory element and itself applies no exclusion.

**[0006]** Support for the protocols of the multi-processor communications systems of W091/16681 is provided by a Communications Executive Chip (CEC) which contains logic for many parallel routes of various types. Support for scheduling is provided by a Kernel Executive Chip (KEC) which contains the logic for controlling 64 activities organised in 8 priority levels with 8 activities in each level. Selection at each level is controlled by a round robin polling logic. The highest priority level can be stimulated from external devices, including the set of CECs associated with a CPU.

**[0007]** Both the CEC and the KEC are accessed as memory attached to a private bus of each CPU, with individual chip functions being associated with particular access addresses. This allows the KEC's and CEC's to be used with any type of processor.

**[0008]** A particular feature of the approach to the implementation of routes between activities in adjacent processors, concerns the way in which implicit stimuli are handled. A CEC can multiplex a number (eg 32) of stims (termed secondary stims) and can indicate to the KEC (by means of a "primary stim" that a secondary stim is present. It is therefore necessary to use software to unpack and distribute the secondary stims. In W091/16681, this has to be effected by infrastructure software containing stim servers. Disadvantageously, this arrangement introduces temporal indeterminacy because the stim servers run and impede the progress of application level activities.

**[0009]** The "Butler chips" proposed in the present invention can fulfil the role of the KEC and also absorb CEC functions where feasible. One advantage of using the "Butler chip" in the above context is the removal of the aforementioned temporal indeterminacy by eliminating the need for stim servers. It also facilitates a more flexible priority and poll set scheme.

**[0010]** In one aspect of the invention, an integrated circuit for use as a schedule of activities to be run on an associated CPU, is configured to support a "control node" mechanism by incorporating:

a "stim-wait" channel for holding statuses for at least one pair of control variables corresponding to each of said activities, to control the scheduling of said activities, each of the activities being associated with at least one stimwait channel, a control variable of each of the stim-wait channels being settable to waiting status in relation to its associated activity, and

a plurality of inputs each operable to set a control variable of a respective stim-wait channel to stimmed status,

wherein each stim-wait channel associated with an activity has a ready output when the statuses of a pair of control variables of the channel are both stimmed and waiting, the ready output identifying the associated activity as ready for running on the processor.

**[0011]** The "Butler chip" may be used in association with kernel primitive and builder operations. The "kernel" is software running on the associated CPU which switches in and out the tasks/activities to be performed by the CPU. The "Butler chip" supports the kernel.

**[0012]** The "stim-wait" channels allow an activity to selectively wait and be selectively stimmed. Each of these stimwait channels supports to a control node in software. A control node is introduced to provide a control point at which an activity may wait to be "stimmed" into operation by another activity.

[0013] The provision of multiple stim-wait channels allows each activity to put itself into a condition where it selectively waits for stimuli from a plurality of sources eg. from its associated CPU, a peripheral device or from another "Butler chip".

[0014] In addition to the stim-wait channels, each activity may have associated with it, other control variables to be described in detail here below.

40

35

30

20

45

50

[0015] In another aspect, an integrated circuit for use as a scheduler of activities to be run on an associated CPU is of modular structure being constructed from an assembly of "tiles",

wherein each tile defines a building block having logic and structure, said tiles being abutted one against the other to form a two-dimensional array of n rows and m columns which realises an overall functionality for the integrated circuit and wherein each of the n rows of tiles provides the control logic for each one of n schedulable activities and each of the m columns of tiles provides a particular function.

**[0016]** The control logic includes means for holding control variables corresponding to each activity. Some of these control variables may comprise at least one stim-wait channel.

[0017] A top row of tiles may be added to provide the interfacing circuitry to external devices, such as a CPU.

**[0018]** The word "tile" in this context means a design building block which when butted to other tiles to form a two dimensional array, encapsulates the electronic circuitry and structural information needed for realising overall functionality and direct physical silicon layout.

**[0019]** Thus the "Butler chip" of the present invention is provided with a physical construction that combines simple logic elements with defined interfaces into a regular structure in order to achieve the required functionality.

**[0020]** As all the necessary signal connections are automatically made when the tiles are abutted, there is no requirement for any additional inter-tile routing.

**[0021]** In contrast to conventional clock-driven logic, the "Butler chip" of the present invention uses level-driven, clock-free ripple logic. Asynchronous operation is used with the "Butler chip" responding to events: eg instructions from an associated local processor or asynchronous stimuli from external sources.

**[0022]** Such "external sources" could comprise local peripherals or even other processor's associated "Butler chips". By virtue of the structural design of the "Butler chip"; following an event, the internal logic freely ripples to establish its final stable condition. Where memory elements are required, non-clocked latches are used.

20

30

35

40

45

50

55

**[0023]** The invention offers many advantages. The design can be easily implemented in different technologies because it is not dependent on critical timing parameters. There are no clock signals to distribute and consequently no clock-skew or set-up and hold violation problems. All of the circuitry is related to the application, using minimum circuitry per function. Furthermore, the asynchronous circuitry has non-demanding power-supply requirements particularly if CMOS technology is employed. The chip design can be analysed for correctness by formal mathematical methods and manufactured devices may be tested, in isolation, to achieve full fault coverage.

**[0024]** The "Butler chip" is particularly suited to hard, real-time embedded systems and to systems that need to demonstrate quantifiable levels of dependability.

[0025] It can be used with any type of processor. For example, it can provide support for multi-tasking in a single or multiple processor system. Specifically, it is used to hold control variables for each task or activity assigned to run on an associated processor and to identify the next task that should run. These control variables can be set at any time from different sources. The logic for selecting the next task can be programmed (ie via software). Tasks that are given the same priority level can be selected by the "Butler chip" on a round robin basis within their group. Asynchronous stimuli (eg interrupts from local peripherals) can be handled directly by the "Butler chip" which schedules the relevant task when its turn arrives, according to the programmed priority level selection. Co-operative and pre-emptive scheduling schemes can be supported.

**[0026]** In the example of a multiprocessor system, each processor has its own associated "Butler chip" and connections are made between 11Butler chips", A request for scheduling any task is always registered with a processor's own "Butler chip". Where the task resides on a different processor, "Butler chips" communicate directly and schedule the relevant task on the destination processor when its turn arrives. This avoids the need to unnecessarily interrupt any task running on the destination processor, thereby providing an efficient, temporally deterministic operation.

**[0027]** Some embodiments of the invention will now be described, by way of example only, with reference to the drawings of which:

Figure 1 is a schematic circuit diagram illustrating the use of the "Butler chip" in accordance with the invention in a multiprocessor network;

Figure 2 is a diagram showing the layout of the different types of tile which comprise a "Butler chip" array which is suitable for use with the network of Figure 1;

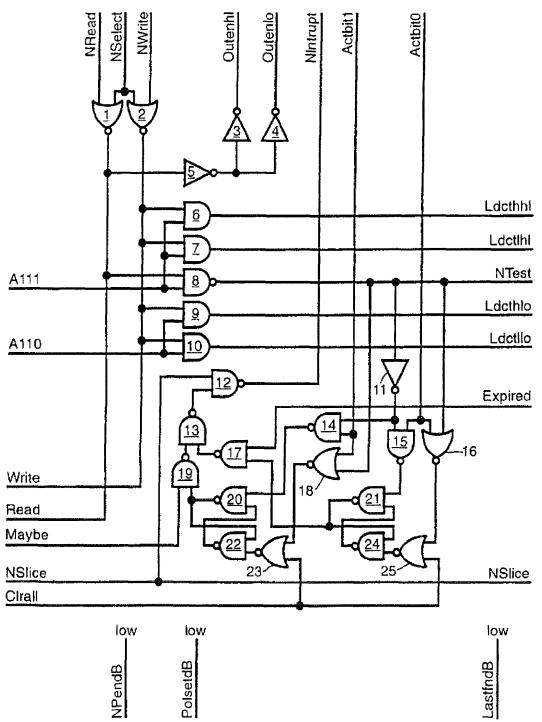

Figures 3 - 10 are logic circuit diagrams of the tiles comprising a "main array" of a "Butler chip";

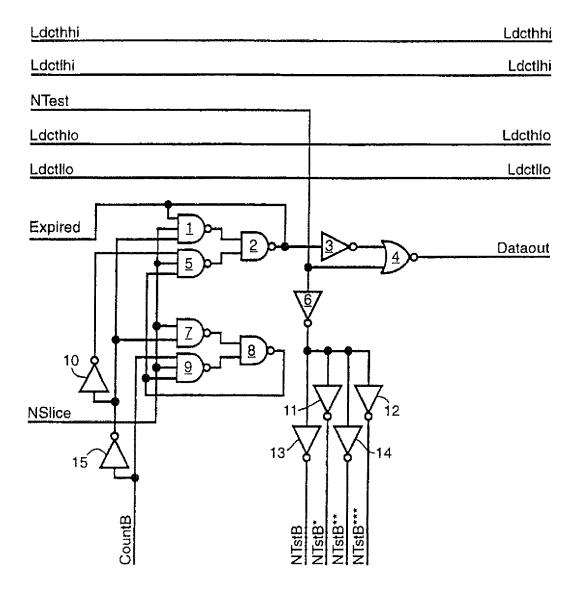

Figures 11-18 are logic circuit diagrams of the tiles comprising a "top row" of a "Butler chip", and

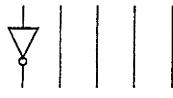

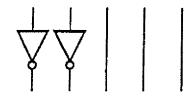

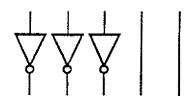

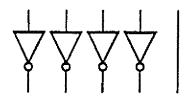

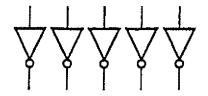

Figure 19 is a series of wiring diagrams illustrating the customising of the tiles of figures 5 and 6.

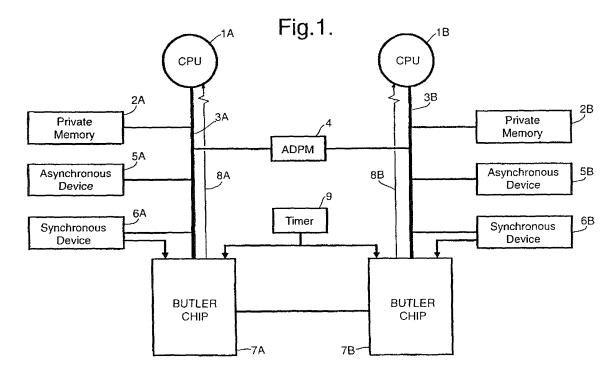

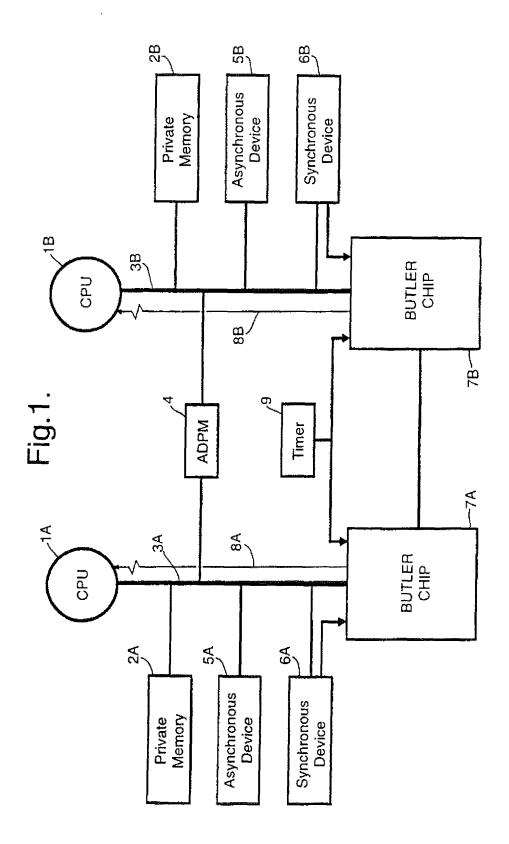

[0028] In Figure 1 a dual processor system comprises two central processing units (CPU) 1A, 1B, each CPU being linked to a private memory 2A, 2B via a data bus 3A, 3B. The CPU's 1A, 1B are linked to each other by means of an asynchronous dual port memory (ADAM) 4. Each CPU 1A, 1B also has access to asynchronous devices (peripherals) 5A, 5B, synchronous devices (ie peripherals which can generate an external stimulus) 6A, 6B and an associated "Butler

chip" 7A, 7B respectively. The "Butler chips" 7A, 7B are connected with one another.

**[0029]** An interrupt line 8A, 8B, runs from each "Butler chip" 7A, 7B to its associated CPU 1A, 1B, This can be used to trigger task switching when using pre-emptive scheduling or to indicate a watch-dog timer overrun when using cooperative scheduling.

[0030] Each "Butler chip" may be provided with a standard memory interface for connection to its associated processor. Conveniently, this could comprise a 16-bit bi-directional data bus, three address lines and three memory control line inputs.

[0031] A preferred example is provided with active-low asynchronous local inputs for use by peripherals. Each may register a request for service at any time. Additionally, there are four groups of asynchronous external inputs. In a multiple processor system these would be connected to other processor's associated "Butler chips". Each group has six lines that are used to identify a specific task number, and an associated active-low stimulus input that registers a request for service. Ten outputs are provided for connection to the external inputs of up to four other "Butler chips". Six are used to identify a specific task number and are connected to all adjacent "Butler chips". The other four outputs are the active-low stimulus outputs, each connected to a different processors "Butler chip".

[0032] One further input line is provided; to the "Butler chip's" internal counter, either from the CPU's clock or from an external timer 9.

[0033] The structure of a "Butler chip" (7A or 7B of Figure 1) will now be described with reference to Figure 2.

**[0034]** As mentioned above, a "Butler chip" comprises a two-dimensional array of tiles. Each tile consists of a plurality of interconnected logic gates and input/output connections for interfacing with adjacent tiles. Each tile type fulfils a particular function.

[0035] In the specific example to follow, a "Butler chip" array 10 is comprised of a main array 11 of 1312 tiles and a top row 12 of a further 21 tiles.

[0036] There are eight different tile types, represented in Figure 2 by the letters S, U, P, E, R, M, A, N. Each tile comprises a few simple logic gates.

[0037] The main array 11 has sixty-four rows that each hold the control variables for an activity.

**[0038]** Row O is associated with activity zero, with activity numbers incrementing for the remaining rows 1 to 63 down the array.

[0039] Each row of the main array 11 contains twenty and a half tiles (Tile N is a double height tile that spans two rows). From left to right these are: -

| 30 | one   | tile  | of | type | Tile_S |

|----|-------|-------|----|------|--------|

|    | two   | tiles | of | type | Tile_U |

|    | one   | tile  | of | type | Tile_P |

|    | two   | tiles | of | type | Tile_U |

| 25 | one   | tile  | of | type | Tile_P |

| 35 | three | tiles | of | type | Tile_U |

|    | one   | tile  | of | type | Tile_P |

|    | two   | tiles | of | type | Tile_U |

|    | one   | tile  | of | type | Tile_P |

| 40 | two   | tiles | of | type | Tile_U |

|    | one   | tile  | of | type | Tile_E |

|    | one   | tile  | of | type | Tile_R |

|    | one   | tile  | of | type | Tile_M |

| 45 | one   | tile  | of | type | Tile_A |

| 45 | half  | tile  | of | type | Tile_N |

20

55

**[0040]** The circuitry of the top row 12 is designed to generate main array control signals and to interface with a CPU, and other "Butler Chips"

[0041] There are eight different tile types, each comprising a few simple gates. The row contains 21 tiles, one at the top of each column. From left to right these are:

```

one

tile

of

type Tile_Stop

tiles

of

type Tile_Utop

two

tile

of

type Tile_Ptop

one

two

tiles

of

type Tile_Utop

one

tile

of

type Tile_Ptop

```

(continued)

of

of

of

of

three

one

two

one

5

tiles

tile

tiles

tile

type Tile\_Utop

type Tile\_Ptop

type Tile\_Utop

type Tile\_Ptop

|    |                       | turo til                                                                                                                                                                                                                                                                                                                                                        | loo of           | tuno Tilo I Itan                                                             |  |  |  |  |

|----|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------|--|--|--|--|

|    |                       |                                                                                                                                                                                                                                                                                                                                                                 | les of           | type Tile_Utop                                                               |  |  |  |  |

|    |                       |                                                                                                                                                                                                                                                                                                                                                                 | le of            | type Tile_Etop                                                               |  |  |  |  |

| 10 |                       |                                                                                                                                                                                                                                                                                                                                                                 |                  | type Tile_Rtop                                                               |  |  |  |  |

| 10 |                       | one til                                                                                                                                                                                                                                                                                                                                                         | le of            | type Tile_Mtop                                                               |  |  |  |  |

|    |                       | one til                                                                                                                                                                                                                                                                                                                                                         | le of            | type Tile_Atop                                                               |  |  |  |  |

|    |                       | one til                                                                                                                                                                                                                                                                                                                                                         | le of            | type Tile_Ntop                                                               |  |  |  |  |

| 15 | [0042] In the followi | ng description of the preferr                                                                                                                                                                                                                                                                                                                                   | red embodime     | nents, meanings of certain terms used are listed below:                      |  |  |  |  |

|    | active-high           | A boolean variable whose a low.                                                                                                                                                                                                                                                                                                                                 | true value is    | represented by a high and false value is represented by                      |  |  |  |  |

| 20 | active-low            | A boolean variable whose true value is represented by a low and false value is represented by a high.                                                                                                                                                                                                                                                           |                  |                                                                              |  |  |  |  |

|    | activity              | The number assigned to a                                                                                                                                                                                                                                                                                                                                        | software tasl    | sk that can be scheduled.                                                    |  |  |  |  |

| 25 | array                 | The arrangement of tiles th                                                                                                                                                                                                                                                                                                                                     | nat form the n   | main BUTLER structure.                                                       |  |  |  |  |

|    | array-operation the   | An event initiated pulse that srlatch.                                                                                                                                                                                                                                                                                                                          | t freely ripples | es along a logic chain in array to set or reset a pre-selected               |  |  |  |  |

| 30 | cirali                | The array-operation where all (except 'Last') srlatches in the array are reset. Initiated by a Clear_All BUTLER instruction                                                                                                                                                                                                                                     |                  |                                                                              |  |  |  |  |

|    | cirpollend            | The array-operation where the 'Pollend' srlatch is reset for an activity. Initiated by a Clear_Pollend BUTLER instruction to remove a pollset boundary.                                                                                                                                                                                                         |                  |                                                                              |  |  |  |  |

| 35 | clrstarted            | The array-operation where the 'Started' srlatch is reset for an activity. Initiated by a Clear_Started BUTLER instruction for an activity that is to be excluded from being scheduled.                                                                                                                                                                          |                  |                                                                              |  |  |  |  |

| 40 | established           | The final stable condition o                                                                                                                                                                                                                                                                                                                                    | of a signal wh   | nen any ripple logic transient effects have subsided.                        |  |  |  |  |

| 40 | high                  | A positive voltage level.                                                                                                                                                                                                                                                                                                                                       |                  |                                                                              |  |  |  |  |

| 45 | latch                 | An arrangement of gates used to form a memory element. Latches are given single-word names with an upper-case first letter, lower-case subsequent letters and are enclosed in single quotes (e.g. 'Latch'). Where reference is made to the boolean variable implemented by a single-bit latch, the latch name enclosed in double quotes is used (e.g. "Latch"). |                  |                                                                              |  |  |  |  |

|    | low                   | A zero voltage level.                                                                                                                                                                                                                                                                                                                                           |                  |                                                                              |  |  |  |  |

| 50 | nextact               | The array-operation when the processor. Initiated by                                                                                                                                                                                                                                                                                                            | -                | chosen to be the next for scheduling is being returned to UTLER instruction. |  |  |  |  |

|    | pollset               | A contiguous group of activ                                                                                                                                                                                                                                                                                                                                     | vities designa   | ated to have equal priorities.                                               |  |  |  |  |

| 55 | reset                 | As a noun, the false state of                                                                                                                                                                                                                                                                                                                                   | of a srlatch. A  | As a verb, applying the make-false input to a srlatch.                       |  |  |  |  |

|    | set                   | As a noun, the true state of                                                                                                                                                                                                                                                                                                                                    | f a srlatch. As  | as a verb, applying the make-true input to a srlatch.                        |  |  |  |  |

The array-operation where the 'Pollend' srlatch is set for an activity. Initiated by a Set Pollend setpollend BUTLER instruction to insert a pollset boundary. setstarted The array-operation where the 'Started' srlatch is set for an activity. 5 Initiated by a Set-Started BUTLER instruction for an activity that is allowed to be included as a candidate for being scheduled. setstimmed The array-operation where the 'Stimmed' latch(es) are set for an activity'. Initiated by a Do\_Stim BUTLER instruction. 10 The array-operation where the 'Suspended' latch is set for an activity. Initiated by a Set-Suspended setsuspended BUTLER instruction. The array-operation when the 'Waiting' srlatch(es) are set for the activity most recently returned setwaiting 15 to the processor for scheduling. Initiated by a Do-Wait BUTLER instruction (when the activity currently running on the processor co-operatively offers a reschedule point having finished its current work). signal A physical line able to assume a high or low value. Active-high signals are given single-word 20 names with an upper-case first letter and lower-case or numerical subsequent characters (e.g. Signal3). Active-low signal names are prefixed with an upper-case N (e.g. NSigna17). Where it is necessary to individually identify the two ends of a signal that forms a connection between tile rows, each end is postfixed with an A or B (e.g. Signal4B would be directly 25 connected to Signal4A in the tile below). Where it is necessary to individually identify the two ends of a signal that forms a connection between tile columns, each end is postfixed with an L or R (e.g. Signal2L would be directly connected to Signal2R in the tile to the Left; Signal2R would be directly connected to Signal2L in the tile to the right). 30 A boolean latch with independent make-true and make-false inputs that may be applied at any time. srlatch suspend The array-operation when the 'Suspended' srlatch is set for the activity most recently returned to the processor for scheduling. Initiated by a Suspend BUTLER instruction (when the activity currently running on the processor cooperatively offers a reschedule point but wishes to continue). 35 The active condition of a signal during an array-operation. (e.g. taken Signal3 is taken high during suspend). tlatch A latch with a control signal that selects one of two modes of operation. Either the latch is trans-40 parent and its output tracks its input, or it is latched when its output retains the value it held when last transparent. transmitted The value existing at one place is established at another. 45 The high or low condition of a signal. Operations of each "Butler chip" are carried out in response

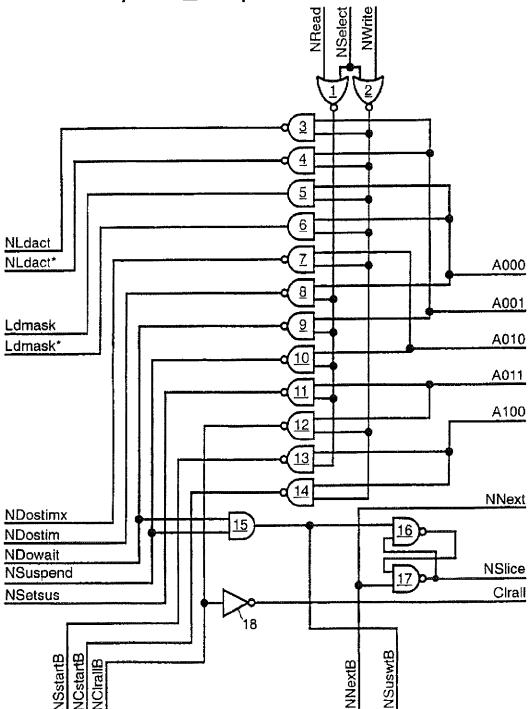

| ADDRESS |    |    | "WRITE" INSTRUCTION   | "READ" INSTRUCTION |

|---------|----|----|-----------------------|--------------------|

| A2      | A1 | A0 |                       |                    |

| 0       | 0  | 0  | Load_Mask [D15-D0]    | Do_Stim            |

| 0       | 0  | 1  | Load_Activity [D5-D0] | Do_Wait            |

| 0       | 1  | 0  | Do_Stimx              | Suspend            |

| 0       | 1  | 1  | Clear_All             | Set_Suspended      |

to memory writes or reads from its associated CPU, as shown in the table below.

value

50

55

(continued)

| ADDF | RESS |    | "WRITE" INSTRUCTION      | "READ" INSTRUCTION |

|------|------|----|--------------------------|--------------------|

| A2   | A1   | A0 |                          |                    |

| 1    | 0    | 0  | Clear_Started            | Set_Started        |

| 1    | 0    | 1  | Clear_Pollend            | Set_Pollend        |

| 1    | 1    | 0  | Load_Counter-Lo [D15-D0] | Nextact [D15-D0]   |

| 1    | 1    | 1  | Load_Counter_Hi [D15-D0] | Control_Interrupts |

**[0043]** Writes to, and reads from a "Butler chip" are used to load operational data, return data to each CPU and to initiate internal "Butler chip" operations. To minimise the temporal constraints on the CPU interface, write accesses that are used to load operational data to a "Butler chip" do not initiate operations within the chip.

[0044] Writes to a "Butler chip" may be carried out by the associated CPU at any time.

5

10

20

35

40

45

50

55

**[0045]** Instructions Load\_Mask, Load\_Counter\_Lo and Load\_Counter\_Hi use the values on all sixteen data lines (D15-DO). These enter the "Butler chip" via tiles N,S\_top, U\_top and P\_top (labelled Datain and Din in the accompanying figures). The mask is an array of sixteen bits used to select one or more stim\_wait channels as an argument for "Butler chip" operations.

**[0046]** Each activity/task to be scheduled has sixteen pairs of "stimmed" and "waiting" (control) variables, each pair being referred to as a "stim-wait" channel. Some instructions can operate on individual or groups of stim-wait channels. The "stim-wait" channels to be operated on are specified by including a logic "one" in an appropriate bit position in the data word of the "Load Mask" instruction.

**[0047]** The instruction Load\_Activity uses only the values on the six data lines (D5-DO) which enter the "Butler chip" via tile E\_top. No data line values are used by the other "write" instructions.

[0048] Reads from a "Butler chip" may be carried out by the CPU at any time. In general, read instructions will not return valid data to the CPU. Read instructions will return valid data on all sixteen data lines (DO-D15) in defined circumstances to be described below. During normal operation only data returned by a "Nextact" instruction is used (Nextact returns the number of the next activity to be scheduled to the CPU). "Nextact" will return valid data when the time from a preceding "Suspend" or "Do Wait" instruction is sufficient to have allowed the next activity selection logic to have stabilised.

**[0049]** Each "Butler chip" performs specified functions when accessed as memory. It is not intended for use where unintentional memory accesses may occur, such as in direct-memory-access, cache or refresh memory systems.

**[0050]** Each "Butler chip" holds the control variables for each activity assigned to run on its associated CPU. In the specific example, sixteen "stim-wait" channels are for internal use (ie interactions between a "Butler chip" 7A and its associated CPU 1A) these are held on the SU and P tiles. Four of the sixteen "stim-wait" channels are additionally for interactions from a neighbouring "Butler chip" 7B. These are held on the 'P' tiles. One of the sixteen "stim-wait" channels is additionally for interactions with the peripheral 6A. This is held on the S tile. The number of U and P tiles may be varied to suit the application or dispensed with altogether. Depending upon the values of these control variables and others as described herebelow, the Butler chip" continuously computes the next activity to be scheduled, taking into account any currently programmed priority levels.

**[0051]** The "Butler chip" is designed to operate correctly in an asynchronous environment. The next activity selection logic operates continuously and can respond to multiple inputs that may arrive at any time from temporarily incoherent sources. The outputs from the next activity selection logic are put onto the least significant seven bits (D6-D0) of the data bus during all read instructions. Because a result may be in the process of being updated during a read operation, read instructions will not always return valid data.

[0052] During normal operation only the Nextact read instruction is required to return valid data. (The number of the next activity to be scheduled.) This is achieved by temporarily inhibiting any changes to the asynchronously stimulated variables from entering the next activity selection logic, and allowing time for the next activity selection logic to stabilise before executing a Nextact instruction. A preceding Suspend or Do\_Wait instruction is used to inhibit visibility of any changes to the asynchronously stimulated variables from entering the next-activity-selection logic.

**[0053]** The maximum time for the next activity selection logic to stabilise in response to a change is determined by the ripple logic search chain. This worse case time also applies to all instructions that may alter the next activity selected, including "Stimmed", "Waiting", "Suspended", "Started" and "Pollend" variables (to be described below). The value of this time is implementation specific and is calculated by a summation of the worst case gate delays in the complete search logic chain.

[0054] A "Clear-All" instruction from the CPU disables interrupts, removes any pollset boundaries and initialises (i.e.

makes false) the "started", the "suspended" and the sixteen "stimmed" and "waiting" control variables for all activities.

**[0055]** Some instructions operate on a specified activity number. This activity number is specified in the data word of a Load\_Activity instruction and is held on the "Butler chip".

**[0056]** Activities (or tasks) are numbered from zero to sixty-four. When priority levels apply, smaller activity numbers have the higher priorities. Activity number sixty-four always has the lowest priority and can be used to schedule an idle activity at a time when no other activities are candidates for scheduling.

**[0057]** Following a "Clear All" instruction activities numbered zero to sixty-three are assigned equal priorities. Priority levels can be allocated to individual activities or to groups of activities, by inserting "pollset" boundaries.

[0058] A "Set Pollend" instruction will insert a pollset boundary. The activity specified in the most recent "Load Activity" instruction will then become the largest number in this pollset. (The following activity number will automatically become the smallest activity number in the next priority pollset). A "Clear Pollend" instruction will remove the pollset boundary (if it exists) at the activity number specified in the most recent "Load Activity" instruction. Pollset boundaries may be inserted or removed at any time.

**[0059]** Where more than one activity is a candidate for scheduling at any one time, the next activity selection logic will select an activity from the highest priority pollset that contains a candidate. If this pollset contains more than one candidate, selection is made on a round robin basis within the pollset, the search starting from the activity following the activity that was last returned for scheduling in that pollset.

[0060] An activity will only be included as a candidate for scheduling when it is started and ready:

20

25

30

35

40

45

50

55

A "Set Started" instruction will make the "started" control variable true for the activity specified in the most recent "Load Activity" instruction. A "Clear Started" instruction will make the "started" control variable false for the activity specified in the most recent "Load Activity" instruction. The nstarted" variable thus indicates whether or not an activity can be considered for scheduling.

An activity is ready when either its "suspended" variable is true, or it has a matched pair of true "stimmed" and "waiting" control variables.

[0061] A "Set Suspended" instruction will make the "suspended" variable true for the activity specified in the most recent "Load Activity" instruction. A "Suspend" instruction will make the "suspended" variable true for the activity currently running on the CPU (ie the last activity returned to the CPU for scheduling). The "suspended" variable will be made false when the activity is returned to the CPU as the next activity to be scheduled. A Suspend instruction allows an activity to suspend its operation and ensures that a request for continued operation is registered by means of the "suspended" variable. This instruction operates on the current activity whose activity number is remembered on the "Butler chip" as well as being passed back to the CPU.

[0062] A "Do Wait" instruction will make the "waiting" variable true for the stim-wait channel(s) specified in the most recent "Load Mask" instruction for the activity currently running on the CPU. The "waiting" variable will be made false when this activity is returned to the CPU as the next activity to be scheduled.

**[0063]** Both the Suspend and Do Wait instructions are always associated with the end of a processing slice and therefore always shortly precede the Nextact instruction which will notify the CPU of the next activity to be scheduled. For this reason and as described in greater detail below, the outputs associated with asynchronous stimuli are latched in order to temporarily prevent their onward propagation.

**[0064]** A "Do Stim" instruction will make the "stimmed" variable true for the stim-wait channel(s) specified in the most recent "Load Mask" instruction for the activity specified in the most recent "Load Activity" instruction. The "stimmed" variable will be made false when the activity is returned to the CPU as the next activity to be scheduled.

[0065] When an activity is selected for scheduling, the suspended and all its, stimmed and waiting variables are cleared to false.

**[0066]** When "Butler chips" are interconnected, each chip is able to make "stimmed" variables true in other chips. Certain stim-wait channels for one "Butler chip" can be associated with a stim-wait channel in another chip by physical connection. A "Do Stimx" instruction will make the associated "stimmed" variable in a connected chip true for the activity specified in the most recent "Load Activity" instruction.

[0067] Following a "Clear All" instruction the interrupt output line will be held in its non-active state (ie High) with interrupts disabled.

**[0068]** A "Control interrupts" instruction uses the least significant two bits of the activity number specified in the most recent "Load Activity" instruction (Actbitl and ActbitO) to define its operation.

[0069] A "Control interrupts" instruction when Actbitl is high will allow interrupts to be generated when the "Butler chip" detects that there is a candidate for scheduling with a higher priority than the activity currently running on the CPU. When this is the case, the interrupt output line will be held low. A "Do Wait" or a "Suspend" instruction will restore the interrupt line to its non-active state. A "Nextact" instruction will allow further interrupts to be generated. A "Control Interrupts" instruction when Actbitl is low will prevent generation of these interrupts.

**[0070]** Each "Butler chip" has a 32-bit down-counter that counts low to high transitions on the counter input line. A "Do Wait" or a "Suspend" instruction initialises the counter to the 32-bit number that is held on the "Butler chip". A "Nextact" instruction enables the counter to start counting.

**[0071]** The 32-bit number that is used to initialise the counter is programmable. A "Load\_Counter\_Lo" instruction loads the data word into the least significant 16-bits of the number. A "Load\_Counter Hi" instruction loads the data word into the most significant 16-bits of the number.

[0072] A "Control Interrupts" instruction when ActbitO is high will cause an interrupt to be generated when the "Butler chip" counter has received a programmed number (plus one) of signal transitions on its counter input line. When this is the case, the interrupt output line will be held low. A "Do Wait" or a "Suspend" instruction will restore the interrupt line to its non-active state. A "Nextact" instruction will allow further interrupts to be generated. A "Control Interrupts" instruction when ActbitO is low will prevent generation of these interrupts.

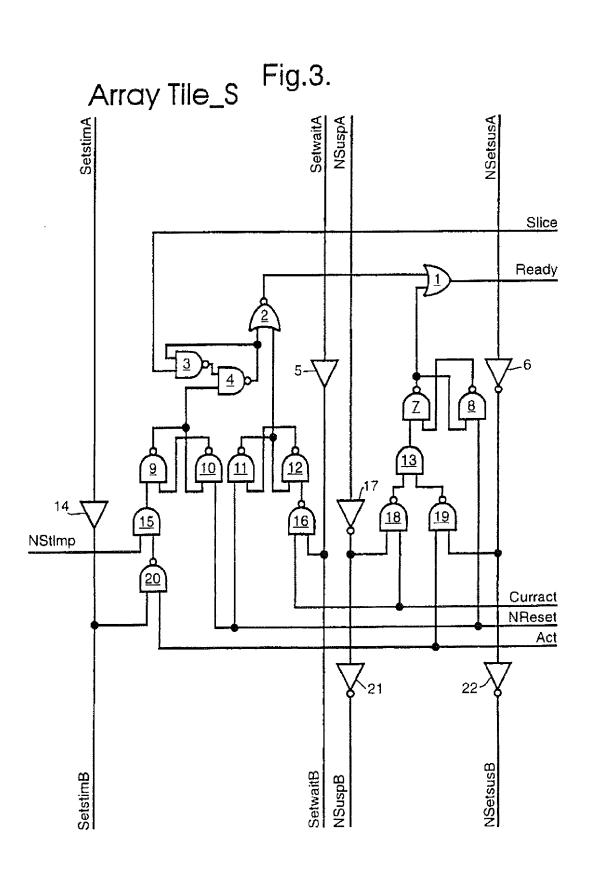

[0073] The tiles of the main array 11 will now be described with reference to Figures 3 - 10.

**[0074]** The structure of tile type 'S' is shown in Figure 3. The function of this tile is to hold an activity's "Suspended" and local "Stimmed" and "Waiting" Boolean variables and to indicate whenever either "Suspended" is true or both "Stimmed" and "Waiting" are true.

|   | Outputs: | Ready to | Tile_U |                  |

|---|----------|----------|--------|------------------|

|   |          | SetwaitB | to     | Tile S below     |

|   |          | SetstimB | to     | Tile_S below     |

|   |          | NSuspB   | to     | Tile_S below     |

|   |          | NSetsusB | to     | Tile_S below     |

|   |          |          |        |                  |

| J | Inputs:  | SetwaitA | from   | Tile_S above     |

|   |          | SetstimA | from   | Tile_S above     |

|   |          | NSuspA   | from   | Tile_S above     |

|   |          | NSetsusA | from   | Tile_S above     |

|   |          | Slice    | from   | Tile_U           |

|   |          | Curract  | from   | Tile_U           |

|   |          | NReset   | from   | Tile_U           |

|   |          | Act      | from   | Tile_U           |

|   |          | NStimp   | from   | BUTLER I/O input |

The operation of tile type 'S' is as follows:

15

20

25

30

40

45

50

55

[0075] Cross-coupled gates 7 and 8 form a srlatch. This 'Suspended' latch is set via gates 13,17 and 18 when NSuspA is low and Curract is high, or via gates 6, 13 and 19 when NSetsusA is low and Act is high. (NSuspA is taken low during suspend; Curract is high when this was the last activity returned to a CPU for scheduling; NSetsusA is taken low during setsuspended; Act will be high whenever this activity was chosen by the most recent Load\_Activity instruction.) The 'Suspended' latch is reset when NReset is low. (NReset is taken low during clrall or during nextact when this activity is being returned to the CPU.) Concurrent set and reset of the 'Suspended' latch cannot occur because NSuspA, NSetsusA and NReset are taken low, only while executing different instructions.

[0076] Cross-coupled gates 11 and 12 form a srlatch. This 'Waiting' latch is set via gates 5 and 16 when SetwaitA and Curract are high. SetwaitA is taken high during setwaiting if this stim-wait channel mask-bit was set in the most recent Load Mask instruction. Curract is high when this was the last activity returned to the CPU for scheduling. The 'Waiting' latch is reset when NReset is low. (NReset is taken low during clrall or during nextact when this activity is being returned to the CPU.) Concurrent set and reset of the 'Waiting' latch cannot occur because SetwaitA is taken high and NReset is taken low, only while executing different instructions.

[0077] Cross coupled gates 9 and 10 form a srlatch. This 'Stimmed' latch is set via gate 15 when NStimp is low, or via gates 14, 15 and 20 when SetstimA and Act are high. (NStimp is an input from a local peripheral; SetstimA is taken high during setstimmed if this stim-wait channel mask-bit was set in the most recent Load\_Mask instruction; Act will be high whenever this activity was chosen by the most recent Load\_Activity instruction.) The 'Stimmed' latch is reset when NReset is low. (NReset is taken low during clrall or during nextact when this activity is being returned to the CPU.) Concurrent set and reset of the 'Stimmed' latch can occur, when NStimp from an asynchronous peripheral source is concurrent with NReset. The normally complementary outputs from the 'Stimmed' srlatch will both be high. This causes no problem because this activity will be being returned to the CPU as the next activity to be scheduled at this time. If removal of concurrent set and reset are coincident, the 'Stimmed' latch will, after the delay needed to resolve the

metastability effect, become either set or reset. Time is available between executing instructions for the latch to settle: if it becomes set, NStimp is assumed to have occurred after nextact; if it becomes reset, NStimp is assumed to have occurred before nextact. Either condition provides for correct system operation.

[0078] When Slice is low, gate 3 output will be high and gate 4 output will be the inverse of the "stimmed" latch value. When Slice is high, gate 3 output will be the inverse of gate 4 output. If gate 4 output is high when Slice switches high, gate 4 output will be maintained high by the low on gate 3 output until Slice switches low. (Slice is high between a Do\_Wait or a Suspend instruction and a subsequent Nextact instruction, i.e. during a context switch and low while a task/activity is running.) The inclusion of the gates 3 and 4 effectively defers visibility of a 'Stimmed' latch value change that is set following a Do\_Wait or a Suspend instruction, until after a subsequent Nextact instruction, (i.e. when the 'Stimmed' latch is set by an asynchronous local peripheral during a context switch).

**[0079]** Ready is established high via gates 1 and 2 when the 'Stimmed' and 'Waiting' latches are both set; or via gate 1 when the 'Suspended' latch is set. (Note;- gate 2 has deferred visibility of a 'Stimmed' latch value that becomes set during a context switch.

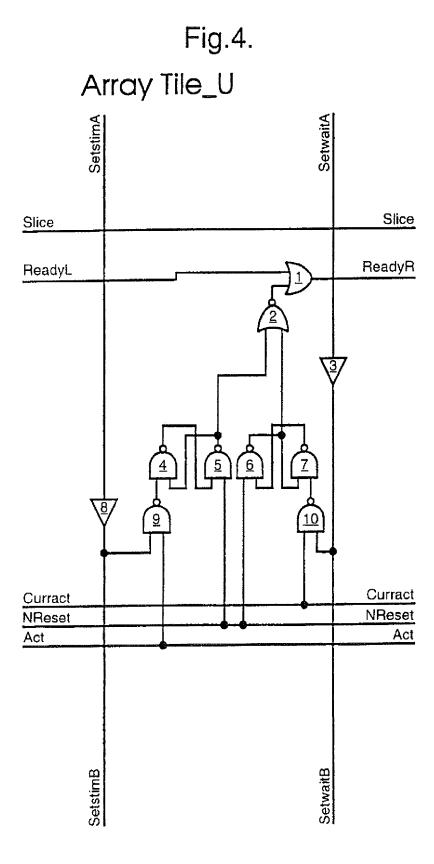

**[0080]** The structure of tile type 'U' is shown in Figure 4. Its function is to hold an activity's internal "Stimmed" and "Waiting" Boolean variables, and to indicate whenever both this pair of "Stimmed" and "Waiting" variables are true, or transmit that a ready condition already exists.

|     |        | SetstimB  | to Tile_U below                  |

|-----|--------|-----------|----------------------------------|

|     |        | SetwaitB  | to Tile_U below                  |

| Inj | puts:  | ReadyL    | from Tile_S or Tile_U or Tile_P  |

|     |        | Curract   | from Tile_U, Tile_P or Tile_E    |

|     |        | NReset    | from Tile_U, Tile_P or Tile_E    |

|     |        | Act       | from Tile_U, Tile_P or Tile_E    |

|     |        | SetstimA  | from Tile_U above                |

|     |        | SetrwaitA | from Tile_U above                |

| Ro  | outes: | Slice     | from Tile U, Tile_P or Tile E to |

|     |        |           | Tile_S, Tile_U or Tile_P         |

|     |        | Curract   | from Tile_U, Tile P or Tile E to |

|     |        |           | Tile_S, Tile_U or Tile_P         |

|     |        | NReset    | from Tile_U, Tile_P or Tile E to |

Act

ReadyR

Outputs:

from Tile\_U, Tile\_P or Tile E to Tile\_S, Tile\_U or Tile\_P

Tile\_S, Tile\_U or Tile\_P

to Tile\_U or Tile\_P or Tile\_E

The operation of tile type 'U' is as follows:

15

20

25

30

35

50

55

[0081] Cross coupled gates 6 and 7 form a snatch. This 'Waiting latch is set via gates 3 and 10 when SetwaitA and Curract are high. (SetwaitA is taken high during setwaiting if this stim-wait channel mask-bit was set in the most recent Load-Mask instruction; Curract is high when this was the last activity returned to the CPU for scheduling.) The 'Waiting' latch is reset when NReset is low. (NReset is taken low during clrall or during nextact when this activity is being returned to the CPU).) Concurrent set and reset of the 'Waiting' latch cannot occur, because SetwaitA is taken high and NReset is taken low, only while executing different instructions.

**[0082]** Cross coupled gates 4 and 5 form a srlatch. This 'Stimmed' latch is set via gates 8 and 9 when SetstimA and Act are high. (SetstimA is taken high during setstimmed if this stim-wait channel mask-bit was set in the most recent Load-Mask instruction; Act will be high whenever this activity was chosen by the most recent Load\_Activity instruction.) The 'Stimmed' latch is reset when NReset is low. (NReset is taken low during clrall or during nextact when this activity is being returned to the processor.) Concurrent set and reset of the 'Stimmed' latch cannot occur, because SetstimA is taken high and NReset is taken low only while executing different instructions.

[0083] ReadyR is established high via gates 1 and 2 when the 'Stimmed' and 'Waiting' latches are both set; or via gate 1 when ReadyL is high.

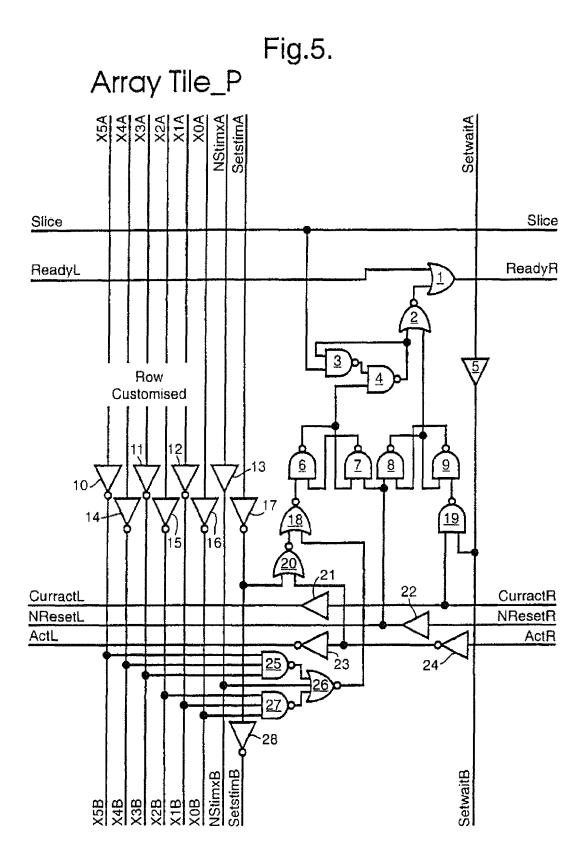

[0084] The structure of the type 'P' is shown in Figure 5. Its function is to hold one pair of external "Stimmed" and "Waiting" Boolean variables for an activity and to indicate a ready condition whenever both this pair of "stimmed" and "waiting" variables are true, or transmit that a ready condition already exists.

|    | Outputs: | ReadyR   | to Tile_U or Tile P or Tile_E   |

|----|----------|----------|---------------------------------|

|    | •        | X5B      | to Tile P below                 |

|    |          | X4B      | to Tile P below                 |

| 5  |          | X3B      | to Tile_P below                 |

|    |          | X2B      | to Tile_P below                 |

|    |          | X1B      | to Tile P below                 |

|    |          | XOB      | to Tile_P below                 |

| 10 |          | NStimxB  | to Tile P below                 |

| 10 |          | SetstimB | to Tile_P below                 |

|    |          | SetwaitB | to Tile P below                 |

|    |          | CurractL | to Tile_S or Tile_U or Tile_P   |

|    |          | NResetL  | to Tile S or Tile U or Tile P   |

| 15 |          | ActL     | to Tile S or Tile U or Tile_P   |

|    | Inputs:  | X5A      | from Tile P above               |

|    |          | X4A      | from Tile_P above               |

|    |          | X3A      | from Tile_P above               |

| 20 |          | X2A      | from Tile_P above               |

|    |          | X1A      | from Tile P above               |

|    |          | XOA      | from Tile P above               |

|    |          | NStimxA  | from Tile_P above               |

|    |          | SetstimA | from Tile P above               |

| 25 |          | SetwaitA | from Tile_P above               |

|    |          | ReadyL   | from Tile S or Tile U or Tile_P |

|    |          | Slice    | from Tile U or Tile P or Tile_E |

|    |          | CurractR | from Tile_U or Tile_P or Tile E |

| 30 |          | NResetR  | from Tile_U or Tile_P or Tile_E |

|    |          | ActR     | from Tile_U or Tile_P or Tile_E |

|    | Routes:  | Slice    | from Tile_E, Tile U or Tile_P   |

|    |          |          | to Tile_S, Tile_U or Tile_P     |

|    |          |          |                                 |

45

50

55

[0085] Each Tile\_P is customised according to its row number in the array by inverting or transmitting values on lines X5A, X4A, X3A, X2A and X1A (see Fig. 19). The customising pattern of Fig. 19 ensures that only one row (the activity being externally addressed) will establish all six lines high. When all six lines are high, the outputs of gates 25 and 27 will both be low.

[0086] In operation, cross-coupled gates 8 and 9 form a srlatch. This 'Waiting' latch is set via gates 5 and 19 when SetwaitA and Curract are high. (SetwaitA is taken high during setwaiting if this stim-wait channel mask-bit was set in the most recent Load\_Mask instruction; Curract is high when this was the last activity returned to the CPU for scheduling.) The 'Waiting' latch is reset via gate 22 when NResetR is low. (NResetR is taken low during clrall or during nextact when this activity is being returned to the CPU.) Concurrent set and reset of the 'Waiting' latch cannot occur, because SetwaitA is taken high and NResetR is taken low, only while executing different instructions.

[0087] Cross coupled gates 6 and 7 form a srlatch. This "stimmed" latch is set via gates 13, 18 and 26 when NStimxA and the outputs of gates 25 and 27 are low, or via gates 17, 18, 20 and 24 when SetstimA and ActR are high. (NStimxA is transmitted from a BUTLER input from an asynchronous external source; the outputs of gates 25 and 27 are low when this activity is being externally addressed; SetstimA is taken high during setstimmed if this stim-wait channel mask-bit was set in the most recent Load Mask instruction; Act will be high whenever this activity was chosen by the most recent Load\_Activity instruction). The "Stimmed" latch is reset via gate 22 when NReset is low. (NReset is taken low during clrall or during nextact when this activity is being returned to the CPU). Concurrent set and reset of the "Stimmed" latch can occur when NStimxA from an asynchronous external source is Concurrent with NResetR. The normally complementary outputs from the "Stimmed" srlatch will both be high. This causes no problem because this activity will be being returned to the CPU as the next activity to be scheduled at this time. If removal of concurrent set and reset are coincident, the "Stimmed" latch will, after the delay needed to resolve the metastability effect, become either set or reset. Time is available between executing instructions for the latch to settle: if it becomes set, NStimxA is assumed to have occurred after nextact; if it becomes reset, NStimxA is assumed to have occurred before nextact. Either condition provides for

correct system operation.

15

50

55

[0088] When Slice is low, gate 3 output will be high and gate 4 output will be the inverse of the "stimmed" latch value. When Slice is high, gate 3 output will be the inverse of gate 4 output. If gate 4 output is high when Slice switches high, gate 4 output will be maintained high by the low on gate 3 output until Slice switches low. (Slice is high between a Do Wait or a Suspend instruction and a subsequent Nextact instruction i.e. during a context switch.) The inclusion of this circuitry effectively defers visibility of a "Stimmed" latch that is set, following a Do Wait or a Suspend instruction, until after a subsequent Nextact instruction (ie when the "Stimmed" latch is set by an asynchronous external stimulus during a context switch).

[0089] ReadyR is established high via gates 1 and 2 when the "Stiinmed" and "Waiting" latches are both set; or via gate I when ReadyL is high. (Gate 2 has deferred visibility of a "stimmed" latch value that becomes set during a context switch)

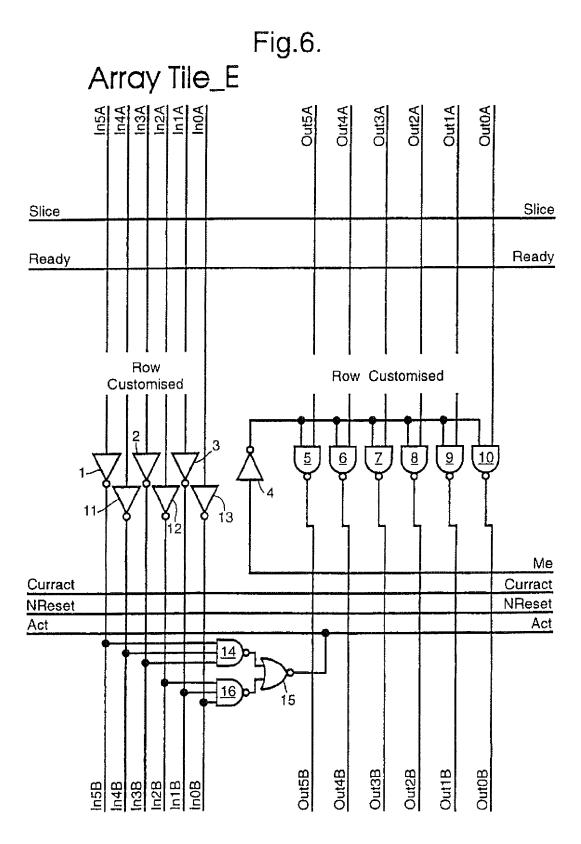

**[0090]** Figure 6 shows the structure of tile type 'E', whose function is to identify whether an activity was chosen by the most recent "Load\_Activity" instruction and to inject a starting point into the distributed activity number encoding logic when this is the next activity to be returned to the CPU for scheduling.

| 15 |          |         |                              |

|----|----------|---------|------------------------------|

|    | Outputs: | Act     | to Tile_U and Tile_R         |

|    |          | In5B    | to Tile E below              |

|    |          | In4B    | to Tile E below              |

|    |          | In3B    | to Tile_E below              |

| 20 |          | In2B    | to Tile_E below              |

|    |          | In1B    | to Tile_E below              |

|    |          | InOB    | to Tile E below              |

|    |          | Out5B   | to Tile E below              |

| 25 |          | Out4B   | to Tile E below              |

|    |          | Out3B   | to Tile E below              |

|    |          | Out2B   | to Tile_E below              |

|    |          | OutlB   | to Tile E below              |

|    |          | OutOB   | to Tile E below              |

| 30 | Inputs:  | InSA    | from Tile_E above            |

|    |          | In4A    | from Tile_E above            |

|    |          | In3A    | from Tile E above            |

|    |          | In2A    | from Tile E above            |

| 35 |          | InIA    | from Tile_E above            |

|    |          | InOA    | from Tile_E above            |

|    |          | Me      | from Tile_R                  |

|    |          | Out5A   | from Tile_E above            |

|    |          | Out4A   | from Tile_E above            |

| 40 |          | Out3A   | from Tile_E above            |

|    |          | Out2A   | from Tile_E above            |

|    |          | Out1A   | from Tile_E above            |

|    |          | OutOA   | from Tile_E above            |

| 45 | Routes:  | Slice   | from Tile R to Tile_U        |

|    |          | Ready   | $from  Tile\_R  to  Tile\_U$ |

|    |          | Curract | $from  Tile\_R  to  Tile\_U$ |

|    |          | NReset  | $fromTile\_RtoTile\_U$       |

|    |          |         |                              |

**[0091]** Each Tile\_E is customised according to its row number in the array by inverting or transmitting values on lines In5A, In4A, In3A, In2A and In1A (see Fig. 19). The customising pattern of Fig. 19 ensures that only one row (the activity chosen by the most recent Load\_Activity instruction) will establish all six lines high. Act is established high via gates 14, 15 and 16 whenever all six lines are high.

[0092] Similarly, each Tile\_E is customised according to its row number in the array by inverting or transmitting values on lines Out5A, Out4A, Out3A, Out2A and Out1A. The customising pattern ensures that the activity that injects a starting point (i.e. establishes Out5B, Out4B, Out3B, Out2B, Out1B and OutOB high) will establish its encoded activity number on lines Out5B, Out4B, Out3B, Out2B, Out1B and OutOB at the bottom of the array.

**[0093]** Out5B, Out4B, Out3B, Out2B, Out1B and OutOB are established high via gates 4, 5, 6, 7, 8, 9 and 10 whenever Me is high. (Me will be high when this is the next activity to be returned to the CPU for scheduling.) At the top of the array Out5A, Out4A, Out3A, Out2A, Out1A and OutOA are hardwired low. This ensures that the encoded number on the six lines at the bottom of the array will be zero when no schedulable activity is present in the array.

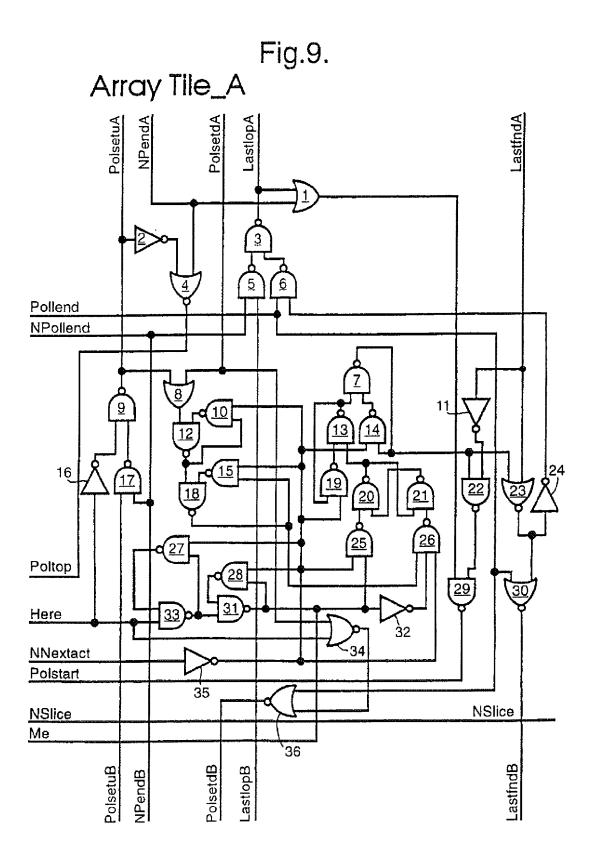

**[0094]** Figure 7 shows the structure of tile type 'R' whose functions are to identify when a particular schedulable activity is the next one to be returned to the CPU and to remember when this is the activity currently running on the CPU ie to generate "Curract, the last "Me". Further functions are to identify when a context switch is in progress and to generate "Slice", to generate a reset for the activity's 'Suspended' latch and all of its 'Stimmed' and 'Waiting' latches, during nextact when the activity is being returned to the CPU, and to distribute signals to reset all the activity's srlatches during clrall.

|    | Outputs: | Here     | to Tile_M             |

|----|----------|----------|-----------------------|

|    |          | NSlice   | to Tile_M             |

|    |          | Slice    | to Tile_E             |

| 15 |          | Curract  | to Tile_E             |

|    |          | NReset   | to Tile_E             |

|    |          | Lclrall  | to Tile_M             |

|    |          | Searchou | to Tile_M             |

| 20 |          | NAct     | to Tile_M             |

|    |          | NNextact | to Tile_M             |

|    |          | NSstartB | to Tile_R below       |

|    |          | NCstartB | to Tile_R below       |

|    |          | NCIrallB | to Tile_R below       |

| 25 |          | NNextB   | to Tile_R below       |

|    |          | SuswtB   | to Tile_R below       |

|    | Inputs:  | Ready    | from Tile E           |

|    |          | Act      | from Tile_E           |

| 30 |          | Searchin | from Tile_M           |

|    |          | Me       | from Tile_M           |

|    |          | NSstartA | from Tile_R above     |

|    |          | NCstartA | from Tile_R above     |

|    |          | NCIrallA | from Tile_R above     |

| 35 |          | NNextA   | from Tile_R above     |

|    |          | NSuswtA  | from Tile_R above     |

|    | Routes:  | Me       | from Tile_M to Tile_E |

55

[0095] Cross-coupled gates 21 and 23 form a srlatch. This 'Switching' latch is set when NSuswtA is low, (i.e. during a Do Wait or a Suspend instruction.) The 'Switching' latch is reset via gates 1 and 30 when NNextA is low. (NNextA is taken low during nextact.) Concurrent set and reset of the 'Switching' latch cannot occur, because NSuswtA and NNextA are taken low, only while executing different instructions. Slice will be high and NSlice will be low when the 'Switching' latch is set.

[0096] Cross-coupled gates 6 and 7 form a srlatch. This 'Started' latch is set via gates 3 and 11 when NSstartA is low and Act is high, (NSstartA is taken low during setstarted; Act will be high whenever this activity was chosen by the most recent Load\_Activity instruction.) The 'Started' latch is reset via gates 10 and 12 when NClrall is low; or via gates 5, 12, 15 and 27 when NCstartA is low and Act is high. (NClrall is taken low during cirall; NCstartA is taken low during clrstarted; Act will be high whenever this activity was chosen by the most recent Load\_Activity instruction.) Concurrent set and reset of the 'Started' latch cannot occur, because NSstartA, NCstartA and NClrallA are taken low, only while executing different instructions.

[0097] When the 'Started' latch is set and Ready is high, the output from gate 2 will be low, indicating that this activity is a candidate for scheduling.

**[0098]** Gates 4, 8, 9 and 13 form a tlatch. The tlatch is used to retain the value on the output of gate 2, existing at the start of nextact for the duration of nextact. At all other times the tlatch output (gate 13 output) tracks the value on the output of gate 2, (i.e. the output of gate 13 will be maintained low for the whole duration of nextact when this activity is a candidate for scheduling).

[0099] Here is established high via gates 14 and 16 when the output of gate 13 is low and Searchin is high (i.e. when

this activity is a candidate for scheduling and no schedulable activity has been found in the search logic chain so far).

**[0100]** Searchou is established low (indicating that a schedulable activity has been found in the search logic chain) via gate 17, when either the output from gate 13 or Searchin are low.

**[0101]** Gates 18, 19, 20 and 22 form a tlatch. This 'Curract' tlatch is used to retain the value of Me between nextacts. It is transparent (updated) only during nextact.

**[0102]** NReset is taken low when either NNextA is taken low and Me is high, via gates 1, 25 and 26, or NCIrallA is taken low, via gates 10, 29 and 26 (i.e. during nextact when this activity is being returned to the CPU, or during clrall).

[0103] LcIrall (a local clear-all signal) is taken high via gate 10, when NCIrallA is taken low (i.e. during cIrall).

[0104] NNextact is taken low via gates 1 and 30, when NNextA is taken low (i.e. during Nextact).

[0105] NAct is established low via gate 27 when Act is high. (Act will be high whenever this activity was selected by the most recent Load Activity instruction.)

**[0106]** The structure of tile type 'M' is shown in Figure 8. Its functions are to configure the next activity search logic chain, to allow designation of the pollset boundaries and to identify when a higher priority activity than that currently running on the CPU may be available for scheduling.

| Outputs:    | Pollend             | to Tile A                                                                                                                                                                            |

|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | NPollend            | to Tile_A                                                                                                                                                                            |

|             | MaybeA              | to Tile_M above                                                                                                                                                                      |

|             | SearchuA            | to Tile_M above                                                                                                                                                                      |

|             | SearchdB            | to Tile_M below                                                                                                                                                                      |

|             | NFoundB             | to Tile_M below                                                                                                                                                                      |

|             | NSpollB             | to Tile_M_below                                                                                                                                                                      |

|             | NCpollB             | to Tile_M below                                                                                                                                                                      |

| Inputs:     | Searchou            | from Tile_R                                                                                                                                                                          |

|             | Here                | from Tile R                                                                                                                                                                          |

|             | NAct                | from Tile_R                                                                                                                                                                          |

|             | LcIrall             | from Tile_R                                                                                                                                                                          |

|             | NSlice              | from Tile_R                                                                                                                                                                          |

|             | Polstart            | from Tile_A                                                                                                                                                                          |

|             | Poltop              | from Tile_A                                                                                                                                                                          |

|             | NFoundA             | from Tile_M above                                                                                                                                                                    |

|             | NSpollA             | from Tile_M above                                                                                                                                                                    |

|             | NCpollA             | from Tile_M above                                                                                                                                                                    |

|             | SearchuB            | from Tile M below                                                                                                                                                                    |

|             | MaybeB              | from Tile_M below                                                                                                                                                                    |

| Routes:     | Here                | from Tile_R to Tile_A                                                                                                                                                                |

|             | NNextact            | from Tile R to Tile A                                                                                                                                                                |

|             | Me                  | from Tile_A to Tile R                                                                                                                                                                |

|             | NSlice              | from Tile R to Tile_A                                                                                                                                                                |

| SearchdA/Se | earchin from Tile_N | M above to Tile_R                                                                                                                                                                    |

|             | Inputs:             | NPollend MaybeA SearchuA SearchdB NFoundB NSpollB NCpollB Inputs: Searchou Here NAct LcIrall NSlice Polstart Poltop NFoundA NSpollA NCpollA SearchuB MaybeB Routes: Here NNextact Me |

45

50

55

[0107] Cross-coupled gates 12 and 13 form a srlatch. This 'Pollend' latch is set via gates 8, 15 and 20 when NSpollA and NAct are low. (NSpollA is taken low during setpollend; NAct will be low whenever this activity was chosen by the most recent Load\_Activity instruction.) The 'Pollend' latch is reset via gate 16 when LcIrall is high, or via gates 9, 16 and 21 when NCpollA and NAct are low. (LcIrall is taken high during chrall; NCpollA is taken low during cirpollend; NAct will be low whenever this activity was chosen by the most recent Load\_Activity instruction.) Concurrent set and reset of the 'Pollend' latch cannot occur, because NSpollA, NCpollA and LcIrall are taken low, only while executing different instructions

[0108] A round robin search loop is formed for each designated pollset. A single search chain passing through all activities is configured that runs through each round robin search loop in turn, respecting the priority order of the pollsets. [0109] When not selected as the lowest activity number in a pollset, Pollend will be low and complementary NPollend will be high. The value on SearchuB is transmitted to SearchuA via gates 1 and 3. When not the starting point in a round robin search, Polstart will be low. The value on Searchou will be transmitted to SearchdB via gates 5, 6, 7 and 10 and the value on NFoundA will be transmitted to NFoundB via gates 18 and 25. (NFoundA will be low when a higher priority pollset has already found an activity to schedule.) When the starting point in a round robin search, Polstart will be high.

The value on NFoundA will be transmitted to SearchdB via gates 5, 6, 7 and 11, and the value on Searchou will be transmitted to NFoundB via gates 19 and 25.

**[0110]** When selected as the lowest activity number in a pollset (i.e. with Pollend high and complementary Pollend low) a round robin search loop boundary is formed. The value on SearchuB is transmitted to SearchdB via gates 4 and 6. When not the starting point in a round robin search, Polstart will be low, The value on NFoundA will be transmitted to NFoundB via gates 18 and 25, and the value on Searchou will be transmitted to SearchuA via gates 1, 2, 7 and 10. When the starting point in a round robin search, Polstart will be high. The value on NFoundA will be transmitted to NSearchuA via gates 1, 2, 7 and 11, and the value on Searchou will be transmitted to FoundB via gates 12 and 25.

**[0111]** At the top of the array SearchuA is connected to SearchdA to complete a search loop, and NFoundA hardwired high to indicate that no higher priority poll set has found a schedulable activity.

**[0112]** At the bottom of the array SearchdB is connected to SearchuB to complete a search loop. NFoundB is high when no schedulable activity is present in the array and is connected to D6out, to return activity 64 (the idle activity).

**[0113]** A logic chain running up the array is used to determine when there is a schedulable activity belonging to a higher priority pollset. The logic chain is made false when it crosses the top of the pollset of the last activity returned to the CPU. The chain is made true when a potentially schedulable activity is identified.

**[0114]** Gates 17, 22, 23 and 28 form a tlatch that is used to retain the value of Poltop between context switches (i.e. gate 17 output remembers when this activity has the smallest number in the poll set of the activity currently running on the CPU). The tlatch is made transparent (updated) when NSlice is low. (Nslice will be low during a context switch, i.e. between a Suspend or a Do\_Wait instruction and a subsequent Nextact instruction.)

**[0115]** MaybeA is established low via gate 14, when the output on gate 17 is high. MaybeA is established high when the output on gate 17 is low. Either Me or MaybeB are high via gates 14 and 27.