(19)

#

# (11) **EP 2 166 657 A1**

(12)

EUROPEAN PATENT APPLICATION

published in accordance with Art. 153(4) EPC

- (43) Date of publication: 24.03.2010 Bulletin 2010/12

- (21) Application number: 08739878.0

Europäisches Patentamt

European Patent Office Office européen des brevets

(22) Date of filing: 04.04.2008

- (51) Int Cl.: *H02M 3/155*<sup>(2006.01)</sup>

- (86) International application number: PCT/JP2008/056772

- (87) International publication number: WO 2009/008197 (15.01.2009 Gazette 2009/03)

- (84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MT NL NO PL PT RO SE SI SK TR Designated Extension States:

AL BA MK RS

- (30) Priority: 09.07.2007 JP 2007179237

- (71) Applicant: Murata Manufacturing Co. Ltd. Nagaokakyo-shi, Kyoto 617-8555 (JP)

- (72) Inventors:

UNO, Yoshiyuki Nagaokakyo-shi Kyoto 617-8555 (JP)

- TOKUGAWA, Tomokuni Nagaokakyo-shi Kyoto 617-8555 (JP)

HOSOTANI, Tatsuya

- HOSOTANI, Tatsuya Nagaokakyo-shi Kyoto 617-8555 (JP)

- (74) Representative: Laufhütte, Dieter et al Lorenz-Seidler-Gossel Widenmayerstrasse 23 80538 München (DE)

#### (54) **PFC CONVERTER**

(57) A diode bridge (B1) that performs full-wave rectification on an AC input power supply (Vac) is provided. A switching element (Q1) that performs switching on an output voltage thereof, an inductor (L1) that passes a current interrupted by the switching element (Q1) and that accumulates and emits excitation energy, a diode (D1), and a smoothing capacitor (C1) constitute a stepup chopper circuit. A digital signal processing circuit (13) detects a phase of an input voltage (Vi), and a switching frequency of the switching element (Q1) is modulated in accordance with the phase. Accordingly, the switching frequency can be appropriately modulated without depending on an input voltage, so that a wide range of input voltages can be accepted while suppressing EMI noise with a peak generated in the switching frequency and higher-order frequency components thereof.

#### Description

**Technical Field**

<sup>5</sup> **[0001]** The present invention relates to an alternating current to direct current (AC-DC) converter that receives an AC power supply and that outputs a DC voltage, particularly to a power-factor correction (PFC) converter for improving a power factor.

Background Art

10

20

**[0002]** In Japan, Europe, etc., harmonic current control that is classified in accordance with an application or input power is performed. In order to respond to such control, a circuit called a PFC converter is added to a power supply of general home appliances subjected to harmonic current control, whereby measures have been taken to suppress harmonic currents.

<sup>15</sup> **[0003]** In a typical switching power supply device using a commercial AC power supply as an input power supply, the commercial AC power supply is rectified and smoothed so as to be converted to a DC voltage, and switching by a DC-DC converter is performed on the DC voltage. Therefore, an input current is discontinuous and is significantly distorted compared to a sinusoidal wave. This causes a harmonic current.

**[0004]** For the purpose of suppressing the harmonic current, a PFC converter is provided in a stage after a full-wave rectifier circuit and before a smoothing circuit configured using a smoothing capacitor.

- **[0005]** This PFC converter, which is constituted by a chopper circuit, operates so that an envelope of an input current waveform and that of an input voltage waveform have the same phase, i.e., have similar sinusoidal waveforms. Accordingly, a harmonic current can be suppressed to a certain level or lower.

- [0006] However, in a typical PFC converter that performs a chopper operation at a certain switching frequency, electromagnetic interference (EMI) noise with a high peak value occurs in the switching frequency and higher-order frequencies thereof. Patent Document 1 discloses a PFC converter for improving such circumstances. In this PFC converter, a switching frequency is changed within a range where an original purpose is not impaired, whereby EMI noise is dispersed on a frequency axis to decrease the peak value of the EMI noise. Also, the switching frequency of the PFC converter at the vicinity of a peak value of an input voltage waveform is increased, whereby the size of an inductor L1 can be reduced.

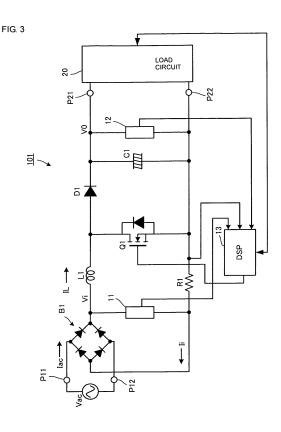

- [0007] Now, a configuration example of the PFC converter disclosed in Patent Document 1 will be described with reference to Fig. 1.

[0008] In the power-factor improving circuit illustrated in Fig. 1, a series circuit including a step-up reactor L1, a switching element O1 constituted by a MOSEET and a current detecting resistor P is connected to both output terminals of a

element Q1 constituted by a MOSFET, and a current detecting resistor R is connected to both output terminals of a diode bridge B1 that rectifies an AC power supply voltage of an AC power supply Vac1. A series circuit including a diode D1 and a smoothing capacitor C1 is connected to both ends of the switching element Q1, and a load RL is connected

<sup>35</sup> D1 and a smoothing capacitor C1 is connected to both ends of the switching element Q1, and a load RL is connected to both ends of the smoothing capacitor C1. The switching element Q1 is turned on/off under pulse width modulation (PWM) control by a control circuit 10. The current detecting resistor R detects an input current flowing through the diode bridge B1.

[0009] The control circuit 10 includes an error amplifier 111, a multiplier 112, an error amplifier 113, a voltage controlled oscillator (VCO) 115, and a PWM comparator 116.

**[0010]** The error amplifier 111 calculates an error between a voltage of the smoothing capacitor C1 and a reference voltage E1. The multiplier 112 multiplies an error voltage signal by a voltage rectified by the diode bridge B1. The error amplifier 113 generates an error between a multiplication result generated by the multiplier 112 and a current signal flowing through the diode bridge B1 and outputs the error to the PWM comparator 116.

<sup>45</sup> **[0011]** The VCO 115 generates a triangular-wave signal of a frequency according to a voltage value of a rectified AC power supply voltage.

**[0012]** In the PWM comparator 116, a triangular-wave signal from the VCO 115 is input to a minus terminal, whereas a signal from the error amplifier 113 is input to a plus terminal. That is, the PWM comparator 116 applies a duty pulse according to a current flowing through the diode bridge B1 and an output voltage to the switching element Q1. This duty

<sup>50</sup> pulse is a pulse-width control signal that continuously compensates for fluctuation of an AC power supply voltage and a DC load voltage in constant cycles. With this configuration, control is performed so that the waveform of an AC power supply current matches the waveform of an AC power supply voltage, whereby the power factor is improved.

[Patent Document 1] Japanese Unexamined Patent Application Publication No. 2004-282958

55

**Disclosure of Invention**

Problems to be Solved by the Invention

- <sup>5</sup> **[0013]** However, in the configuration disclosed in Patent Document 1, an instantaneous value of an input voltage is captured and is used as a voltage to be applied to the VCO, whereby the switching frequency is modulated in accordance with the instantaneous value of the input voltage. Therefore, the switching frequency of the PFC converter fluctuates in accordance with fluctuation of an effective value of the input voltage.

- [0014] For this reason, in a case of electronic apparatuses that are used in a plurality of areas where different input voltages are used, the switching frequency significantly varies depending on the area where the electronic apparatuses are used. For example, the effective value is 100 V in Japan, whereas the effective value is 220 to 240 V in Europe. In order to realize an electronic apparatus that can be used anywhere in the world, the electronic apparatus needs to be adaptable to a wide range of input voltages, e.g., from 85 to 264 V in effective values, considering fluctuation in voltage or the like.

- 15 [0015] If the switching frequency is allowed to be changed simply in accordance with an input voltage, the switching frequency significantly changes within a voltage range necessary for worldwide use (within a range from 85 to 264 V). When the switching frequency significantly changes in this manner, it is necessary to use an inductor having an inductance that prevents saturation of the inductor even when the switching frequency is low. This causes an increase in size of the inductor. On the other hand, when the switching frequency is high, a large switching loss occurs.

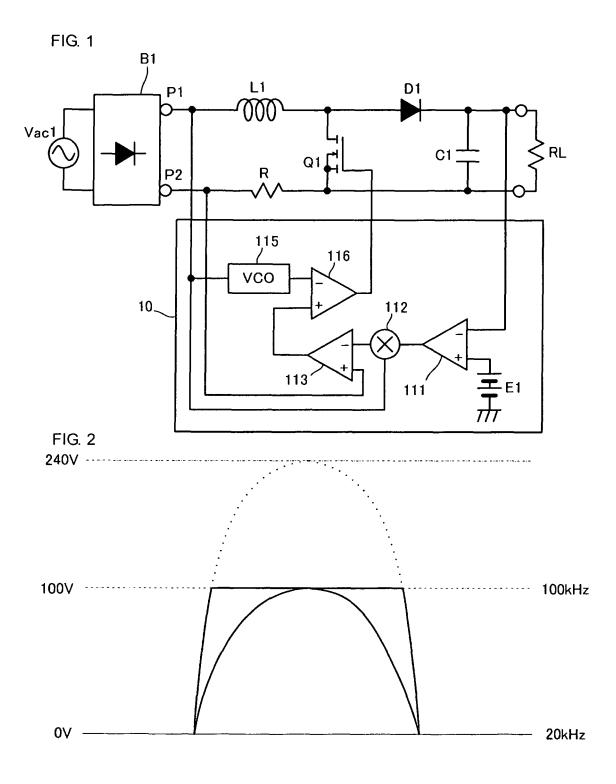

- 20 [0016] In order to suppress such an increase in switching frequency, Patent Document 1 suggests a method for cramping the upper limit of the switching frequency. In this case, however, the following problem arises. That is, as illustrated in Fig. 2, in a case where a circuit is designed by optimizing the switching frequency when the effective value of the input voltage is 100 V, the circuit operates at the upper limit of the switching frequency in the most region of an input voltage waveform in an area where the effective value of the input voltage is 240 V. Such a situation significantly

- deteriorates an effect of appropriately changing the switching frequency and dispersing EMI noise that occurs with a peak. [0017] Accordingly, an object of the present invention is to enable appropriate modulation of a switching frequency without depending on an input voltage and to provide a PFC converter adaptable to a wide range of input voltages while suppressing a peak of EMI noise in the switching frequency and higher-order frequencies thereof.

- 30 Means for Solving the Problems

[0018] In order to solve the above-described problems, the present invention has the following configuration.

(1) In a PFC converter including at least two switching circuits that perform switching on an AC voltage input from

an AC input power supply, an inductor that passes a current interrupted by the switching circuits, and a smoothing circuit that smoothes an output voltage in a stage after the inductor, the PFC converter includes:

phase detecting means for detecting a phase of a voltage of the AC input power supply; and switching frequency modulating means for modulating a switching frequency of the switching circuits in accordance with a phase of a voltage waveform of the AC input power supply, a half cycle of the voltage waveform of the AC input power supply being one cycle.

#### [0019]

40

- 45 (2) In a PFC converter including a rectifier circuit that performs full-wave rectification on an AC input power supply, a switching circuit that performs switching on an output voltage of the rectifier circuit, an inductor that passes a current interrupted by the switching circuit (and that accumulates and emits excitation energy), and a smoothing circuit that smoothes the output voltage in a stage after the inductor, the PFC converter includes:

- 50 phase detecting means for detecting a phase of a voltage of the AC input power supply; and switching frequency modulating means for modulating a switching frequency of the switching circuit in accordance with a phase of a voltage waveform of the AC input power supply, a half cycle of the voltage waveform of the AC input power supply being one cycle.

#### 55 **[0020]**

(3) On the basis of the phase of the voltage (waveform) of the AC input power supply, the switching frequency modulating means decreases the switching frequency of the switching circuit when an instantaneous value of the

voltage of the AC input power supply is at a lower limit or at the vicinity of the lower limit, and increases the switching frequency of the switching circuit when the instantaneous value of the voltage of the AC input power supply is at an upper limit or at the vicinity of the upper limit.

#### 5 **[0021]**

10

15

20

30

(4) The switching frequency modulating means is means for obtaining a peak value or an effective value of an input voltage on the basis of an instantaneous value obtained through sampling of the voltage of the AC input power supply and shifts a modulation range of the switching frequency of the switching circuit to a low frequency side as the peak value or the effective value is higher.

#### [0022]

(5) The phase detecting means includes a waveform shaping circuit that shapes a waveform of a voltage signal of the AC input power supply (by using a comparator, a Zener diode, a shunt regulator, a photo coupler, or the like) to generate a substantially-rectangular-wave signal, and means for sampling the rectangular-wave signal and detecting a rise or fall time of the rectangular-wave signal.

#### [0023]

(6) The phase detecting means samples a voltage signal of the AC input power supply and detects at least one of a time when an instantaneous value of the voltage signal reaches a peak, a time when the instantaneous value is a minimum, and a time when the instantaneous value is a predetermined value.

#### 25 Advantages

[0024] According to the present invention, the following advantages can be obtained.

(1) A switching frequency of a switching circuit is modulated in accordance with a phase of a voltage waveform of an AC input power supply in which a half cycle of the voltage waveform of the AC input power supply is used as a cycle. Accordingly, a PFC converter that is capable of performing switching at an optimal switching frequency regardless of an effective value of the voltage of the AC input power supply and that is adaptable to a wide range of input voltages can be constituted.

#### *35* **[0025]**

(2) The switching frequency of the switching circuit is decreased when an instantaneous value of the AC input power supply voltage is at a lower limit or at the vicinity of the lower limit, whereas the switching frequency of the switching circuit is increased when the instantaneous value of the AC input power supply voltage is at an upper limit or at the vicinity of the upper limit. This enables use within a range where an inductor is not saturated at a time when an input current becomes large without causing an increase in inductance of the inductor, and the size and weight can be reduced. Also, since the switching frequency of the switching circuit is decreased when an instantaneous value of the voltage of the AC input power supply is at a lower limit or at the vicinity of the lower limit, a switching loss can be reduced.

#### 45

40

#### [0026]

50

(3) A modulation range of the switching frequency of the switching circuit shifts to a low frequency side as a peak value or an effective value of the AC input power supply voltage is higher. Thus, a switching loss can be reduced by decreasing the switching frequency in a range where the inductor is not saturated, and the efficiency can be enhanced.

#### [0027]

(4) A substantially-rectangular-wave signal generated through waveform shaping of a voltage signal of the AC input power supply is sampled, and the phase of the AC input power supply voltage is detected on the basis of a rise or fall time of the signal. Accordingly, only input information of binary signals is necessary to be handled. This reduces an operation process load, whereby the number of bits of an A/D converter can be advantageously reduced, and

the cost and power consumption can be reduced.

#### [0028]

(5) A voltage signal of the AC input power supply is sampled, and the phase of the AC input power supply voltage is detected from at least one of a time when an instantaneous value of the voltage signal reaches a peak, a time when the instantaneous value is a minimum, and a time when the instantaneous value is a predetermined value. Accordingly, a mere voltage dividing resistor circuit may be used as a circuit provided outside a DSP, for example. As a result, the circuit configuration can be simplified, the size can be reduced, and the reliability can be enhanced.

Brief Description of Drawings

#### [0029]

15

20

[Fig. 1] Fig. 1 is a circuit diagram of a PFC converter disclosed in Patent Document 1.

[Fig. 2] Fig. 2 is a diagram illustrating an example of change of a switching frequency with respect to an input voltage of a conventional PFC converter.

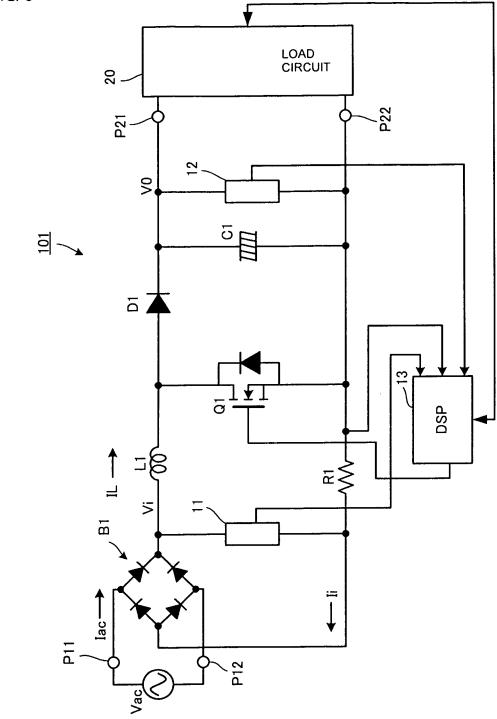

[Fig. 3] Fig. 3 is a circuit diagram of a PFC converter according to a first embodiment.

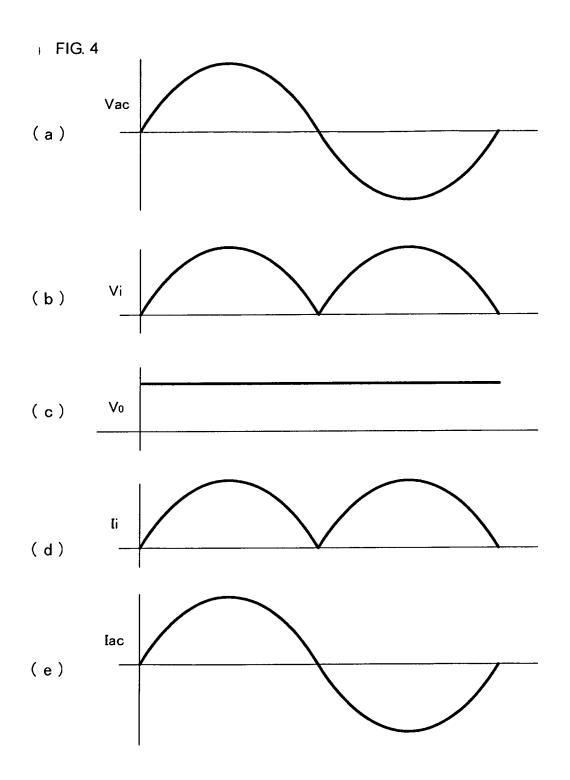

[Fig. 4] Fig. 4 includes waveform diagrams of a voltage and current of individual parts of the PFC converter.

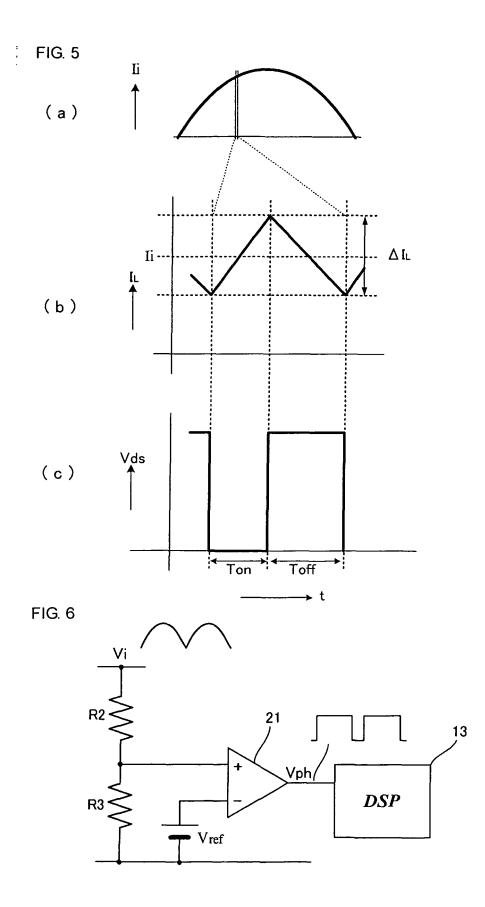

[Fig. 5] Fig. 5 includes diagrams illustrating waveforms of a current flowing through an inductor in the PFC converter and an example of on and off times of a switching element.

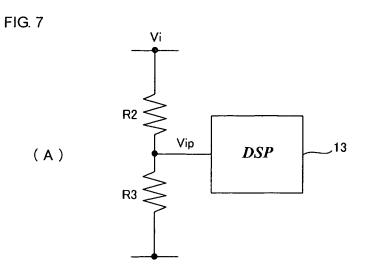

[Fig. 6] Fig. 6 is a diagram illustrating a configuration example of an input voltage detecting circuit.

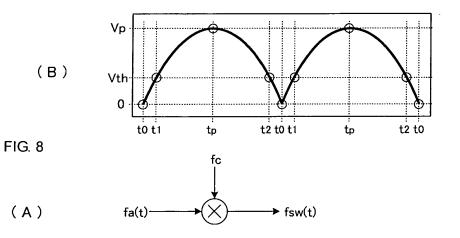

[Fig. 7] Fig. 7 includes diagrams illustrating another configuration example of the input voltage detecting circuit. [Fig. 8] Fig. 8 includes diagrams illustrating modulation control of a switching frequency in accordance with an

- instantaneous value of an input voltage.

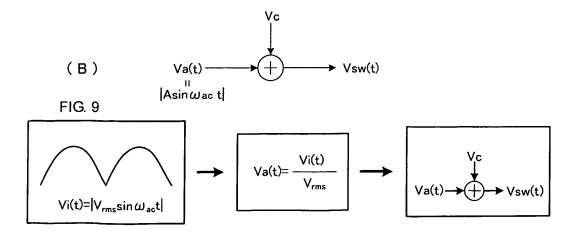

- <sup>25</sup> [Fig. 9] Fig. 9 is a diagram illustrating modulation control of a switching frequency in a PFC converter according to a second embodiment.

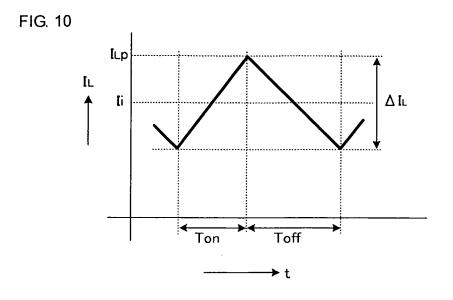

[Fig. 10] Fig. 10 is a diagram illustrating a method for detecting an input voltage in a PFC converter according to a third embodiment.

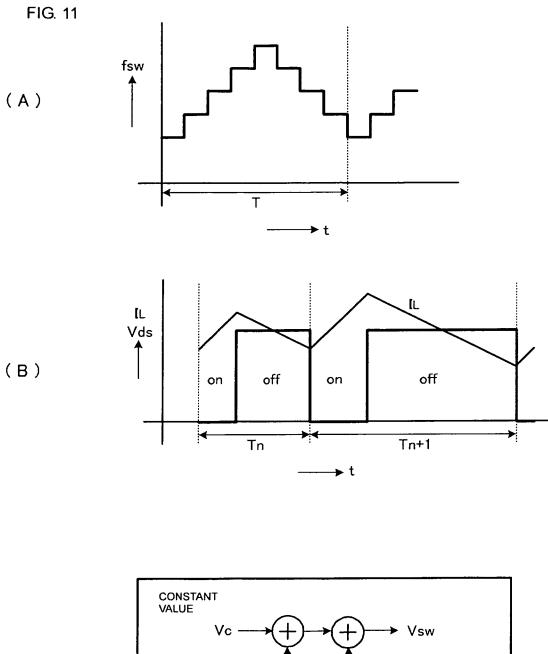

[Fig. 11] Fig. 11 includes diagrams illustrating modulation control of a switching frequency in a PFC converter according to a fourth embodiment.

[Fig. 12] Fig. 12 is a diagram illustrating an example of change of a modulation range of a switching frequency caused by change of a peak value or an effective value of an input voltage of a PFC converter according to a fifth embodiment.

[Fig. 13] Fig. 13 is a circuit diagram of a PFC converter according to a sixth embodiment.

35

Reference Numerals

#### [0030]

| 40 | Vac:               | AC input power supply                   |

|----|--------------------|-----------------------------------------|

|    | Vi:                | full-wave rectification input voltage   |

|    | B1:                | diode bridge                            |

|    | L1, L11, and L12:  | inductor                                |

|    | Q1, Q11, and Q12:  | switching element                       |

| 45 | D1 and D11 to D14: | diode                                   |

|    | C1 and C11:        | smoothing capacitor                     |

|    | R1:                | current detecting resistor              |

|    | 11:                | input voltage detecting circuit         |

|    | 12:                | output voltage detecting circuit        |

| 50 | 13:                | digital signal processing circuit (DSP) |

|    | 20:                | load circuit                            |

|    | 101:               | PFC converter                           |

55

Best Modes for Carrying Out the Invention

<First Embodiment>

Fig. 3 is a circuit diagram of the PFC converter according to the first embodiment. In Fig. 3, reference numerals P11 and P12 denote input ports of the PFC converter 101, and reference numerals P21 and P22 denote output ports of the PFC converter 101. An AC input power supply Vac, which is a commercial AC power supply, is input to the input ports P11 and P12, and a load circuit 20 is connected to the output ports P21 and P22.

<sup>5</sup> The load circuit 20 is, for example, a circuit of a DC-DC converter and an electronic apparatus that is supplied with power by the DC-DC converter.

**[0032]** In an input stage of the PFC converter 101, a diode bridge B1 that performs full-wave rectification on the AC input power supply Vac is provided. On the output side of the diode bridge B1, a series circuit including an inductor L1, a switching element Q1, and a current detecting resistor R1 is connected. A rectifying and smoothing circuit including an inductor L1, a diode D1 and a current detecting resistor R1 is connected. A rectifying and smoothing circuit including the diode D1 and a current detecting resistor R1 is connected.

- a diode D1 and a smoothing capacitor C1 is connected to both ends of the switching element Q1. The inductor L1, the switching element Q1, the diode D1, and the smoothing capacitor C1 constitute a so-called step-up chopper circuit.

[0033] An input voltage detecting circuit 11 is provided between both ends on the output side of the diode bridge B1. Also, an output voltage detecting circuit 12 is provided between the output ports P21 and P22. A digital signal processing circuit 13 is constituted by a digital signal processor (DSP) and controls the PFC converter 101 through digital signal

- <sup>15</sup> processing. That is, the digital signal processing circuit 13 receives an output signal of the input voltage detecting circuit 11 and detects the phase of the voltage of the AC input power supply in the method described below. Also, the digital signal processing circuit 13 receives an output signal of the output voltage detecting circuit 12 and detects an output voltage. Furthermore, the digital signal processing circuit 13 turns on/off the switching element Q1 at a predetermined switching frequency.

- 20 [0034] Furthermore, the digital signal processing circuit 13 includes a port for communicating with the load circuit 20, thereby performing data communication or input/output of signals, constantly transmitting a status or the like of the converter to the load circuit (electronic apparatus), transmitting an input voltage, an output voltage, an output current, and the like, and receiving a load status or the like from the load circuit side to reflect it in switching control. [0035] Fig. 4 includes waveform diagrams of a voltage and current in individual parts of the PFC converter illustrated

- <sup>25</sup> in Fig. 3 in a commercial cycle of the AC input power supply. As illustrated in Fig. 4(a), the AC input power supply Vac is a sinusoidal AC voltage having a predetermined frequency and a predetermined effective value. Full-wave rectification performed by the diode bridge B1 causes the input voltage applied to the foregoing step-up chopper circuit to have a full-wave rectification waveform, as illustrated in Fig. 4(b). Also, as illustrated in Fig. 4(c), an output voltage Vo of the PFC converter 101 is a DC voltage depending on a prede-

- termined step-up ratio and an effective value of the AC input power supply voltage. A current li flowing on the output side of the diode bridge B1 has a similar waveform as the full-wave rectification waveform illustrated in Fig. 4(b). A current lac flowing through the AC input power supply has a waveform similar to the voltage waveform (Fig. 4(a)). Accordingly, a harmonic current is suppressed.

[0036] Fig. 5 includes waveform diagrams of a voltage and current of the PFC converter 101 in a switching cycle.

- In Fig. 5, (a) is a current waveform of an average value Ii of a current flowing through the inductor L1 in a commercial cycle, (b) is a waveform diagram of a current I<sub>L</sub> flowing through the inductor L1 in a switching cycle, part of which is enlarged on a time axis, and (c) is a waveform diagram of a drain-source voltage Vds of the switching element Q1.

[0037] In an on period Ton of the switching element Q1, the current I<sub>L</sub> flows through the inductor L1, and the current

- $I_L$  increases with a slope determined in accordance with a voltage between both ends of the inductor L1 and the inductance of the inductor L1. After that, in an off period Toff of the switching element Q1, the current  $I_L$  decreases with a slope determined in accordance with a voltage between the both ends of the inductor L1 and the inductance thereof. In this way, the current  $I_L$  flowing through the inductor L1 fluctuates in the switching cycle within the width of a current ripple  $\Delta I_L$ . **[0038]** The digital signal processing circuit 13 performs switching control so that an average value of the current flowing through the inductor follows a full-wave rectification waveform (sinusoidal wave). Accordingly, an input current propor-

- 45 tional to an input voltage flows, so that a harmonic is suppressed. [0039] Fig. 6 is a circuit diagram illustrating a specific configuration example of the input voltage detecting circuit 11 illustrated in Fig. 3. In Fig. 6, a voltage-dividing resistor circuit including resistors R2 and R3 is configured to divide an input voltage Vi and input the voltage to a plus terminal of a comparator 21, and input a reference voltage Vref to a minus terminal of the comparator 21. Thus, an output voltage Vph of the comparator 21 serves as a rectangular-wave signal

- 50 that is at a high level when the full-wave rectification input voltage Vi exceeds a predetermined threshold and is at a low level when the full-wave rectification input voltage Vi does not exceed the predetermined threshold. The digital signal processing circuit 13 detects a phase angle 0° of the full-wave rectification input voltage Vi on the basis of a rise time from a low level to a high level of an output signal of the comparator 21 and/or a fall time from a high level to a low level. [0040] The rise time and the fall time of the rectangular-wave signal, which is the output signal Vph of the comparator

- 55 21, change when the effective value (or the peak value) of the full-wave rectification input voltage Vi fluctuates. However, a phase angle of 0° or 180° of the AC input power supply Vac is to be detected, and thus the phase angle can be detected without depending on the voltage of the AC input power supply.

[0041] Fig. 7 illustrates a configuration example of the input voltage detecting circuit 11 different from the configuration

illustrated in Fig. 6. In this example, the voltage-dividing resistor circuit including the resistors R2 and R3 is simply provided, and a divided voltage therefrom is applied to the digital signal processing circuit 13. The digital signal processing circuit 13 receives a voltage signal of the full-wave rectification input voltage Vi, samples the voltage signal in a predetermined sampling cycle and converts the voltage signal into digital data, and sequentially stores the digital data. Then,

- the digital signal processing circuit 13 detects the phase angle of the full-wave rectification input voltage Vi on the basis of the digital data sequence. The method therefor includes the following three methods.

[0042] In the first method, as illustrated in Fig. 7, a time tp when a sampling value reaches a peak during change is detected. At that time, a maximum value in the data sequence may be detected. In a case where the sampling cycle is rough compared to a commercial cycle, the time when the peak is obtained may be calculated through approximate

- 10 calculation of a sinusoidal wave on the basis of a series of pieces of data. The time tp is detected as a phase angle of 90° (or 270°).

**[0043]** In the second method, times t1 and t2 when a voltage signal of the full-wave rectification input voltage reaches a predetermined threshold Vth are detected, and an intermediate time between t1 and t2 is detected as a phase angle of  $0^{\circ}$  (or 180°).

- <sup>15</sup> **[0044]** In the third method, a time t0 when a minimum value is obtained in the sampling data sequence is detected, and the time is detected as a phase angle of 0° (or 180°) of the full-wave rectification input voltage. By detecting the phase angle of the full-wave rectification input voltage in the above-described manner, a time change of the phase angle or the time of a half cycle is determined, so that the frequency of the full-wave rectification input voltage can be detected.

- [0045] According to the above-described circuit configuration, the circuit configuration of the input voltage detecting circuit 11 is extremely simplified, and the number of components can be reduced.

[0046] On the basis of the phase of the voltage signal of the full-wave rectification input voltage detected in the above-described in the above-described circuit and the number of the phase of the voltage signal of the full-wave rectification input voltage detected in the above-described circuit and the number of the phase of the voltage signal of the full-wave rectification input voltage detected in the above-described circuit and the number of the number

described manner, a sinusoidal wave (an absolute value of the sinusoidal wave) that synchronizes with the input voltage is shaped inside the digital signal processing circuit 13. On the basis of the sinusoidal wave, the switching frequency of the switching element Q1 is modulated.

**[0047]** Fig. 8 includes diagrams illustrating the control thereof. In Fig. 8(A), fc represents a fixed switching frequency in a case where frequency modulation is not performed, and fa(t) represents a modulation frequency that fluctuates with time lapse. Switching of the switching element Q1 is performed by using a frequency fsw(t), which is obtained as a result of modulating the fixed frequency fc with the modulation frequency fa(t).

- **[0048]** Fig. 8(B) illustrates a process in the digital signal processing circuit 13. Here, a value Vc is a value corresponding to the foregoing fixed frequency fc, and Va(t) is a value corresponding to the foregoing modulation frequency fa(t). That is, when an angular frequency of an input voltage is represented by  $\omega ac$ , Va(t) = |Asin $\omega act$ | is obtained. Since  $\omega ac$  is known as described above, Va(t) is calculated on the basis of the value of sin $\omega act$ . Vsw is a value corresponding to the foregoing switching frequency fsw(t) and is obtained by calculating Vsw(t) = Vc+Va(t). The switching element Q1 is turned

- <sup>35</sup> on/off in a switching cycle for realizing the switching frequency according to the value of Vsw(t). As a result, the switching frequency fluctuates within a predetermined frequency range, so that EMI noise with a peak that occurs in the switching frequency and higher-order frequency components thereof can be suppressed.

<Second Embodiment>

40

**[0049]** In the first embodiment, a sinusoidal wave that synchronizes with an input voltage is generated in the digital signal processing circuit 13. In the second embodiment, an input voltage signal is detected and is normalized, and the normalized signal is used as a signal for frequency modulation. The circuit configuration of a PFC converter is the same as that illustrated in Fig. 3.

45 [0050] Fig. 9 is a diagram illustrating a process of a digital signal control circuit of the PFC converter according to the second embodiment. In Fig. 9, an input voltage Vi is expressed by the following equation. [0051]

50

25

Vi(t) = |Vrms sinwact|

Here, Vrms represents an effective value of the input voltage Vi, and ωac represents an angular frequency of Vi(t). This voltage signal is normalized by using the effective value thereof, and the normalized signal is expressed by Va(t) in the following equation.

55

[0052]

Va(t) = Vi(t) / Vrms

<sup>5</sup> Then, the foregoing Va(t) is added to the value Vc corresponding to the fixed frequency, whereby a value Vsw(t) corresponding to the switching frequency is obtained.

**[0053]** The digital signal processing circuit 13 performs switching on the switching element Q1 in a switching cycle for realizing the switching frequency according to the foregoing value Vsw(t).

[0054] In this way, by normalizing the input voltage by using the effective value thereof, constant modulation of the switching frequency can be performed even if the effective value of the input voltage changes.

<Third Embodiment>

[0055] In the first and second embodiments, a voltage signal of a full-wave rectification input voltage is directly input to the digital signal processing circuit in order to detect a voltage waveform of the AC input power supply. In the third embodiment, an input voltage is detected on the basis of a current flowing through the inductor L1. The circuit configuration of a PFC converter is the same as that illustrated in Fig. 3.

**[0056]** Fig. 10 is a diagram illustrating an on time Ton and an off time Toff of the switching element Q1 and a waveform of a current flowing through the inductor L1.

20 [0057] The current I<sub>L</sub> flowing through the inductor L1 is detected by the digital signal processing circuit 13 on the basis of a dropped voltage of the current detecting resistor R1. The digital signal processing circuit 13 then calculates an instantaneous value of the full-wave rectification input voltage Vi in accordance with the following equations. [0058]

25

$\Delta I_L = (Vi/L) \text{ Ton } \cdots (1)$

30

35

$Vi = L\Delta I_L / Ton \cdots$  (2)

In this way, by detecting the full-wave rectification input voltage Vi on the basis of the current flowing through the inductor L1, the necessity of the input voltage detecting circuit 11 can be eliminated, so that the entire circuit can be further simplified.

**[0059]** In Fig. 10, the current in the period Ton is the current flowing through the switching element Q1. Thus, the input voltage Vi can be detected also by providing the current detecting resistor R1 illustrated in Fig. 3 in a path of the current flowing through the switching element Q1 and detecting the current of the Q1 as a voltage signal.

[0060] Additionally, the current flowing through the inductor may be detected by providing a current detecting resistor in a line of the diode bridge B1 connected to the inductor, instead of by using a method for detecting the current on the basis of a dropped voltage of the current detecting resistor R1 illustrated in Fig. 3. Alternatively, the current may be detected by using a current transformer or a Hall element.

<Fourth Embodiment>

45

50

**[0061]** In a fourth embodiment, another example of switching frequency modulation will be described. The circuit configuration of a PFC converter is the same as that illustrated in Fig. 3.

**[0062]** In the first to third embodiments, the switching frequency is continuously modulated in accordance with change in voltage of the AC input power supply. Fig. 11(A) illustrates discrete modulation of a switching frequency. In Fig. 11 (A), the horizontal axis indicates the time whereas the vertical axis indicates the switching frequency. In this example,

a half cycle T of the input voltage Vi is regarded as one cycle, and a switching frequency fsw is discretely changed at regular time intervals. In this example, the switching frequency can stand at five steps of values.

[0063] In such a case where the switching frequency is discretely changed, too, the phase of an input voltage causes the switching frequency to be decreased when an instantaneous value of the input voltage is at the lower limit or at the vicinity of the lower limit and causes the switching frequency to be increased when an instantaneous value of the input voltage is at the upper limit or at the vicinity of the upper limit. Such frequency modulation causes the switching frequency to stand at a plurality of values, so that a peak of EMI noise in the switching frequency and a harmonic frequency thereof is suppressed.

**[0064]** Alternatively, in the discrete frequency modulation, the switching frequency may be switched between two values in accordance with the phase of the input voltage. For example, the switching frequency may be modulated to f1 when the phase of the input voltage is 45° to 135° and to f2 in the other cases.

**[0065]** In the example illustrated in Fig. 11(B), a switching cycle is calculated and is changed in each switching cycle. In this example, the time of a next switching cycle is calculated at the end of a switching cycle, and the on time and off time of the switching element are controlled in accordance with the time.

**[0066]** Fig. 11(C) illustrates an example in which modulation is further performed by using a random component other than a value Va of a modulation signal that synchronizes with an input voltage waveform. The random component Vr randomly fluctuates in a range narrower than a change width of the modulation signal Va that synchronizes with the input voltage. The value Vr is obtained through random number calculation.

**[0067]** Also, the frequency modulation may be performed by using a triangular wave that synchronizes with the input voltage or an exponential function.

**[0068]** With this configuration, EMI noise that occurs at the vicinity of the switching frequency further disperses on a frequency axis, so that an overall peak can be lowered.

15

20

40

55

5

10

<Fifth Embodiment>

**[0069]** A PFC converter according to a fifth embodiment performs shift control on a switching frequency in accordance with a peak value or an effective value of an input voltage. The circuit configuration of the PFC converter is the same as that illustrated in Fig. 3.

**[0070]** Fig. 12 illustrates an example of controlling a switching frequency in accordance with a peak value or an effective value of an input voltage of the PFC converter according to the fifth embodiment. In the first and second embodiments, a description has been given that the switching frequency fc (Vc when represented by a control value) before modulation is constant. In the fifth embodiment, an instantaneous value of an input voltage is controlled in the same manner as that

<sup>25</sup> in the first to fourth embodiments, and an entire modulation range of the switching frequency is shifted in accordance with a peak value or an effective value of the input voltage.

**[0071]** As illustrated in Fig. 12, in a case where the effective value of the AC input power supply is AC 100 V, for example, the switching frequency changes in a frequency range from fsw11 to fsw12. On the other hand, in a case of AC 230 V, the switching frequency changes in a range from fsw21 to fsw22.

- <sup>30</sup> **[0072]** In such control, a peak value or an effective value of the input voltage may be detected first, and fc (vc as a control value) illustrated in Fig. 8 or 9 may be changed in accordance with the peak value or the effective value of the input voltage. Accordingly, a switching loss can be reduced by decreasing the switching frequency in the range where the inductor is not saturated, so that the efficiency can be enhanced.

- 35 <Sixth Embodiment>

**[0073]** Fig. 13 is a circuit diagram of a PFC converter according to a sixth embodiment. In Fig. 13, reference numerals P11 and P12 denote input ports of the PFC converter 102, and reference numerals P21 and P22 denote output ports of the PFC converter 102. An AC input power supply Vac, which is a commercial AC power supply, is input to the input ports P11 and P12, and a load circuit 20 is connected to the output ports P21 and P22.

The load circuit 20 is, for example, a circuit of a DC-DC converter and an electronic apparatus that is supplied with power by the DC-DC converter.

**[0074]** In the example illustrated in Fig. 3, full-wave rectification is performed on the AC input power supply by the diode bridge B1, and then switching of a rectified voltage is performed. In the example illustrated in Fig. 13, switching

- <sup>45</sup> is performed in a bridge circuit. That is, a switching circuit including switching elements Q11 and Q12 that perform switching on an AC voltage input from the AC input power supply Vac and diodes D11 and D12 (body diodes of FETs may be used as D11 and D12 when the FETs are used as Q11 and Q12) is provided on a lower arm, and diodes D13 and D14 are provided on an upper arm. Also, inductors L11 and L12 that pass a current interrupted by the foregoing switching circuit and a smoothing circuit configured using a capacitor C11 that smoothes an output voltage are provided.

- 50 [0075] Also, an input voltage detecting circuit 11 is provided as a voltage detecting circuit for the AC input power supply. Furthermore, a Hall element 14 is provided to detect an AC input current.

[0076] A digital signal processing circuit 13 is constituted by a DSP and controls the PFC converter 102 by performing digital signal processing as described below.

The digital signal processing circuit 13 receives an output signal of the input voltage detecting circuit 11 and detects an AC power supply voltage.

Also, the digital signal processing circuit 13 receives an output signal of the output voltage detecting circuit 12 and detects an output voltage.

Also, the digital signal processing circuit 13 detects an input current from an output signal of the Hall element 14.

**[0077]** Furthermore, the digital signal processing circuit 13 turns on/off the switching elements Q11 and Q12 at a predetermined switching frequency.

**[0078]** A circuit operation caused by switching control of the switching elements Q11 and Q12 performed by the digital signal processing circuit 13 is as follows.

<sup>5</sup> **[0079]** First, the digital signal processing circuit 13 turns on both of the switching elements Q11 and Q12. Accordingly, a current flows through a path Vac  $\rightarrow$  L11  $\rightarrow$  Q11  $\rightarrow$  Q12  $\rightarrow$  L12  $\rightarrow$  Vac, or in the opposite direction, so that excitation energy is accumulated in the inductors L11 and L12.

**[0080]** After that, the digital signal processing circuit 13 turns off both of the switching elements Q11 and Q12. Accordingly, a current flows through a path Vac  $\rightarrow$  L11  $\rightarrow$  D13  $\rightarrow$  C11 (20)  $\rightarrow$  D12  $\rightarrow$  L12  $\rightarrow$  Vac, or a path Vac  $\rightarrow$  L12  $\rightarrow$  C14 (20)  $\rightarrow$  D12  $\rightarrow$  L12  $\rightarrow$  Vac, or a path Vac  $\rightarrow$  L12  $\rightarrow$  Vac,

<sup>10</sup> D14  $\rightarrow$ C11 (20)  $\rightarrow$  D11  $\rightarrow$  L11  $\rightarrow$  Vac (at this time, Q11 or Q12 connected in parallel to D11 or D12 that is in a continuity state may be in an on state), whereby the excitation energy is emitted from the inductors L11 and L12 and the capacitor C11 is charged with voltage.

**[0081]** In this way, full-wave rectification and switching are performed on an AC input voltage by the bridge including the switching elements Q11 and Q12 and the diodes D11, D12, D13, and D14. Also, a chopper operation is performed by the inductors L11 and L12 and the foregoing bridge.

**[0082]** The present invention can also be applied to the PFC converter configured to perform switching by using such a bridge circuit.

#### 20 Claims

- 1. A PFC converter including at least two switching circuits that perform switching on an AC voltage input from an AC input power supply, an inductor that passes a current interrupted by the switching circuits, and a smoothing circuit that smoothes an output voltage in a stage after the inductor, the PFC converter comprising:

- 25

30

15

phase detecting means for detecting a phase of a voltage of the AC input power supply; and switching frequency modulating means for modulating a switching frequency of the switching circuits in accordance with a phase of a voltage waveform of the AC input power supply, a half cycle of the voltage waveform of the AC input power supply being one cycle.

2. A PFC converter including a rectifier circuit that performs full-wave rectification on an AC input power supply, a switching circuit that performs switching on an output voltage of the rectifier circuit, an inductor that passes a current interrupted by the switching circuit, and a smoothing circuit that smoothes the output voltage in a stage after the inductor, the PFC converter comprising:

35

phase detecting means for detecting a phase of a voltage of the AC input power supply; and switching frequency modulating means for modulating a switching frequency of the switching circuit in accordance with a phase of a voltage waveform of the AC input power supply, a half cycle of the voltage waveform of the AC input power supply being one cycle.

40

45

- 3. The PFC converter according to Claim 1 or 2, wherein, on the basis of the phase of the voltage of the AC input power supply, the switching frequency modulating means decreases the switching frequency of the switching circuit when an instantaneous value of the voltage of the AC input power supply is at a lower limit or at the vicinity of the lower limit, and increases the switching frequency of the switching circuit when the instantaneous value of the voltage of the voltage of the vicinity of the government of the voltage of the AC input power supply is at an upper limit or at the vicinity of the upper limit.

- 4. The PFC converter according to Claims 1 to 3, wherein the switching frequency modulating means is means for obtaining a peak value or an effective value of an input voltage on the basis of an instantaneous value obtained through sampling of the voltage of the AC input power supply and shifting a modulation range of the switching frequency of the switching circuit to a low frequency side as the peak value or the effective value is higher.

- **5.** The PFC converter according to any of Claims 1 to 4, wherein the phase detecting means includes a waveform shaping circuit that shapes a waveform of a voltage signal of the AC input power supply to generate a substantially-rectangular-wave signal, and means for detecting a rise and/or fall time of the rectangular-wave signal.

- 55

50

6. The PFC converter according to any of Claims 1 to 4, wherein the phase detecting means samples a voltage signal of the AC input power supply and detects at least one of a time when an instantaneous value of the voltage signal reaches a peak, a time when the instantaneous value is a minimum, and a time when the instantaneous value is a

#### predetermined value.

| 5  |  |  |  |

|----|--|--|--|

| 10 |  |  |  |

| 15 |  |  |  |

| 20 |  |  |  |

| 25 |  |  |  |

| 30 |  |  |  |

| 35 |  |  |  |

| 40 |  |  |  |

| 45 |  |  |  |

| 50 |  |  |  |

| 55 |  |  |  |

FIG. 3

(C)

FIG. 12 AC230V AC100V INPUT VOLTAGE Vac ≁t AC100V fsw12 fsw22 fsw11' SWITCHING FREQUENCY fsw fsw21<sup>/</sup> AC230V ł ≁t FIG. 13 <u>102</u>

|                                                                                                                                                                         | INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                           | International application No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PCT/JP2008/056772                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                         | CATION OF SUBJECT MATTER<br>(2006.01)i                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| According to Inte                                                                                                                                                       | ernational Patent Classification (IPC) or to both nationa                                                                                                                                                                                                                                                                                                                                                                                                             | al classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| B. FIELDS SE                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Minimum docun<br>H02M3/155                                                                                                                                              | nentation searched (classification system followed by cl                                                                                                                                                                                                                                                                                                                                                                                                              | lassification symbols)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Jitsuyo                                                                                                                                                                 | Shinan Koho 1922-1996 Ji                                                                                                                                                                                                                                                                                                                                                                                                                                              | ent that such documents are included in the fields searched<br>tsuyo Shinan Toroku Koho 1996-2008<br>proku Jitsuyo Shinan Koho 1994-2008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                         | pase consulted during the international search (name of                                                                                                                                                                                                                                                                                                                                                                                                               | data base and, where practicable, search terms used)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                         | JTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Category*                                                                                                                                                               | Citation of document, with indication, where ap                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Y                                                                                                                                                                       | JP 2004-282958 A (Sanken Ele<br>07 October, 2004 (07.10.04),<br>Par. Nos. [0025] to [0038]; I<br>(Family: none)                                                                                                                                                                                                                                                                                                                                                       | ectric Co., Ltd.), 1-6<br>Figs. 1 to 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Y                                                                                                                                                                       | JP 2001-145358 A (Sanyo Elec<br>25 May, 2001 (25.05.01),<br>Par. Nos. [0040] to [0048]; I<br>(Family: none)                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Y                                                                                                                                                                       | JP 2000-69752 A (Matsushita<br>Ltd.),<br>03 March, 2000 (03.03.00),<br>Par. No. [0008]<br>(Family: none)                                                                                                                                                                                                                                                                                                                                                              | Electric Works, 4-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| × Eurther do                                                                                                                                                            | ocuments are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                     | Saa patent family annay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| * Special cate<br>*A document de<br>be of particu<br>"E" earlier applie<br>date<br>*L" document w<br>cited to esta<br>special reaso<br>*O" document pr<br>priority date | gories of cited documents:<br>fining the general state of the art which is not considered to<br>lar relevance<br>cation or patent but published on or after the international filing<br>which may throw doubts on priority claim(s) or which is<br>blish the publication date of another citation or other<br>n (as specified)<br>ferring to an oral disclosure, use, exhibition or other means<br>iblished prior to the international filing date but later than the | <ul> <li>See patent family annex.</li> <li>"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</li> <li>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</li> <li>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is acombined with one or more other such documents, such combination being obvious to a person skilled in the art</li> <li>"&amp;" document member of the same patent family</li> <li>Date of mailing of the international search report</li> </ul> |

| 01 July                                                                                                                                                                 | recompletion of the international search<br>y, 2008 (01.07.08)<br>ng address of the ISA/                                                                                                                                                                                                                                                                                                                                                                              | 15       July, 2008 (15.07.08)         Authorized officer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                         | se Patent Office                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Facsimile No.                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Telephone No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Form PCT/ISA/210 (second sheet) (April 2007)

| INTERNATIONAL | SEARCH REPORT |

|---------------|---------------|

|---------------|---------------|

## ORT International application No.

I

|                   |                                                                                                                              | PCT/JP2      | 008/056772            |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|

| C (Continuation). | DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                          |              |                       |

| Category*         | Citation of document, with indication, where appropriate, of the relev                                                       | ant passages | Relevant to claim No. |

| Y                 | JP 2001-161069 A (Hitachi, Ltd.),<br>12 June, 2001 (12.06.01),<br>Par. Nos. [0025] to [0026]; Figs. 1 to 2<br>(Family: none) |              | 5                     |

| У                 | (Family: none)<br>JP 2007-46972 A (Hitachi, Ltd.),<br>22 February, 2007 (22.02.07),<br>Par. No. [0003]<br>(Family: none)     |              | 6                     |

|                   |                                                                                                                              |              |                       |

|                   |                                                                                                                              |              |                       |

Form PCT/ISA/210 (continuation of second sheet) (April 2007)

#### **REFERENCES CITED IN THE DESCRIPTION**

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

#### Patent documents cited in the description

• JP 2004282958 A [0012]