# (11) **EP 2 187 514 A1**

(12)

# EUROPEAN PATENT APPLICATION

published in accordance with Art. 153(4) EPC

(43) Date of publication: 19.05.2010 Bulletin 2010/20

(21) Application number: 08751756.1

(22) Date of filing: 19.05.2008

(51) Int Cl.: **H02M 3/28** (2006.01) **G05F 3/26** (2006.01)

(86) International application number: PCT/JP2008/001238

(87) International publication number: WO 2008/146463 (04.12.2008 Gazette 2008/49)

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MT NL NO PL PT RO SE SI SK TR

**Designated Extension States:**

AL BA MK RS

(30) Priority: 22.05.2007 JP 2007134858

(71) Applicant: Panasonic Corporation Kadoma-shi Osaka 571-8501 (JP) (72) Inventors:

NISHIHARA, Hideki

Osaka-shi, Osaka 540-6207 (JP)

KOMATSU, Akeyuki

Osaka-shi, Osaka 540-6207 (JP)

(74) Representative: Grünecker, Kinkeldey, Stockmair & Schwanhäusser Anwaltssozietät Leopoldstrasse 4 80802 München (DE)

### (54) SWITCHING POWER SUPPLY DEVICE

(57) An object of the present invention is to provide a switching power supply which can stably determine whether an overcurrent occurs or not on the secondary side. A sample voltage corresponding to a load current value detected by detection resistors R7 and R8 is compared with a reference voltage by an input-side transistor

Q4 and an output-side transistor Q3 which compose a first current mirror circuit 14, so that it is possible to determine whether an overcurrent occurs or not. Moreover, a current passing through the output circuit of the transistor Q3 is temperature-compensated by a second current mirror circuit 17 made up of transistors Q6 and Q5.

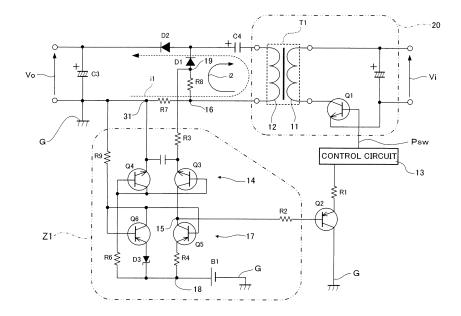

FIG. 1

#### Technical Field

[0001] The present invention relates to a switching power supply which outputs the secondary-side voltage of a voltage conversion section after rectifying and smoothing the voltage and controls switching on the primary side of the voltage conversion section according to a detected load current to perform overcurrent protection.

1

#### Background Art

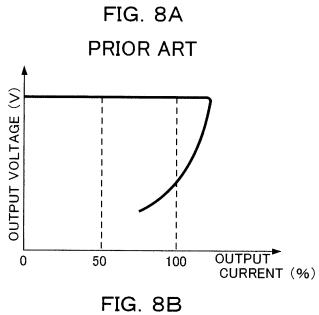

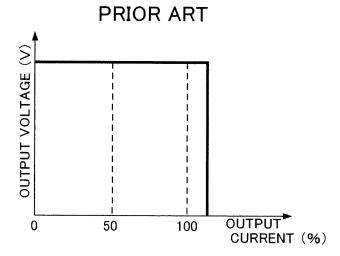

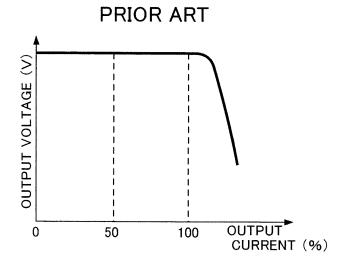

[0002] In a power supply, an overcurrent protection circuit is provided for limiting a load current to protect the power supply and a load from an overload. Generally, overcurrent protection is broadly divided into three methods shown in FIGS. 8(a), 8(b) and 8(c).

[0003] In FIG. 8(a), when an output current exceeds the set upper limit, an output voltage decreases and the output current is reduced to provide protection. This method is called Fold-back Type Drooping Characteristic based on the pattern of the correlation characteristic of the output voltage and the output current.

[0004] In FIG. 8(b), when an output current exceeds the set upper limit, the output current is immediately reduced to provide protection. This method is called "pendent character" based on the pattern of the correlation characteristic of an output voltage and the output current. In FIG. 8(c), when an output current exceeds the set upper limit, the output current is reduced at a constant power to provide protection. This method is called an inverted V-shaped characteristic based on the pattern of the correlation characteristic of an output voltage and the output current.

[0006] In the case of a switching power supply for detection for overcurrent protection only on the primary side of a transformer, an overcurrent protection set value is deviated by a change of an input voltage, resulting in low accuracy.

[0007] In the case of the overcurrent protection characteristic of FIG. 8(c), it is possible to protect a switching transistor on the primary side of a transformer but a current increases in a diode for rectification on the secondary side of the transformer even under protection, which is disadvantageous to overcurrent protection (described in Patent Document 1 and so on).

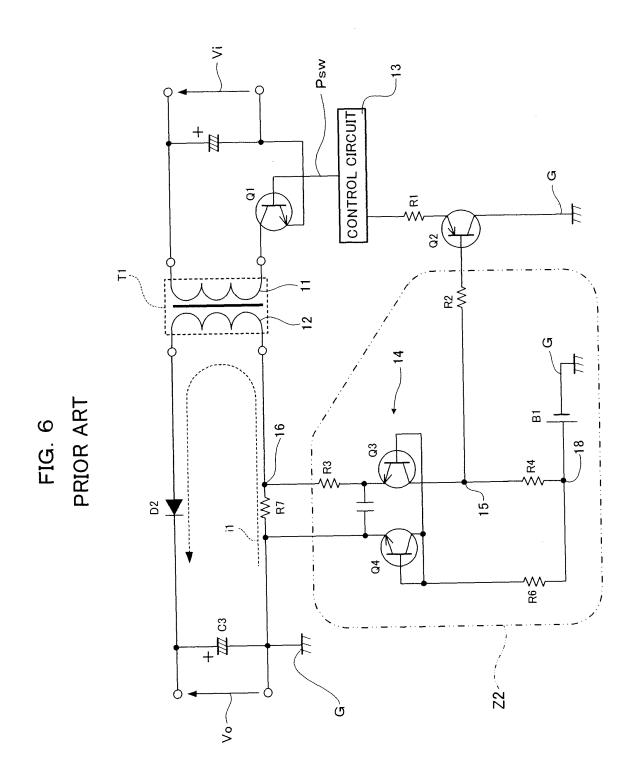

[0008] As compared to FIG. 8(c), when a load current is detected on the secondary side of a transformer T1 as shown in FIG. 6, satisfactory overcurrent protection can be expected.

[0009] In FIG. 6, to a primary winding 11 of the transformer T1, an input DC voltage Vi is applied through a switching transistor Q1 acting as a series control element. The frequency of a pulse signal Psw applied to the base of the switching transistor Q1 is controlled by a con-

[0010] The output of a secondary winding 12 of the

transformer T1 is half-wave rectified by a diode D2 and the output is smoothed by a capacitor C3 to obtain an output voltage Vo. A load current i1 is detected by a detection resistor R7 disposed in a secondary-side circuit. [0011] An error amplifier Z2 for supplying information to the control circuit 13 according to a detected voltage of the detection resistor R7 is configured as follows:

[0012] A current mirror circuit 14 is made up of an inputside transistor Q4 and an output-side transistor Q3. Between a reference potential G and the base of the transistor Q4 whose base and collector are connected to each other, a voltage source B1 is connected via a resistor R6. The emitter of the transistor Q4 is connected to the detection resistor R7 on the side of the reference notential G

[0013] The base of the transistor Q3 is connected to the base of the transistor Q4 and the collector of the transistor Q3 is connected to the junction point of the resistor R6 and the voltage source B1 via a resistor R4. The emitter of the transistor Q3 is connected to a junction point 15 of the detection resistor R7 and the secondary winding 12 via a resistor R3.

[0014] A junction point 16 of the collector of the transistor Q3 and the resistor R4 is connected to the base of an output transistor Q2 via a resistor R2. The emitter and collector of the transistor Q2 are interposed between one end of a resistor R1 having the other end connected to the control circuit 13 and the reference potential G.

In the error amplifier Z2 configured thus, the resistor R4 for determining a reference voltage is connected to the collector of the transistor Q3 and the amplification degree of the error amplifier Z2 is determined by a ratio between the resistance values of the resistors R3 and R4.

[0016] When the load current i1 increases, a voltage drop across the detection resistor R7 increases, the voltage of the junction point 16 of the resistor R7 and the resistor R3 decreases, and the collector current of the transistor Q3 increases. Accordingly, a potential decreases on the junction point 15 of the collector of the transistor Q3, the base current of the output transistor Q2 increases, and the load current i1 increases to a set value. At this point, the resistor R1 connected to the control circuit 13 is connected to the reference potential G via the output transistor Q2 and the switching frequency of the primary side is controlled to achieve overcurrent protection of "Fold-back Type Drooping Characteristic" shown in FIG. 8(a).

Patent Document 1: Japanese Patent Laid-Open No. 2004-215394

Disclosure of the Invention

Problems to be Solved by the Invention

[0017] In the circuit configuration of FIG. 6, however, the amplification degree of the error amplifier Z2 is

40

50

changed by a temperature change (temperature characteristic) of the resistor R4, so that the reference voltage may be changed and the set value of overcurrent protection may be deviated.

[0018] A current passing through the transistor Q3 is larger than a current passing through the transistor Q4. When a current passing through i1 increases, a voltage difference across the detection resistor R7 increases. When the load current i1 increases and a current difference increases between the value of current passing through the transistor Q3 and the value of current passing through the input-side transistor Q4, a temperature difference occurs between the transistor Q3 and the transistor Q4. In other words, the set value of overcurrent protection may vary between the absence of a temperature difference between the transistor Q3 and the inputside transistor Q4 in, for example, a cold state immediately after turn-on and the presence of a large temperature difference between the transistor Q3 and the transistor Q4 after aging.

**[0019]** An object of the present invention is to provide a switching power supply which can stably judge the occurrence of overcurrent on the secondary side of a voltage conversion section.

#### Means for Solving the Problems

[0020] A switching power supply according to a first aspect of the present invention for outputting the secondary-side voltage of a voltage conversion section after rectifying and smoothing the voltage, and controlling switching on the primary side of the voltage conversion section according to a detected load current to perform overcurrent protection, the switching power supply including: a detection resistor for detecting a load current on the secondary side of the voltage conversion section; a first current mirror circuit made up of a first transistor of an input side and a second transistor of an output side; and a second current mirror circuit made up of a third transistor of the input side and a fourth transistor of the output side, wherein the detected voltage of the detection resistor is applied between one end of the first transistor and one end of the second transistor, the fourth transistor fed with a current set by the third transistor is interposed between the second transistor and a reference potential, and switching on the primary side of the voltage conversion section is controlled according to the potential of the junction point of the second transistor and the fourth transistor to perform overcurrent protection.

**[0021]** A switching power supply according to a second aspect of the present invention, in the first aspect, wherein the junction point of the second transistor and the fourth transistor and the base of the second transistor are connected via a resistor.

**[0022]** A switching power supply according to a third aspect of the present invention, in one of the first and second aspects, wherein a circuit for rectifying and smoothing the secondary-side voltage of the voltage con-

version section is a half-wave voltage doubling rectifier circuit in which a first diode has an anode connected to one end of the output of the voltage conversion section, the first diode has a cathode connected to the anode of a second diode, the junction point of the first diode and the second diode is connected to the other end of the output of the voltage conversion section via a capacitor, and an output voltage from the cathode of the second diode and the one end of the output of the voltage conversion section is smoothed as an output voltage, the detection resistor for detecting the load current on the secondary side of the voltage conversion section is made up of a first detection resistor interposed between the one end of the output of the voltage conversion section and the anode of the first diode, and a second detection resistor interposed between the first detection resistor and the anode of the first diode, and a voltage across the first detection resistor and the second detection resistor which are connected in series is applied between the one 20 end of the first transistor and the one end of the second transistor.

#### Advantage of the Invention

[0023] According to the present invention, a second current mirror circuit is provided to perform temperature compensation on a first current mirror circuit, achieving a stable overcurrent protection operation.

30 Brief Description of the Drawings

#### [0024]

35

40

45

50

55

FIG. 1 is a structural diagram showing a switching power supply according to a first embodiment of the present invention;

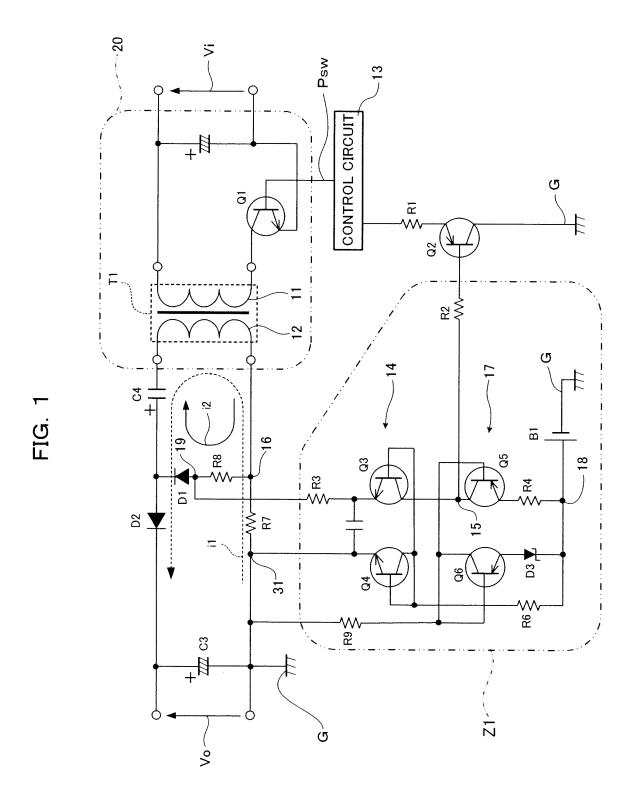

FIG. 2 is a structural diagram showing a switching power supply according to a second embodiment of the present invention;

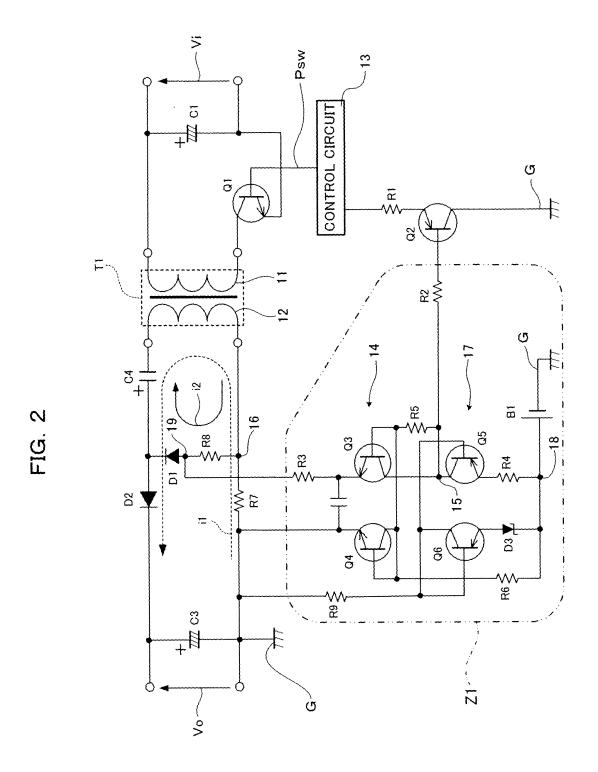

FIG. 3 is a structural diagram showing a switching power supply according to a third embodiment of the present invention;

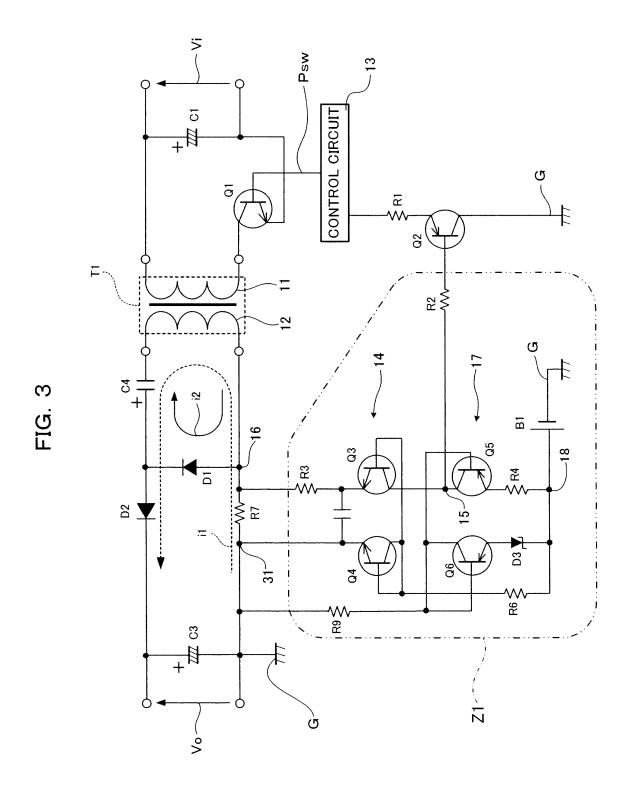

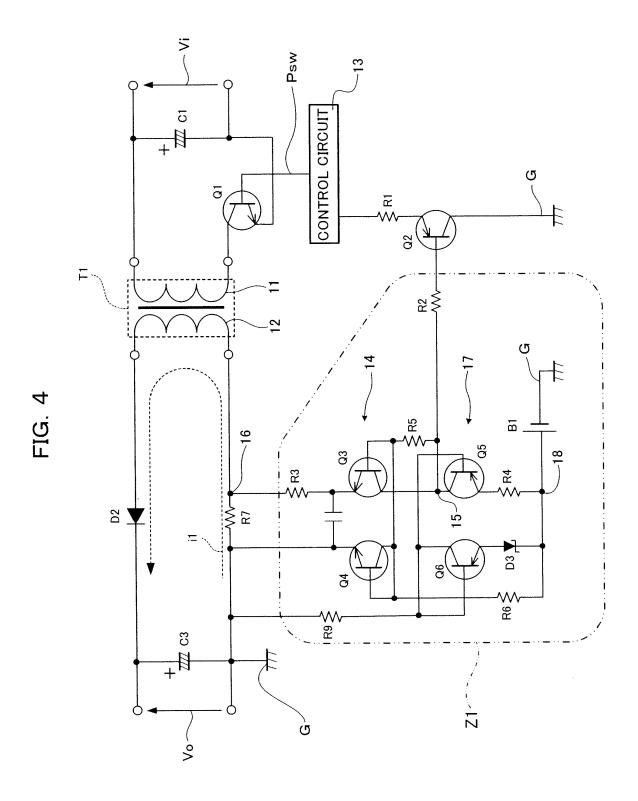

FIG. 4 is a structural diagram showing a switching power supply according to a fourth embodiment of the present invention;

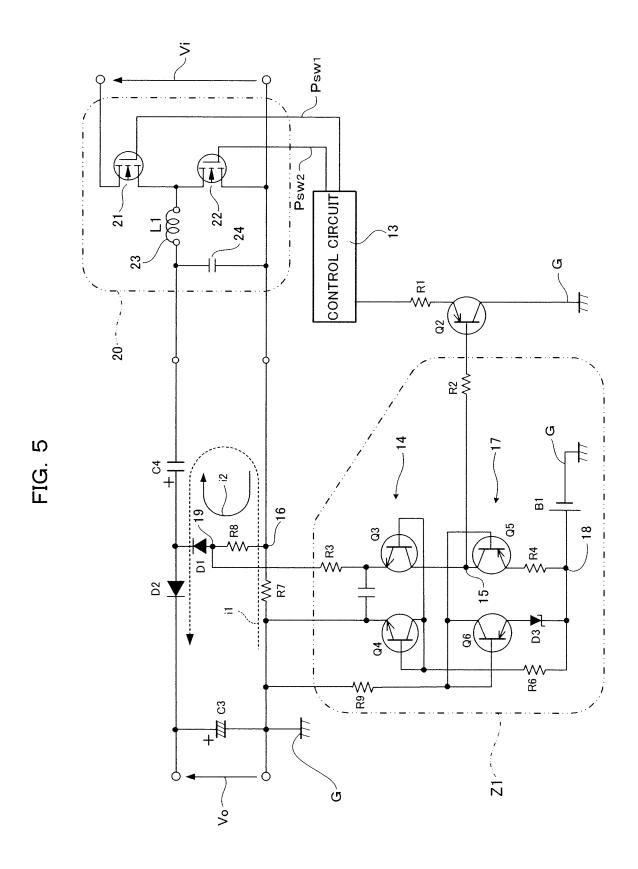

FIG. 5 is a structural diagram showing a switching power supply according to a fifth embodiment of the present invention;

FIG. 6 is a structural diagram showing a switching power supply of the prior art;

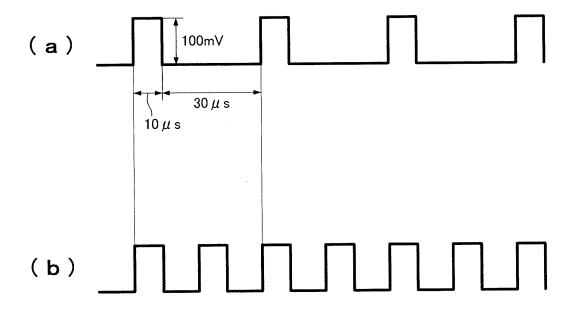

FIG. 7 is a detected waveform chart of the main parts of the third embodiment and the first embodiment according to the present invention; and

FIG. 8 is an explanatory drawing showing a typical overcurrent protection method.

20

40

Best Mode for Carrying Out the Invention

**[0025]** Referring to FIGS. 1 to 5, embodiments of the present invention will be described below.

(First Embodiment)

**[0026]** FIG. 1 shows a switching power supply in which a voltage conversion section 20 is made up of a transformer T1 and the output voltage of a secondary winding 12 of the transformer T1 is subjected to half-wave voltage doubling rectification by a diode D1, a diode D2, and a capacitor C4. As compared with the switching power supply of half-wave rectification shown in FIG. 6, a current mirror circuit 17 made up of a transistor Q6 and a transistor Q5 is provided in addition to the diode D1, a detection resistor R8, and the capacitor C4.

[0027] To be specific, to a primary winding 11 of the transformer T1, an input DC voltage Vi is applied through a switching transistor Q1 acting as a series control element. The frequency of a pulse signal Psw applied to the base of the switching transistor Q1 is controlled by a control circuit 13.

**[0028]** The output of the secondary winding 12 of the transformer T1 is subjected to voltage doubling rectification by the diodes D1 and D2 and the capacitor C4, the output is smoothed by a capacitor C3, and an output DC voltage Vo is outputted.

**[0029]** A half-cycle current i2 for charging the capacitor C4 through the diode D1 by an output voltage E of the secondary wiring 12 of the transformer T1 is detected by the detection resistor R8 connected in series with the diode D1. In the subsequent half cycle, a load current i1 for charging the capacitor C3 through the diode D2 by the output voltage E of the secondary winding 12 of the transformer T1 and the terminal voltage of the capacitor C4 is passed, so that an output DC voltage Vo of  $2 \cdot E$  is generated across the capacitor C3. The load current i1 is detected by a detection resistor R7.

**[0030]** The capacitor C3 has one end connected to a reference potential G and the secondary winding 12 of the transformer T1 has one end connected to the reference potential G via the detection resistor R7. The detection resistor R8 having one end connected to the anode of the diode D1 has the other end connected to a junction point 16 of the detection resistor R7 and one end of the secondary winding 12.

**[0031]** An error amplifier Z1 for supplying information to the control circuit 13 according to the detected voltages of the detection resistors R7 and R8 is configured as follows:

**[0032]** A first current mirror circuit 14 is made up of an NPN transistor Q4 and an NPN transistor Q3. The base and collector of the transistor Q4 are connected to each other and are connected to the reference potential G via a resistor R6 and a voltage source B1. The emitter of the transistor Q4 is connected to the reference potential.

[0033] The base of the transistor Q3 is connected to

the base of the transistor Q4 and the collector of the transistor Q3 is connected to a junction point 18 of the resistor R6 and the voltage source B1 via the second current mirror circuit 17.

[0034] The second current mirror circuit 17 is made up of the PNP transistor Q6 and the PNP transistor Q5. The base and collector of the transistor Q6 are connected to each other and are connected to the reference potential G via a resistor R9. The emitter of the transistor Q6 is connected to the junction point 18 of the resistor R6 and the voltage source B1 via a constant voltage diode D3. The base of the transistor Q5 is connected to the base of the transistor Q6, the collector of the transistor Q5 is connected to the collector of the transistor Q3, and the emitter of the transistor Q5 is connected to the junction point 18 of the resistor R6 and the voltage source B1 via a resistor R4.

**[0035]** A junction point 15 of the collector of the transistor Q3 and the collector of the transistor Q5 is connected to the base of an output transistor Q2 via a resistor R2. The emitter and collector of the transistor Q2 are interposed between one end of a resistor R1 having the other end connected to the control circuit 13 and the reference potential G.

**[0036]** The emitter of the transistor Q3 is connected to a junction point 19 of the anode of the diode D1 and the detection resistor R8 via a resistor R3.

**[0037]** With this configuration, the collector current of the transistor Q5 is expressed as follows:

$$(Vz + Q6Vbe - Q5Vbe)/r4$$

where Vz is the Zener voltage of the constant voltage diode D3, "Q6Vbe" is a voltage between the base and emitter of the transistor Q6, "Q5Vbe" is a voltage between the base and emitter of the transistor Q5, and "r4" is the resistance value of the resistor R4. It is possible to obtain a constant current not affecting a temperature change, achieving a stable overcurrent protection operation.

**[0038]** Further, in addition to the detection resistor R7, the terminal voltage of the series circuit of the detection resistor R7 and the detection resistor R8 is used as the sample signal of the error amplifier Z1. An overcurrent can be detected not only from one cycle but from both cycles of the load current i1 and the load current i2, so that the control circuit 13 can be controlled with higher accuracy.

**[0039]** FIG. 7 shows specific examples when the single detection resistor is used and the two detection resistors are used. In this case, an operation is performed with an input of a 24 V DC voltage and an output of 240 V DC voltage and 2.5 A.

**[0040]** FIG. 7(a) shows a detected voltage waveform when only the detection resistor R7 is used as shown in FIG. 3. The voltage waveform is obtained between a junc-

tion point 31 of the detection resistor R7 and the reference potential G and the junction point 16 of the detection resistor R7 and the secondary side of the transformer T1. **[0041]** FIG. 7(b) shows a detected voltage waveform when the detection resistor R7 and the detection resistor R8 are used as shown in FIG. 1. The voltage waveform is obtained between the junction point 31 of the detection resistor R7 and the reference potential G and the junction point 19 of the detection resistor R8 and the diode D1.

[0042] When the terminal voltage of the series circuit of the detection resistor R7 and the detection resistor R8 is used thus as the sample signal of the error amplifier Z1, an overcurrent is detected from both cycles of the load current i1 and the load current i2. Thus the control circuit 13 can be accurately controlled as compared with the case where only the detection resistor R7 is used.

#### (Second Embodiment)

**[0043]** FIG. 2 shows a second embodiment of the present invention.

**[0044]** FIG. 2 is different from FIG. 1 only in that the base of a transistor Q3 is connected to the collector of a transistor Q5 via a resistor R5.

[0045] In other words, the amplification degree of an error amplifier Z1 is determined by the resistor R5 and a resistor R3. Since one end of the resistor R5 has a constant current not affecting a temperature change (temperature characteristic), the bases of a transistor Q4 and the transistor Q3 which are connected to the other end of the resistor R5 have the same potential. Thus substantially the same current passes through the transistor Q3 and the transistor Q4, thereby reducing a deviation of the set value of overcurrent protection.

#### (Third Embodiment)

**[0046]** FIG. 3 shows a third embodiment of the present invention.

[0047] FIG. 3 shows a switching power supply using a rectification method of half-wave voltage doubling rectification as in FIG. 1 illustrating the first embodiment. FIG. 3 is different from FIG. 1 only in that the terminal voltage of a detection resistor R7 is used as the sample signal of an error amplifier Z1. In this case, a control circuit 13 is controlled by detecting an overcurrent only from one cycle. Thus it is possible to achieve a stable overcurrent protection operation not affecting a temperature change as compared with the prior art, though the performance of overcurrent protection with a varying load is not as satisfactory as the performance of the first embodiment. The overcurrent protection can be similarly performed also in FIG. 2 illustrating the second embodiment.

#### (Fourth Embodiment)

[0048] FIG. 4 shows a fourth embodiment of the

present invention.

**[0049]** FIG. 4 shows a switching power supply using a rectification method of half-wave rectification. FIG. 4 is different from FIG. 2 illustrating the second embodiment only in that the terminal voltage of a detection resistor R7 is used as the sample signal of an error amplifier Z1.

(Fifth Embodiment)

**[0050]** FIG. 5 shows a fifth embodiment of the present invention.

[0051] In FIG. 5, a voltage conversion section 20 is made up of a DC-DC converter including MOS transistors 21 and 22, an inductor 23, and a capacitor 24. FIG. 5 is different from FIG. 1 illustrating the first embodiment only in that pulse signals Psw1 and Psw2 applied to the gates of the MOS transistors 21 and 22 from a control circuit 13 are controlled to control switching on the primary side and perform voltage conversion and overcurrent protection. The overcurrent protection can be similarly performed also in the second to fourth embodiments.

[0052] In the foregoing embodiments, the first current mirror circuit 14 is made up of the NPN transistors Q3 and Q4 of a first conductivity type and the second current mirror circuit 17 is made up of the PNP transistors Q5 and Q6 of a second conductivity type. The first current mirror circuit 14 may be made up of PNP transistors Q3 and Q4 and the second current mirror circuit 17 may be made up of NPN transistors Q5 and Q6.

#### Industrial Applicability

**[0053]** The present invention is particularly useful as a power supply having a large load current of several tens amperes and used for equipment in which the accuracy of overcurrent protection setting is highly valued. To be specific, the present invention is assembled as a power supply for an inverter, a motor drive and the like, so that variations in judgment of overcurrent due to a temperature can be eliminated. Thus the present invention can contribute to a more reliable operation and higher safety of assembled equipment.

#### 45 Claims

50

55

30

A switching power supply for outputting a secondaryside voltage of a voltage conversion section after rectifying and smoothing the voltage, and controlling switching on a primary side of the voltage conversion section according to a detected load current to perform overcurrent protection,

the switching power supply comprising:

- a detection resistor for detecting a load current on a secondary side of the voltage conversion section;

- a first current mirror circuit made up of a first

transistor of an input side and a second transistor of an output side; and a second current mirror circuit made up of a third transistor of the input side and a fourth transistor of the output side, wherein a detected voltage of the detection resistor is applied between one end of the first transitor.

wherein a detected voltage of the detection resistor is applied between one end of the first transistor and one end of the second transistor, the fourth transistor fed with a current set by the third transistor is interposed between the second transistor and a reference potential, and switching on the primary side of the voltage conversion section is controlled according to a potential of a junction point of the second transistor and the fourth transistor to perform overcurrent protection.

2. The switching power supply according to claim 1, wherein the junction point of the second transistor and the fourth transistor and a base of the second transistor are connected via a resistor.

3. The switching power supply according to one of claims 1 and 2, wherein a circuit for rectifying and smoothing the secondary-side voltage of the voltage conversion section is a half-wave voltage doubling rectifier circuit in which a first diode has an anode connected to one end of an output of the voltage conversion section, the first diode has a cathode connected to an anode of a second diode, a junction point of the first diode and the second diode is connected to an other end of a secondary winding of a transformer via a capacitor, and an output voltage from a cathode of the second diode

an output voltage from a cathode of the second diode and the one end of the output of the voltage conversion section is smoothed as an output voltage, the detection resistor for detecting the load current on the secondary side of the voltage conversion section is made up of:

a first detection resistor interposed between the

one end of the output of the voltage conversion section and the anode of the first diode, and a second detection resistor interposed between the first detection resistor and the anode of the first diode, and a voltage across the first detection resistor and the second detection resistor which are connect-

the second detection resistor which are connected in series is applied between the one end of the first transistor and the one end of the second transistor.

FIG. 7

rid. ob

FIG. 8C

## EP 2 187 514 A1

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2008/001238

|                                                                                                                                                                                 |                                                                                                                  | ,                                                                                                                                                                                                                                                                         | 000,00==00                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                                                                                                                                                                 | ATION OF SUBJECT MATTER 2006.01)i, G05F3/26(2006.01)i                                                            |                                                                                                                                                                                                                                                                           |                                              |

| According to Inte                                                                                                                                                               | ernational Patent Classification (IPC) or to both nationa                                                        | ıl classification and IPC                                                                                                                                                                                                                                                 |                                              |

| B. FIELDS SE                                                                                                                                                                    | ARCHED                                                                                                           |                                                                                                                                                                                                                                                                           |                                              |

| Minimum docum<br>H02M3/28,                                                                                                                                                      | nentation searched (classification system followed by cl ${\tt G05F3/26}$                                        | assification symbols)                                                                                                                                                                                                                                                     |                                              |

|                                                                                                                                                                                 |                                                                                                                  |                                                                                                                                                                                                                                                                           |                                              |

| Jitsuyo                                                                                                                                                                         |                                                                                                                  | ent that such documents are included in th<br>tsuyo Shinan Toroku Koho<br>roku Jitsuyo Shinan Koho                                                                                                                                                                        | ne fields searched<br>1996–2008<br>1994–2008 |

| Electronic data b                                                                                                                                                               | ase consulted during the international search (name of                                                           | data base and, where practicable, search                                                                                                                                                                                                                                  | terms used)                                  |

| C. DOCUMEN                                                                                                                                                                      | ITS CONSIDERED TO BE RELEVANT                                                                                    |                                                                                                                                                                                                                                                                           |                                              |

| Category*                                                                                                                                                                       | Citation of document, with indication, where app                                                                 | propriate, of the relevant passages                                                                                                                                                                                                                                       | Relevant to claim No.                        |

| У                                                                                                                                                                               | JP 7-248342 A (Nippon Motoro<br>26 September, 1995 (26.09.95)<br>Par. Nos. [0016] to [0026]; I<br>& US 5559500 A | ),                                                                                                                                                                                                                                                                        | 1,2                                          |

| Y<br>A                                                                                                                                                                          | JP 9-37547 A (Sharp Corp.),<br>07 February, 1997 (07.02.97),<br>Par. Nos. [0003] to [0005]; F<br>(Family: none)  |                                                                                                                                                                                                                                                                           | 1,2                                          |

| Further documents are listed in the continuation of Box C. See patent family annex.                                                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                           |                                              |

| "A" document defining the general state of the art which is not considered to be of particular relevance                                                                        |                                                                                                                  | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention "X" document of particular relevance; the claimed invention cannot be |                                              |

| date "L" document which may throw doubts on priority claim(s) or which is                                                                                                       |                                                                                                                  | considered novel or cannot be conside<br>step when the document is taken alone                                                                                                                                                                                            |                                              |

| cited to esta                                                                                                                                                                   | blish the publication date of another citation or other<br>n (as specified)                                      | "Y" document of particular relevance; the cla<br>considered to involve an inventive ste                                                                                                                                                                                   |                                              |

| "O" document referring to an oral disclosure, use, exhibition or other means document published prior to the international filing date but later than the priority date claimed |                                                                                                                  | combined with one or more other such documents, such combination being obvious to a person skilled in the art  "&" document member of the same patent family                                                                                                              |                                              |

| Date of the actual completion of the international search 12 August, 2008 (12.08.08)                                                                                            |                                                                                                                  | Date of mailing of the international search report 19 August, 2008 (19.08.08)                                                                                                                                                                                             |                                              |

| Name and mailing address of the ISA/<br>Japanese Patent Office                                                                                                                  |                                                                                                                  | Authorized officer                                                                                                                                                                                                                                                        |                                              |

Facsimile No.

Form PCT/ISA/210 (second sheet) (April 2007)

## EP 2 187 514 A1

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2008/001238

| (Continuation). DOCUMENTS CONSIDERED TO BE RELEVAN                                                                                                                 |                                                                                                                                                                                                                                                                 |                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Category* Citation of document, with indication, where app                                                                                                         |                                                                                                                                                                                                                                                                 | Relevant to claim No |

| Y Microfilm of the specification annexed to the request of Jap Model Application No. 149868, No. 72678/1990) (Sanyo Electric Co., Ltd.), 04 June, 1990 (04.06.90), | Microfilm of the specification and drawings annexed to the request of Japanese Utility Model Application No. 149868/1988 (Laid-open No. 72678/1990) (Sanyo Electric Co., Ltd.), 04 June, 1990 (04.06.90), Description, page 5, line 1 to page 7, line 3; Fig. 1 |                      |

| P,A JP 2007-163376 A (Matsushita Ltd.), 28 June, 2007 (28.06.07), Par. Nos. [0017] to [0027]; F (Family: none)                                                     |                                                                                                                                                                                                                                                                 | 1-3                  |

Form PCT/ISA/210 (continuation of second sheet) (April 2007)

## EP 2 187 514 A1

#### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

## Patent documents cited in the description

• JP 2004215394 A [0016]