# (11) EP 2 246 868 A1

(12)

# **EUROPEAN PATENT APPLICATION**

(43) Date of publication: **03.11.2010 Bulletin 2010/44**

(51) Int Cl.: H01H 59/00 (2006.01)

(21) Application number: 09158852.5

(22) Date of filing: 27.04.2009

(72) Inventor: Herfst, Rodolf 5161 EB, Sprang-Capelle (NL)

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR

HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL

PT RO SE SI SK TR

(71) Applicant: EPCOS AG 81669 München (DE) (74) Representative: Epping - Hermann - Fischer Patentanwaltsgesellschaft mbH Ridlerstrasse 55 80339 München (DE)

# (54) Capacitive switch with enhanced lifetime

(57) Reducing the negative effects of charging of a capacitive switch enhances the reliability and the lifetime of the capacitive switch. Therefore, a first dielectric layer

is located on the upper surface of a first electrode facing the second electrode, and a second dielectric layer is located on the bottom surface of the second electrode facing the first electrode.

#### **Description**

20

30

40

45

50

Field of the invention

<sup>5</sup> **[0001]** The present invention relates to capacitive switches with enhanced lifetime and reliability by reduced charging effects. The capacitive switches may be MEMS-switches (MEMS = micro electro-mechanical system).

Description of the related art

[0002] Capacitive switches are capacitors comprising two electrodes where at least one electrode is suspended by spring elements and therefore movable. When a voltage that exceeds a certain "pull-in voltage" / "activation voltage" is supplied to the electrodes of the capacitor, the electrostatic force ("pull-in force") leads to a movement of the suspended electrode towards the other electrode; the capacitive switch is in it's "closed" state. The other electrode can have a fixed position. When the applied voltage falls below a certain "release voltage" the mechanical force applied by the spring elements separates the electrodes; the capacitive switch is again in its "open" state. Thus, applied voltages can be converted into mechanical movement.

[0003] Such capacitive switches can be used as ON/OFF switches as they can provide the ability of establishing and abandoning galvanic contact between two electrodes (that not necessarily have to be the electrodes of the capacitor). [0004] Such capacitive switches can also be capacitive elements having a variable capacity: as the capacity of a capacitor depends on the distance of the respective electrodes, a variable distance of the electrodes results in a variable capacity. A capacitive switch has at least two different values of capacitance, i.e. its open and its closed state.

**[0005]** In order to not short-circuit both electrodes, a dielectric can be located between the electrodes. In "RF-MEMS Switches and Switch Circuits" (IEEE Microwave Magazine, December 2001, page 59), MEMS capacitive switches are disclosed.

[0006] The reliability of capacitive switches is restricted by the effect of charge being injected from an electrode into the dielectric and being trapped in there. Trapped charge can e.g. lead to the situation that a closed capacitive switch cannot be released by decreasing the applied voltage below the activation voltage; the system remains in the closed state. [0007] As the amount of charge injection into the dielectric is exponential with voltage, it is known that charge injection can effectively be reduced by reducing the activation voltage of a capacitive switch. However, reducing the activation voltage can lead to situations where the closed state cannot be reached at all or where the transition time from the open state to the closed state is undesirable long.

**[0008]** What is needed is a capacitive switch that is less susceptible to the negative effects of charging and a method for driving such a capacitive switch where the necessity to use a lower activation voltage is avoided.

35 Summary of the invention

**[0009]** The present invention provides a capacitive switch that comprises a first electrode, a second electrode, a first dielectric layer, and a second dielectric layer. The first electrode has a bottom surface and an upper surface. The second electrode has an upper surface and a bottom surface where the second electrode is located above the first electrode's upper surface and the second electrode's bottom surface faces the first electrode's upper surface. The first dielectric layer has a first thickness d1 and is physically attached to the first electrode's upper surface. The second dielectric layer has a second thickness d2 and is physically attached to the second electrode's bottom surface. In an equilibrium state that may be the open state, a gap is located between the first dielectric layer and the second dielectric layer.

**[0010]** Although the effort to produce such a capacitive switch is enhanced (one dielectric layer has to be attached to each of the respective electrodes), such a capacitive switch has advantages over known capacitive switches:

- In applications where a certain overall thickness of the dielectric between the two electrodes is necessary, splitting up the dielectric into two distinct layers results in a lower layer thickness of each single layer. Each layer is physically attached to it's respective electrode. As a result, the maximum injection depth of negative or positive charge is reduced because electrons cannot be implanted in a deeper depth than the respective thickness of the layer.

- A second advantage arises from the fact that overall charging effects of the respective dielectric layers can cancel each other or can at least be reduced by electrostatic interaction of the charged dielectrics.

[0011] For example: It is possible that charging at the metal/dielectric interface no longer has a negative effect on the properties of the capacitive switch since interface charging can be compensated by influence charge at both interfaces. This is in contrast to known capacitive switches whose dielectric's charge can be transferred from the surface touching the metal electrode to the opposite surface and can be trapped there more effective than in a thinner dielectric.

[0012] Thus, depending on the vertical distribution of the charge density, the lower thickness and the negative sign can decrease the effect of trapped charge.

[0013] In one embodiment of the present invention, the first electrode is physically attached to a substrate.

**[0014]** A capacitive switch wherein the first electrode is physically attached to the substrate can easily be produced by providing a substrate, depositing a metal or a combination of metals (e.g. an alloy or distinct sub-layers) onto the substrate, and structuring the metal layer in order to get the first electrode.

**[0015]** In an alternative embodiment, the first electrode is physically attached to a first anchor that itself is physically attached to the substrate and that physically attaches the first electrode to the substrate. If there is only a partial spatial overlap of the electrode and the first anchor, there can be an additional dielectric layer located on the bottom side of the first electrode which may be advantageous with respect to thermal induced stress.

**[0016]** In one embodiment of the present invention, the second electrode is suspended by at least one spring element to a second anchor. The at least one spring element can - for instance - be a flexible lever or a flexible beam. A flexible lever can be fixed at one distal end to a substrate while the respective other distal end can be the support to which the second electrode is attached to. a flexible beam can be attached to a substrate with both ends while the second electrode is attached to a centered area of the beam.

[0017] In a further embodiment, the ratio d1 / d2 of the thickness of the two dielectric layers is in-between 0,2 and 0,95.

[0018] In an alternative embodiment, the ratio of the thicknesses d1 / d2 is in-between 0,95 and 1,05.

[0019] In still another alternative embodiment, the ratio of the thicknesses d1 / d2 is in-between 1,05 and 5.

**[0020]** The inventors found out that a capacitive switch whose first and second dielectric layer each have a thickness that is optimized in such a way that the combination of the thicknesses provides a capacitive switch where the dielectric layers' electrostatic charging effects cancel each other fully or at least partially, such that the lifetime and the reliability of the capacitive switch is strongly enhanced.

**[0021]** In one embodiment of the invention, a third dielectric layer is physically attached to the first electrode's bottom surface (e.g. when the first electrode and a respective anchor do not overlap completely). In another embodiment a fourth dielectric layer is physically attached to the second electrode's upper surface. Further, In still another embodiment the third and the fourth dielectric layer simultaneously are attached to the respective electrode.

[0022] As already mentioned above, an electrode layer having a dielectric physically attached to the underside and another dielectric layer physically attached to the upper side, stress - e. g. thermal induced stress caused by different thermal coefficients of expansion - in the electrode and the attached layers can be reduced. Especially bending of the respective electrode due to the bi-material effect (analog to the bimetal-effect) is effectively reduced. It is, however, possible to chose materials for the electrodes and the dielectrics having similar or identical thermal coefficients of expansion.

[0023] Either the first or the second electrode can be electrically connected to a ground terminal or to ground.

**[0024]** In situations where the capacitive switch is not in use, i.e. is inactive, the electrical connection to ground enables de-charging of the respective dielectric layer from charge that has been accumulated during its active period. Because the respective dielectric is thinner compared to known capacitive switches the time needed for de-charging is reduced.

**[0025]** The capacitive switch can be a MEMS-device i.e. a MEMS capacitive switch. It can provide switching capabilities where galvanic connections are established or abandoned with all the advantages of MEMS switches over e. g. PIN diodes or FET switches. Among these are: Near-zero power consumption, very high isolation, very low insertion losses.

**[0026]** Alternatively, it can be used as a switchable capacitive element having two distinct states (open / close) or that can be driven with a continuously variable voltage in order to provide a capacitive element that has a continuously variable capacity depending on the continuously variable voltage.

[0027] In a preferred embodiment, the capacitive switch is part of a radio frequency (RF-) circuit. Then, the first or the second electrode is electrically connected to the signal path of the radio frequency circuit. Such a capacitive switch can be part of an impedance matching circuit. The capacitive switch can be one out of a group of elements of a capacitive switch array. Such arrays can be used in order to match the impedance of a signal path to the variable impedance of an antenna.

**[0028]** Each of the first electrode and the second electrode can independently comprise aluminum, tungsten, gold, nickel, copper, AlCu, or an alloy of these metals. Each electrode can further comprise additional elements. Each electrode can consist only of a single element and each electrode can consist of an alloy of different metals.

**[0029]** Both, the first and the second dielectric layer can comprise silicon oxide (e.g.  $SiO_2$ ), silicon nitride, a silicon oxy-nitride (e.g.  $SiO_3$ ), aluminum nitride, alumina ( $AL_2O_3$ ), or silicon carbide.

**[0030]** Each of the third and the fourth dielectric layer also can comprise silicon oxide (e.g.  $SiO_2$ ), silicon nitride, a silicon oxy-nitride (e.g.  $SiO_3$ ), aluminum nitride, alumina ( $AL_2O_3$ ), or silicon carbide.

[0031] A method for manufacturing a capacitive switch can comprise the steps:

- depositing a first metal layer on a substrate,

20

30

35

40

45

50

55

- forming the first electrode (EI1) by structuring the first metal layer,

- depositing a first dielectric layer (DL1) onto the first electrode (EI1),

- depositing a sacrificial layer onto the first dielectric layer (DL1),

- structuring the sacrificial layer,

- depositing a second dielectric layer (DL2),

- depositing a second metal layer,

15

20

25

30

35

- forming a second electrode (El2) by structuring the second metal layer,

- removing the sacrificial layer by etching.

[0032] In one embodiment of the method, the sacrificial layer or the residual parts of the structured sacrificial layer is / are removed before the second dielectric layer is deposited.

[0033] Each of the layers can be deposited by means of atomic layer deposition, vapor deposition or chemical vapor deposition.

[0034] A method for driving a capacitive switch comprises the steps:

- starting from an equilibrium state where a gap (GP) is located between the first dielectric layer (DL1) and the second dielectric layer (DL2) of the capacitive switch

- bringing into contact the first (DL1) and the second (DL2) dielectric layer by applying a DC voltage across the gap (GP) between first (El1) and second (El2) electrode, where the first electrode is part of a moving structure

- separating the first (DL1) from the second (DL2) dielectric layer by decreasing or releasing the DC voltage.

[0035] A method for driving also can comprise the steps:

- starting from an equilibrium state where a gap (GP) is located between the first dielectric layer (DL1) and the second dielectric layer (DL2)

- bringing into contact the first (DL1) and the second (DL2) dielectric layer by applying a AC voltage across the gap (GP) between first (El1) and second (El2) electrode, where the first electrode is part of a moving structure and where cycle duration of the AC voltage is bigger than the relaxation time of the moving element and the AC cycle duration is shorter than twice the relaxation time of the moving element,

- separating the first (DL1) from the second (DL2) dielectric layer by releasing the AC voltage.

**[0036]** Here, AC cycle duration is understood to be the average time needed to change the sign of the polarization of one electrode. In other words: the transition time from one polarity to the opposite polarity is shorter than the relaxation time of the moving element.

**[0037]** In one method for driving the capacitive switch the period of time when a positive voltage is applied to the period of time when a negative voltage is applied.

Brief description of the drawings

**[0038]** The present invention will become fully understood from the detailed description given herein below and the accompanying drawings. In the drawings,

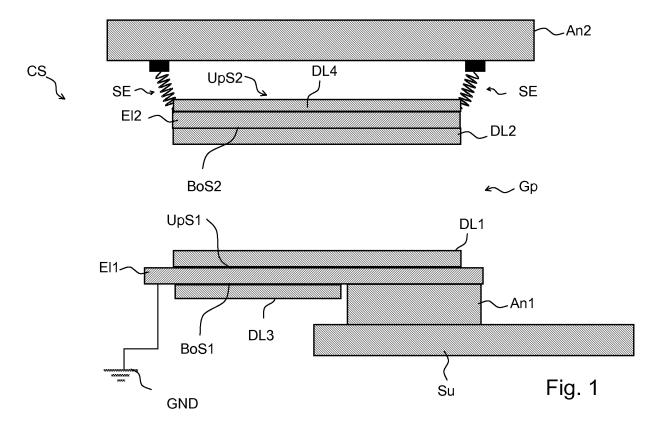

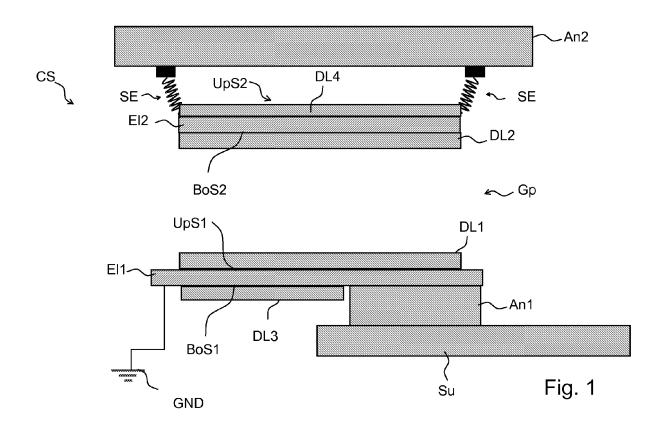

- FIG. 1 illustrates a cross-section of a capacitive switch,

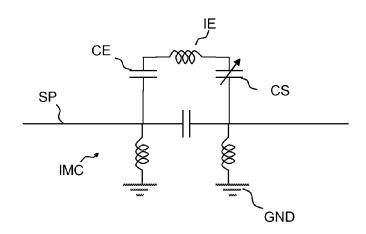

- FIG. 2 illustrates an equivalent circuit diagram of an impedance matching circuit where a capacitive switch is used as a capacitive element with variable capacity.

Detailed description of the embodiments

[0039] FIG. 1 illustrates a capacitive switch CS having a first electrode E11 and a second electrode E12. A first dielectric layer DL1 is located on the upper surface UpS1 of the first electrode ad physically attached to the surface. A second dielectric layer DL2 is located at the underside of the second electrode BoS2 and physically attached to the surface. The first electrode E11 is physically attached to a first anchor An1 which itself is physically attached to a substrate Su. The first electrode E11 and the first anchor An1 do not completely overlap. Opposite to the first dielectric layer DL1, a third dielectric layer DL3 is located on the area of the bottom surface BoS1 of the first electrode E11 where the first electrode E11 and the first anchor An1 do not overlap.

**[0040]** The second electrode E12 is suspended by spring elements SE. The spring elements physically attach the second electrode El2 to a second anchor An2.

[0041] The second electrode E12 can be electrically connected to an external switching environment (not shown). In

FIG. 1, the first electrode E11 is electrically connected to ground GND.

[0042] A gap Gp separates the first dielectric layer DL1 from the second dielectric layer DL2. The upper surface UpS1 of the first electrode El1 faces the bottom surface BoS2 of the second electrode El2.

**[0043]** FIG. 2 illustrates one possible application of a capacitive switch CS where the capacitive switch CS is part of an impedance matching circuit IMC. The impedance matching circuit is electrically connected to a signal path SP - e.g. as part of the electrical environment of a mobile communication device. The impedance matching circuit IMC further comprises capacitive elements CE and inductive elements IE that are electrically connected to the capacitive switch CS and the signal path SP.

**[0044]** The capacitive switch of the present invention can be mounted in any arbitrary spatial position. The phrases "upper" and "lower" surface refer to the position of the respective elements relative to other elements of the capacitive switch. The wording does not refer to the absolute position of the elements.

**[0045]** The present invention comprises electrodes and dielectric layers. The basic concept does not depend on details concerning the dimensions of the components/elements building the capacitive switch further. The invention is not restricted by the embodiments or the accompanying figures. Embodiments based on combinations of presented features or embodiments that further comprise additional elements are also possible.

[0046] Thus, numerous variations departing from the figures are possible without departing from the scope of the invention.

List of reference signs

[0047]

10

20

25

35

45

50

AN1, AN2: first anchor, second anchor

BOS1: bottom surface of first electrode

BOS2: bottom surface of second electrode

CE: capacitive element CS: capacitive switch

DL1, DL2, DL3, DL4: first, second, third and fourth dielec tric layer

EL1, EL2: first, second electrode

30 GND: ground

IE: inductive element

IMC: impedance matching circuit

SE: spring element SP: signal path SU: substrate

UPS1: upper surface of first electrode

UPS2: upper surface of second electrode

#### 40 Claims

- 1. A capacitive switch (CS), comprising:

- a first electrode (EI1) having an bottom surface (BoS1) and an upper surface (UpS1),

- a second electrode (El2) being located above the first electrode's upper surface (UpS1) and having an upper surface (UpS2) and an bottom surface (BoS2), the bottom surface (BoS2) of the second electrode (El2) facing the first electrode's upper surface (UpS1),

- a first dielectric layer (DL1) having a first thickness d1 and being physically attached to the first electrode's upper surface (UpS1),

- a second dielectric layer (DL2) having a second thickness d2 being physically attached to the second electrode's bottom surface (BoS2),

#### where

- in an equilibrium state a gap (GP) is located between the first dielectric layer (DL1) and the second dielectric layer (Dl2).

- 2. The capacitive switch of claim 1, where the first electrode (EI1) is physically attached to a substrate.

- 3. The capacitive switch of claim 1, where the first electrode (EI1) is physically attached to a first anchor (An1) that physically attaches the first electrode to a substrate (Su).

- **4.** The capacitive switch of one of the previous claims, where the second electrode (El2) is suspended by at least one spring element to a second anchor (An2).

- **5.** The capacitive switch of one of the previous claims, where the ratio d1 / d2 of the thicknesses is in between 0,2 and 0,95 or in between 0,95 and 1,05 or in between 1,05 and 5.

- 10 **6.** The capacitive switch of one of the previous claims, further comprising

- a third dielectric (DL3) layer being physically attached to the first electrode's bottom surface (BoS1) or

- a fourth dielectric layer (DL4) being physically attached to the second electrode's upper surface (UpS2).

- 7. The capacitive switch of one of the previous claims, wherein one of the first (El1) and the second (El2) electrode is electrically connected to a ground terminal (GND) or wherein one of the first (El1) and second (El2) electrode is electrically connected to the signal path (SP) of a RF-circuit.

- 8. The capacitive switch of one of the previous claims, formed as a MEMS device.

- **9.** The capacitive switch of one of the previous claims, wherein

- the first electrode (EI1) comprises one of AI, W, Au, AlCu, Ni,

- the second electrode (El2) comprises one of Al, W, Au, AlCu, Ni,

- the first dielectric layer (DL1) comprises one of SiO<sub>2</sub>, SiN, SiON, AlN, Al<sub>2</sub>O<sub>3</sub>, SiC,

- the second dielectric layer (DL2) comprises one of Si02, SiN, SiON, AlN, Al<sub>2</sub>O<sub>3</sub>, SiC.

- 10. The capacitive switch of one of claims 6 to 9, where

- the third dielectric layer (DL3) comprises one of SiO<sub>2</sub>, SiN, SiON, AlN, Al<sub>2</sub>O<sub>3</sub>, SiC, and

- the fourth dielectric layer (DL4) comprises one of Si02, SiN, SiON, AlN, Al<sub>2</sub>O<sub>3</sub>, SiC.

- 11. Method for manufacturing a capacitive switch of one of the previous claims comprising the steps:

- depositing a first metal layer on a substrate,

- building the first electrode (EI1) by structuring the first metal layer,

- depositing the first dielectric layer (DL1) onto the first electrode (El1),

- depositing a sacrificial layer onto the first dielectric layer (DL1),

- structuring the sacrificial layer,

- depositing the second dielectric layer (DL2),

- depositing a second metal layer,

- building the second electrode (El2) by structuring the second metal layer,

- removing the sacrificial layer by etching.

- **12.** Method according to the previous claim where the sacrificial layer is removed before the second dielectric layer is deposited.

- **13.** Method for manufacturing a capacitive switch of one of the previous claims where the dielectric layers are deposited by means of an atomic layer deposition method.

- **14.** Method for driving a capacitive switch of one of claims 1 to 11, comprising the steps:

- starting from an equilibrium state where a gap (GP) is located between the first dielectric layer (DL1) and the second dielectric layer (DL2)

- bringing into contact the first (DL1) and the second (DL2) dielectric layer by applying a DC voltage across the gap (GP) between first (El1) and second (El2) electrode, where the first electrode is part of a moving structure separating the first (DL1) from the second (DL2) dielectric layer by releasing the DC voltage.

6

20

5

25

30

40

35

45

55

**15.** Method for driving a capacitive switch of one of claims 1 to 11, comprising the steps:

- starting from an equilibrium state where a gap (GP) is located between the first dielectric layer (DL1) and the second dielectric layer (DL2)

- bringing into contact the first (DL1) and the second (DL2) dielectric layer by applying an AC voltage across the gap (GP) between first (EI1) and second (EI2) electrode, where the first electrode is part of a moving structure and where cycle duration of the AC voltage is bigger than the relaxation time of the moving element and the AC cycle duration is shorter than twice the relaxation time of the moving element,

- separating the first (DL1) from the second (DL2) dielectric layer by releasing the AC voltage.

Fig. 2

# **EUROPEAN SEARCH REPORT**

Application Number EP 09 15 8852

| Category                       | Citation of document with ir of relevant passa                                                                                                      | ndication, where appropriate,<br>ages                                                                             | Relevant<br>to claim                                 | CLASSIFICATION OF THE APPLICATION (IPC) |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------|--|

| Х                              | WO 03/078299 A (ECO<br>IONESCU MIHAI ADRIA<br>PHILIPPE [CH)<br>25 September 2003 (<br>* the whole documen                                           | N [CH]; FLUCKIGĒR<br>2003-09-25)                                                                                  | 1-15                                                 | INV.<br>H01H59/00                       |  |

| Х                              | US 2009/067115 A1 (<br>AL) 12 March 2009 (<br>* the whole documen                                                                                   |                                                                                                                   | 1-15                                                 |                                         |  |

| Х                              | WO 01/35433 A (HRL<br>17 May 2001 (2001-0<br>* the whole documen                                                                                    | 5-17)                                                                                                             | 1-15                                                 |                                         |  |

| Х                              | US 5 233 459 A (BOZ<br>3 August 1993 (1993<br>* figure 1 *                                                                                          | LER CARL O [US] ET AL)                                                                                            | 1                                                    |                                         |  |

| Х                              | WO 99/26333 A (MASS<br>TECHNOLOGY [US]) 27<br>* figure 24 *                                                                                         | ACHUSETTS INST<br>May 1999 (1999-05-27)                                                                           | 1                                                    | TECHNICAL FIELDS<br>SEARCHED (IPC)      |  |

| A                              | US 2006/012940 A1 (<br>AL) 19 January 2006<br>* figure 3 *                                                                                          | SONG IL-JONG [KR] ET<br>(2006-01-19)                                                                              | 1                                                    | H01H                                    |  |

| D,A                            | and Switch Circuits<br>IEEE MICROWAVE MAGA<br>CENTER, PISCATAWAY,<br>vol. 2, no. 4,                                                                 | ZINE, IEEESERVICE<br>NJ, US,<br>01-12-01), pages 59-71,                                                           |                                                      |                                         |  |

|                                | The present search report has I                                                                                                                     | peen drawn up for all claims                                                                                      |                                                      |                                         |  |

|                                | Place of search                                                                                                                                     | Date of completion of the search                                                                                  |                                                      | Examiner                                |  |

|                                | The Hague                                                                                                                                           | 7 September 2009                                                                                                  | 7 September 2009 Rup                                 |                                         |  |

| X : parti<br>Y : parti<br>docu | ATEGORY OF CITED DOCUMENTS icularly relevant if taken alone cularly relevant if combined with anotly ment of the same category nological background | T : theory or principle E : earlier patent door after the filing date D : document cited in L : document oited fo | ument, but publi<br>the application<br>other reasons | shed on, or                             |  |

# ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 09 15 8852

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

07-09-2009

| Patent document cited in search report |            |    | Publication date | Patent family member(s)    |                                                           |               | Publication date                                         |

|----------------------------------------|------------|----|------------------|----------------------------|-----------------------------------------------------------|---------------|----------------------------------------------------------|

| WO                                     | 03078299   | Α  | 25-09-2003       | AU<br>US                   | 2002322966<br>2005227428                                  |               | 29-09-20<br>13-10-20                                     |

| US                                     | 2009067115 | A1 | 12-03-2009       | NON                        | E                                                         |               |                                                          |

| WO                                     | 0135433    | Α  | 17-05-2001       | AU<br>EP<br>JP<br>US<br>US | 7067700<br>1230660<br>2003515235<br>2002055260<br>6396368 | A2<br>T<br>A1 | 06-06-20<br>14-08-20<br>22-04-20<br>09-05-20<br>28-05-20 |

| US                                     | 5233459    | Α  | 03-08-1993       | WO<br>US                   | 9501624<br>5784189                                        |               | 12-01-19<br>21-07-19                                     |

| WO                                     | 9926333    | A  | 27-05-1999       | US                         | 6127908                                                   | Α             | 03-10-20                                                 |

| US                                     | 2006012940 | A1 | 19-01-2006       | JP<br>JP<br>KR             | 4108694<br>2006032339<br>20060005596                      | Α             | 25-06-20<br>02-02-20<br>18-01-20                         |

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

#### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

# Non-patent literature cited in the description

RF-MEMS Switches and Switch Circuits. IEEE Microwave Magazine, December 2001, 59 [0005]