# (11) **EP 2 256 577 A1**

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication: **01.12.2010 Bulletin 2010/48**

(21) Application number: **10176318.3**

(22) Date of filing: 19.05.2004

(84) Designated Contracting States: **DE FR GB IT NL SE**

(30) Priority: 27.05.2003 US 446312

(62) Document number(s) of the earlier application(s) in accordance with Art. 76 EPC:

07024069.2 / 1 903 417 04252903.2 / 1 486 844

(71) Applicant: Power Integrations, Inc. San Jose, California 95138 (US)

(51) Int Cl.: **G05F 1/46** (2006.01) **H01L 29/78** (2006.01)

H02M 1/00 (2007.01)

(72) Inventor: Disney, Donald R. Cupertino, CA 95014 (US)

(74) Representative: Peterreins, Frank Fish & Richardson P.C. HighLight Business Towers Mies-van-der-Rohe-Strasse 8 80807 München (DE)

#### Remarks:

This application was filed on 13-09-2010 as a divisional application to the application mentioned under INID code 62.

### (54) Electronic control device comprising a transistor with a tap connection

(57) A technique for controlling a power supply (70) with power supply control element (82) with a tap element. In one embodiment, a power supply regulator includes a power transistor (88) having first, second, third and fourth terminals (89, 91, 93, 94). A control circuit (83) is included, which is coupled to the third and fourth terminals (93, 94) of the power transistor (88). The power transistor (88) is configured to switch a current between the first and second terminals (89, 91) in response a control signal received from the control circuit (83) at the third

terminal (93). A voltage between the fourth (94) and second terminals (91) of the power transistor (83) is substantially proportional to a current flowing between the first and second terminals (89, 91) when a voltage between the first and second terminals (89, 91) is less than a pinch off voltage. The voltage between the fourth (94) and second terminals (91) of the power transistor is substantially constant and less than the voltage between the first and second terminals (89, 91) when the voltage between the first and second terminals (89, 91) is greater than the pinch off voltage.

20

**[0001]** The present invention relates generally to control elements used in electronic circuits and, more specifically, the present invention relates to control elements with integrated power transistors.

1

**[0002]** Two of the primary goals in the design of control elements with integrated power transistors are cost and performance. Cost is generally reduced when the number of external components required in the electronic circuit are reduced, and when smaller, more efficient power transistors are employed. Performance may be improved by adopting a more efficient power transistor, which increases efficiency, and by lowering the manufacturing variance, which allows better control of critical parameters such as the peak current delivered by the power transistor.

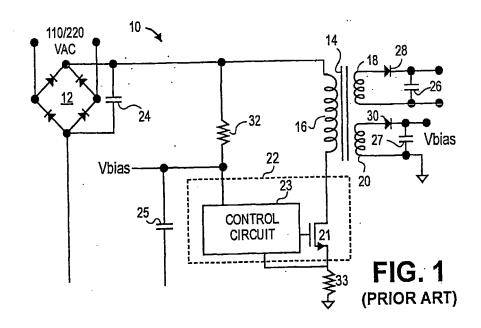

[0003] Figure 1 shows a power supply 10, which is provided as an example of an electronic circuit using a control element with power transistor. The control element 22 for this known power supply 10 includes a control circuit 23 and a separate power transistor 21. In power supply 10, the start-up function is performed by resistor 32, which provides the high voltage DC from bridge rectifier 12 to the control circuit 23. Unfortunately, resistor 32 is expensive, requires a large area in the power supply and lowers supply efficiency by dissipating power continuously, even after the start-up function is completed. The current limit function of power supply 10 is provided by a sense resistor 33 that is in series with the source of power transistor 21. The voltage across resistor 33, which increases with increasing current through power transistor 21, is coupled to the control circuit 23. When the current through power transistor 21 reaches a predetermined level, the control circuit 23 turns of power transistor 21. Drawbacks of this approach are the cost, size and power dissipation of resistor 33.

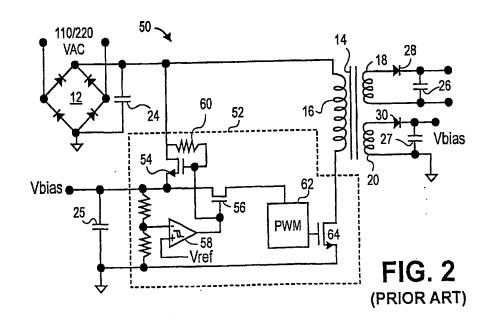

**[0004]** Figure 2 shows a known power supply 50 similar to power supply 10, except that resistor 32 has been eliminated. A voltage regulator internal to power supply chip 52 now performs the start-up function. The voltage regulator in power supply chip 52 may be turned off after the start-up function is completed, thus eliminating the extra power dissipation inherent to power supply 10. However, the voltage regulator in power supply chip 52 includes a high-voltage offline transistor 54 that consumes a significant area on power supply chip 52 and is also prone to electrical static discharge (ESD) and safe operating area (SOA) damage.

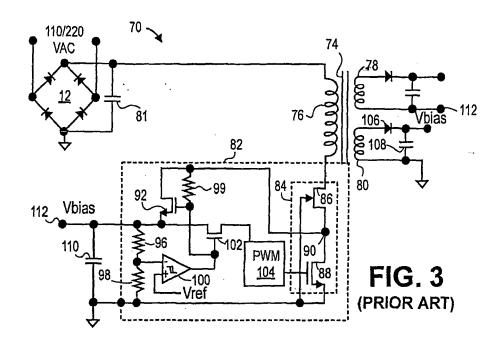

**[0005]** Figure 3 shows a known power supply 70 that avoids some of the problems of power supplies 10 and 50. Power supply 70 does not require a start-up resistor 32 or a high-voltage offline transistor 54. Instead, a tap 90 at the junction between junction field effect transistor (JFET) 86 and insulated gate field effect transistor (IGFET) 88 of metal oxide semiconductor field effect transistor (MOSFET) 84 is used to perform the start-up function. Tap 90 may also be used to monitor the voltage for

performing the current limit function, obviating the need for a separate sense resistor. The main limitation of this approach is that the MOSFET 84 used in power supply 70 is limited to one that can be monolithically integrated on the chip 82. In some cases, discrete power devices with higher efficiency may be available, but cannot be employed in the monolithic approach of power supply 70. An integrated control element with power transistor and tap element is disclosed. In one embodiment, a control element according to embodiments of the present invention includes a power transistor having first, second, third and fourth terminals. A control circuit is included, which is coupled to the third and fourth terminals of the power transistor. The power transistor adapted to switch a current between the first and second terminals in response a control signal to be received from the control circuit at the third terminal. A voltage between the fourth and second terminals of the power transistor is substantially proportional to a current flowing between the first and second terminals when a voltage between the first and second terminals is less than a pinch off voltage. The voltage between the fourth and terminals of the power transistor is substantially constant and less than the voltage between the first and second terminals when the voltage between the first and second terminals is greater than or equal to the pinch off voltage.

[0006] A high voltage transistor according to embodiments of the present invention includes a drain region having a first conductivity type. The transistor also includes at least one source region having the first conductivity type. At least one body region having a second conductivity type opposite to the first conductivity type is included in the transistor. The at least one body region adjoins the source region. The transistor includes at least one drift region having the first conductivity type and adjoining at a first end the drain region. The at least one drift region extends from the first end to adjoin at a second end the at least one body region. The at least one source region is separated from the second end of the at least one drift region by the at least one body region. The transistor further includes a tap region of a first conductivity type and a tap drift region extending from the tap region to the drain region. The transistor also includes an insulated gate adjacent to the at least one body region.

**[0007]** Additional features and benefits of the present invention will become apparent from the detailed description, figures and claims set forth below.

**[0008]** The present invention detailed illustrated by way of example and not limitation in the accompanying figures.

Figure 1 is a schematic diagram of a known power supply that includes a separate control circuit and power transistor. A high voltage resistor is used to perform the start-up function and a sense resistor is used to provide the current limit function.

Figure 2 is a schematic diagram of a known power supply that includes an integrated control circuit and

35

40

45

power transistor. A separate offline transistor is used to perform the start-up function.

Figure 3 is a schematic diagram of a known power supply that includes an integrated control circuit and power transistor. A tap in the integrated power transistor provides the start-up and current limit functions.

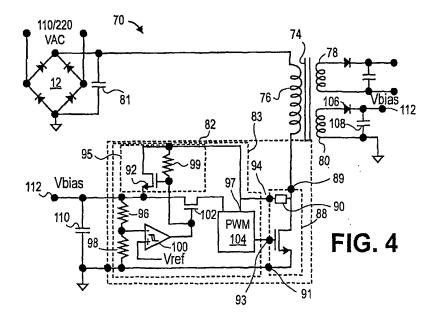

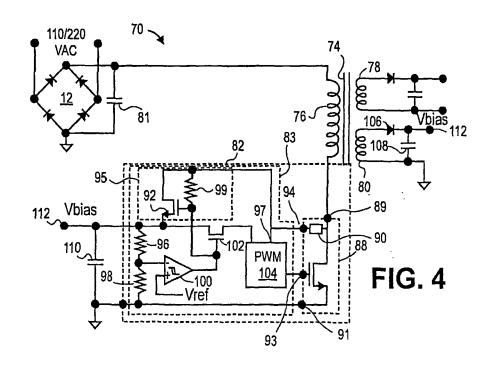

Figure 4 is a schematic diagram of one embodiment of a power supply control element with a tap element in accordance with the teachings of the present invention.

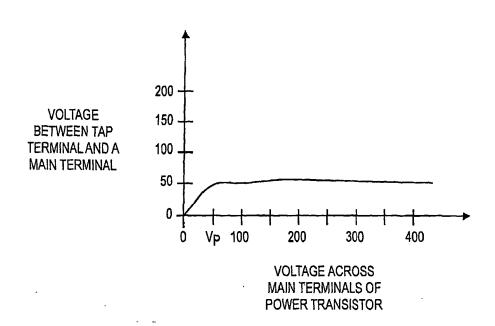

Figure 5 is a diagram illustrating the relationship between the voltage across the drain and source terminals and a tap element of one embodiment of a power transistor in accordance with the teachings of the present invention.

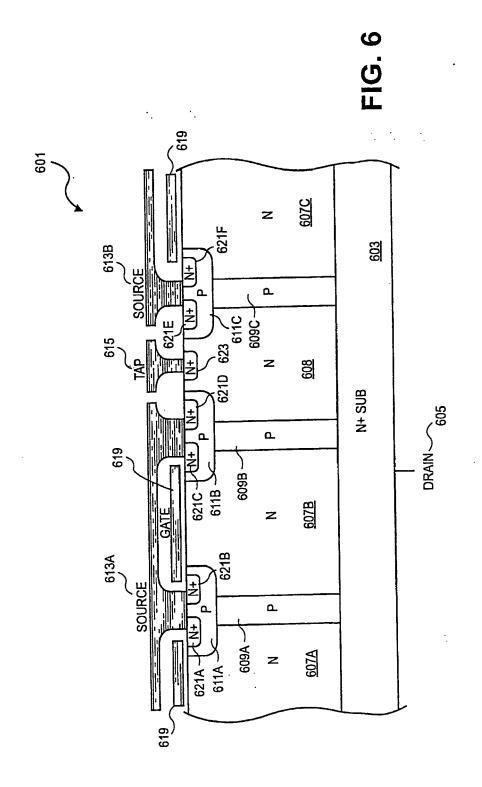

Figure 6 is a diagram illustrating a cross-sectional side view of one embodiment of a power transistor in accordance with the teachings of the present invention.

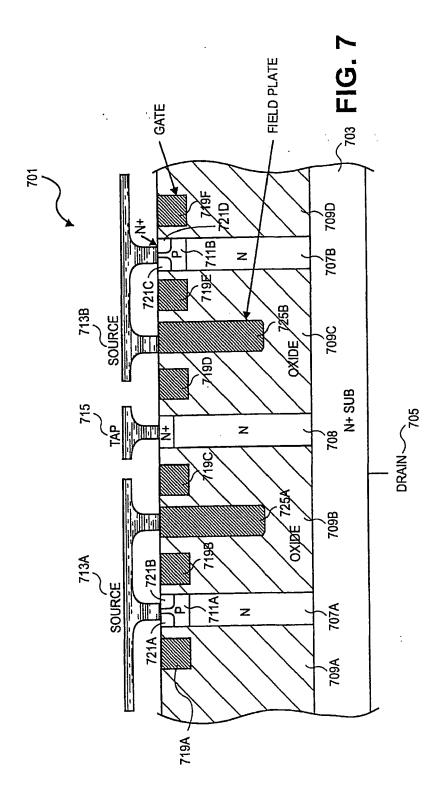

Figure 7 is a diagram illustrating a cross-sectional side view of another embodiment of a power transistor in accordance with the teachings of the present invention.

**[0009]** A novel control element including a power transistor with a tap element is disclosed. In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. It will be apparent, however, to one having ordinary skill in the art that the specific detail need not be employed to practice the present invention. In other instances, well-known materials or methods have not been described in detail in order to avoid obscuring the present invention.

**[0010]** The following description uses the example of a power supply to illustrate the benefits of the present invention. It will be apparent to one skilled in the art that the techniques are not limited to use in power supplies but apply to any electronic circuit employing a control element with integrated power transistor.

[0011] In general, a power supply according to embodiments of the present invention includes a power control element that includes a control circuit and a power transistor. The control circuit and power transistor may be packaged together in a single package. A power transistor according to embodiments of the present invention includes a tap element that provides a voltage proportional to the current flowing through the power transistor when the voltage across the main terminals of the power transistor is less than a pinch off voltage. In one embodiment, when the voltage across the main terminals of the power transistor is greater than or equal to the pinch off voltage, the voltage provided at the tap element is substantially fixed at a voltage, which may be substantially less than the voltage across the main terminals of the power transistor.

[0012] In one embodiment, the tap element may be

used for a start-up function for the power supply control element. In this embodiment, current is drawn from a main terminal of the power transistor through the tap element and into the control circuit.

**[0013]** In another embodiment, the tap element may be used to provide a signal for a current limit function of the power supply control element. In this embodiment, the tap element provides a voltage to the control circuit that is proportional to the current flowing through the power transistor.

**[0014]** In other embodiment, the tap element may be used provide other functions, such as for example sensing the voltage across the main terminals of the power transistor when the power transistor is in the off state. In addition, several or all of these functions maybe realized in the same power supply control element.

**[0015]** To illustrate, Figure 4 shows generally a schematic diagram of a power supply control element 82 in a power supply 70 according to embodiments of the present invention. In operation, alternating current (AC) voltage is rectified and filtered with rectifier 72 and capacitor 81. Energy transfer element 74 is coupled to receive the rectified voltage from rectifier 72 with primary winding 76. Energy transfer element also includes output winding 78 and bias winding 80. Energy is transferred across energy transfer element 74 from primary winding 76 to output winding 78 and bias winding 80 in response to power supply control element 82.

[0016] In one embodiment, power supply control element 82 includes control circuit 83 and power transistor 88 having main terminals 89 and 91, a tap element 90, a tap terminal 94 and a control terminal 93. In one embodiment, the main terminals 89 and 91 are the drain and source terminals, respectively, and control terminal 93 is the gate terminal of a power transistor 88 in accordance with the teachings of the present invention. In one embodiment, power transistor 88 is a metal oxide field effect transistor (MOSFET).

[0017] As shown in the depicted embodiment, main terminal 89 is coupled to primary winding 76 of energy transfer element 74. In operation, power transistor 88 is switched on and off to regulate the transfer of power from primary winding 76 to output winding 78 and bias winding 80. For example, in one embodiment, a feedback signal is received from the bias winding 80 through Vbias 112. Pulse width modulator (PWM) 104 is coupled to control terminal 93 to provide a control signal to switch power transistor 88 on and off in response to Vbias 112. It is appreciated of course that other configurations of switched mode power supplies may be employed that utilize power transistor 88 in accordance with the teachings of the present invention.

**[0018]** In one embodiment, power transistor 88 has a blocking voltage rating compatible with the peak voltage generated in the power supply circuit. When power transistor 88 is off, a relatively high voltage, which is greater than or equal to a pinch off voltage V<sub>P</sub> of power transistor 88, may be present across its main terminals 89 and 91.

20

35

40

Under this condition, the maximum voltage appearing at tap terminal 94 is in one embodiment significantly reduced from the maximum voltage appearing at main terminal 89 of power transistor 88, such that the circuit elements in control circuit 83 are not subjected to excessive voltages in accordance with the teachings of the present invention.

**[0019]** In one embodiment, start-up circuitry 95 of control circuit 83 may employ the use of tap element 90 for a start-up function. For example, in the embodiment illustrated in Figure 4, tap terminal 94 provides a voltage to a regulator 92 and a resistor 99 included in control circuit 83. To start up the power supply, current is drawn through the primary winding 76, power transistor 88 via tap element 90, and regulator 92 to charge up bypass capacitor 110. When the voltage at node 112 reaches the desired level, regulator 92 may be turned off.

[0020] In one embodiment, a line-sense function of control circuit 83 may also employ the use of tap element 90. For example, in the embodiment illustrated in Figure 4, when the voltage at main terminal 89 decreases below a pinch off voltage, the tap terminal 94 provides a voltage to line sensor 97 that is substantially proportional to the voltage difference between main terminals 89 and 91 of the power transistor 88. The voltage provided by tap element 90 to line sensor 97 is coupled to the PWM circuit 104, such that PWM circuit 104 can provide a line sense function of control circuit 83. For example, the PWM circuit 104 may stop switching the power transistor 88 when the line voltage falls below a certain level.

[0021] In one embodiment, when power transistor 88 is turned on, a relatively low voltage appears across its main terminals 89 and 91 and current flows through the primary winding 76 and the main terminals 89 and 91 of power transistor 88. In this mode of operation, the voltage across main terminals 89 and 91 is below a pinch off voltage and tap element 90 therefore provides a voltage at tap terminal 94 that is substantially proportional to the current flowing through the main terminals of power transistor 88 in accordance with the teachings of the present invention. The tap terminal 94 voltage is coupled to the PWM circuit 104, such that PWM circuit 104 can provide a current limit function of the control element. In order to minimize the tolerance of the current limit function, it is preferable to package control circuit 82 and power transistor 88 together and then perform an electrical trimming operation to adjust the current limit of the complete control element 82.

**[0022]** Figure 5 is a diagram illustrating the relationship between the voltage across the main terminals and the voltage of a tap terminal of one embodiment of a power transistor in accordance with the teachings of the present invention. The tap terminal voltage increases with increasing voltage across the main terminals of the power transistor up to a certain level and then remains relatively constant as the voltage across the power transistor is increased further. To illustrate, Figure 5 shows the voltage at the tap terminal increasing with the voltage across

the main terminals (e.g. between the drain and source terminals of the power MOSFET) until a pinch off voltage V<sub>P</sub>, which in the illustrated embodiment is approximately 50V. Thus, the maximum voltage of the tap terminal is shown as about 50V in this example, but the maximum voltage could range from 5 to 150V in other embodiments. Figure 5 also illustrates that the maximum voltage of the tap terminal in one embodiment remains substantially constant or fixed for voltage levels across the main terminals of the power transistor greater than or equal to the pinch off voltage V<sub>P</sub>. In another embodiment, it is noted that the voltage at the tap terminal may increase with increasing voltage levels across the main terminals of the power transistor as long as the voltage at the tap element is reduced or limited so as not to subject the circuit elements in control circuit to excessive voltages in accordance with the teachings of the present invention. [0023] Figure 6 is a diagram illustrating a cross-sectional side view of one embodiment of a power transistor 601 in accordance with the teachings of the present invention. It is appreciated that although power transistor 601 has been illustrated as an n-channel transistor in Figure 6, a p-channel transistor may be realized by utilizing the opposite conductivity types for all of the illustrated doped regions.

[0024] In one embodiment, power transistor 601 includes an insulated gate 619, including for example polysilicon, drain terminal 605 and source terminals 613, which are illustrated as 613A and 613B. N+ source regions 621, which are shown as 621A-F, are coupled to source terminals 613 and N+ drain region 603 is coupled to drain terminal 605. N+ source regions 621 are adjoining P-body regions 611, which are shown as 611A-C. A plurality of N- drift regions 607, which are shown as 607A-C, adjoin at one end N+ drain region 603 and extend from the N+ drain region 603 to adjoin at the other end P-body regions 611. In one embodiment, an N- tap drift region 608 is also included, which also extends from N+ drain region 603. An N+ tap region 623 adjoins N- tap drift region 608 at the opposite end from N+ drain region 603. A tap element 615 is coupled to N+ tap region 623. In one embodiment, N- tap drift region 608 is substantially similar to the N- drift regions 607 and may even be characterized as one of the plurality of N- drift regions 607. In another embodiment, N- tap drift region 608 may have a different construction, dimensions, such as for example width, and/or a different doping profile than the N- drift regions 607 to optimize or change the pinch off voltage  $V_{P}$ .

[0025] In one embodiment, N- drift regions 607 are separated by P- type regions 609 of semiconductor material. As illustrated in Figure 6, the N- drift regions 607 are separated by P- type regions 609 of semiconductor material and are arranged such that alternating regions ofN- drift regions 607 and P- type regions 609 of semiconductor material are interposed among one another in power transistor. 601.

[0026] In the on state, insulated gate 619 is biased

40

such that channels are formed proximate to insulated gate 619 across P- body regions 611 to form conduction paths between N+ source regions 621 and N- drift regions 607. Accordingly, conduction paths are provided through N- drift regions 607 between source electrodes 613 and drain electrode 605. In the off state, insulated gate 619 is biased such that there are no longer channels under insulated gate 619 through P-body regions 611 to form conduction paths between source electrodes 613 and drain electrode 605.

[0027] In operation, when N+ drain region 603 is biased at a relatively low voltage with respect to N+ source regions 621, tap element 615 is resistively coupled to drain terminal 605 through N+ tap region 623 and through N- tap drift region 608. Accordingly, tap element 615 in one embodiment tracks the voltage of drain terminal 605 and is therefore proportional to the current through drain terminal 605. In one embodiment, these conditions occur with the voltage difference between the main terminals, source and drain terminals 613 and 605, is less than the pinch off voltage V<sub>P</sub>. However, at a higher drain terminal 605 bias, or when the voltage difference between the main terminals, source and drain terminals 613 and 605, is greater than or equal to the pinch off voltage V<sub>P</sub>, a portion of the tap N- type regions 608 is substantially or completely depleted of free charge carriers by P- type regions 609 on the neighboring sides of N- tap drift region

[0028] In the embodiment illustrated Figure 6, the P-type regions 609 are illustrated as pillars and are numbered as 609A-C on either sides of N- drift regions 607 as well as N- tap drift region 608. In one embodiment, when the N-drift regions 607 and N- tap drift region 608 are completely depleted of free charge carriers, the voltage of tap element 615 is effectively fixed at Vp when the voltage difference between the main terminals, source and drain terminals 613 and 605, is greater than or equal to  $V_{\rm P}$ , as illustrated for example in Figure 5.

**[0029]** Figure 7 is a diagram illustrating a cross-sectional side view of another embodiment of a power transistor 701 in accordance with the teachings of the present invention. It is appreciated that although power transistor 701 has been illustrated as an n-channel transistor in Figure 7, a p-channel transistor may be realized by utilizing the opposite conductivity types for all of the illustrated doped regions.

[0030] In one embodiment, power transistor 701 includes insulated gates 719, shown as insulated gates 719A-F, drain terminal 705 and source terminals 713, which are illustrated as 713A and 713B. N+ source regions 721, which are shown as 721A-D, are coupled to source terminals 713 and N+ drain region 703 is coupled to drain terminal 705. N+ source regions 721 are adjoining P- body regions 711, which are shown as 711A and 711B. A plurality ofN- drift regions 707, which are shown as 707A and 707B, adjoin at one end N+ drain region 703 and extend from the N+ drain region 703 to adjoin at the other end P- body regions 711. In one embodiment,

an N- tap drift region 708 is also included, which also extends from the N+ drain region 703. An N+ tap region 723 adjoins N- tap drift region 708 at the opposite end from N+ drain region 703. A tap element 715 is coupled to N+ tap region 723. In one embodiment, N- tap drift region 708 is substantially similar to the N- drift regions 707 and may even be characterized as one of the plurality of N- drift regions 707. In another embodiment, N- tap drift region 708 may have a different construction, dimensions, such as for example width, and/or a different doping profile than the N- drift regions 707 to optimize or change the pinch off voltage  $V_{\rm P}$ .

[0031] In one embodiment, N- drift regions 707 and N-tap drift region 708 are separated by regions of dielectric material 709 in which field plates 725 are disposed. As illustrated in the embodiment of Figure 7, dielectric material regions 709 are shown as 709A-D and in one embodiment may include oxide. Field plates 725 are shown as 725A and 725B and are coupled to source terminals 713. In the depicted embodiment, the N- drift regions 707 are separated by regions of dielectric material 709 and field plates 725 such that alternating regions of N- drift regions 707 and regions of dielectric material 709 and field plates 725 are interposed among one another in power transistor 701.

**[0032]** In the on state, insulated gates 719 are biased such that channels are formed proximate to insulated gates 719 across P- body regions 711 to form conduction paths between N+ source regions 721 and N- drift regions 707. Accordingly, conduction paths are provided through N- drift regions 707 between source electrodes 713 and drain electrode 705. In the off state, insulated gates 719 are biased such that there are no longer channels proximate to insulated gates 719 through P- body regions 711 to form conduction paths between source electrodes 713 and drain electrode 705.

[0033] In operation, when N+ drain region 703 is biased at a relatively low voltage with respect to N+ source regions 721, tap element 715 is resistively coupled to drain terminal 705 through N+ tap region 723 and through N- tap drift regions 708. Accordingly, the voltage of tap element 715 tracks the voltage of drain terminal 705 and is therefore proportional to the current through drain terminal 705. In one embodiment, these conditions occur with the voltage difference between the main terminals, source and drain terminals 713 and 705, is less than the pinch off voltage V<sub>P</sub>. However, at a higher drain terminal 705 bias, or when the voltage difference between the main terminals, source and drain terminals 713 and 705, is greater than or equal to the pinch off voltage V<sub>P</sub>, a portion of the N- drift regions 707 and N- tap drift region 708 is substantially or completely depleted of free charge carriers by field plates 725 disposed in the dielectric regions 709 on neighboring sides of N-drift regions 707 and N- tap drift region 708.

**[0034]** The voltage of tap element 715 is effectively fixed at Vp when the voltage difference between the main terminals, source and drain terminals 713 and 705, is

20

25

30

35

40

45

50

55

greater than or equal to  $V_{\text{P}}$ , as illustrated for example in Figure 5.

**[0035]** In the foregoing detailed description, the present invention has been described with reference to specific exemplary embodiments thereof. It will, however, be evident that various modifications and changes may be made thereto without departing from the broader spirit and scope of the present invention. The present specification and figures are accordingly to be regarded as illustrative rather than restrictive.

**[0036]** Although the present invention is defined in the attached claims, it should be understood that the present invention can also (alternatively) be defined in accordance with the following embodiments:

1. A power supply control element, comprising:

a power transistor having first, second, third and fourth terminals; and a control circuit coupled to the third and fourth terminals of the power transistor,

wherein a current provided at the fourth terminals of the power transistor is to be drawn from at least one of the first and second terminals of the power transistor to provide power to the control circuit.

- 2. The power supply control element of embodiment 1 wherein a voltage between the fourth and second terminals of the power transistor is substantially proportional to a current flowing between the first and second terminals when a voltage between the first and second terminals is less than a pinch off voltage.

- 3. The power supply control element of embodiment 1 wherein a voltage between the fourth and second terminals is substantially constant and less than the voltage between the first and second terminals when the voltage between the first and second terminals is greater than a pinch off voltage.

- 4. The power supply control element of anyone of embodiments 1 to 3 wherein the power transistor is configured to switch a current between the first and second terminals in response a control signal received from the control circuit at the third terminal.

- 5. A power supply control element, comprising:

a power transistor having first, second, third and fourth terminals; and a control circuit coupled to the third and fourth terminals of the power transistor,

wherein a voltage between the fourth and second terminals is substantially proportional to a current flowing between the first and second terminals, the voltage between the fourth and second terminals providing an input signal to a current limit function of the control circuit.

6. A power supply control element, comprising:

a power transistor having first, second, third and fourth terminals; and a control circuit coupled to the third and fourth terminals of the power transistor, wherein a voltage at the fourth terminal is coupled to provide an input signal to a line sense function of the control circuit.

- 7. The power supply control element of embodiment 6 wherein the voltage between the fourth and second terminals of the power transistor is substantially proportional to the voltage between the first and second terminals is less than a pinch off voltage.

- 8. The power supply control element of embodiment 5 or 6 wherein the voltage between the fourth and second terminals of the power transistor is substantially constant and less than the voltage between the first and second terminals when the voltage between the first and second terminals is greater than or equal to a pinch off voltage.

- 9. The power supply control element of anyone of embodiments 5 to 8 wherein the power transistor is configured to switch a current between the first and second terminals in response a control signal received from the control circuit at the third terminal.

- 10. A high voltage transistor, comprising:

a drain region of a first conductivity type; a source region of the first conductivity type; a tap region of the first conductivity type; a body region of a second conductivity type opposite to the first conductivity type, the body region adjoining the source region; a drift region of the first conductivity type extending from the drain region to the body region; a tap drift region of the first conductivity type extending from the drain region to the tap region; and an insulated gate adjacent the body region.

- 11. The high voltage transistor of embodiment 10 further comprising a semiconductor region of the second conductivity type, disposed between the drift region and the tap drift region.

- 12. The high voltage transistor of embodiment 10 further comprising a field plate disposed between the drift region and the tap drift region.

20

35

40

45

50

- 13. The high voltage transistor of any one of embodiments 10, 11 or 12 wherein a voltage between the tap region and the source region is proportional to a voltage between the drain region and the source region when the voltage between the drain region and the source region is less than a pinch off voltage.

- 14. The high voltage transistor of anyone of embodiments 10 to 13 wherein the tap drift region is configured to pinch off the voltage difference between the tap region and the source region when the voltage difference between the drain region and the source region is greater than a pinch off voltage.

- 15. The high voltage transistor of anyone of embodiments 10 to 14 wherein a voltage between the tap region and the source region is substantially constant when the voltage difference between the drain region and the source region is greater than a pinch off voltage.

- 16. The high voltage transistor of anyone of embodiments 10 to 15 further comprising:

a source electrode coupled to the source region; a drain electrode coupled to the drain region; and

a gate electrode coupled to the insulated gate.

- 17. The high voltage transistor of embodiment 16 wherein the source electrode is coupled to the source region and the field plate.

- 18. The high voltage transistor of anyone of embodiments 10 to 17 wherein the first conductivity type comprises N type semiconductor material and the second conductivity type comprises P type semiconductor material.

- 19. The high voltage transistor of embodiment 12 wherein the first conductivity type comprises N type semiconductor material and the second conductivity type comprises P type semiconductor material, wherein the field plate is disposed in dielectric material comprising silicon dioxide.

- 20. The high voltage transistor of anyone of embodiments 10 to 19 wherein the tap drift region has a construction and doping profile that is substantially similar to the drift region.

- 21. The high voltage transistor of anyone of embodiments 10 to 19 wherein the tap drift region has a construction that is different than the drift region.

- 22. The high voltage transistor of anyone of embodiments 10 to 19 wherein the tap drift region has a dimension that is different than the drift region.

- 23. The high voltage transistor of anyone of embodiments 10 to 19 wherein the tap drift region has a doping profile that is different than the drift region.

- 24. An electronic circuit control element, comprising:

a power transistor having first, second, third and fourth terminals; and

a control circuit coupled to the third and fourth terminals of the power transistor,

wherein the voltage between the fourth and second terminals of the power transistor is substantially proportional to a current flowing between the first and second terminals when a voltage between the first and second terminals is less than a pinch off voltage, wherein the voltage between the fourth and second terminals of the power transistor is substantially constant and less than the voltage between the first and second terminals when the voltage between the first and second terminals is greater than the pinch off voltage.

25. A power supply regulator, comprising:

a power transistor having first, second, third and fourth terminals; and

a control circuit coupled to the third and fourth terminals of the power transistor,

wherein a voltage between the fourth and second terminals is substantially proportional to a current flowing between the first and second terminals when a voltage between the first and second terminals is less than a pinch off voltage, wherein the voltage between the fourth and second terminals is substantially constant and less than the voltage between the first and second terminals when the voltage between the first and second terminals is greater than the pinch off voltage.

- 26. The control element or power supply regulator of embodiment 24 or 25 wherein the fourth terminal is coupled to provide power to the control circuit.

- 27. The control element or power supply regulator of embodiment 24 or 25 wherein the fourth terminal is coupled to a current limit function of the control circuit

- 28. The control element or power supply regulator of embodiment 24 or 25 wherein the fourth terminal is coupled to a line sense function of the control circuit.

- 29. The control element or power supply regulator of embodiments 24 to 28 wherein the power transistor and control circuit are packaged together in a

7

10

15

20

25

30

35

single package.

30. The power supply regulator of embodiment 25 wherein the power transistor is configured to switch a current between the first and second terminals in response a control signal to be received from the control circuit at the third terminal.

#### **Claims**

**1.** A power supply control element comprising:

a power transistor (601, 701) having first and second main terminals (613, 713, 605, 705), a gate terminal (619, 719), and a tap terminal (615, 715); and

a control circuit (83) coupled to the gate (619, 719) and tap (615, 715) terminals of the power transistor (601, 701),

wherein a voltage at the tap terminal (615, 715) is coupled to provide an input signal to a line sense function of the control circuit (83) or a current provided at the tap terminal (615, 715) of the power transistor (601, 701) is to be drawn from at least one of the first and second main terminals (613, 713, 605, 705) of the power transistor (601, 701) to provide power to the control circuit (83)

#### characterized in that:

a tap element (615, 715) is resistively coupled to the first of the main terminals (605, 705) through a tap region (623, 723) and through a tap drift region (608, 708) when a region (603, 703) coupled to the first of the main terminals (605, 705) is biased at a relatively low voltage with respect to regions (621, 721) coupled to the second of the main terminals (605, 705), and a portion of the drift regions (607, 707) and the tap drift region (608, 708) is substantially or completely depleted of free charge carriers at a higher first main terminal (605, 705) bias or when the voltage difference between the main terminals (613, 713, 605, 705) is greater than or equal to a pinch off voltage.

2. The power supply control element of claim 1, wherein the power transistor (601, 701) comprises:

insulated gates (619, 719);

source (613, 713) and drain terminals (605, 705);

source regions (621, 721) coupled to the source terminals (613, 713),

wherein the source regions (621, 721) adjoin

body regions (611, 711);

a drain region (603, 703) coupled to drain terminals (605, 705);

a plurality of drift regions (607, 707) adjoining at one end the drain regions (603, 703) and extending from the drain regions (603, 703) to adjoin at the other end the body regions (611, 711), wherein:

the tap drift region (608, 708) extends from the drain region (603, 703)

the tap region (623, 723) adjoins the tap drift region (608, 708) at the opposite end from the drain region (603, 703); and

the tap element (615, 715) is coupled to the tap region.

- 3. The power supply control element of claim 2, wherein the tap element (615, 715) is resistively coupled to the drain terminal (605, 705) through the tap region (623, 723) and through the tap drift region (608, 708) when the drain region (603, 703) is biased at a relatively low voltage with respect to the source regions (621, 721) and the portion of the drift regions (607, 707) and the tap drift region (608, 708) is substantially or completely depleted of free charge carriers at the higher drain terminal (605, 705) bias or when the voltage difference between the source (613, 713) and drain (605, 705) terminals is greater than or equal to the pinch off voltage.

- 4. The power supply control element of any preceding claim, wherein a voltage between the tap and second of the main terminals of the power transistor is substantially proportional to a current flowing between the first and second terminals when a voltage between the first and second terminals is less than the pinch off voltage.

- 40 5. The power supply control element of any preceding claim wherein a voltage between the tap and second of the main terminals is substantially constant and less than the voltage between the first and second main terminals when the voltage between the first and second main terminals is greater than the pinch off voltage.

- 6. The power supply control element of any preceding claim wherein the power transistor is configured to switch a current between the first and second main terminals in response a control signal received from the control circuit (83) at the gate terminal.

- 7. The power supply control element of any preceding claim wherein the current provided at the tap terminal of the power transistor is to be drawn from at least one of the first and second main terminals of the power transistor to provide power to the control cir-

50

cuit (83).

**8.** The power supply control element of claim 1, wherein the power transistor comprises a high voltage transistor comprising:

5

a drain region of a first conductivity type; a source region of the first conductivity type; a body region of a second conductivity type opposite to the first conductivity type, the body region adjoining the source region; a drift region of the first conductivity type extending from the drain region to the body region; an insulated gate adjacent the body region; a tap region of the first conductivity type; and a tap drift region of the first conductivity type also extending from the drain region to the tap region.

10

15

**9.** A high voltage transistor according to claim 8 further comprising a semiconductor region of the second conductivity type, disposed between the drift region and the tap drift region.

20

**10.** A high voltage transistor according to claim 8 further comprising a field plate disposed between the drift region and the tap drift region.

28

**11.** A high voltage transistor according to any one of claims 8 to 10 wherein the tap drift region has a construction and doping profile that is substantially similar to the drift region.

3

**12.** A high voltage transistor according to any one of claims 8 to 10 wherein the tap drift region has a construction that is different than the drift region.

35

**13.** A high voltage transistor according to any one of claim 8 to 10 wherein the tap drift region has a dimension that is different than the drift region.

40

**14.** A high voltage transistor according to any one of claim 8 to 10 wherein the tap drift region has a doping profile that is different than the drift region.

45

50

FIG. 5

## **EUROPEAN SEARCH REPORT**

Application Number EP 10 17 6318

| Category                                   | Citation of document with ir of relevant passa                                                                                                                              | ndication, where appropriate,                                            | Relevant<br>to claim                                  | CLASSIFICATION OF THE APPLICATION (IPC)   |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------|

| А                                          | US 6 462 971 B1 (BA<br>8 October 2002 (200                                                                                                                                  | LAKRISHNAN BALU ET AL)                                                   |                                                       | INV.<br>G05F1/46<br>H02M1/00<br>H01L29/78 |

| A                                          | US 2002/159276 A1 (<br>31 October 2002 (20<br>* the whole documen                                                                                                           |                                                                          | 1-14                                                  |                                           |

| A                                          | US 2002/060340 A1 (DEBOY GERALD [DE] E<br>23 May 2002 (2002-0<br>* the whole documen                                                                                        | 5-23)                                                                    | 1-14                                                  |                                           |

| A                                          | US 4 811 075 A (EKL<br>7 March 1989 (1989-<br>* the whole documen                                                                                                           | 03-07)                                                                   | 1-14                                                  |                                           |

| A                                          | EP 0 585 789 A (POW<br>9 March 1994 (1994-<br>* the whole documen                                                                                                           |                                                                          | 1-14                                                  | TECHNICAL FIELDS<br>SEARCHED (IPC)        |

| A                                          | MILLMAN J ET AL: "M<br>FIELD-EFFECT TRANSI<br>1 January 1988 (198<br>MICROELECTRONIQUE.<br>MICROELECTRONICS, M<br>MCGRAW HILL, FR, PA<br>XP002280262<br>* the whole documen | STORS" 8-01-01), TRANSLATION OF CGRAW HILL 1987, PARIS, GE(S) 133 - 170, | 1                                                     | G05F<br>H02M<br>H01L<br>H03K              |

|                                            | The present search report has l                                                                                                                                             | •                                                                        |                                                       |                                           |

|                                            | Place of search                                                                                                                                                             | Date of completion of the search                                         | C                                                     | Examiner                                  |

|                                            | Munich                                                                                                                                                                      | 13 October 2010                                                          |                                                       | rdella, Simone                            |

| X : parti<br>Y : parti<br>docu<br>A : tech | ATEGORY OF CITED DOCUMENTS icularly relevant if taken alone icularly relevant if combined with another of the same category inological background written disclosure        | L : document cited fo                                                    | ument, but publi<br>the application<br>rother reasons | shed on, or                               |

## ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 10 17 6318

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

13-10-2010

| cite | Patent document<br>ed in search report |    | Publication date |                                              | Patent family member(s)                                                                                       |                       | Publication date                                                                                     |

|------|----------------------------------------|----|------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------|

| JS   | 6462971                                | B1 | 08-10-2002       | US<br>US<br>US<br>US<br>US<br>US<br>US<br>US | 2002172055 A<br>2009310389 A<br>6351398 B<br>6366481 B<br>6313976 B<br>6356464 B<br>6304462 B<br>2008186747 A | 1<br>1<br>1<br>1<br>1 | 21-11-200<br>17-12-200<br>26-02-200<br>02-04-200<br>06-11-200<br>12-03-200<br>16-10-200<br>07-08-200 |

| JS   | 2002159276                             | A1 | 31-10-2002       | DE                                           | 10108131 A                                                                                                    | 1                     | 05-09-200                                                                                            |

| JS   | 2002060340                             | A1 | 23-05-2002       | WO<br>DE<br>EP<br>JP<br>JP                   | 0063972 A<br>19918028 A<br>1175700 A<br>4099315 B<br>2002542629 T                                             | 1<br>1<br>2           | 26-10-200<br>02-11-200<br>30-01-200<br>11-06-200<br>10-12-200                                        |

| JS   | 4811075                                | A  | 07-03-1989       | DE<br>EP<br>JP<br>JP<br>JP                   | 3861707 D<br>0295391 A<br>2529717 B<br>63314869 A<br>2804460 B<br>8172184 A                                   | 1<br>2<br>2           | 07-03-199<br>21-12-198<br>04-09-199<br>22-12-198<br>24-09-199                                        |

| EP   | 0585789                                | Α  | 09-03-1994       | DE<br>DE<br>JP<br>JP<br>US                   | 69300361 D<br>69300361 T<br>3510652 B<br>6178538 A<br>5313381 A                                               | 2<br>2                | 14-09-199<br>04-04-199<br>29-03-200<br>24-06-199<br>17-05-199                                        |

FORM P0459

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82