### (11) **EP 2 259 162 A1**

(12)

### **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication:

08.12.2010 Bulletin 2010/49

(51) Int Cl.:

G05F 1/575 (2006.01)

H02M 3/07 (2006.01)

(21) Numéro de dépôt: 10164554.7

(22) Date de dépôt: 01.06.2010

(84) Etats contractants désignés:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO SE SI SK SM TR

Etats d'extension désignés:

**BAMERS**

(30) Priorité: 03.06.2009 FR 0953653

(71) Demandeur: STMicroelectronics (Grenoble 2)

SAS

38000 Grenoble (FR)

(72) Inventeurs:

• Gicquel, Hugo 38000, GRENOBLE (FR)

Sabut, Marc 38320, EYBENS (FR)

Reaute, Fabien 38140, RENAGE (FR)

(74) Mandataire: Zapalowicz, Francis Bureau D.A. Casalonga - Josse 8 Avenue Percier

75008 Paris (FR)

(54) Dispositif de génération d'une tension de référence destinée à un système du type à capacité commutée.

(57) Le dispositif génère une tension de référence, en particulier destinée à un système du type à capacité commutée, à partir d'une tension de consigne. Il comprend une boucle de régulation (BR) possédant une première entrée pour recevoir la tension de consigne (VBG) et un étage de sortie (ETSS) agencé en suiveur de ten-

sion et rebouclé sur une deuxième entrée de ladite boucle, et un étage supplémentaire (ETSP) configuré pour délivrer ladite tension de référence audit système à capacité commuté, cet étage supplémentaire, couplé à l'étage de sortie, étant également agencé en suiveur de tension et apparié avec l'étage de sortie.

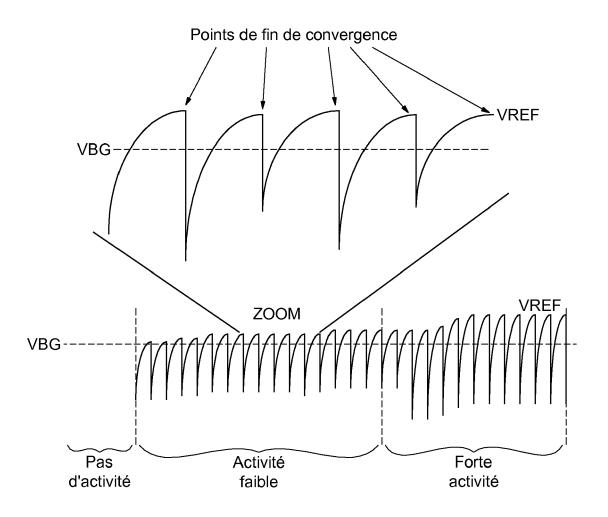

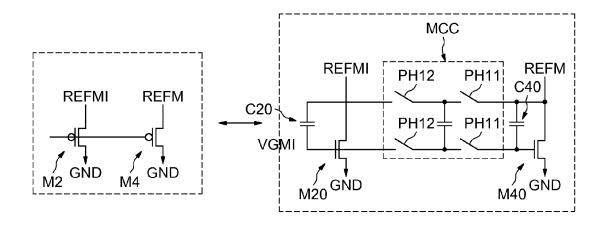

## FIG.2

EP 2 259 162 A1

#### Description

**[0001]** L'invention concerne les circuits électroniques, et plus particulièrement la génération d'une tension de référence, par exemple destinée à un système à capacité commutée.

[0002] La précision d'un tel système à capacité commutée est très fortement liée à la précision de la tension de référence. Par exemple, dans un convertisseur analogique numérique 12 bits à architecture pipelinée avec une dynamique de 2 Vpp (deux fois la tension crête-crête), le bit de poids faible (LSB) correspond à une tension de 500 microvolts, ce qui implique une précision de la tension de référence de l'ordre de 100 microvolts.

**[0003]** Dans les solutions classiques, la tension de référence délivrée à un système à capacité commutée est généralement produite par une boucle de régulation comportant un amplificateur opérationnel suiveur recevant en entrée une tension de consigne.

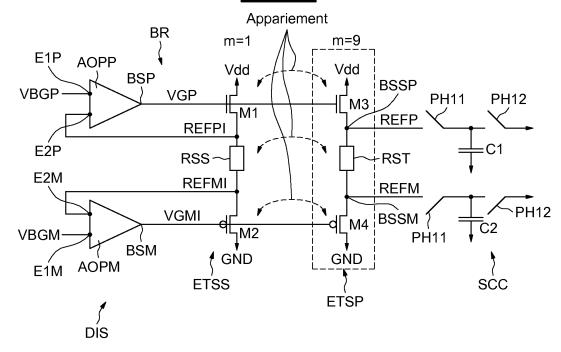

**[0004]** Un inconvénient majeur d'une telle réalisation réside, comme illustré sur la figure 1, dans le fait que seule la valeur moyenne de la tension de référence VREF est régulée sur la valeur de consigne VBG, mais cette valeur moyenne est différente des valeurs aux points de fin de convergence.

**[0005]** Et, il convient de noter que dans un environnement de capacité commutée, la valeur en chaque point de fin de convergence est la seule à être prise en compte puisque c'est cette valeur qui est échantillonnée pour le cycle d'horloge suivant. Il en résulte alors, comme illustré sur la figure 1, des valeurs aux points de fin de convergence dépendantes de l'activité du système à capacité commutée.

**[0006]** Plus précisément, alors que dans les cas d'une absence d'activité du système à capacité commutée, la valeur de référence VREF est bien entendu égale à la valeur de consigne VBG, ce n'est pas le cas en présence d'une activité.

**[0007]** Et, les valeurs de la tension de référence VREF aux points de fin de convergence diffèrent en outre en fonction du volume d'activité.

[0008] En cas d'une faible activité, c'est-à-dire si par exemple la valeur de la capacité du système à capacité commutée est faible ou bien si la fréquence de commutation des commutateurs est faible, les valeurs aux points de fin de convergence, quoique différentes de la valeur de consigne VBG, restent proches de cette valeur de consigne.

**[0009]** Ce n'est par contre pas le cas en présence d'une forte activité (capacité importante et/ou fréquence de commutation élevée).

[0010] Un second inconvénient réside dans la durée d'établissement de la tension de consigne, qui dépend de la largeur de bande passante de la boucle de régulation. Et, des fréquences de commutation élevées rendent les exigences de bande passante difficiles à atteindre et au prix d'une consommation élevée. C'est la raison pour laquelle le noeud où est présent la tension de référence

VREF est généralement connecté à un condensateur externe de forte valeur capacitive. Ce dernier agit alors comme un fournisseur de charge capacitive instantanée, ce qui permet de relâcher les contraintes sur la largeur de bande de la boucle, c'est-à-dire la boucle en courant continu. Cette approche ne peut toutefois pas être utilisée dans un système totalement intégré.

**[0011]** Selon un mode de mise en oeuvre et de réalisation, il est proposé un dispositif de génération d'une tension de référence destinée à un système du type à capacité commutée, permettant de réguler les valeurs aux points de fin de convergence sur la valeur de consigne et ce, d'une façon indépendante de l'activité.

**[0012]** Il est également proposé un dispositif de génération d'une telle tension de référence qui puisse être totalement intégré.

**[0013]** Selon un aspect, il est ainsi proposé un dispositif de génération d'une tension de référence, en particulier destinée à un système du type à capacité commutée, ladite tension de référence étant générée à partir d'une tension de consigne.

[0014] Selon une caractéristique générale de cet aspect, le dispositif comprend une boucle de régulation, possédant une première entrée pour recevoir la tension de consigne, et un étage de sortie agencé en suiveur de tension et rebouclé sur une deuxième entrée de ladite boucle ; le dispositif comporte un étage supplémentaire configuré pour délivrer ladite tension de référence, cet étage supplémentaire, couplé à l'étage de sortie, étant également agencé en suiveur de tension et apparié avec l'étage de sortie.

[0015] Avec une telle structure, dans une application à un système à capacité commuté, on découple le système à capacité commutée de l'étage de sortie de la boucle de régulation et chaque point de fin de convergence est alors le point de repos ou point d'équilibre de l'étage de sortie, c'est-à-dire que la valeur de chaque point de fin de convergence devient égale à la valeur d'équilibre de la boucle, c'est-à-dire la valeur de la tension de consigne.

[0016] Bien que la structure du dispositif de génération de la tension de référence puisse être une structure à entrée unique (« Single Ended » selon une dénomination anglosaxonne bien connue de l'homme du métier), le dispositif présente avantageusement une structure différentielle et l'étage supplémentaire comporte alors deux bornes de sortie délivrant la tension de référence différentielle.

[0017] Selon un mode de réalisation :

- l'étage de sortie comprend au moins un circuit de sortie comportant, connectés en série entre deux bornes d'alimentation, un transistor NMOS de sortie en montage suiveur avec un module résistif de sortie, et un élément de sortie formant transistor PMOS de sortie en montage suiveur avec ledit module résistif de sortie;

- l'étage supplémentaire comprend au moins un cir-

40

cuit supplémentaire comportant, connecté en série entre les deux bornes d'alimentation, un transistor NMOS supplémentaire en montage suiveur avec un module résistif supplémentaire et un élément supplémentaire formant un transistor PMOS supplémentaire en montage suiveur avec ledit module résistif supplémentaire;

les grilles des transistors NMOS sont reliées ensemble et les éléments formant le transistor PMOS sont reliées ensemble, les deux bornes du module résistif supplémentaire formant les dites deux bornes de sortie aptes à délivrer la tension de référence différentielle.

[0018] L'élément de sortie formant transistor PMOS peut être un transistor PMOS et l'élément supplémentaire formant transistor PMOS peut être un transistor PMOS. Dans ce cas, les grilles du transistor PMOS sont reliées ensemble.

[0019] Par contre, en fonction de la technologie utilisée, en particulier avec des technologies présentant de faibles tensions de seuil des transistors MOS et de faibles tensions d'alimentation, il est particulièrement avantageux de pouvoir émuler l'élément de sortie formant transistor PMOS en utilisant un transistor NMOS monté en diode « haute fréquence » (car la liaison drain-source est assurée par un condensateur), ce qui permet d'éviter que la tension de grille ne descende à des valeurs négatives (sous la masse).

[0020] Plus précisément, selon un tel mode de réalisation, l'élément de sortie formant transistor PMOS et l'élément supplémentaire formant transistor PMOS comprennent un premier transistor NMOS monté en inverseur couplé à un premier condensateur, un deuxième transistor NMOS monté en inverseur couplé à un deuxième condensateur, et un module à capacité commutée monté en parallèle avec le premier condensateur et le deuxième condensateur, les grilles des transistors NMOS montés en inverseur étant connectées ensemble par l'intermédiaire du module à capacité commutée. Le deuxième transistor NMOS couplé au deuxième condensateur fait office de diode haute fréquence.

**[0021]** Le coefficient d'appariement entre l'étage de sortie et l'étage supplémentaire est sans importance. Selon un mode de réalisation, chaque circuit de sortie est identique à chaque circuit supplémentaire, et le degré d'appariement est réalisé par le rapport entre le nombre de circuits supplémentaires et le nombre de circuits de sortie.

[0022] Lorsque l'on souhaite délivrer au système à capacité commutée un courant relativement fort, il est préférable que l'étage supplémentaire comporte un nombre de circuits supplémentaires identiques connectés en parallèle, ce nombre étant supérieur au nombre de circuits de sortie de l'étage de sortie. On choisira ainsi par exemple une structure comportant un seul circuit de sortie et plusieurs circuits supplémentaires identiques connectés en parallèle.

**[0023]** Selon un mode de réalisation, le dispositif comprend en outre un générateur de tension de bande interdite comportant un étage terminal possédant une résistance, ayant avantageusement une valeur programmable ou réglable, connectée en série entre deux transistors en montage source de courant ;

[0024] la boucle de régulation comporte un amplificateur opérationnel différentiel possédant une première entrée formant ladite première entrée de la boucle de régulation et connectée à l'une des bornes de la résistance dudit étage terminal de façon à recevoir une tension de bande interdite flottante en tant que tension de consigne ; [0025] l'amplificateur opérationnel comporte une deuxième entrée formant ladite deuxième entrée de la boucle de régulation ;

[0026] le module résistif de sortie du circuit de sortie de l'étage de sortie comprend deux résistances de sortie;

[0027] la boucle de régulation comporte un comparateur possédant une première entrée connectée à la borne commune des deux résistances de sortie, une deuxième entrée pour recevoir une tension de mode commun, et une sortie connectée à une entrée de mode commun de l'amplificateur différentiel;

[0028] l'autre borne de l'une des deux résistances est connectée à la deuxième entrée de l'amplificateur différentiel, tandis que l'autre borne de l'autre résistance est connectée à l'autre borne de la résistance dudit étage terminal du générateur de tension de borne interdite.

30 [0029] Lorsque la tension d'alimentation est inférieure à la tension de référence à délivrer, l'amplificateur opérationnel différentiel peut être avantageusement associé à une pompe de charge dont la sortie est connectée à la grille du transistor NMOS de sortie de chaque circuit de 35 sortie.

[0030] Selon un autre aspect, il est proposé un assemblage électronique comportant un dispositif de génération d'une tension de référence du type de celui défini ci avant, connecté à un système du type à capacité commutée.

**[0031]** D'autres avantages et caractéristiques de l'invention apparaîtront à l'examen de la description détaillée de modes de réalisation, nullement limitatifs, et des dessins annexés sur lesquels :

- la figure 1, déjà décrite, illustre des inconvénients d'une solution de l'art antérieur;

- la figure 2 illustre schématiquement un mode de réalisation d'un dispositif selon l'invention;

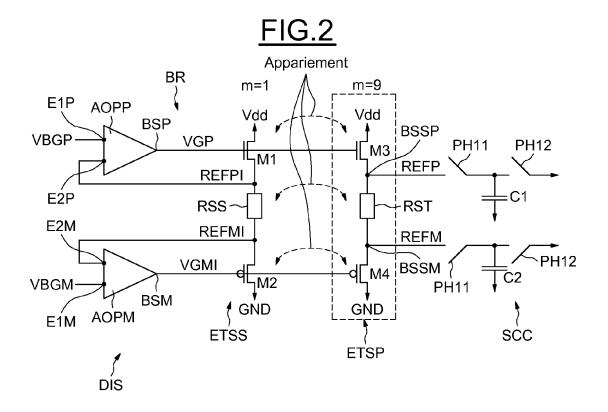

- la figure 3 illustre plus en détails un mode de réalisation d'une partie du dispositif de la figure 2;

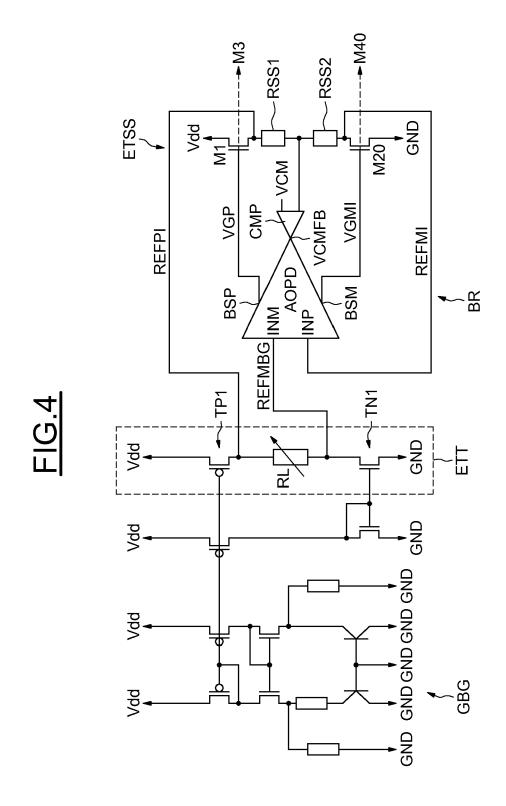

- la figure 4 illustre plus en détails un autre exemple de réalisation différentielle d'un dispositif selon l'invention;

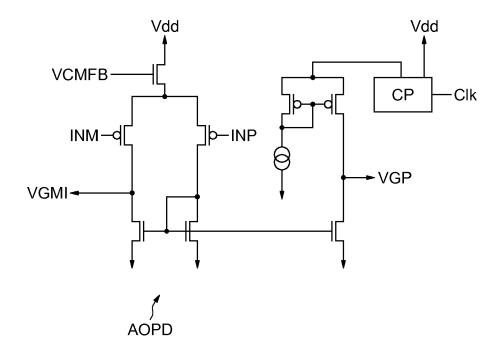

- la figure 5 illustre un exemple de solution utilisant une pompe de charge ; et

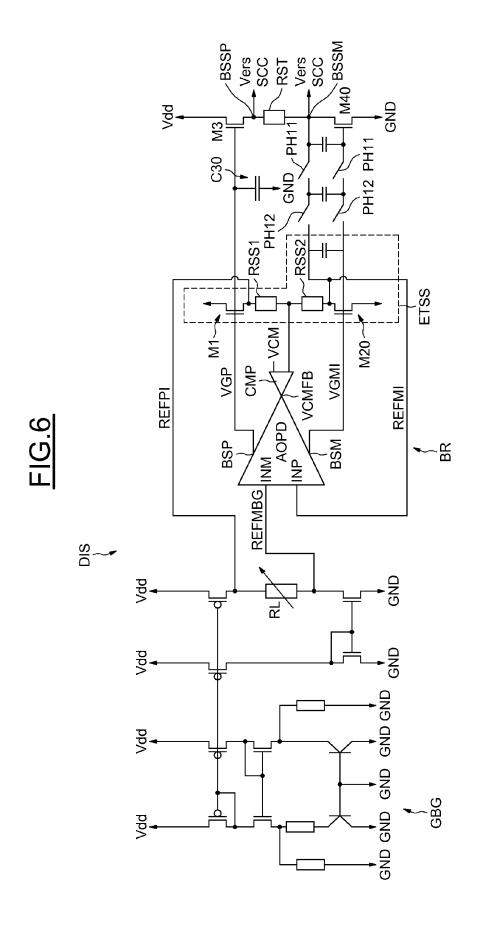

- la figure 6 illustre un mode de réalisation différentiel plus détaillé d'un dispositif selon l'invention.

3

40

45

[0032] Sur la figure 2, la référence DIS désigne de façon générale un dispositif de génération d'une tension de référence, ici une tension de référence différentielle REFP, REFM. Le dispositif DIS est, dans cette application particulière, connecté à un système à capacité commutée SCC, de structure classique et connue en soi et comportant ici deux condensateurs C1 et C2 capables d'être successivement chargés et déchargés par le biais de la tension de référence différentielle via des interrupteurs commandés par des signaux de commande PHI1, PHI2.

**[0033]** Le dispositif DIS comprend une boucle de régulation BR, ici de structure différentielle.

[0034] La boucle de régulation comporte ici deux amplificateurs opérationnels AOPM et AOPP. L'amplificateur opérationnel AOPP comporte une première entrée E1P tandis que l'amplificateur AOPM comporte une première entrée E1M. Ces deux premières entrées E1P et E1M forment une entrée différentielle pour recevoir une tension de consigne différentielle VBGP, VBGM.

[0035] L'amplificateur AOPP comporte une deuxième entrée E2P et l'amplificateur AOPM comporte une deuxième entrée E2M.

**[0036]** Il est par ailleurs prévu un étage de sortie ETSS agencé en suiveur de tension et rebouclé sur les deuxièmes entrées E2P et E2M des amplificateurs AOPP et AOPM.

**[0037]** L'étage de sortie ETSS comporte un circuit de sortie connecté entre deux bornes d'alimentation, à savoir la tension d'alimentation Vdd et la masse GND.

**[0038]** Ce circuit comporte, connectés en série entre les deux bornes d'alimentation, un transistor NMOS M1 en montage suiveur avec un module résistif formé ici d'une résistance RSS, et un transistor PMOS M2 en montage suiveur avec la résistance RSS.

[0039] Plus précisément, le drain du transistor M1 est relié à la tension Vdd tandis que la grille du transistor M1 est reliée à la borne de sortie BSP de l'amplificateur AOPP et reçoit la tension VGP.

**[0040]** La source du transistor M1 à laquelle est présente la tension REFPI, est connectée à la résistance RSS.

**[0041]** Le drain du transistor M2 est connecté à la masse. Sa grille, qui reçoit la tension VGMI, est connectée la borne de sortie BSM de l'amplificateur AOPM et la source du transistor M2, à laquelle est présente la tension REFMI, est connectée à l'autre borne de la résistance RSS.

**[0042]** Le dispositif DIS comporte en outre un étage supplémentaire ETSP. Cet étage supplémentaire ETSP comporte au moins un circuit supplémentaire, de structure identique à celle du circuit de sortie de l'étage de sortie.

**[0043]** Chaque circuit supplémentaire comporte donc, connectés en série entre la tension d'alimentation Vdd et la masse GND, un transistor NMOS M3 en montage suiveur avec un module résistif supplémentaire formé ici d'une résistance RST, et un transistor PMOS M4 en mon-

tage suiveur avec la résistance RST.

**[0044]** Les grilles des transistors M1 et M3 sont reliées ensemble et les grilles des transistors M2 et M4 sont reliées ensemble.

[0045] Par ailleurs, les sources des transistors M3 et M4 sont respectivement connectées aux deux bornes de la résistance RST et forment deux bornes de sortie BSSP et BSSM aptes à délivrer une tension de référence différentielle REFP, REFM au système à capacité commutée SCC.

[0046] L'étage supplémentaire ETSP est apparié (à l'étage de sortie ETSS). Le coefficient d'appariement est ici égal à 9. En pratique, en ce qui concerne les transistors, ceci peut être réalisé avec un transistor M3 ayant une largeur de canal neuf fois plus importante que la largeur de canal du transistor M1.

[0047] Il peut en être de même pour le transistor PMOS.

**[0048]** Cela étant, en pratique, cet appariement peut se traduire par la connexion en parallèle de neuf circuits supplémentaires de structure identique à celle du circuit de sortie M1, RSS et M2.

**[0049]** Le fait d'avoir un rapport d'appariement de 1 à 9 entre l'étage de sortie et l'étage supplémentaire permet en l'espèce, de pouvoir délivrer un courant de charge relativement fort au système SCC.

**[0050]** Chaque point de fin de convergence est atteint lorsque le condensateur C1 (respectivement C2) est chargé à la tension REFP (respectivement REFM).

[0051] A ce moment-là, il n'y a plus de courant qui passe dans les condensateurs C1 et C2, et le courant qui passe dans la résistance RST est égal au courant de repos de l'étage de sortie ETSS, c'est-à-dire au courant qui passe dans la résistance RSS. Or, à cet instant, compte tenu de la structure utilisée et de l'appariement entre les étages, la tension REFP, REFM est égale à la tension d'équilibre REFPI, REFMI, c'est-à-dire en fait à la tension de consigne souhaitée.

[0052] On obtient donc bien en sortie du dispositif, c'est-à-dire aux bornes BSSP et BSSM, une tension de référence dont la valeur en chaque point de fin de convergence est régulée sur la tension de consigne VBG. Par contre, la valeur moyenne de cette tension de référence bouge. On remarque donc que le fonctionnement de ce dispositif est totalement différent du fonctionnement d'un dispositif de l'art antérieur dans lequel c'est la valeur moyenne de la tension de référence qui est régulée sur la valeur de consigne alors que les valeurs de la tension de référence délivrées à chaque point de fin de convergence bougent.

**[0053]** En outre, dans le mode de réalisation illustré ici, cette régulation de la valeur de tension à chaque point de fin de convergence sur la valeur de la tension de consigne est indépendante de l'activité.

[0054] En fonction de la technologie utilisée, la grille du transistor M2, et par conséquent la grille du transistor M4, peut descendre sous la masse, et présenter donc une tension négative.

45

**[0055]** Pour éviter cet inconvénient, les transistors PMOS M2 et M4 montés en suiveurs, peuvent être remplacés par la structure illustrée sur la partie droite de la figure 3, qui permet d'émuler des transistors PMOS.

[0056] Plus précisément, les deux transistors PMOS M2 et M4 (partie gauche de la figure 3) sont remplacés par la structure de la partie droite de la figure 3 qui comporte un premier transistor NMOS M20 monté en inverseur, couplé à un premier condensateur C20, et un deuxième transistor NMOS M40 également monté en inverseur et couplé à un deuxième condensateur C40.

[0057] Un module à capacité commutée MCC est monté en parallèle avec le premier condensateur C20 et avec le deuxième condensateur C40. Les grilles des transistors montés en inverseur M20 et M40 sont connectées ensemble par l'intermédiaire du module à capacité commutée MMC.

**[0058]** En fonctionnement, il s'opère un transfert de charge entre les condensateurs C20 et C40 tant que les tensions grille/source des transistors M20 et M40 sont différentes.

**[0059]** Une telle structure permet de tout référencer par rapport à la masse et permet notamment une meilleure réjection d'alimentation.

[0060] Dans le mode de réalisation de la figure 4, les deux amplificateurs AOPP et AOPM de la figure 2 sont remplacés par un amplificateur AOPD complètement différentiel comportant deux entrées INM et INP, et deux sorties BSP et BSM.

[0061] La sortie BSP est connectée à la grille du transistor M1 de l'étage de sortie ETTS tandis que la sortie BSM est reliée à la grille du transistor M20 de l'étage de sortie ETTS.

[0062] Le module résistif de sortie de la figure 2 est formé ici de deux résistances identiques RSS1 et RSS2. [0063] La boucle de régulation BR comporte par ailleurs un comparateur CMP possédant une première entrée connectée à la borne commune des deux résistances RSS1 et RSS2, ainsi qu'une deuxième entrée pour recevoir une tension de mode commun VCM.

**[0064]** La sortie du comparateur délivre une tension VCMFB à une entrée de mode commun de l'amplificateur différentiel AOPD.

[0065] Dans ce mode de réalisation, la tension de consigne est une tension de bande interdite générée par un générateur de bande interdite GBG de structure classique. On rappelle ici qu'une tension de bande interdite (band gap voltage) est une tension, d'environ 1,2 volts, indépendante de la température.

[0066] Plus précisément, comme illustré sur la figure 4, le générateur GBG comporte une source de tension apte à générer une tension de bande interdite couplée à des miroirs de courant. Ce générateur de tension de bande interdite GBG comporte par ailleurs un étage terminal ETT possédant une résistance variable RL connectée en série entre deux transistors TP1 et TN1 en montage source de courant.

[0067] La tension de consigne flottante REFMBG pré-

sente à l'une des bornes de la résistance RL, est délivrée à l'entrée INM de l'amplificateur AOPD.

**[0068]** L'autre entrée INP de l'amplificateur AOPD est connectée à la borne de la résistance RSS2 différente de la borne commune avec la résistance RSS1.

**[0069]** De même, l'autre borne de la résistance RSS1, différente de cette borne commune, est connectée à l'autre borne de la résistance variable RL.

**[0070]** Un tel mode de réalisation permet, pour un système différentiel, de générer la tension de consigne (tension de bande interdite) en mode « flottant », autour de la tension de mode commun VCM.

[0071] Les trois résistances du générateur de tension de borne interdite GBG ainsi que la résistance variable RL sont appariées, de façon à pouvoir générer le niveau requis pour la tension de consigne. En outre, le fait que la résistance RL ait une valeur résistive réglable ou programmable permet par exemple de générer quatre niveaux de tension de consigne différents, par exemple un niveau 2vpp; 1,6vpp; 1,4vpp ou 1vpp, où vpp désigne la tension crête-crête.

[0072] Lorsque la tension VGP délivrée par l'amplificateur opérationnel AOPD a une valeur supérieure à la tension d'alimentation Vdd, il est avantageusement prévu, comme illustré sur la figure 5, d'associer une pompe de charge CP à l'amplificateur opérationnel différentiel AOPD. La sortie de cette pompe de charge est connectée à la sortie BSP de l'amplificateur AOPD et par conséquent à la grille du transistor NMOS M1 du circuit de sortie de l'étage de sortie ETS.

**[0073]** Le mode de réalisation de la figure 6 reprend les différents éléments qui viennent d'être décrits en référence aux figures précédentes et notamment le générateur de tension de bande interdite GBG, ainsi que la structure d'émulation des transistors PMOS par les transistors NMOS montés en diode.

**[0074]** Outre ces différents éléments, un condensateur additionnel C30 est connecté entre les grilles des transistors M1 et M3 et la masse GND.

[0075] Ce transistor permet notamment d'améliorer la réjection d'alimentation.

**[0076]** Un tel mode de réalisation permet une amélioration du rapport de réjection de l'alimentation (PSRR : Power Supply Rejection Ratio, selon une dénomination anglo-saxonne bien connue de l'homme du métier).

[0077] Ce paramètre PSRR est amélioré par rapport à la tension d'alimentation Vdd. En effet, en cas de variation de l'alimentation Vdd, on a une atténuation de la variation du courant injecté due au gain du transistor M3.

[0078] Le paramètre PSRR est également amélioré par rapport à la masse. En effet, le condensateur C30 excite la grille du transistor M1 simultanément à la source du transistor M20. Les différents modes de réalisation qui viennent d'être décrits permettent d'offrir notamment les avantages suivants :

en terme de bruit, la boucle de régulation est une boucle basse fréquence avec un condensateur de

5

10

15

20

25

30

35

40

45

50

- découplage ayant une valeur capacitive importante (condensateur C30); et il en résulte par conséquent une forte limitation du bruit thermique;

- l'étage supplémentaire, qui est une réplique de l'étage de sortie, est en fait un simple étage transconducteur. De ce fait, il n'apporte pas de contribution propre et il peut donc être considéré comme un commutateur en série;

- le système est modulaire. En effet, le nombre de circuits supplémentaires de l'étage supplémentaire peut être augmenté facilement en fonction notamment de l'augmentation de la charge capacitive (C1, C2) ou de la fréquence de commutation;

- il n'est pas nécessaire, comme dans l'art antérieur, de connecter un condensateur externe de couplage aux bornes de sortie du dispositif de génération de la tension de référence. Ceci offre notamment un gain de deux plots (pads, en langue anglaise) dans l'anneau des entrées/sorties (IO ring) entourant classiquement un circuit intégré;

- le système est particulièrement stable et il présente un paramètre PSRR élevé.

#### Revendications

- 1. Dispositif de génération d'une tension de référence, en particulier destinée à un système du type à capacité commutée, à partir d'une tension de consigne, caractérisé en ce qu'il comprend une boucle de régulation (BR) possédant une première entrée pour recevoir la tension de consigne (VBG) et un étage de sortie (ETSS) agencé en suiveur de tension et rebouclé sur une deuxième entrée de ladite boucle, et un étage supplémentaire (ETSP) configuré pour délivrer ladite tension de référence, cet étage supplémentaire, couplé à l'étage de sortie, étant également agencé en suiveur de tension et apparié avec l'étage de sortie.

- Dispositif selon la revendication 1, présentant une structure différentielle et dans lequel l'étage supplémentaire comporte deux bornes de sortie (BSSP, BSSM) délivrant la tension de référence différentielle.

- 3. Dispositif selon la revendication 2, dans lequel l'étage de sortie (ETSS) comprend au moins un circuit de sortie comportant, connectés en série entre deux bornes d'alimentation, un transistor NMOS de sortie (M1) en montage suiveur avec un module résistif de sortie (RSS) et un élément de sortie formant transistor PMOS de sortie (M2; M20) en montage suiveur avec ledit module résistif de sortie, l'étage supplémentaire (ETSP) comprend au moins un circuit supplémentaire comportant, connectés en série entre les deux bornes d'alimentation, un transistor NMOS supplémentaire (M3) en montage suiveur avec un

- module résistif supplémentaire (RST) et un élément supplémentaire formant transistor PMOS supplémentaire (M4; M40) en montage suiveur avec ledit module résistif supplémentaire, les grilles des transistors NMOS (M1, M3) étant reliées ensemble et les éléments formant transistors PMOS étant reliés ensemble, les deux bornes du module résistif supplémentaire (RST) formant lesdites deux bornes de sortie apte à délivrer ladite tension de référence différentielle.

- 4. Dispositif selon la revendication 3, dans lequel l'élément de sortie formant transistor PMOS est un transistor PMOS (M2) et l'élément supplémentaire formant transistor PMOS est un transistor PMOS (M4), les grilles des transistors PMOS étant reliées ensemble.

- 5. Dispositif selon la revendication 3, dans lequel l'élément de sortie formant transistor PMOS et l'élément supplémentaire formant transistor PMOS comprennent un premier transistor NMOS monté en inverseur (M20) couplé à un premier condensateur (C20), un deuxième transistor NMOS monté en inverseur (M40) couplé à un deuxième condensateur (C40) et un module à capacité commutée (MCC) monté en parallèle avec le premier condensateur et le deuxième condensateur, les grilles des transistors NMOS montés en inverseur étant connectées ensemble par l'intermédiaire du module à capacité commutée.

- 6. Dispositif selon l'une des revendications 3 à 5, dans lequel chaque circuit de sortie est identique à chaque circuit supplémentaire et l'étage supplémentaire comporte un nombre de circuits supplémentaires identiques connectés en parallèle supérieur au nombre de circuits de sortie de l'étage de sortie.

- Dispositif selon l'une des revendications 2 à 6, comprenant en outre un générateur de tension de bande interdite (GBG) comportant un étage terminal (ETT) possédant une résistance (RL) connectée en série entre deux transistors en montage source de courant (TP1, TN1), dispositif dans lequel la boucle de régulation (BR) comporte un amplificateur opérationnel différentiel (AOPD) possédant une première entrée (INM) formant ladite première entrée de la boucle de régulation et connectée à l'une des bornes de la résistance (RL) dudit étage terminal de façon à recevoir une tension de bande interdite flottante (REFM-BG) en tant que tension de consigne, une deuxième entrée formant ladite deuxième entrée de la boucle de régulation, dans lequel le module résistif de sortie comprend deux résistance de sortie (RSS1, RSS2), dans lequel la boucle de régulation comporte un comparateur (CMP) possédant une première entrée connectée à la borne commune des deux résistances de sortie, une deuxième entrée pour recevoir

25

30

35

40

45

une tension de mode commun (VCM) et une sortie connectée à une entrée de mode commun de l'amplificateur différentiel, l'autre borne de l'une des deux résistances (RSS2) étant connectée à la deuxième entrée (INP) de l'amplificateur différentiel, l'autre borne de l'autre résistance (RSS1) étant connectée à l'autre borne de la résistance (RL) dudit étage terminal (ETT).

- **8.** Dispositif selon la revendication 7, dans lequel la résistance (RL) de l'étage terminal a une valeur réglable.

- 9. Dispositif selon la revendication 7 ou 8, dans lequel l'amplificateur opérationnel différentiel (AOPD) est associé à une pompe de charge (CP) dont la sortie est connectée à la grille du transistor NMOS de sortie de chaque circuit de sortie.

- 10. Assemblage électronique comportant un dispositif 20 de génération de tension (DIS) selon l'une des revendications 1 à 9, connecté à un système de type à capacité commutée (SCC).

55

# FIG.1 Art antérieur

FIG.3

# FIG.5

### RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande EP 10 16 4554

| Catégorie                                    | Citation du document avec<br>des parties pertin                                                                                                                                                       |                                                                                           | esoin,                                                                                                                  | Revendication concernée                                                      | CLASSEMENT DE LA<br>DEMANDE (IPC)       |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|

| Υ                                            | THOMAS TOIFL ET AL: regulator with high supply-rejection us in 45nm CMOS SOI" SOLID-STATE CIRCUIT A-SSCC '08. IEEE AS NJ, USA, 3 novembre pages 157-160, XPO3 ISBN: 978-1-4244-26 * le document en en | "A small-ar-bandwidth ing a regulat S CONFERENCE, IAN, IEEE, PI 2008 (2008-1 1372987 04-1 | ed replica<br>2008.<br>SCATAWAY,<br>1-03),                                                                              |                                                                              | INV.<br>G05F1/575<br>ADD.<br>H02M3/07   |

| '                                            | re document en en                                                                                                                                                                                     |                                                                                           |                                                                                                                         | 2-4,0-10                                                                     |                                         |

| Υ                                            | US 2006/125463 A1 (<br>AL) 15 juin 2006 (2<br>* alinéa [0055] - a<br>9-12 *                                                                                                                           | 006-06-15)                                                                                |                                                                                                                         | 2-4,6-10                                                                     |                                         |

| A                                            | GERRIT W DEN BESTEN<br>V-to-3.3 V Voltage<br>Digital IC's in 3.3<br>IEEE JOURNAL OF SOL<br>SERVICE CENTER, PIS<br>vol. 33, no. 7,<br>1 juillet 1998 (199<br>ISSN: 0018-9200<br>* le document en en    | Regulator for<br>V CMOS Techn<br>ID-STATE CIRC<br>CATAWAY, NJ,<br>8-07-01), XPO           | Supplying ology" UITS, IEEE US,                                                                                         | 1-10                                                                         | DOMAINES TECHNIQUES<br>RECHERCHES (IPC) |

| X                                            |                                                                                                                                                                                                       |                                                                                           |                                                                                                                         |                                                                              |                                         |

| Le pre                                       | ésent rapport a été établi pour tou                                                                                                                                                                   | ites les revendications                                                                   |                                                                                                                         |                                                                              |                                         |

| •                                            | Lieu de la recherche                                                                                                                                                                                  | Date d'achèvement                                                                         | de la recherche                                                                                                         |                                                                              | Examinateur                             |

|                                              | La Haye                                                                                                                                                                                               | 24 sep                                                                                    | tembre 2010                                                                                                             | ) Ari                                                                        | as Pérez, Jagoba                        |

| X : parti<br>Y : parti<br>autre<br>A : arriè | ATEGORIE DES DOCUMENTS CITE iculièrement pertinent à lui seul iculièrement pertinent en combinaison e document de la même catégorie pre-plan technologique ilgation non-écrite                        | avec un [                                                                                 | : théorie ou principe<br>: document de brev<br>date de dépôt ou a<br>) : cité dans la demai<br>. : cité pour d'autres r | l a la base de l'in<br>et antérieur, mai<br>près cette date<br>nde<br>aisons | vention<br>s publié à la                |

### RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande EP 10 16 4554

| Catégorie                                                | Citation du document avec<br>des parties pertir                                                                                                                                                               |                   |                                                                                                                                                                    | endication<br>ncernée                | CLASSEMENT DE LA<br>DEMANDE (IPC)       |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------|

| А                                                        | US 2003/052659 A1 (<br>[JP] ET AL) 20 mars<br>* abrégé; figure 1                                                                                                                                              | MONOMOUSHI MA     | SAHIKO<br>3-20)                                                                                                                                                    | 10                                   |                                         |

|                                                          |                                                                                                                                                                                                               |                   |                                                                                                                                                                    | -                                    | DOMAINES TECHNIQUES<br>RECHERCHES (IPC) |

|                                                          |                                                                                                                                                                                                               |                   |                                                                                                                                                                    |                                      |                                         |

|                                                          | ésent rapport a été établi pour tou<br>ieu de la recherche                                                                                                                                                    | Date d'achèvement |                                                                                                                                                                    |                                      | Examinateur                             |

|                                                          | La Haye                                                                                                                                                                                                       | ·                 | tembre 2010                                                                                                                                                        | Aria                                 | as Pérez, Jagoba                        |

| X : parti<br>Y : parti<br>autre<br>A : arriè<br>O : divu | ATEGORIE DES DOCUMENTS CITÉ<br>culièrement pertinent à lui seul<br>culièrement pertinent en combinaisor<br>document de la même catégorie<br>re-plan technologique<br>lgation non-écrite<br>ument intercalaire | avec un C<br>L    | : théorie ou principe à la<br>: document de brevet al<br>date de dépôt ou après<br>): cité dans la demande<br>: cité pour d'autres raiso<br>: membre de la même fa | ntérieur, mais<br>s cette date<br>ns | s publié à la                           |

### ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

EP 10 16 4554

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Les dits members sont contenus au fichier informatique de l'Office européen des brevets à la date du Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

24-09-2010

|                | Document brevet cité<br>au rapport de recherche |    | Date de<br>publication |                            | Membre(s) de la<br>famille de brevet(s)                              | Date de<br>publication                                             |

|----------------|-------------------------------------------------|----|------------------------|----------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------|

|                | US 2006125463                                   | A1 | 15-06-2006             | TW                         | 259940 B                                                             | 11-08-2006                                                         |

|                | US 2003052659                                   | A1 | 20-03-2003             | CN<br>JP<br>JP<br>KR<br>TW | 1421757 A<br>3813477 B2<br>2003084723 A<br>20030023521 A<br>581945 B | 04-06-2003<br>23-08-2006<br>19-03-2003<br>19-03-2003<br>01-04-2004 |

|                |                                                 |    |                        |                            | 301743 0                                                             |                                                                    |

|                |                                                 |    |                        |                            |                                                                      |                                                                    |

|                |                                                 |    |                        |                            |                                                                      |                                                                    |

|                |                                                 |    |                        |                            |                                                                      |                                                                    |

|                |                                                 |    |                        |                            |                                                                      |                                                                    |

|                |                                                 |    |                        |                            |                                                                      |                                                                    |

|                |                                                 |    |                        |                            |                                                                      |                                                                    |

|                |                                                 |    |                        |                            |                                                                      |                                                                    |

| 0460           |                                                 |    |                        |                            |                                                                      |                                                                    |

| EPO FORM P0460 |                                                 |    |                        |                            |                                                                      |                                                                    |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82