# (11) EP 2 261 953 A2

(12)

# **EUROPEAN PATENT APPLICATION**

(43) Date of publication: 15.12.2010 Bulletin 2010/50

(21) Application number: 10075634.5

(22) Date of filing: 15.05.2002

(51) Int CI.:

H01L 21/00 (2006.01) G02B 6/42 (2006.01) G02B 6/12 (2006.01) G02B 6/26 (2006.01) G06G 7/48 (2006.01)

(84) Designated Contracting States:

DE FR GB

(30) Priority: 17.05.2001 US 859693 17.05.2001 US 859297 17.05.2001 US 859647 17.05.2001 US 859239 17.05.2001 US 859338 17.05.2001 US 859279 17.05.2001 US 859769 17.05.2001 US 859321 17.05.2001 US 859663

(62) Document number(s) of the earlier application(s) in accordance with Art. 76 EPC:

17.05.2001 US 859786

02752045.1 / 1 402 294

(71) Applicant: Optronx, Inc.

Allentown, PA 18106 (US)

(72) Inventor: Deliwala, Shrenik

Orefield PA Pennsylvania 18069 (US)

(74) Representative: Howson, Richard G.B.

Kilburn & Strode LLP

20 Red Lion Street

London WC1R 4PJ (GB)

# (54) Optical waveguide devices with additional polysilicon layers

(57) A device for coupling light into/from an integrated optical/electronic circuit disposed at least in part in a wafer having an insulator layer (152, 104) and an upper semiconductor layer that includes an optical waveguide (160). The integrated optical/electronic circuit includes at least one active optical waveguide device (150), and at least one passive optical waveguide device (800),

each of which is associated with, at least in part, in the upper semiconductor layer. In one aspect, the passive optical waveguide device (800) can be created by deposing a polysilicon layer (191) on the upper semiconductor layer. In another aspect, the passive optical waveguide device can be created by etching a Total Internal reflection (TIR) boundary within the upper semiconductor layer.

# **Description**

5

10

15

20

30

35

40

45

50

55

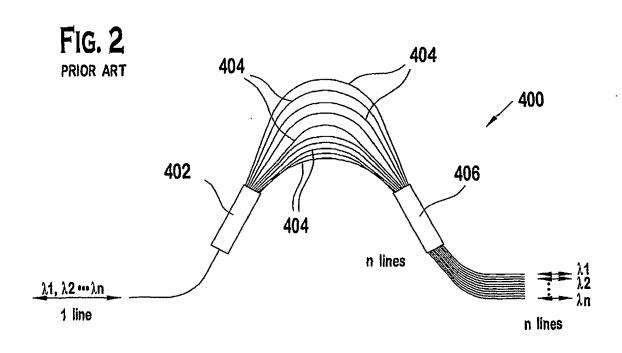

#### Cross-Reference to Related Applications

**[0001]** This application is a continuation in part to U.S. Patent Application Serial No. 09/991,542, filed November 10, 2001 (incorporated herein by reference), which is a continuation in part to U.S. Patent Application Serial No. 09/859,693, filed May 17, 2001 (incorporated herein by reference).

#### Field of the Invention

**[0002]** This invention relates to optical waveguide devices, and more particularly to passive optical waveguide devices, as well as integrated optical circuits including passive optical waveguide devices.

#### Background of the Invention

**[0003]** In the integrated circuit industry, there is a continuing effort to increase device speed and increase device densities. Optical systems and technologies promise to deliver increasing speed and circuit packing density in the future. Optical waveguides typically include optical waveguide devices to provide optical functionality. Such optical waveguide devices can perform a variety of optical functions in integrated optical waveguide circuits such as optical signal transmission and attenuation.

**[0004]** In one aspect, optical waveguide devices include a variety of passive optical waveguide devices and/or a plurality of active optical waveguide devices. For example, certain gratings, lenses, filters, photonic crystals, and the like can be fabricated as passive optical waveguide devices. Similarly, active optical waveguide devices may function as filters, gratings, lenses, deflectors, switches, transmitters, receivers, and the like. Availability of a variety of passive and active optical waveguide devices and/or electronic devices provides a desired range of functionality. The availability of these devices is useful in making optical waveguide circuits simpler to design and fabricate.

**[0005]** A passive optical device does not change its function over a period of time excluding device degradations. A large variety of passive optical devices that include, e.g., optical fibers, slab optical waveguides, or thin film optical waveguides, may provide many optical functions. As such, the output or optical functionality of passive optical waveguide devices cannot be tuned or controlled. Additionally, passive active devices cannot be actuated (i.e., or turned on and off) depending on the present use of a region of an optical waveguide.

**[0006]** Many active optical waveguide devices such as modulators, filters, certain lenses, and certain gratings are precisely tunable. Tunability of certain active optical waveguide devices is important in making them more functional and competitive with present electronic circuits and devices.

[0007] Silicon-on-Insulator (SOI) and CMOS represent two technologies that have undergone a considerable amount of research and development relating to electronic devices and circuits. SOI technology can also integrate optical devices and circuits. It would be desirable to provide active optical waveguide device functionality and/or passive optical waveguide device functionality based largely on the CMOS devices and technology as well as manufacturing methods that allow for simultaneous fabrication of optically active and passive waveguide elements.

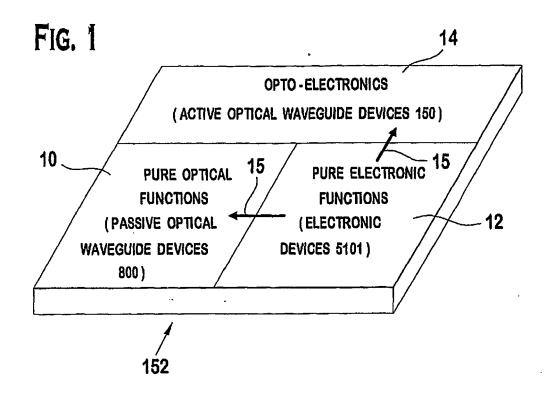

[0008] One embodiment of prior-art optical waveguide device is an arrayed waveguide grating (AWG) as shown in FIG. 2. The AWG 400 includes an input coupler 402, a plurality of arrayed waveguides 404, and an output coupler 406. The AWG 400 can be configured as a wavelength-division demultiplexer (if light signals travel from the left to the right in FIG. 2) or a wavelength-division multiplexer (if light signals travel from the right to the left in FIG. 2). In the AWG 400, each arrayed waveguide 404 has a different length between the input coupler 402 and the output coupler 406. The difference in length between each one of the different arrayed waveguides 404 corresponds to an optical phase shift of  $m2\pi$ , where m is an integer for the central design wavelength of the light that is applied to the AWG 400. Since each arrayed waveguide 404 has a different length, the light passing through the longer arrayed waveguides arrives at the output coupler 406 later than the light passing through the shorter arrayed waveguides.

**[0009]** AWGs 400, however, are difficult and expensive to produce. Each arrayed waveguide 404 is measured and formed separately. The operation of the AWG 400 requires that the different arrayed waveguides 404 differ in length by a distance equal to an  $m2\pi$  optical phase shift for the central design wavelength that the AWG is designed to multiplex/demultiplex. The cross-sectional area and the material of each arrayed waveguide 404 of the AWG 400 is constant to maintain the effective mode index (or the propagation constant  $\beta$ ) of the different arrayed waveguides 404, and therefore provide a uniform velocity of light traveling through the different arrayed waveguides. As such, in present designs, each arrayed waveguide 404 of the AWG 400: a) has precisely calculated and measured lengths; b) has the same precisely produced and measured cross-sectional areas; c) has different lengths, such that the difference between the successive lengths,  $\Delta I$  is such that  $\beta \Delta I = m2\pi$ ; and d) is smoothly-curved through a gradual radius of curvature to reduce bending losses of light flowing through the arrayed waveguide 404. Due to these requirements, the AWG 400 is challenging to

2

design and fabricate since it is difficult to ensure the precise relative lengths of each one of the arrayed waveguides 404. Both the precision requirements and fabrication tolerances place extreme requirements on the manufacturing process. These waveguides traditionally use different indices of glass to make the core and the cladding. Silicon is used in the fabrication process but does not participate in the optical function. A 6" Si wafer may be able to accommodate 5-50 AWGs 400 depending on the design requirements and the available index contrast between the core and the cladding, which is generally of the order of a few percent. The waveguides in AWGs are designed to be polarization independent so that both the polarizations of the input light are more or less treated equally. Considerable time and human effort is therefore necessary to produce precise AWGs 400.

[0010] It would therefore be desirable to fabricate passive optical waveguide devices (such as AWGs) using standard CMOS fabrication techniques which, when combined with active optical functions such as a modulator on the same substrate, could form the basis of a WDM system on a chip. It would also be desirable to fabricate such passive optical waveguide devices as AWGs and interferometers in a manner that the lengths and shapes of the arrayed waveguides are simple to accurately calculate, measure, and produce. Furthermore, it would be desired to apply active optical waveguide devices as tuning devices associated with optical circuits including passive optical waveguide devices, wherein much of the fabrication errors inherent in passive optical waveguide devices or device degradation over time can be dynamically tuned out by tuning the associated active optical waveguide devices.

#### Summary of the Invention

15

20

30

35

40

45

50

55

[0011] One aspect of the invention relates to a passive optical waveguide device deposited on a wafer. The wafer includes an insulator layer and an upper semiconductor layer formed at least in part from silicon. The upper silicon layer forms at least part of an optical waveguide, such as a slab waveguide. The passive optical waveguide device includes an optical waveguide, a gate oxide, and a polysilicon layer (i.e., a layer formed at least in part from polysilicon) In some embodiments, the optical waveguide is formed within the upper semiconductor layer, a gate oxide layer that is deposited above the upper semiconductor layer, and a polysilicon layer that is deposited above the gate oxide layer. The polysilicon layer projects a region of static effective mode index within the optical waveguide. The region of static effective mode index has a different effective mode index than the optical waveguide outside of the region of static effective mode index. The region of static effective mode index has a depth extending within the optical waveguide. A value and a position of the effective mode index within the region of static effective mode index remains substantially unchanged over time. The region of static effective mode index applies a substantially unchanging optical function to light travelling through the region of static effective mode index over the lifetime of the passive optical waveguide device.

[0012] As explained below, the terms "gate oxide" or "gate oxide layer" as used herein refer to the type of oxides (or other electrically insulating materials including glass) that are typically used to form a gate regardless of whether the material is used functionally to form all or part of a gate. Each region of static/altered effective mode index described herein is due to the presence of polysilicon deposited on the "gate oxide" layer, and controlled (at least in part) by controlling the shape or dimensions of the polysilicon. The polysilicon acts to guide light though one or more layers of a wafer (similar to a rib waveguide) and, depending on the width and height of the polysilicon, acts to create a region with a different effective mode index or having a different propagation constant, as compared to remaining regions on the wafer. Various "photonic guides" may be created simply by the presence of polysilicon deposited on the gate oxide. Optionally, a layer below the gate oxide layer (e.g., an upper silicon layer of an SOI substrate) may also be etched to create total reflection boundaries that also serve to define the "photonic guide." By positioning different "photonic guides" (or polysilicon portions) in appropriate geometric relationships on a substrate as described herein, many useful passive and/or active optical devices may be fabricated using well understood manufacturing steps of electronic device manufacturing. Different portions of the "photonic guides" may be made active by construction of appropriate electrodes for diode or transistor action and local, variable effective mode index created, as described below. Exemplary passive complex functions formed using the "photonic guides" described herein include AWG's for separation and combining of different colors of light in the waveguide, interferometers, lenses, and gratings.

**[0013]** One aspect of the invention relates to an integrated optical circuit comprising an optical waveguide and an evanescent coupler. The optical waveguide is located on a wafer. The optical waveguide is formed from an upper semiconductor layer of the wafer, a gate oxide layer deposited on the upper semiconductor layer, and a polysilicon layer deposited on the gate oxide layer. The evanescent coupling region is formed at least in part from a gap portion that optically couples light to the upper semiconductor layer of the optical waveguide using the evanescent coupling region. Light can be coupled from outside of the passive optical waveguide device via the evanescent coupling region into the optical waveguide. Alternatively, light can be coupled from the optical waveguide through the evanescent coupling region out of the passive optical waveguide device. The polysilicon layer projects a region of static effective mode index within the optical waveguide, wherein the region of static effective mode index has a different effective mode index than the optical waveguide outside of the region of static effective mode index. A value and a position of the effective mode index within the region of static effective mode index remains substantially unchanged over time and applies a substantially

unchanging optical function to light travelling through the region of static effective mode index within the optical waveguide over the lifetime of the passive optical waveguide device.

[0014] One aspect of the invention relates to an optical waveguide device that controls the transmission of light through an optical waveguide. The optical waveguide device comprises an active optical waveguide device and a passive optical waveguide device. The active optical waveguide device is formed at least in part on a semiconductor layer and includes an electrode portion. A region of altered effective mode index is created by the active optical waveguide device. An effective mode index of the region of altered effective mode index within the optical waveguide is controlled by application of an electric voltage to the electrode portion in a manner that alters a free carrier density of the region of altered effective mode index. Changing the electric voltage to the electrode portion changes the effective mode index in the region of altered effective mode index. The passive optical waveguide device is formed at least in part from a polysilicon layer deposited on the semiconductor layer. An effective mode index of a region of static effective mode index within the optical waveguide is created by the polysilicon layer of the passive optical waveguide device. The polysilicon layer has a shape and a height. The effective mode index of the region of static effective mode index is related to the shape of the polysilicon layer and the height of the polysilicon layer. A value and a position of the effective mode index within the region of static effective mode index remains substantially unchanged over time and applies a substantially unchanging optical function to light travelling through the region of static effective mode index over the lifetime of the passive optical waveguide device. The optical waveguide forms at least a part of both the active optical waveguide device and the passive optical waveguide device. The optical waveguide couples the active optical waveguide device and the passive optical waveguide device, and the optical waveguide is formed at least in part using the semiconductor layer. In one aspect, the active optical waveguide device can be configured to provide electronic transistor action.

10

20

30

35

40

45

50

55

[0015] One aspect of the present invention relates to an interferometer comprising at least one optical waveguide, a first passive optical waveguide segment, and a second passive optical waveguide segment. The at least one optical waveguide includes at least one gate oxide layer deposited on a semiconductor layer of a wafer and a polysilicon layer deposited on the at least one gate oxide layer. The first passive optical waveguide segment includes a first portion of the polysilicon layer. The first portion projects a first region of static effective mode index within the at least one optical waveguide. The first region of static effective mode index has a different effective mode index than the at least one optical waveguide outside of the first region of static effective mode index. A value and a position of the effective mode index within the first region of static effective mode index of the first passive optical waveguide segment remains substantially unchanged over time. The first region of static effective mode index therefore applies a substantially unchanging optical function to light travelling through the first region of static effective mode index within the at least one optical waveguide over the lifetime of the first passive optical waveguide segment. The second passive optical waveguide segment includes a second portion of the polysilicon layer. The second portion projects a second region of static effective mode index within the at least one optical waveguide. The second region of static effective mode index has a different effective mode index than the at least one optical waveguide outside of the second region of static effective mode index. A value and a position of the effective mode index within the second region of static effective mode index of the second passive optical waveguide segment remains substantially unchanged over time and applies a substantially unchanging optical function to light travelling through the second region of static effective mode index within the at least one optical waveguide over the lifetime of the second passive optical waveguide segment. A length of the first passive optical waveguide segment equals a length of the second passive optical waveguide segment. The first and second passive optical waveguide segments are coupled to each other and together form at least in part the optical waveguide. The first and second passive optical waveguide segments and the optical waveguide are each formed at least in part from the semiconductor layer. The first region of static effective mode index has a different effective mode index than the second region of static effective mode index. In one embodiment, the difference in effective mode between the first and the second region of static effective mode index is at least partially provided by a difference in cross-sectional areas respectively between the first portion of the polysilicon layer and the second portion of the polysilicon layer. In another embodiment, the difference in effective mode between the first and the second region of static effective mode index is at least partially provided by a difference in axial lengths respectively between the first portion of the polysilicon layer and the second portion of the polysilicon layer.

**[0016]** One aspect of the present invention relates to an arrayed waveguide grating (AWG) deposited on a wafer that includes an upper semiconductor layer comprising a first port, a plurality of second ports, a gate oxide layer, a polysilicon layer, and a plurality of arrayed waveguides. The gate oxide layer is deposited above the upper semiconductor layer. The polysilicon layer is deposited above the gate oxide layer. The plurality of arrayed waveguides extend between the first port and each one of the plurality of second ports. Each one of the plurality of arrayed waveguides are at least partially formed by the upper semiconductor layer, the polysilicon layer, and the gate oxide layer. Each one of the arrayed waveguides is associated with a portion of the polysilicon layer. Each portion of the polysilicon layer has a different cross-sectional area, wherein each of the arrayed waveguides has a different effective mode index. A value and a position of the effective mode index associated with each of the respective arrayed waveguides remains substantially unchanged over time and applies a substantially unchanging optical function to light travelling through the respective

arrayed waveguide over the lifetime of the respective arrayed waveguide. In one embodiment, the different effective mode indexes in each of the respective arrayed waveguides is provided by a difference in cross sectional area of the polysilicon layer associated with each one of the plurality of arrayed waveguides. In another embodiment, the different effective mode indexes in each of the respective arrayed waveguides is provided by a difference in axial length of the polysilicon layer associated with each one of the plurality of arrayed waveguides.

[0017] One embodiment of the present invention relates to an optical waveguide device that controls the transmission of light through an optical waveguide. The optical waveguide device includes a first passive optical waveguide device and a second passive optical waveguide device. The first passive optical waveguide device is etched, at least in part, in a semiconductor layer of a wafer. A value and a position of an effective mode index within the first passive optical waveguide device remains substantially unchanged over time and applies a substantially unchanging optical function to light travelling through the first passive optical waveguide device over the lifetime of the first passive optical waveguide device. The second passive optical waveguide device is formed at least in part from a polysilicon layer deposited above an unetched portion of the semiconductor layer. The effective mode index of a region of static effective mode index within the optical waveguide is created by the polysilicon layer of the second passive optical waveguide device. The effective mode index of the region of static effective mode index is related to a shape of the polysilicon layer and a height of the polysilicon layer. A value and a position of the effective mode index within the region of static effective mode index remains substantially unchanged over time, and applies a substantially unchanging optical function to light travelling through the region of static effective mode index over the lifetime of the second passive optical waveguide device. The optical waveguide forms at least a part of both the first passive optical waveguide device and the second passive optical waveguide device. The optical waveguide couples the first passive optical waveguide device and the second passive optical waveguide device, and the optical waveguide is formed at least in part using the semiconductor layer.

[0018] One aspect of the present invention relates to a device that provides for the transmission of light through a first optical waveguide and a second optical waveguide. The device includes a semiconductor layer and a polysilicon coupler. The semiconductor layer includes at least one etched portion between first and second unetched portions. The first optical waveguide includes the first unetched portion and a first total internal reflection (TIR) boundary between the first unetched portion and the at least one etched portion. The second optical waveguide includes the second unetched portion and a second TIR boundary between the at least one unetched portion and the second etched portion. The polysilicon coupler at least partially overlaps the etched portion of the semiconductor layer. The polysilicon coupler optically couples the first optical waveguide and the second optical waveguide, wherein light can flow from the first optical waveguide via the polysilicon coupler portion to the second optical waveguide.

[0019] One aspect of the present invention relates to a passive optical waveguide device, comprising a silicon layer of a Silicon-on-Insulator (SOI) wafer, a gate oxide layer that is often fabricated on glass, and the polysilicon layer. The gate oxide layer is commonly used during the fabrication of electronic transistors. The polysilicon layer is often used during the fabrication of electronic transistors. The polysilicon layer is often used to form a portion of a gate electrode used in Field Effect Transistors (FET). The glass layer is deposited on the silicon layer, and the polysilicon layer is deposited on the glass layer. By controlling the width and the height of the polysilicon layer the effective mode index or the propagation constant β is controlled to provide a rib or ridge optical waveguide. Many structures that perform a variety of optical functions can be constructed by adjusting the polysilicon parameters (e.g., shape, dimension, height, etc.). Furthermore, optical waveguide devices such as AWGs, can be constructed in an existing CMOS fab, using cost effective techniques and processes. Certain passive optical waveguide devices that can be constructed using the techniques described herein include, e.g.,: rectangular AWGs, lenses and lens arrays, adiabatic tapers, and Bragg structures. Many embodiments of passive optical waveguide devices can be constructed in thin SOI by etching the silicon layer. Examples of passive optical waveguide devices that are formed by etching the silicon layer in thin SOI include mirrors, mirror arrays, Echelle gratings, MMI, adiabatic tapers, coupled waveguides, and focusing Echelle devices

# Brief Description of the Drawings

**[0020]** The accompanying drawings, which are incorporated herein and constitute part of this specification, illustrate the presently preferred embodiment of the invention, and, together with the general description given above and the detailed description given below, serve to explain features of the invention.

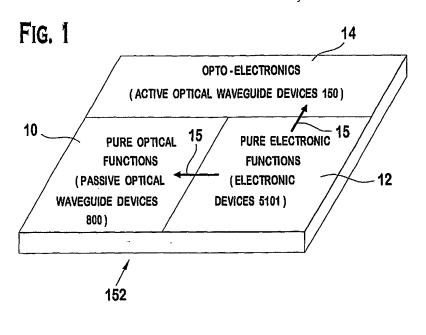

- FIG. 1 shows a logical diagram of an integrated optical/electronic circuit;

- FIG. 2 shows an top view of one prior art embodiment of arrayed waveguide grating; FIG. 3 shows an end cross-sectional view of one embodiment of passive optical

- waveguide device;

20

30

35

40

45

50

55

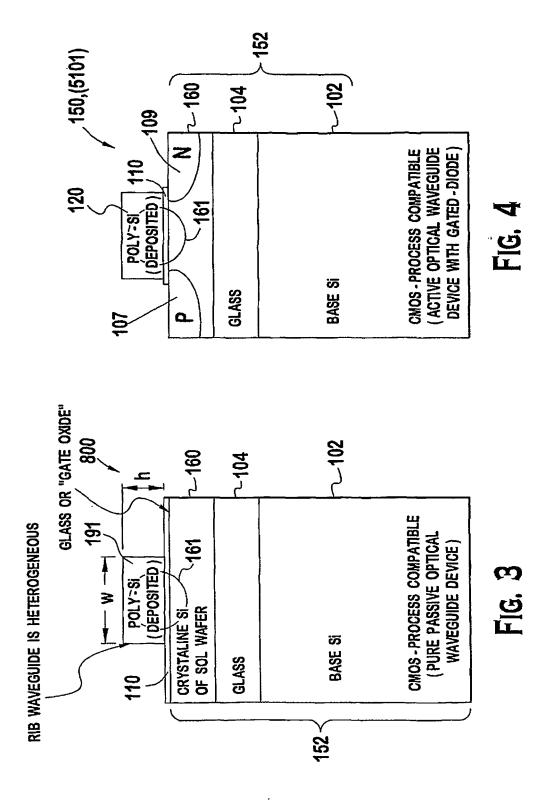

- FIG. 4 shows an end cross-sectional view of one embodiment of either an active optical waveguide device or an electronic device:

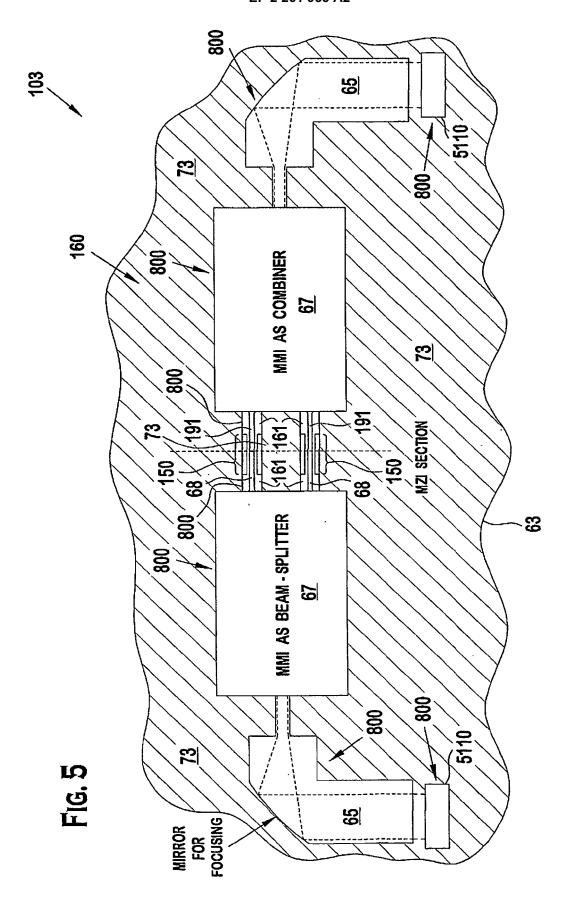

- FIG. 5 shows a top view of an integrated optical device that includes a passive optical waveguide device and an

active optical waveguide device or an electronic device;

10

20

30

45

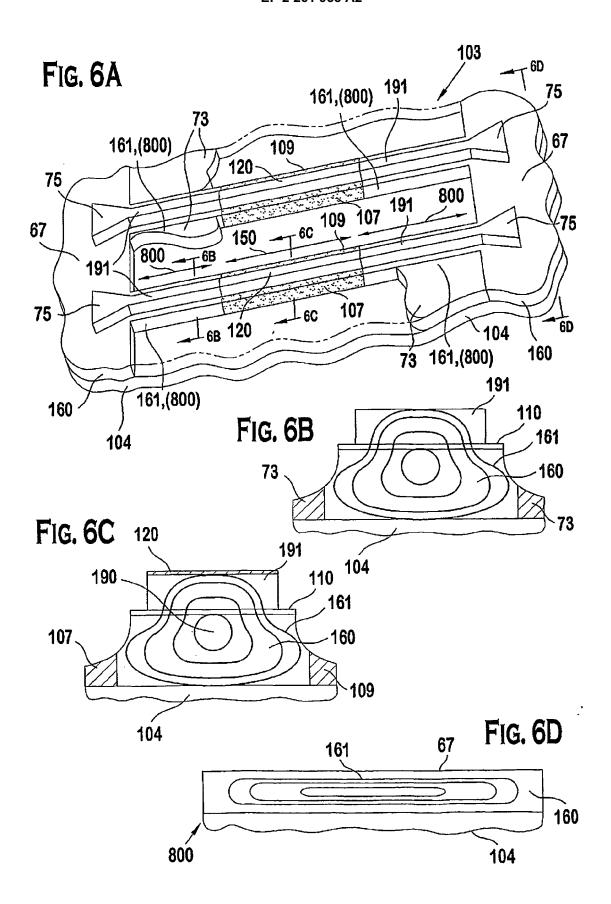

- FIG. 6A shows an expanded view of a portion of the integrated optical device shown in FIG. 5;

- FIG. 6B shows a sectional view taken through sectional lines 6B--6B of FIG. 6A, illustrating a cross-sectional view of one embodiment of active optical waveguide device;

- FIG. 6C shows a sectional view taken through sectional lines 6C--6C of FIG. 6A illustrating a cross sectional view of one embodiment of passive optical waveguide device;

- FIG. 6D shows a sectional view taken through sectional lines 6D--6D of FIG. 6A illustrating a cross sectional view of another embodiment of passive optical waveguide device;

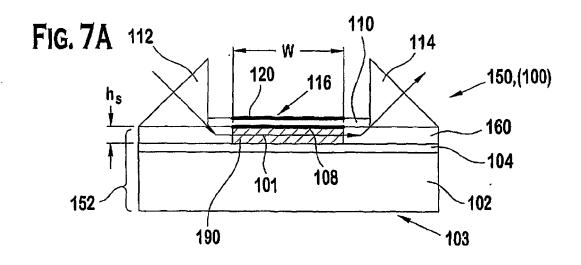

- FIG. 7A shows a side cross-sectional view of one embodiment of an active optical waveguide device including a field effect transistor (FET);

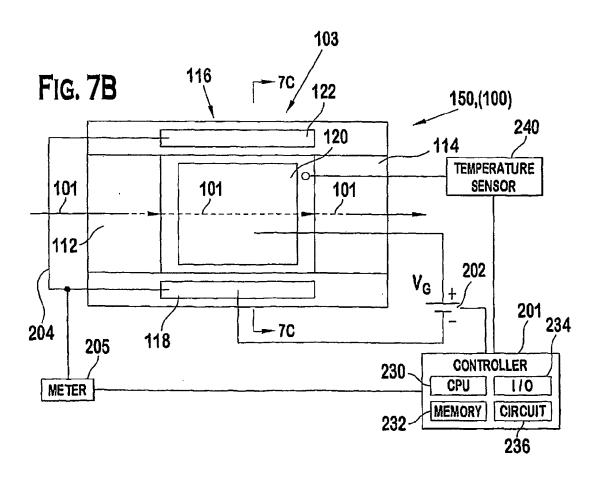

- FIG. 7B shows a top view of the active optical waveguide device of FIG. 7A;

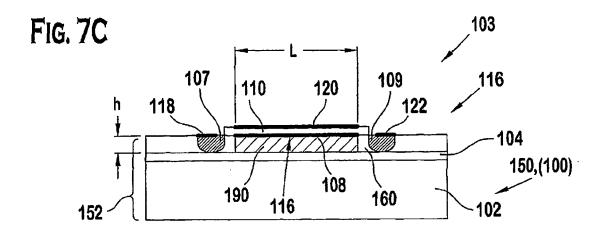

- FIG. 7C shows a front cross-sectional view of the active optical waveguide device of FIG. 7A;

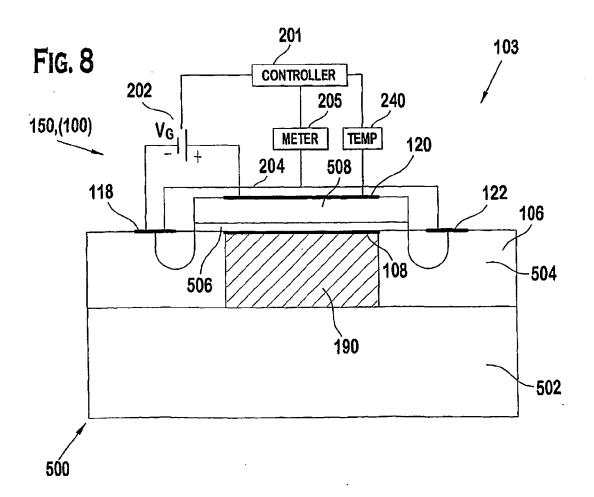

- FIG. 8 shows a front view of another embodiment of an active optical waveguide device including a high electron mobility transistor (HEMT);

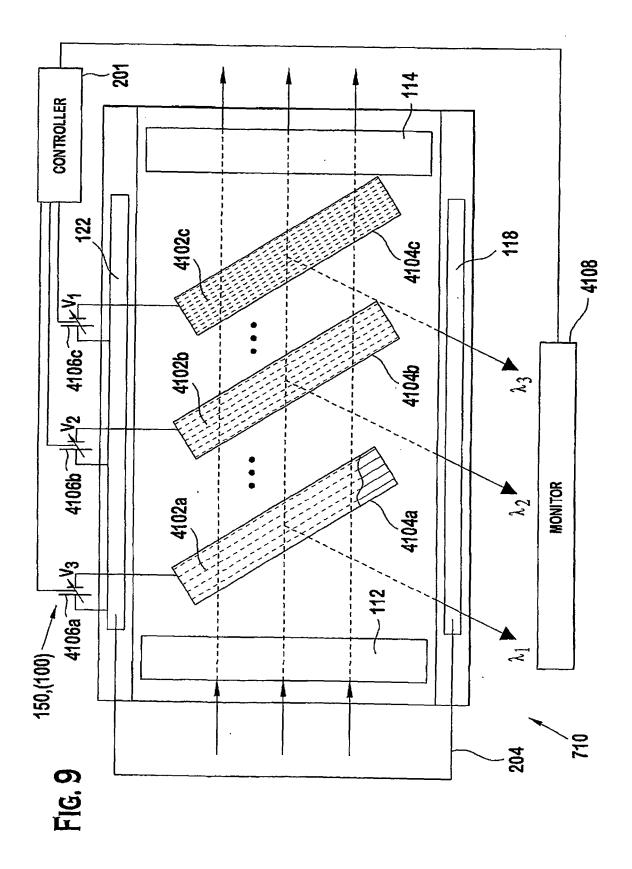

- FIG. 9 is a top view of one embodiment of active optical waveguide devices formed on the FET as illustrated in FIGS. 7A to 7C;

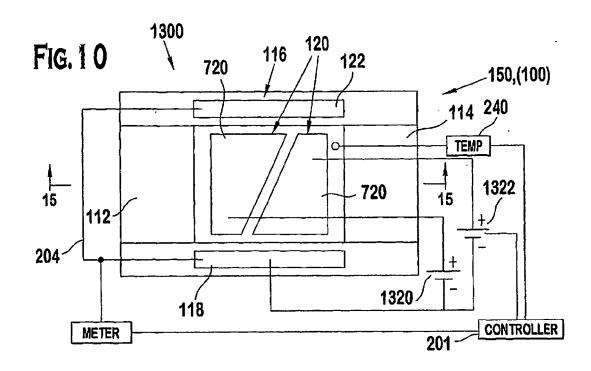

- FIG. 10 is a top view of another embodiment of active optical waveguide devices formed on the FET as illustrated in FIGS. 7A to 7C;

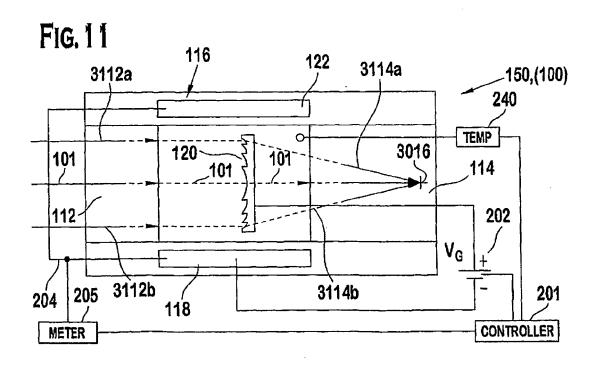

- FIG. 11 is a top view of yet another embodiment of active optical waveguide devices formed on the FET as illustrated in FIGS. 7A to 7C;

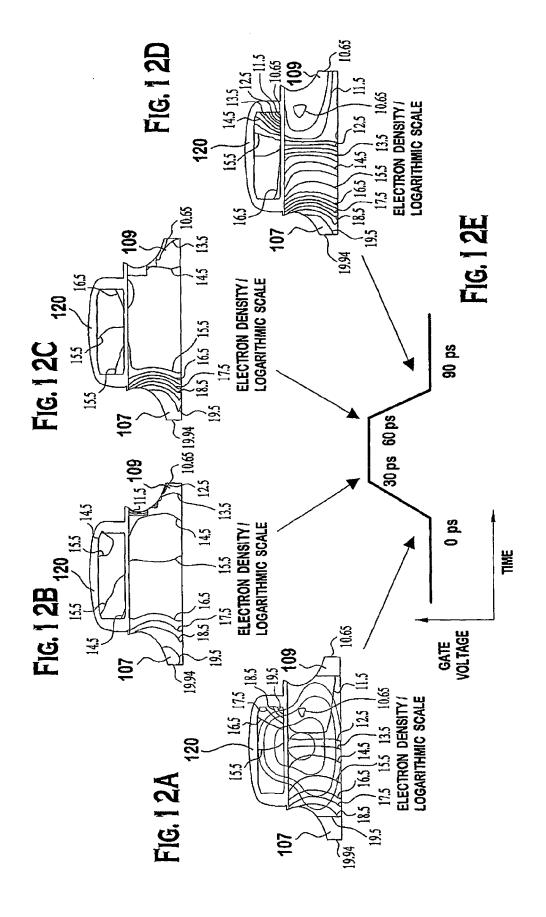

- FIGs. 12A to 12D illustrate the electron density progression of one embodiment of active optical waveguide device as the gate voltage varies;

- FIG. 12E illustrates the progression of different voltages applied between the gate and body contacts of one embodiment of art active wavequide device;

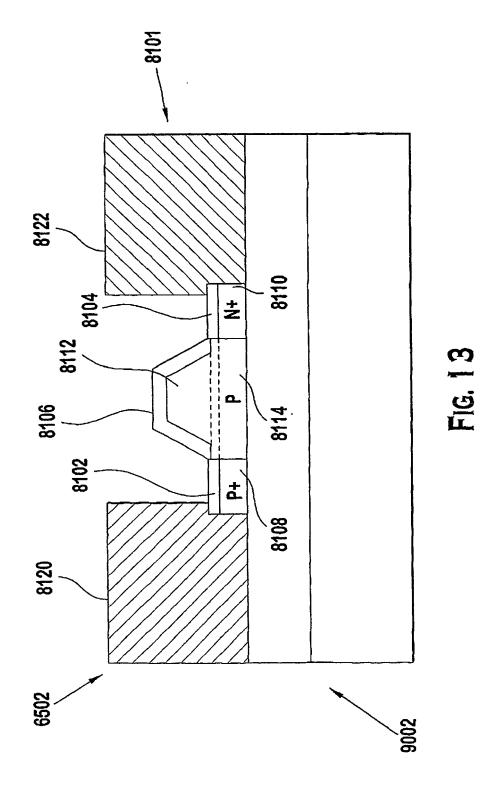

- 25 FIG. 13 shows another embodiment of active optical waveguide device;

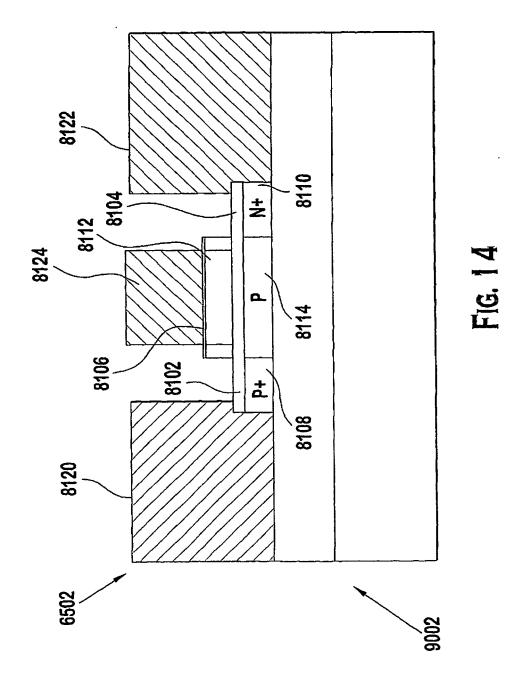

- FIG. 14 shows yet another embodiment of active optical waveguide device;

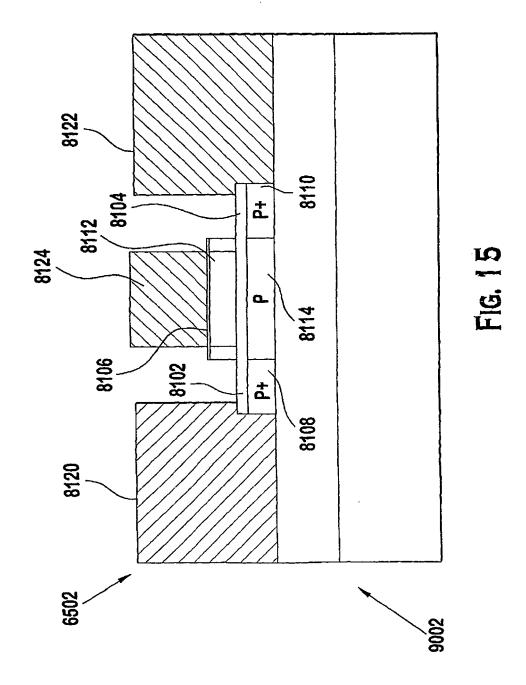

- FIG. 15 shows still another embodiment of active optical waveguide device;

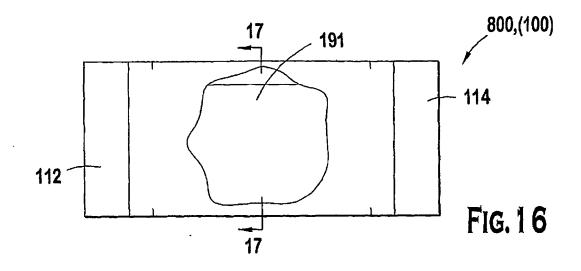

- FIG. 16 shows a top view of one generalized embodiment of a passive optical waveguide device;

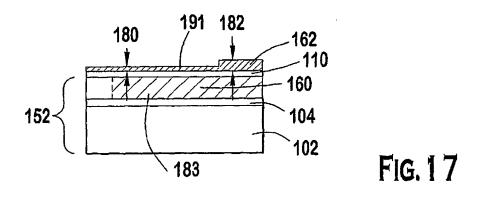

- FIG. 17 shows a cross-sectional view through sectional lines 17--17 of the passive optical waveguide device of FIG. 16:

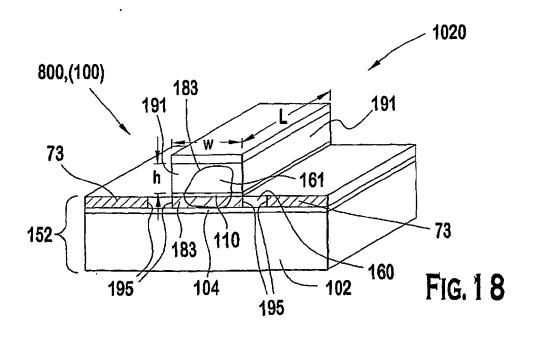

- FIG. 18 shows a perspective view of one embodiment of the passive optical waveguide device that is a polyloaded waveguide;

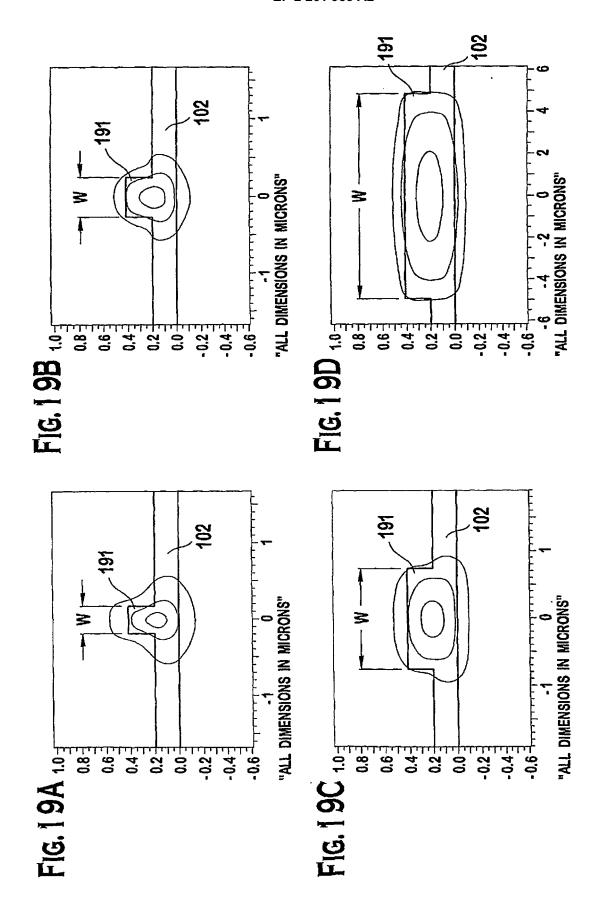

- FIGs. 19A, 19B, 19C, and 19D show respective end views simulating light travelling within multiple optical waveguides, in which the width of the optical waveguide is varied for each optical simulation;

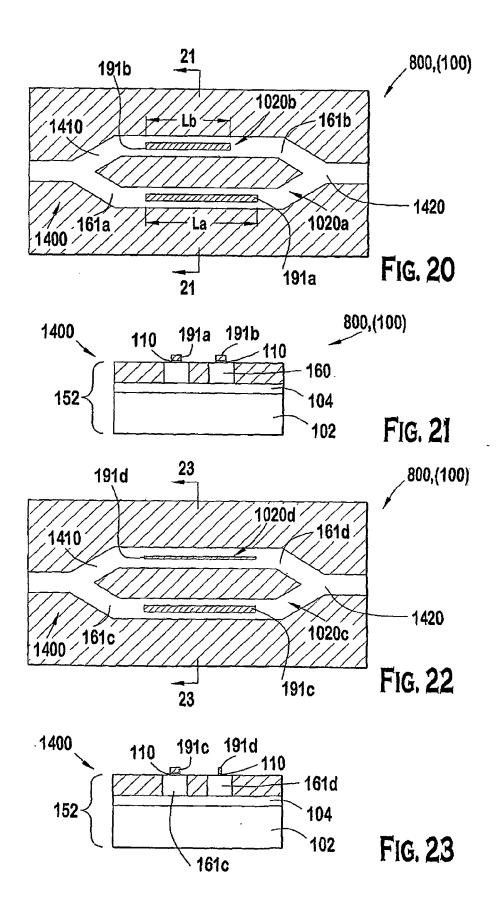

- FIG. 20 shows a top view of a passive optical waveguide device that is configured as an interferometer;

- FIG. 21 shows a cross-sectional view taken through section lines 21-21 of FIG. 20;

- FIG. 22 shows a top view of a passive optical waveguide device that is configured as another embodiment of interferometer:

- FIG. 23 shows a cross-sectional view taken through section lines 23--23 of FIG. 22;

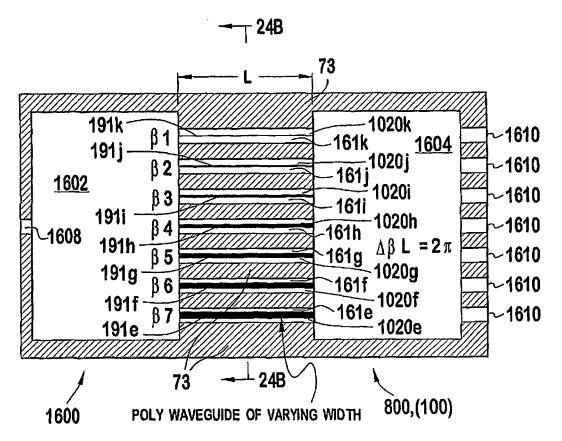

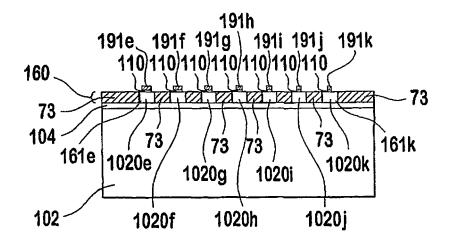

- FIGs. 24A and 24B respectively show top and cross-sectional views of a passive optical waveguide device that is configured as an arrayed waveguide grating (AWG);

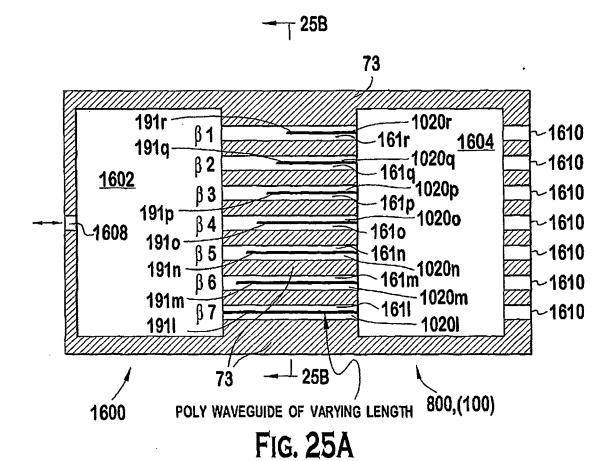

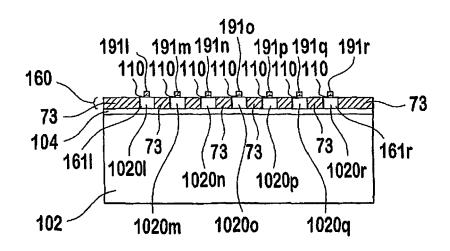

- FIGs. 25A and 25B respectively show top and cross-sectional views of a passive optical waveguide device that is configured as another embodiment of AWG;

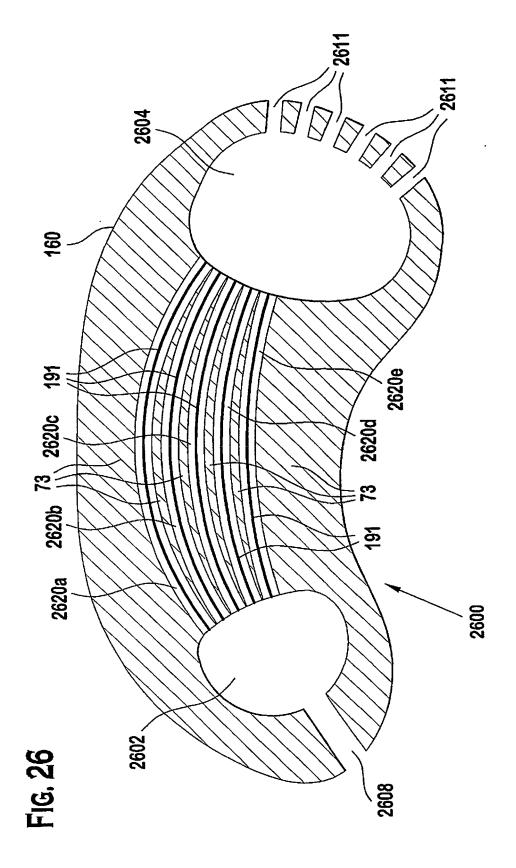

- FIG. 26 shows a top view of a passive optical waveguide device that is configured as another embodiment of AWG;

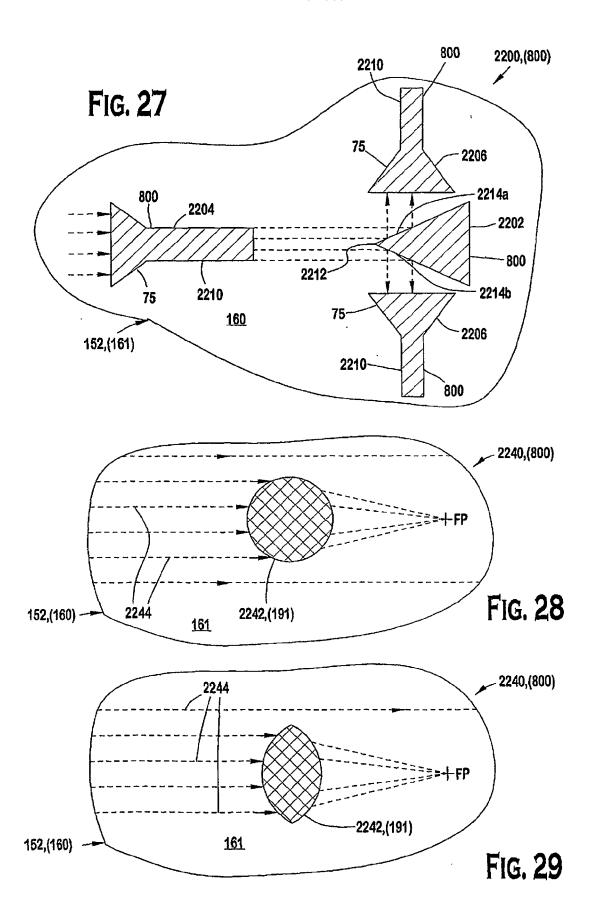

- FIG. 27 shows a top view of a plurality of the passive optical waveguide devices that are configured as a beamsplitter;

- FIG. 28 shows a top view of another passive optical waveguide device that is configured as one embodiment of optical lens;

- FIG. 29 shows a top view of yet another passive optical waveguide device that is configured as another embodiment of the optical lens;

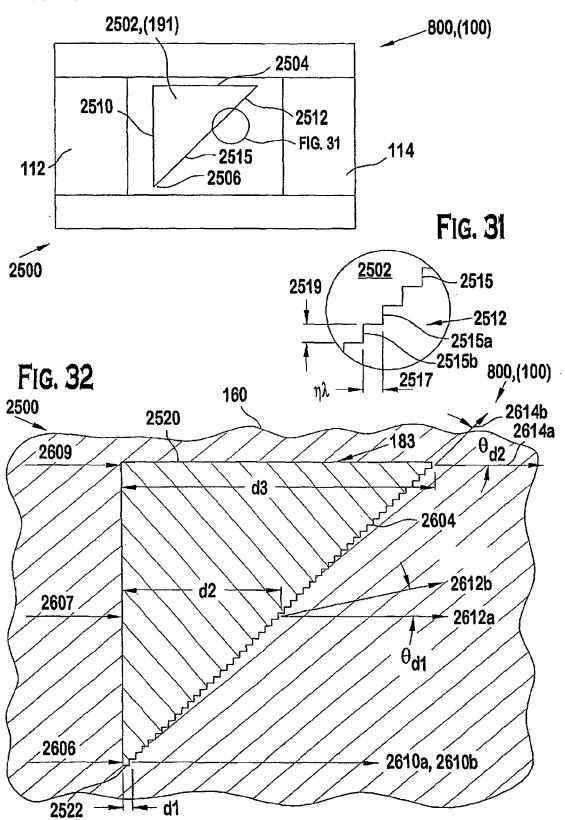

- FIG. 30 shows a top view of another embodiment of the passive optical waveguide device, a portion of which is shown expanded in FIG. 31, the passive optical waveguide device is configured as an Echelle grating;

- FIG. 32 shows a further top view of the passive optical waveguide device of FIG. 30 illustrating the diffraction of optical paths as light passes through the Echelle diffraction grating shown, wherein a region of static effective mode index that is projected from the Echelle diffraction grating is shown;

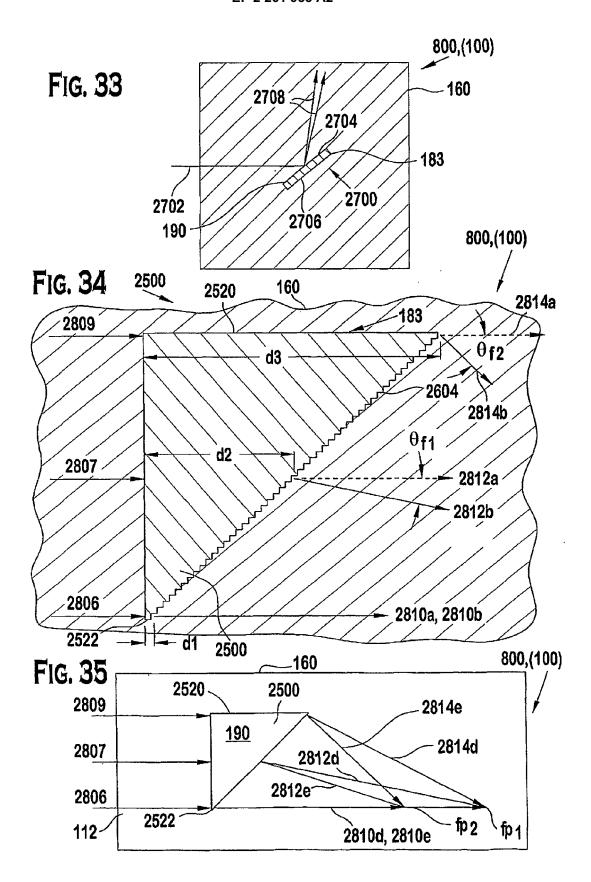

- FIG. 33 shows a passive optical waveguide device configured to operate as an Echelle diffraction grating;

- FIG. 34 shows a top view of a passive optical waveguide device illustrating the focusing of multiple optical paths as light passes through the Echelle lens grating similar to as shown in FIG. 30;

- FIG. 35 shows a device view of the passive optical waveguide device that is configured as the Echelle lens grating

as shown in FIG. 34 that acts to focus light;

5

10

15

20

25

30

35

40

45

50

55

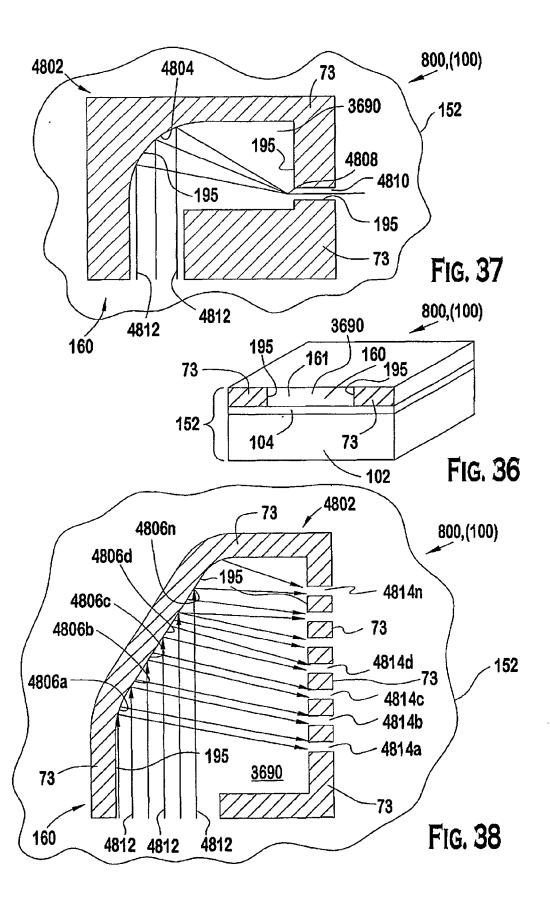

FIG. 36 shows a perspective view of another embodiment of passive optical waveguide device that is formed by etching the silicon layer, that is configured as an optical waveguide;

FIG. 37 shows a top view of another embodiment of passive optical waveguide device that is formed by etching the silicon layer, that is configured as a mirror;

FIG. 38 shows a top view of yet another embodiment of passive optical waveguide device that is formed by etching the silicon layer, that is configured as a multiple mirror device;

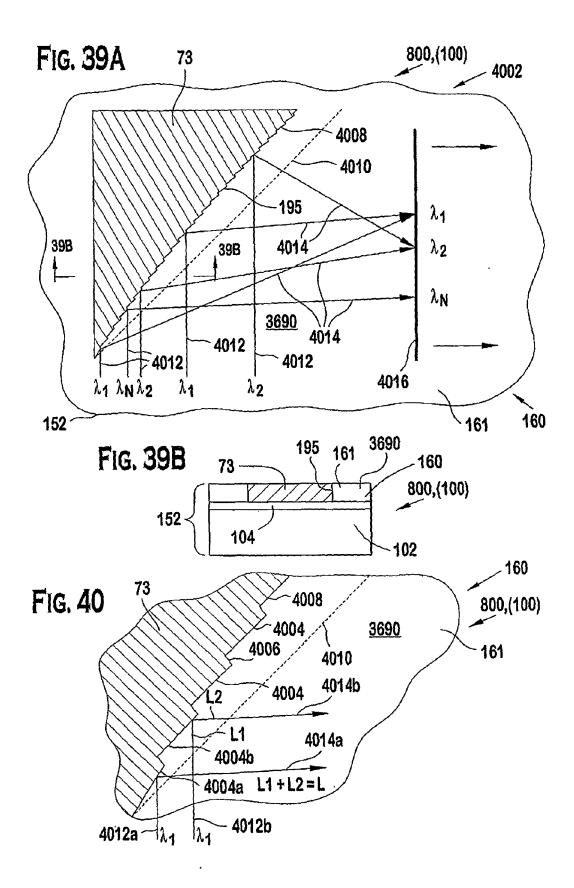

FIGs. 39A and 39B show respective top and cross-sectional views of yet another embodiment of passive optical waveguide device that is formed by etching the silicon layer, that is configured as a refectory Echelle diffraction grating; FIG. 40 shows an expanded view of a portion of the passive optical waveguide device shown in FIG. 39;

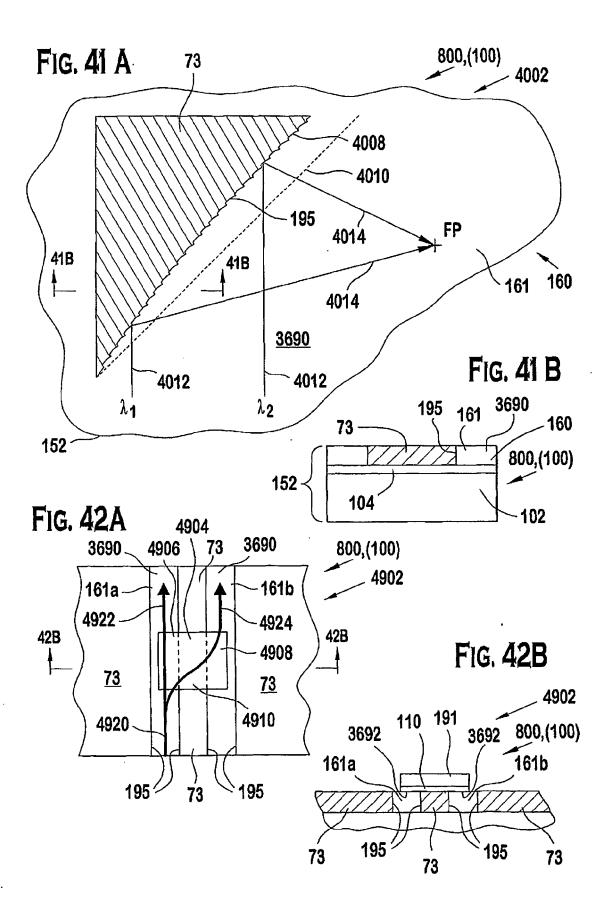

FIGs. 41A and 41B show respective top and cross-sectional views of yet another embodiment of passive optical waveguide device that is formed by etching the silicon layer, that is configured as a refectory Echelle lens grating; FIG. 42A shows a top view of one embodiment of passive optical waveguide device that is configured as an interoptical waveguide coupler;

FIG. 42B shows a cross sectional view of the inter-optical waveguide coupler as taken along sectional lines 42--42 of FIG. 42A;

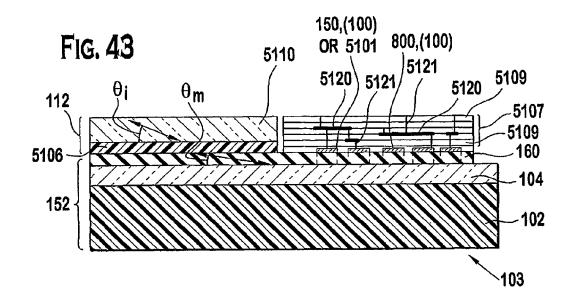

FIG. 43 shows a cross-sectional view of one embodiment of an integrated optical/electronic circuit;

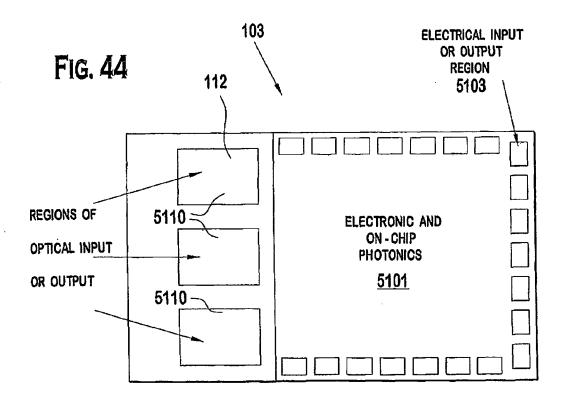

FIG. 44 shows a top view of the embodiment of the integrated optical/electronic circuit shown in FIG. 43;

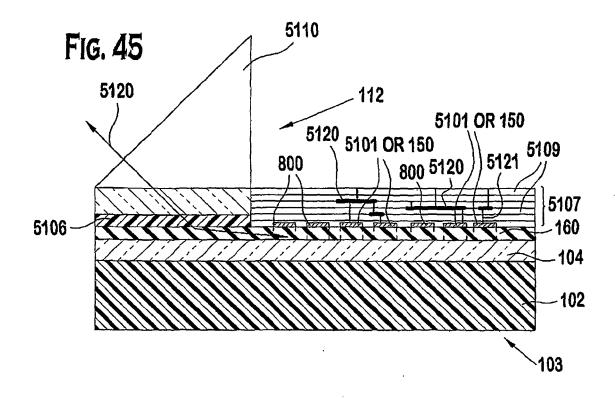

FIG. 45 shows a cross-sectional view of one embodiment of the integrated optical/electronic circuit;

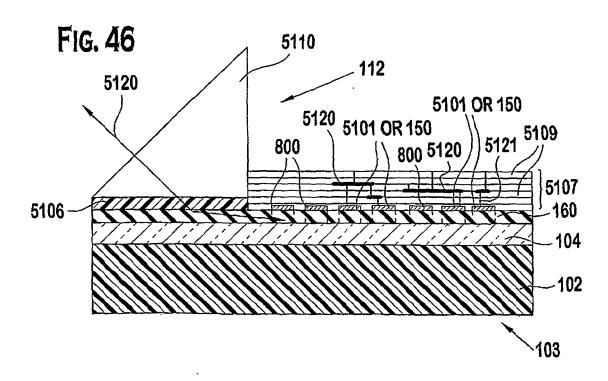

FIG. 46 shows a cross-sectional view of another embodiment of the integrated optical/electronic circuit;

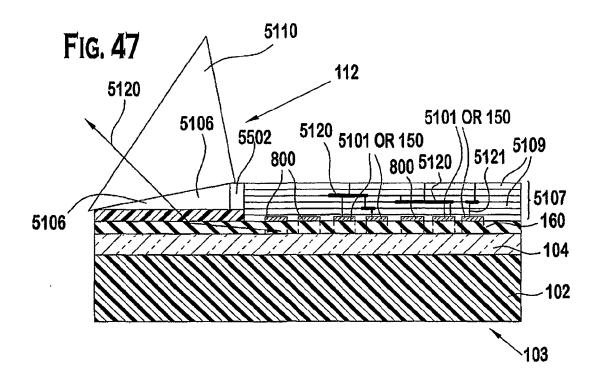

FIG. 47 shows yet another cross-sectional view of an alternate embodiment of the integrated optical/electronic circuit;

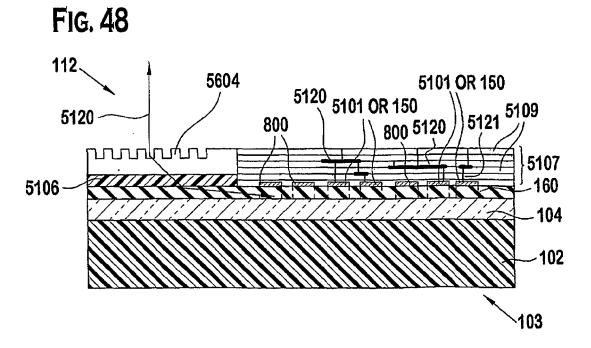

FIG. 48 shows a cross-sectional view of yet another alternate embodiment of the integrated optical/electronic circuit;

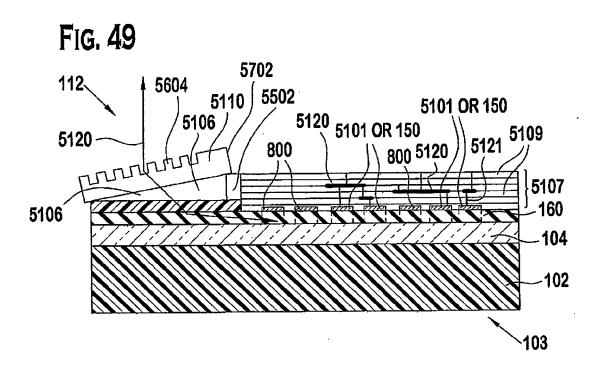

FIG. 49 shows a cross-sectional view of another alternate embodiment of the integrated optical/electronic circuit;

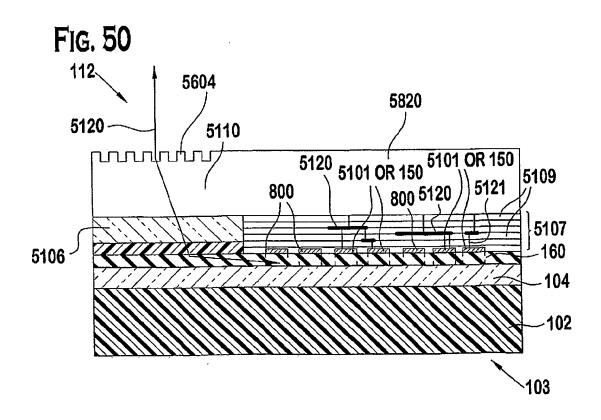

FIG. 50 shows a cross-sectional view of yet another alternate embodiment of the integrated optical/electronic circuit;

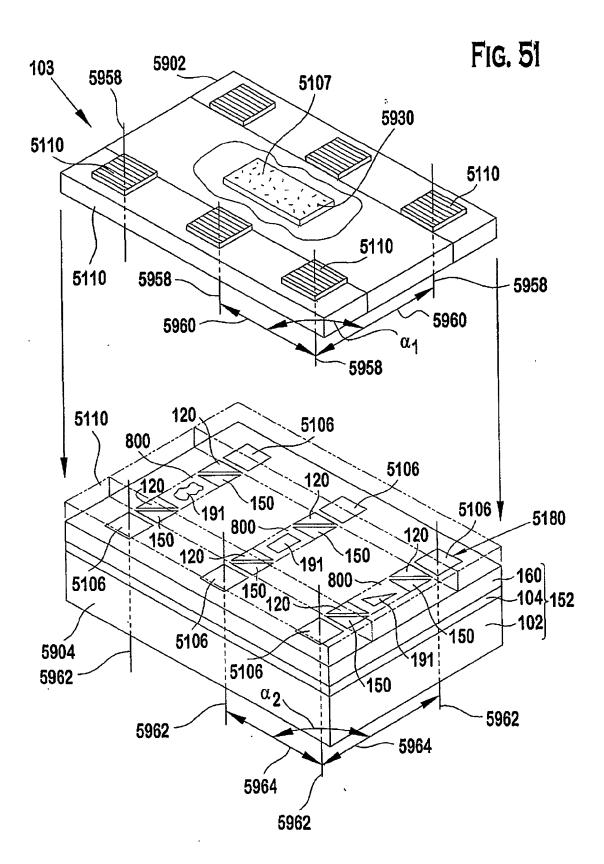

FIG. 51 shows a partially exploded perspective view of an embodiment of the integrated optical/electronic circuit using flip chips;

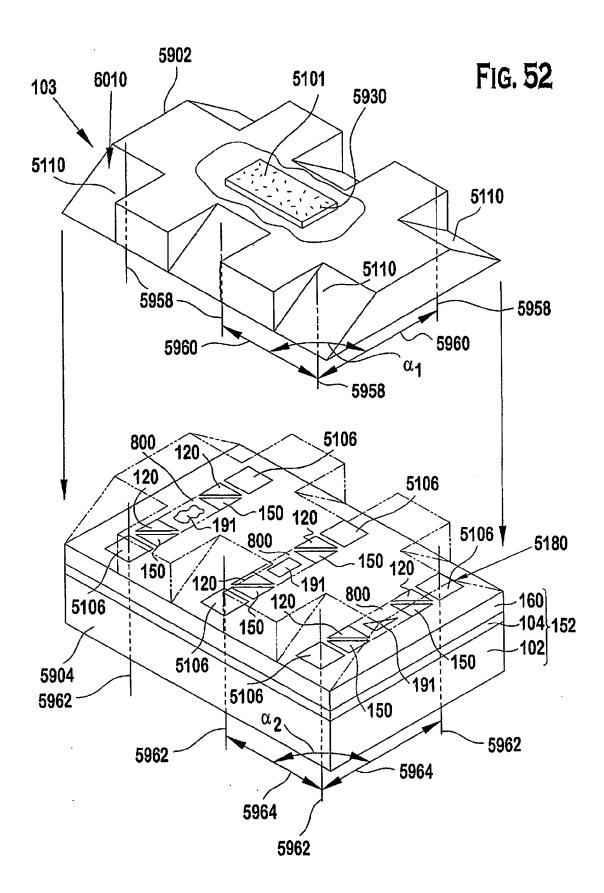

FIG. 52 shows a partially exploded perspective view of an alternate embodiment of the integrated optical/electronic circuit using flip chips;

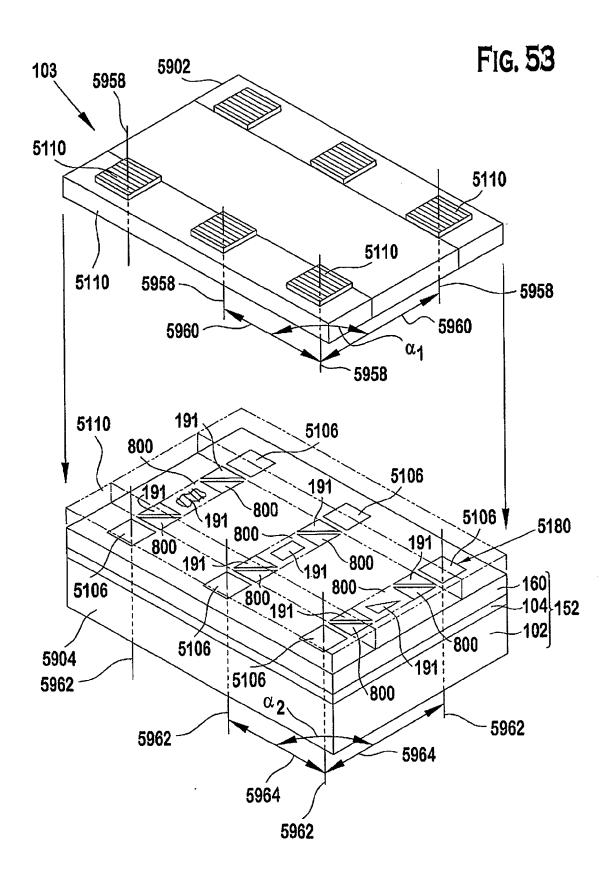

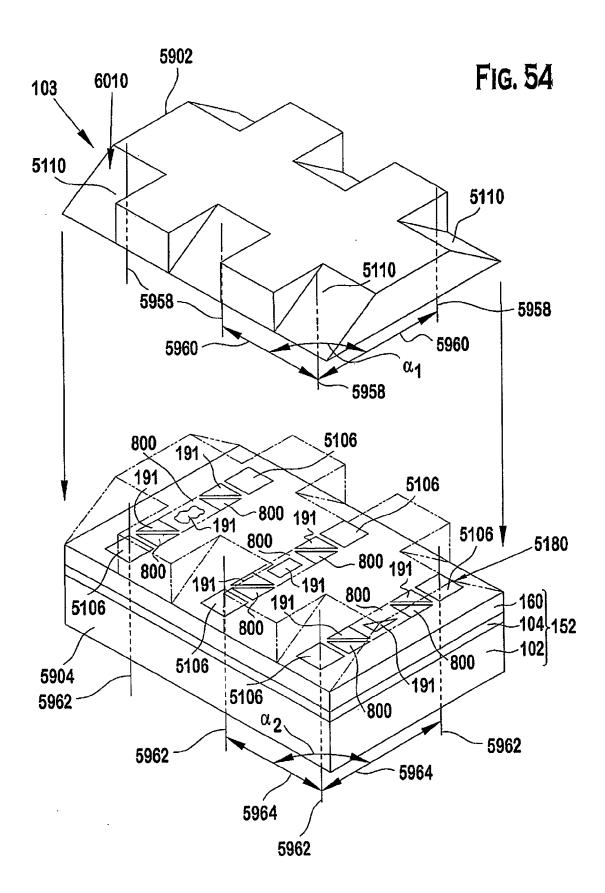

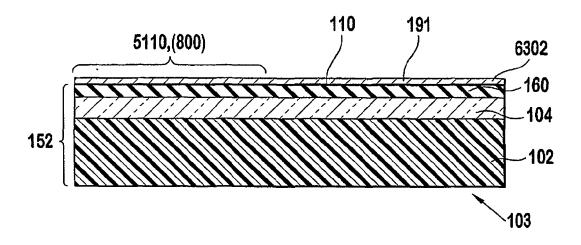

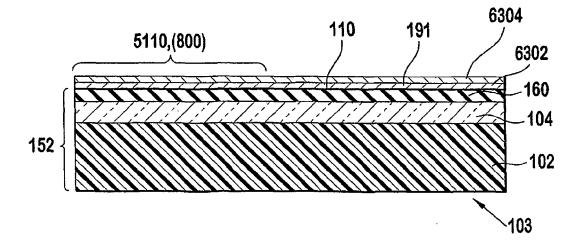

FIG. 53 shows a partially exploded perspective view of one embodiment of an integrated optical circuit using flip chips; FIG. 54 shows a partially exploded perspective view of an alternate embodiment of the integrated optical circuit using flip chips.

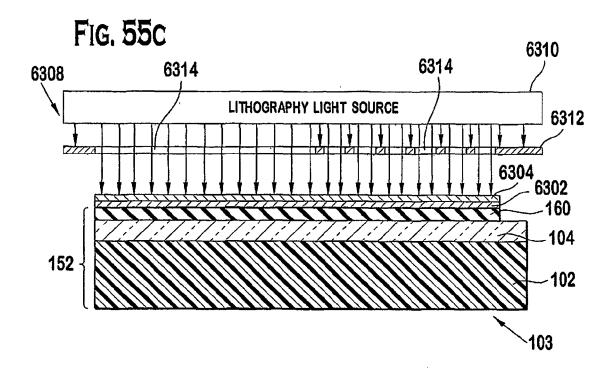

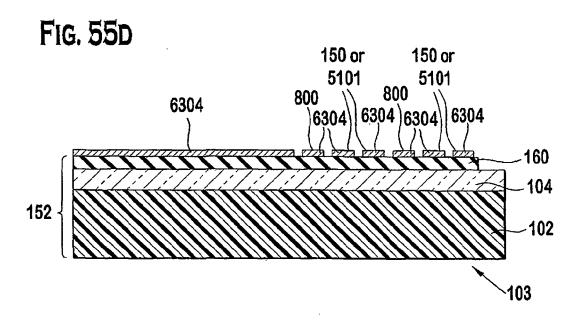

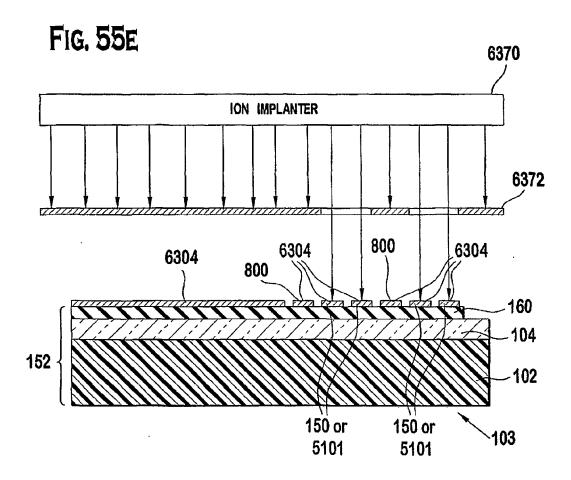

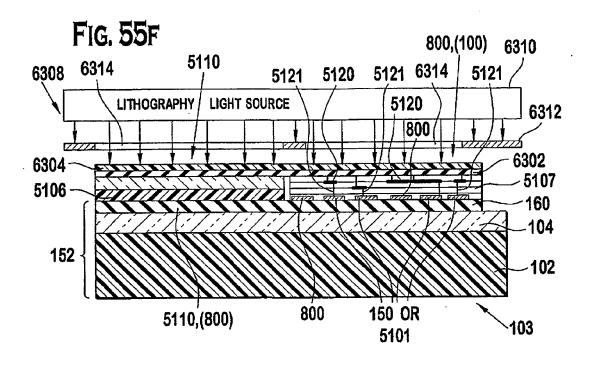

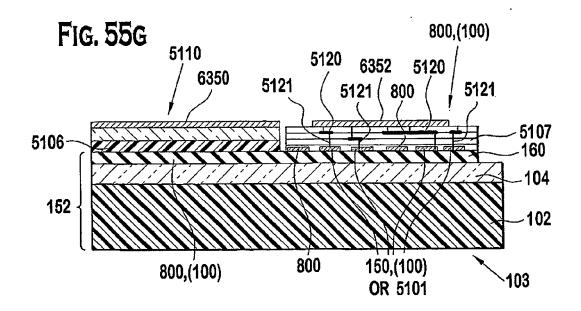

FIGs. 55A to 55G show a method of fabricating a layer on the partially completed integrated optical/electronic circuit, similar to as shown in FIG. 43; .

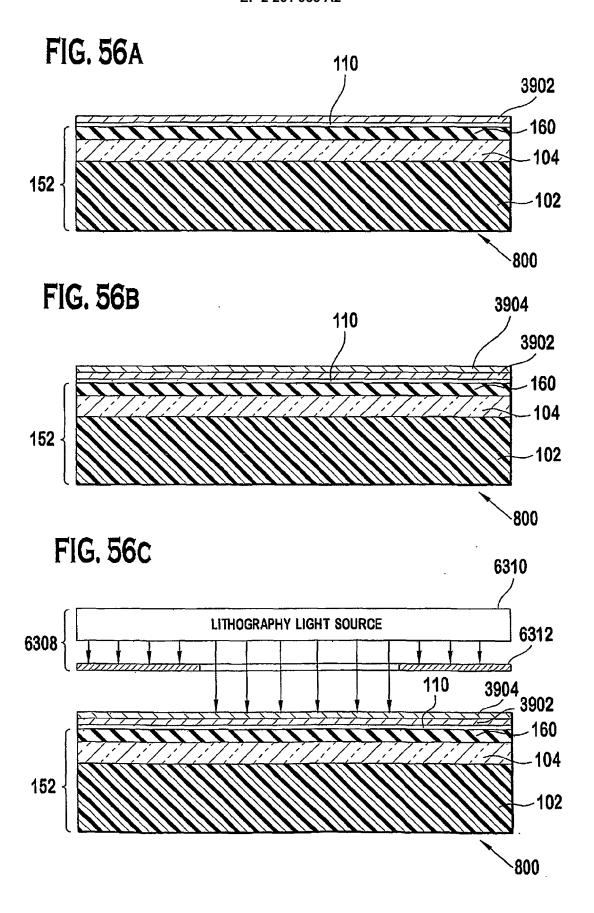

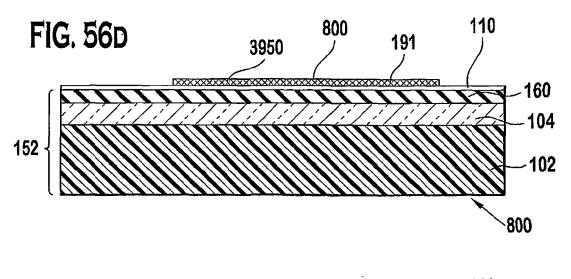

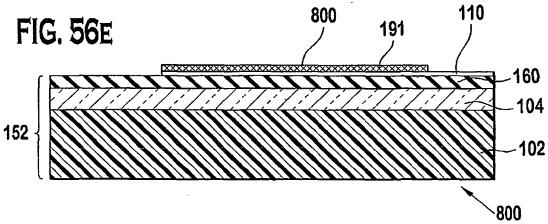

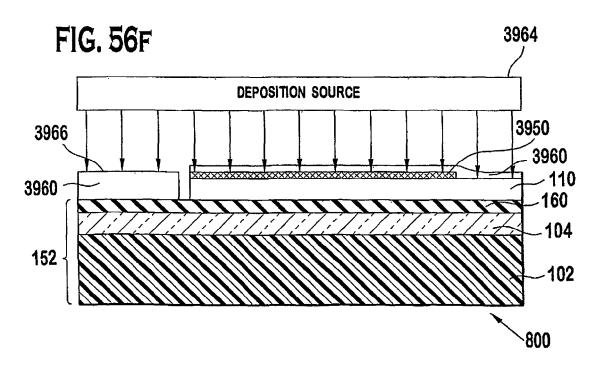

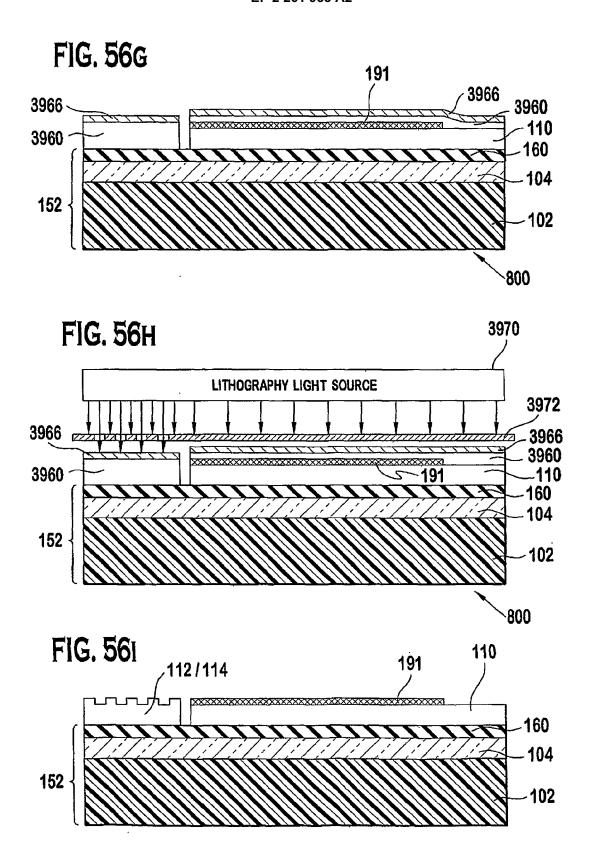

FIGs. 56A to 56I show a method of fabricating a layer on the partially completed passive optical waveguide device in combination with a light coupler; and

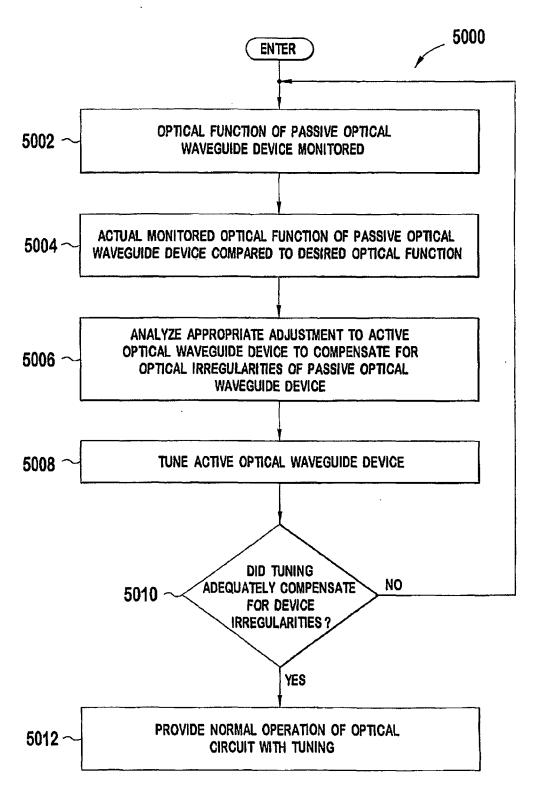

FIG. 57 shows one embodiment of a tuning method in which an active optical waveguide device tunes light output from a passive optical waveguide device.

**[0021]** Throughout the figures, unless otherwise stated, the same reference numerals and characters denote like features, elements, components, or portions of the illustrated embodiments.

# Detailed Description of the Embodiment

I. Optical Waveguide Device Introduction

**[0022]** The present disclosure provides multiple embodiments of optical waveguide devices 100 in which light travels within an optical waveguide 160 on a single wafer 152. FIG. 1 illustrates a logical diagram of one embodiment of integrated optical/electronic circuit 103. The integrated optical/electronic circuit 103 may provide pure optical functions 10, pure electronic functions 12, and opto-electronic functions 14 on the single wafer 152. Each type of optical function is preferably performed by a different type of device configured for that particular function. For example, passive optical waveguide devices 800, described herein, can perform the pure optical functions 10. Electronic devices 5101, described herein, can perform the pure electronics functions 12. Active optical waveguide devices 150, described herein, can perform the opto-electronics functions 14. While the pure optical functions 10, the pure electronic functions 12, and the opto-electronic functions 14 are illustrated at distinct locations on the wafer 152, in actuality the devices that perform these functions are each typically physically interspersed across the wafer 152. For example, one passive optical waveguide device 800 may be adjacent, and operationally associated with, one active optical waveguide device 150 or one electronic device 5101. One active optical waveguide device 150 may be used, for example, to tune out optical operational irregularities present in the passive optical waveguide device 800. The passive optical waveguide devices can be closely

combined with active optical waveguide devices. For example, a silicon passive optical waveguide (which is a passive optical waveguide device) constructed using standard CMOS processes can be combined with active electronics devices 5101 (such as diodes or transistors) to form the integral part of an optical modulator as one embodiment of integrated optical/electronic circuit 103.

**[0023]** The same CMOS-based manufacturing process, described herein, can be used to fabricate the active optical waveguide devices 150, the electronic devices 5101, and the passive optical waveguide devices 800 within the integrated optical/electronic circuit 103 often using the same processing steps as described herein. As such, the devices that can perform the pure optical functions 10, the pure electronic functions 12, and the opto-electronics functions 14 can be produced concurrently, on the same wafer 152, and using the same manufacturing process.

**[0024]** The passive optical waveguide devices 800, the electronic devices 5101, and the active optical waveguide devices 150 can each be fabricated using standard CMOS processing techniques and technology. In one embodiment, the passive optical waveguide devices 800, the electronic devices 5101, and the active optical waveguide devices 150 are described as being fabricated on a single Silicon-on-Insulator (SOI) wafer 152. For example, pure electronic devices such as field effect transistors (FETs) can be deposited and/or etched on the SOI wafer 152. The passive optical waveguide devices 800 and the active optical waveguide devices 150 can be simultaneously deposited and/or etched on the SOI wafer 152. The masks, and the positioning equipment, that are used for etching active optical waveguide devices 5101 can also be used to etch the passive optical waveguide devices 800 and the active optical waveguide devices 150 as described herein.

**[0025]** Semiconductors such as silicon, gate oxides (such as glass), polysilicon, and metal form the basic building materials from which electronic devices 5101 are fabricated using CMOS technology. Passive optical waveguide devices 800 and active optical waveguide devices 150 can be fabricated using the same building materials. Similar doping techniques can be applied, where appropriate, for polysilicon that is used in electronic devices 5101, active optical waveguide devices 150, and passive optical waveguide devices 800.

20

30

35

40

45

50

55

[0026] Certain embodiments of passive optical waveguide devices 800 are structurally very similar to certain embodiments of active optical waveguide devices 150. For example, one embodiment of passive optical waveguide device 800 that is integrated on the SOI wafer 152 is illustrated in FIG. 3. One embodiment of active optical waveguide device 150 that is integrated on the SOI wafer 152 is illustrated in FIG. 4. In FIGs. 3 and 4, the SOI wafer 152 includes a substrate 102, an optical insulator 104, and the silicon layer 160. The substrate 102 includes, for example, silicon, gallium arsenide (GaAs), indium phosphate (InP), glass, sapphire, or diamond. The optical insulator 104 includes, e.g., glass, silicon dioxide, or other optically insulating materials. Cladding layers, used with certain slab optical waveguides 160 and optical fibers, are one embodiment of optical insulators 104 and gate oxide layers 110.

[0027] Any description of a specific semiconductor in this disclosure is exemplary, and not limiting in scope, since a very large number of materials may be used. Other materials can be used in the silicon layer 160. Examples of such materials generally include semiconductor materials. The term "semiconductor" used through this disclosure relates particularly to the silicon layer 160 of the optical waveguide devices 100. The silicon layer 160 (often configured as an optical waveguide) is formed at least in part from silicon and may also include GaAs, InP, SiGe, or other materials which in combination with silicon transmit light. At room temperature, silicon and germanium are single element semiconductors. GaAs and InP are examples of binary compound semiconductors. There are semiconductors made from three element semiconductors such as AlGaAs. The salient feature of all semiconductors is the existence of a band-gap between the valence and the conduction band. During the fabrication of the optical waveguide device 100, multiple semiconductor layers may be deposited and/or etched.

[0028] The embodiment of passive optical waveguide 800 shown in FIG. 3 includes (in addition to the components of the SOI wafer 152) a polysilicon layer 191 and a gate oxide layer 110. The gate oxide layer 110 in CMOS processing often includes glass, such as silicon dioxide. In this disclosure, the term "gate oxide" refers to the type of oxide (or glass) that is typically used to form a gate, but in the present disclosure the gate oxide does not necessarily have to form a gate. For example, the gate oxide layer is applied to polysilicon layers in certain embodiments of passive optical waveguide devices as described herein. Polysilicon, such as used in the polysilicon layer 191, corresponds to a layer formed at least in part from polysilicon and would include, for example, a pure polysilicon layer or a polySi layer doped with materials such as Ge or C. Polysilicon is often used in gate electrodes for field effect transistors (FETs), using CMOS processing. FETs represent one embodiment of electronic device 5101. However, with FETs, the polysilicon of the gate electrodes are doped. The polysilicon used in the polysilicon layer 191 is preferably not doped. Undoped polysilicon layers are desired to limit the light absorption of doped polysilicon. An optical waveguide 161 is formed within the silicon layer 160, the gate oxide layer 110, and/or the polysilicon layer 191. Light travelling within the passive optical waveguide device 800 flows within the optical waveguide 161. The width w and the height h of the polysilicon layer 191 largely determine the cross-sectional configuration, and therefore the optical characteristics, of the optical waveguide 161. In passive optical waveguide devices, the optical waveguide, that defines where light flows, is formed in the silicon layer 160, the gate oxide 110, and the polysilicon layer 191.

[0029] The embodiment of active optical waveguide device 150 shown in FIG. 4 also includes (in addition to the

components of the SOI wafer 152 and the passive optical waveguide device 800 shown in FIG. 3) a gate electrode 120, a first body contact well 107, and a second body contact well 109. The first body contact well 107 and the second body contact well 109 are also known in FET terminology (either respectively or inversely) as a source and a drain. In the active optical waveguide device 150, the optical waveguide 161 is formed within the silicon layer 160, the polysilicon layer 191, the gate oxide 110, and/or the gate electrode 120. The width w and the height h of the gate electrode 120 largely determine the cross-sectional configuration of the optical waveguide 161.

**[0030]** Physically, the active optical waveguide device 150 includes similar materials to FETs. The polysilicon in the gate electrode 120 is doped in a similar manner to the polysilicon in the gate electrode of a FET. Many embodiments of active optical waveguide devices 150 could also function as an electronic device 5101 (such as the FET). The dimensions of active optical waveguide devices 150 may differ from the dimensions of FETs, due to their relative functions. As such, virtually identical CMOS deposition and etching techniques and are used to fabricate the active optical waveguide device as electronic devices such as FETs. The dimensions and configurations of the active optical waveguide devices 150 and the electronic devices 5101 may differ, however, since they respectively control the flow of light and electricity. The silicon layer 160, that is configured to act as a portion of an optical waveguide 161, is also capable of acting as a channel in a FET. As such, the active optical waveguide device 150 shown in FIG. 5 can, indeed, provide electronic transistor action based on suitable electric biasing of the gate electrode 120, the first body contact well 107, and the second body contact well 109.

**[0031]** SOI (such as in SOI wafers 152) is a commonly used, heavily researched, and highly accepted technology for electronics using semiconductors. Modifying the already-accepted SOI platform for electronic circuits to allow for the concurrent fabrication and use of passive optical waveguide circuits 800 and active optical waveguide circuits 150 avoids the necessity of developing an entirely new technology for mass-fabrication of optical waveguide circuits.

20

30

35

40

45

50

55

[0032] In fully operational optical waveguide circuits, located on a single wafer 152, one or more active optical waveguide devices 150 may interface with one or more passive optical waveguide devices 800. Similarly, multiple active optical waveguide devices 150 may be optically coupled to permit light transfer therebetween. Moreover, multiple passive optical waveguide devices 800 may be optically coupled to permit light transfer therebetween. Active optical waveguide devices 150, passive optical waveguide devices 800, and electronic devices 5101 may be fabricated simultaneously on a single SOI wafer 152 as explained below. SOI technology is therefore highly applicable to integrated optical/electronic circuits.

**[0033]** FIG. 5 show a top view of a broken-away portion of an exemplary optical circuit 63 including a plurality of passive optical waveguide devices 800 and a plurality of active optical waveguide devices 150. A plurality of passive optical waveguide devices, illustrated as 800, transfer light to and receive light from active optical waveguide devices 150. The passive optical waveguide devices 800 illustrated in FIG. 6A include a light coupler 5110, a mirror 65, a pair of multiple mode interference (MMI) devices 67 that (from left to right) are configured to act respectively as a light splitter and a light combiner.

[0034] FIG. 6A shows an expanded portion of the integrated optical/circuit 103 shown in FIG. 5, that includes both passive optical waveguide devices 800 and active optical waveguide devices 150. For example, FIG. 6B, which illustrates a portion of the polyloaded optical waveguide shown in FIG. 6A above, includes the silicon layer 160. The polyloaded optical waveguide shown in FIG. 6B is a passive optical waveguide device. FIG. 6C, by comparison, illustrates a portion of one of the modulators 68 shown in FIG. 6A including the silicon layer 160. The optical modulator 68 shown in FIG. 6C is an active optical waveguide devices 150, as illustrated in FIG. 4. Each modulator 68 extends between a pair of the optical waveguides 161. These modulators 68, that are arranged in parallel, act as an interferometer. FIG. 6D illustrates a cross sectional view of a portion of the MMI device 67 illustrated in FIG. 6A that is also a passive optical waveguide device 800, and includes only the silicon layer 160 that is configured to control the travel of light therein. By comparison, the silicon layer 160, the gate oxide layer 110, and the polysilicon layer 191 each can support at least a portion of the flow of light within the passive optical waveguide device 800.

[0035] The passive optical waveguide devices 800 described herein are formed by a progression of depositing, patterning (with a mask), and etching the silicon layer 160, the gate oxide layer 110, or the polysilicon layer 191. The different embodiments of passive optical waveguide devices 800 illustrated in FIG. 5 may further be sub-divided according to how they are fabricated. Certain passive optical waveguide devices 800 are fabricated by etching a portion of the silicon making up the silicon layer 160 in the SOI wafer 152. The etched regions of the silicon layer 160 is filled with air, glass (silicon dioxide), or another silicon layer optical insulator 73. The junction between silicon and the silicon layer optical insulator 73 creates a total internal reflectance (TIR) boundary 195, as described below, that acts to maintain light flowing within the silicon that remains in the silicon layer 160 following etching. This etching away portions of the silicon layer 160 is common in CMOS processing. For example, the silicon in FETs, and other active electronic devices, is often formed by etching away sacrificial material within the silicon layer 160 that falls outside the boundaries of the FETs. In those embodiments of passive optical waveguide devices that include only the silicon layer 160 such as illustrated in FIG. 6D (and devices 65 and 67 in FIG. 5), the silicon layer is etched in a manner that the etched surface provides the total internal reflection (TIR) boundary 195 to the light travelling within the optical waveguide 161 that contacts the etched

surface.

20

30

35

40

45

50

55

[0036] Another embodiment of passive optical waveguide devices 800 is illustrated in FIGs. 3, 5, 6A, and 6B. In this embodiment of passive optical waveguide 800, the polysilicon layer 191 is deposited on the gate oxide 110 after the gate oxide has been deposited on the silicon layer 160. The deposited polysilicon layer 191 creates a region of altered effective mode index 190, as shown in FIG. 6B, that helps to define the optical waveguide 161. The optical waveguide 161, that defines where light flows, exists within the silicon layer 160, the gate oxide 110, and/or the polysilicon layer 191. In those embodiments of passive optical waveguide devices that include the polysilicon layer 191, the silicon layer 161, and the gate oxide layer 110, the silicon layer 160 may, or may not be, etched to still constrain the light to travel within the optical waveguide using the TIR boundary 195. In these embodiments of passive optical waveguide devices, the polysilicon layer 191 and the gate oxide layer 110 are configured to provide a modified, but static (unchanging with time) effective mode index.

[0037] It will be understood by those skilled in the art that the passive optical waveguide devices described below as having polysilicon layer 191, an etched silicon layer 161, and the gate oxide layer 110, could alternatively be formed without etching the silicon layer 161. Similarly, it will be understood by those skilled in the art that the passive optical waveguide devices described below as having polysilicon layer 191, an unetched silicon layer 161, and the gate oxide layer 110, could alternatively be formed with an etched silicon layer 161. The photonic guide function as at least partially provided by the region of static effective mode index in the passive optical waveguide device 800 (or the region of altered effective mode index in an active optical waveguide device 150) may be determined from the cross-section of the polysilicon layer 191 as well as the upper semiconductor layer (such as the Si layer on an SOI substrate.)

[0038] Another embodiment of passive optical waveguide devices 800, shown in FIG. 5, includes the light couplers 5110. Light couplers 5110 are used to couple light into, or couple light out of, the silicon layer 160. The light couplers 5110 can be either etched in the silicon layer 160 of the SOI wafer 152, or alternatively affixed as a separate object to the silicon layer. Techniques to fabricate, and techniques to use the light couplers 5110 as they relate to passive optical waveguide devices are described herein.

**[0039]** Active optical waveguide devices 150, such as illustrated in FIGs. 4, 5, and 6C, include a region where the effective mode is varied during operation of the device by, e.g., applying a voltage to an electrode portion such as the gate electrode 120 or otherwise altering an external parameter during operation of the device. Passive optical waveguide devices 800 (such as those shown in FIGs. 3, 6B, and 6D) include a region where the effective mode index remains constant, or static, over the life of the device. That is, passive optical waveguide devices 800 do not include regions where the effective mode index is varied during operation through alteration of a control voltage or other external parameter. As illustrated in FIG. 6B, adiabatic tapers 75 are located at both of the ends of each polysilicon layer 191. The adiabatic tapers 75 act to converge light travelling toward the passive optical waveguide device (in this instance, the optical waveguides 161).

**[0040]** FIG. 6E illustrates the structural similarity between the modulators 68, which are active optical waveguide devices, and optical waveguides, that are passive optical waveguide devices 800. The only structural difference is that the active optical waveguide device 150 includes the body contact wells 107,109. The addition of these body contact wells 107, 109, that permit operation as gate electrodes and source electrodes, act to alter the effective mode index within the modulator 68. By comparison, the optical waveguides 161 (which are passive optical waveguide devices), lack the body contact wells 107, 109 and the associated electrodes. Therefore, the effective mode index remains static or substantially unchanged over time in passive optical waveguide devices, except for variations due to degradation of the device over time.

[0041] Thin optical waveguides are associated with silicon layers 160 having a thickness of less than or equal to  $10\mu$ . Using silicon layers 160 with a thickness less than  $10\mu$  (such as thin SOI waveguides) has many benefits. Thin SOI silicon layers 160 limit the vertical regions in which light can diffract, and localize the light to a relatively narrow optical space. Optical waveguides 161 including such thin silicon layers 160 are relatively easy to precisely fabricate. Planar lithography techniques (such as used in deposition and etching processes) can be used to fabricate thin SOI devices. [0042] Any optical waveguide 161 supports the transmission of light for one or more modes (light wavelengths at which the optical waveguide transmit light). The concepts described herein relative to the optical waveguide devices 100 apply equally well to any mode of light within the optical waveguide 161. Therefore, a multi-mode optical waveguide 161 can model a single optical device having multiple light modes. The physical phenomena described for the single mode of single mode waveguides 161 pertains to each mode in multi-mode optical waveguides 161.

**[0043]** The following sections relate to the various types of optical waveguide devices that can be used to provide optical and electronic/optical functionality, and to indicate the close functional and structural relationship of certain embodiments of the passive optical waveguide devices 800, active optical waveguide devices 150, and electronic devices 5101. The "Active Optical Waveguide Device" portion of this disclosure describes different embodiments of the active optical waveguide devices 150. The "Passive Optical Waveguide Device" portion of this disclosure describes different embodiments of passive optical waveguide devices 800. The structure and operation of many embodiments of passive optical waveguide devices are then described. The techniques of manufacture of many embodiments of active optical

waveguide devices 150 and passive optical waveguide devices 800 are described. The passive optical waveguide devices 800 can be operationally associated (and fabricated simultaneously) with the active optical waveguide devices 150. The optical waveguide circuits 100 can be fabricated using standard (CMOS) fabrication techniques.

# 5 II. Active Optical Waveguide Devices

20

30

35

40

45

50

55

[0044] This section describes the structure and operation of active optical waveguide devices 150 as illustrated generally in FIG. 4 and 6C. The active optical waveguide devices 150 can be fabricated using CMOS fabrication techniques. Multiple ones of the active optical waveguide devices 150 and passive optical waveguide circuits 800 can be integrated into a single integrated optical waveguide circuit. Examples of these integrated optical waveguide circuits include an arrayed waveguide grating (AWG), a dynamic gain equalizer, and a large variety of integrated optical waveguide circuits. Such optical waveguide devices 100 (both active and passive) and integrated optical waveguide circuits can be made using existing CMOS and other semiconductor fabrication technologies.

**[0045]** Different embodiments of active optical waveguide devices 150 may be located in: a) a Field Effect Transistor (FET) structure as shown in FIGs. 7A to 7C; b) a High Electron Mobility Transistor (HEMT) 500 as shown in FIG. 8; or c) other similar active optical waveguide devices 150 in which an electric current can be applied adjacent to the silicon layer 160 to alter the free carrier concentration in a portion of the silicon layer 160.

**[0046]** In the embodiment of FETs applied to FIGs. 7A to 7C, a substantially constant electrical potential conductor 204 as shown in FIG. 7B extends between the source body contact electrode 118 and the drain body contact electrode 122 to maintain the two electrodes 118, 122 at a common voltage. Holding the source electrode 118 of a FET at the same potential as the drain electrode 122 causes the FET to functionally operate as a MOSCAP. The term "body contact electrode" describes either the common potential source electrode and drain electrode in the FET.

[0047] The application of the voltage to between the gate electrode 120 and the body contact electrodes 118, 122 predominantly changes the distribution of free-carriers (either electrons or holes) near the boundary between the silicon layer 160 and the gate oxide layer 110 (which is an optical and electrical insulator). As sufficient voltage is applied between the gate electrode 120 and the body contact electrode(s) 118, 122 causes the transistor action in field effect transistors, and also actuates an optical action in the active optical waveguide devices 150 as described herein. Passive optical waveguide devices 800, as described below, do not include operational gate electrodes 120 or the body contact electrodes 118,122, and as such do not rely on a change in free carrier concentration to effect operation. Two-dimensional electron gas or 2DEG included in MOSCAPs represent essentially surface localized changes in the free carrier distributions. In a FET structure, for example, an increase in the application of the bias leads consecutively to accumulation of charges of the same polarity as the semiconductor silicon layer 160, i.e. holes in a p-type and electrons in n-type, depletion, and finally inversion. In 2DEGs 108, the polarity of the semiconductor is opposite the type of the predominant free carriers, (i.e. electrons in p-type or holes in n-type). In a High Electron Mobility Transistor (HEMT) 500 (shown in FIG. 6), the electron (hole) distribution formed just below the surface of the optical (and electric) insulator 104 is referred to as 2DEG 108 because of particularly low scattering rates of charge carriers. For the purposes of clarity, all of the above shall be referred to as 2DEG signifying a surface localized charge density change due to application of an external bias

[0048] The silicon layer 160 provides the ability to change the density of the 2DEG 108 by varying the voltage applied between the gate electrode 120 and the body contact electrodes 118, 122. The 2DEG 108 is proximate the light travel path, near the boundary between the silicon layer 160 and the gate oxide layer 110. This change in free-carrier distribution results from application of the potential between the insulated gate electrode 120 and one or a plurality of body contact electrodes 118, 122 connected to the body of the semiconductor. The propagation constant within the optical waveguide 161, and the optical properties, (e.g., phase or amplitude) of light guided through the optical waveguide 161, vary as the density of the free carriers changes. Field-effect transistor action (i.e., rapid change in 2DEG as a function of voltage of the gate electrode 120) controls the properties of light travel in the optical waveguide 161 and integrates electronic and optical functions on one substrate 102. Therefore, traditional FET electronic concepts can provide active optical functionality in the optical waveguide device 100. The FET portion 116 is physically located above, and affixed to, the silicon layer 160 using such semiconductor manufacturing techniques as epitaxial growth, chemical vapor deposition, physical vapor deposition, etc.

**[0049]** The field effect transistor (FET) portion 116 shown in FIGs. 7A to 7C operationally includes a portion of the optical waveguide 161. One embodiment of the silicon layer 160 is proximate to, and underneath, the gate electrode 120 of the FET portion 116. The FET portion 116 includes a first body contact electrode 118 (e.g. source), the gate electrode 120, and a second body contact electrode 122 (e.g. drain). A voltage can be applied by e.g., a voltage source 202 between pairs of the electrodes 118, 120, and 122. To control the active optical waveguide device 150, the voltage level of the gate electrode 120 is varied. The 2DEG 108 is formed at the junction between the silicon layer 160 and the gate oxide layer 110. In some embodiments, the gate electrode 120 is biased relative to the combined first and second body contact electrodes 118, 122.

[0050] The variation in voltage level changes the propagation constant of at least a portion of the optical waveguide 161. The changes in the index profile of the optical waveguide 161 are effected by the location and shapes of all the electrodes 118, 120, 122. The density of the 2DEG generally follows the contour (shape) of the gate electrode 120. The shape of the gate electrode 120 is "projected" as a region of altered effective mode index 190 into the silicon layer 160. The value of the propagation constant may vary at different locations within the optical waveguide 161. In this disclosure, the region of altered effective mode index 190 is considered that region of the optical waveguide 161 where the value of the effective mode index is changed by application of voltage to the gate electrode 120. The term "region of altered effective mode index" is applied to active optical waveguide devices 150 because the value of the effective mode index can be altered by varying the electric signals applied to the different electrodes 118, 120, 122. The region of altered effective mode index 190 typically extends through the vertical height of the optical waveguide 161. Changing the effective mode index in the region of altered effective mode index usually results in a change in the propagation constant in the region of altered effective mode index. Such changing of the propagation constant results in phase modulation of the light passing through that device. In FIGs. 7A to 7C and 8, phase modulation occurs in the region of altered effective mode index 190, indicated in cross-hatching. Different embodiments of gate electrodes 120 can have rectangular or non-rectangular shapes in a horizontal plane. The different embodiments of the active optical waveguide device 150 perform such differing optical functions as optical phase/amplitude modulation, optical filtering, optical deflection, optical

10

20

30

35

40

45

50

[0051] FIGs. 7A to 7C respectively show a side cross-sectional, top, and front cross-sectional view of one embodiment of an optical waveguide device 100. FIG. 7A shows prism couplers 112, 114 coupled to the planar silicon layer 160; the silicon layer 160 being bounded by low-index insulating materials. Other well-known types of couplings such as gratings, tapers, and butt couplings may be coupled to either end of the silicon layer 160. Light passing from the input prism coupler 112 (or other input port) to the output prism coupler 114 (or other output port) follows optical path 101 as shown in FIG. 7A

[0052] The gate electrode 120 is directly above the light path in the silicon layer 160. The low-index dielectric of the gate oxide layer 110 acts as an electrical insulator and an optical insulator that separates the gate electrode 120 from the silicon layer 160. This embodiment of active optical waveguide device 150 is a FET structure with the body contact electrodes 118, 122 forming a symmetric structure typically respectively referred to as "source" and "drain" in FET terminology. A substantially constant potential conductor 204 equalizes the voltage level between the first body contact electrode 118 and the second body contact electrode 122.

[0053] In many embodiments, the channel normally associated with electronic functions of the FET is considered, and acts as, the optical waveguide 161. Examples of electronic-type FETs that can be used in their modified form as FET portions 116 in optical waveguide devices 100 include a metal-oxide-semiconductor FET (MOSFET), a metal-electrical insulator-semiconductor FET (MISFET), a metal semiconductor FET (MESFET), a modulation doped FET (MODFET), a high electron mobility transistor (HEMT), and other similar transistors. The term "body contact electrodes" alternatively describes the substantially common potential source body contact electrode 118 and drain body contact electrode 122 in the FET-like structure 116 (FIG. 7C).

**[0054]** The silicon layer 160 (which may be doped) has a thickness h, and is sandwiched between the optical insulator layer 104 and the gate oxide layer 110. The first optical insulator layer 104 is typically formed from silicon dioxide (glass) or any other optical and electrical insulator commonly used in semiconductors (for example SiN). The optical insulator layer 104 and the gate oxide layer 110, where located, also acts to reflect and confine the light using total internal reflection of the light traversing the optical waveguide 161.

[0055] FIG. 7B shows one embodiment of a voltage source configuration that biases the voltage of the optical waveguide device 100 by using a voltage source 202 and the substantially constant electrical potential conductor 204. The substantially constant potential conductor 204 acts to tie the voltage level of the first body contact electrode 118 to the voltage level of the second body contact electrode 122. The voltage source 202 biases the voltage level of the gate electrode 120 relative to the combined voltage level of the first body contact electrode 118 and the second body contact electrode 122.

[0056] To apply a voltage to the gate electrode 120, a voltage source 202 applies an AC voltage  $v_g$  between the gate electrode 120 and the combined first body contact electrode 118 and second body contact electrode 122. The AC voltage  $v_g$  may be either a substantially regular (e.g. sinusoidal) signal or an irregular signal. An example of an irregular AC voltage  $v_g$  is a digital data transmission signal. In one embodiment, the AC voltage  $v_g$  is the information-carrying portion of the signal. The voltage source 202 can also apply a DC bias  $V_g$  to the gate electrode 120 relative to the combined first body contact electrode 118 and second body contact electrode 122. Depending on the instantaneous value of the  $V_g$ , the concentration of the 2DEG will accumulate, deplete, or invert as shown by the HEMT 500 shown in FIG. 8. In one embodiment, the DC bias  $V_g$  is the signal that compensates for changes in device parameters. A combined DC bias  $V_g$  and AC voltage  $v_g$  equals the total voltage  $V_g$  applied to the gate electrode 120 by the voltage source 202. It will be understood from the description above that modulation of the AC voltage  $v_g$  can thus be used to effect, for example, a corresponding modulation of light passing through the optical waveguide 161.

[0057] The voltage potential of the first body contact electrode 118 is tied to the voltage potential of the second body contact electrode 122 by the substantially constant potential conductor 204 as shown in the embodiments of active optical waveguide device 150 in FIGs. 7B and 8. Certain embodiments of the substantially constant potential conductor 204 as shown in FIG. 8 include a meter 205 (e.g. a micrometer) to measure the electrical resistance of the gate electrode 120 from the first body contact electrode 118 to the second body contact electrode 122. The constant potential conductor uses the term "substantially" because the meter 205 may generate some relatively minor current levels in comparison to the operating voltage and current levels applied to the optical waveguide device 100. In one embodiment, minor current levels measure the resistance of the gate electrode 120. The current level produced by the meter 205 is relatively small since the voltage (typically in the microvolt range) of the meter is small, and the electrical resistance of the silicon layer 160 is considerable (typically in the tens of ohms).

[0058] One embodiment of the optical waveguide devices 100 can be constructed on so-called silicon on insulator (SOI) technology that is used in the semiconductor electronics field. In SOI electronic devices, the vast majority of electronic transistor action in SOI transistors occurs on the top few microns of the silicon. Therefore optically, the material below the top few microns of the silicon layer 160 does not have to transmit light. While still following basic SOI rules, the silicon layer below the top few microns could be formed instead from the optical insulator 104 such as a glass (e.g., silicon dioxide). The SOI technology is based on providing a perfect silicon wafer formed on the gate oxide layer 110 which is an optical (and electrical) insulator such as glass (silicon dioxide), that often starts two to five microns below the upper surface of the silicon. The gate oxide layer 110 electrically isolates the upper two to five microns of silicon from the rest of the silicon.

**[0059]** The inclusion of the optical (electrical) insulator 104 in thin SOI electronic devices 5101 limits the large number of electric paths that can be created through a thicker silicon layer 160. Therefore, forming optical waveguide devices 160 on thin SOT wafers makes SOI transistors and active optical waveguide devices 150 operate faster and consume less power.

20

30

35

40

45

50

55

**[0060]** The electrical resistance of the gate electrode 120 is a function of such parameters as voltage of the gate electrode, temperature, pressure, device age, and device characteristics. The voltage (e.g. the AC voltage or the DC voltage) applied to the gate electrode 120 can be varied to adjust the electrical resistance of the gate electrode 120. Such variations in the electrical resistance of the gate electrode can compensate for temperature, pressure, device age, and/or other operating parameters of the optical waveguide device 100.

**[0061]** As the temperature of the optical waveguide device 100 varies, the DC bias  $V_g$  applied to the gate electrode 120 of the optical waveguide device 100 is adjusted to compensate for the changed temperature. Other parameters (pressure, device age, device characteristics, etc.) can be compensated for in a similar manner as described for temperature (e.g. using a pressure sensor to sense variations in pressure).

[0062] FIGs. 9, 10, and 11 illustrate three embodiments of the active optical waveguide device 150 that include the FET shown in FIGs. 7A, 7B, and 7C, whose optical function differs from each other. The different optical function of the active optical waveguide devices 150 shown in FIGs. 7B, 8, 9, 10, and 11 differ from each other based on the shape of the gate electrode 120. The embodiment of active optical waveguide device 150 shown in FIGs. 7A to 7C, for example, functions as a modulator since the gate electrode 120 is rectangular. The rectangular gate electrode 120 extends across the width of the silicon layer 160, and has a substantially equal axial length, as taken in a direction parallel to the optical waveguide 161 across the entire silicon layer. The shape of the gate electrode 120 projects the 2DEG region within the silicon layer 160. Since the gate electrode 120 has a substantially rectangular configuration, the gate electrode 120 alters the propagation constant or the effective mode index within the silicon layer 160 to be substantially uniform across the width of the silicon layer 160. In this configuration, the active optical waveguide device acts as a modulator since the propagation constant of light travelling in the optical waveguide 161 is substantially uniform. Varying the electric voltage level applied to the gate electrode 120 alters the effective mode index of the 2DEG region, and alters the propagation constant of that portion of the silicon layer 160 corresponding to the 2DEG region.

[0063] Changing the shape of the gate electrode 120 alters the shape of the 2DEG region 108 projected within the silicon layer 160. For example, FIG. 9 illustrates the active optical waveguide device 150 having a plurality of gate electrodes 4102a, 4102b, and 4102c. The grate-like configuration of the gate electrodes 4102a, 4102b, and 4102c differs from the substantially rectangular gate electrode 120 shown in FIG. 7B. The grating-shaped gate electrodes 4102a, b, c therefore project grating-shaped 2DEG regions 108 into the silicon layer 160. The grating-shaped 2DEG regions 108 within the silicon layer 160 have a different effective mode index (and different propagation constant) than the portions of the silicon layer 160 that are located outside of the 2DEG region. The projection of such grating-shaped regions of altered propagation constant within the optical waveguide 161 causes the embodiment of active optical waveguide device 150 as shown in FIG. 9 to function to deflect various wavelengths of light in a similar manner to known optical gratings, depending on the voltage applied to electrodes 120. Only some percentage of light having wavelengths that corresponds to the spacing between the grating-shaped regions of altered propagation constant within the optical waveguide 161 will constructively interfere to produce the deflected beam. Light having wavelengths that corresponds to the spacing between the grating-shaped regions of altered propagation constant will destructively interfere, and will

not factor in the deflected beam.

10

20

30

35

40

45

50

55

[0064] FIG. 10 illustrates one embodiment of the active optical waveguide device 150 having a gate electrode 120 shaped as a pair of optical prisms 720. U.S. Patent Application Ser. No. 09/859,239 (incorporated by reference below) shows one embodiment of active optical waveguide device having the gate electrode shaped as a pair of optical prisms. Each optical prism-shaped gate electrode 720 in FIG. 7B, therefore, when actuated projects an optical prism-shaped 2DEG region 108 into the silicon layer 160. The optical prism-shaped 2DEG region 108 within the silicon layer 160 has a different effective mode index (and different propagation constant) than the portions of the silicon layer 160 that are located outside of the 2DEG region. The projection of such an optical prism-shaped region of altered effective mode index within the silicon layer 160 causes the embodiment of active optical waveguide device 150 as shown in FIG. 7B to function to divert light through a prescribed angle. Active optical waveguide devices 150 including the gate electrode 120 shaped as an optical prism 720 may act as an optical switch.

[0065] FIG. 11 illustrates the active optical waveguide device 150 having the gate electrode 120 shaped as an optical lens 730. U.S. Patent Application Ser. No. 09/859,647 (incorporated by reference below) shows one embodiment of active optical waveguide device having the gate electrode shaped as a lens. The optical lens-shaped gate electrode 120 therefore projects an optical lens-shaped 2DEG region 108 into the silicon layer 160. The optical lens-shaped 2DEG region 108 within the silicon layer 160 has a different effective mode index (and different propagation constant) than the portions of the silicon layer 160 that are located outside of the 2DEG region. The active optical waveguide device 150 as shown in FIG. 7C projects the optical lens-shaped region of altered effective mode index within the silicon layer 160 to focus light to a prescribed focal point 3016.

[0066] FIGs. 12A to 12E illustrate how effective mode index in active optical waveguide devices vary as different charges are applied to the body contact electrodes 107, 109 as well as the gate electrodes. FIG. 12E illustrates a progression of different voltages that are applied between the gate electrode 120 and the body contact electrode(s). The locations that each ones of FIGs. 12A to 12D are located across the voltage plot of FIG. 12E are illustrated by the arrows. FIGs. 12A to 12D illustrate that as different voltages are applied between the gate electrode 120 and the body contact electrode(s), a different electronic profile (indicated by the contours in each figure) is established across the optical waveguide 161. As such, the active optical waveguide device 150 responds to electronic input in a manner that alters the effective mode index within the region of altered effective mode index of the optical waveguide, and therefore can alter how light flows through the optical waveguide.