# (11) EP 2 280 543 A2

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

02.02.2011 Bulletin 2011/05

(51) Int Cl.: **H04N** 5/44 (2011.01)

(21) Application number: 10075649.3

(22) Date of filing: 05.10.1998

(84) Designated Contracting States: **DE FR GB IT NL**

(30) Priority: 15.10.1997 US 950722

(62) Document number(s) of the earlier application(s) in accordance with Art. 76 EPC:

09011725.0 / 2 131 577 98953254.4 / 1 023 804

(71) Applicant: Zilog, Inc. San Jose, CA 95119 (US) (72) Inventor: Tsyrganovich, Anatoliy V. San José

California 95123 (US)

(74) Representative: Hitchcock, Esmond Antony Marks & Clerk LLP

90 Long Acre London

WC2E 9RA (GB)

#### Remarks:

This application was filed on 01-10-2010 as a divisional application to the application mentioned under INID code 62.

### (54) Integrated television processor

(57) By forming a digital video processor and digital television controller on the same integrated circuit, a number of advantages in improved picture quality can be obtained. The length of the communication connections between these two elements can be reduced, thus reducing television picture distortion caused by electromagnetic interference. Additionally, the elements can be controlled by a single dot clock generator with a single phase locked loop circuit. Also, register banks can be used for intercommunication between the television controller and the video processor rather than the communication between the two different ICs over a bus.

EP 2 280 543 A2

15

20

25

40

#### **Background of the Invention**

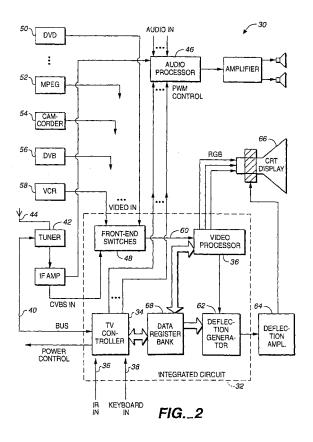

[0001] The present invention relates to television systems, especially in the architecture of television systems. [0002] Contemporary television processors are complicated and multi-functional. They control the television tuner, video processor, audio processor, deflection parameters, power supply, and video input select. Figure 1 is a diagram of a prior art television system. In a typical television system, television controllers are used. Television controllers receive input from the user and control other units in the television processor. Typically, the television controller is formed on an integrated circuit (IC). Additionally, a video processor 14 is formed on another integrated chip. The video processor converts a video signal to pixel data, which is sent to the display such as a CRT display 16.

1

**[0003]** There are disadvantages of having the video processor and the television controller on two different integrated chips. Long wire communication on television chassis with high frequency and sharp signals can cause a lot of electromagnetic interference (EMI) and picture distortions, such as jitter. For this reason, it is desired to have an improved television processor architecture that prevent these problems.

[0004] By putting the television controller and the video

processor together on one integrated circuit chip, the

length of the communication links between these two el-

#### **Summary of the Present Invention**

ements is reduced. This can remove some of the problems of the prior art. Additionally, by using a single dot clock generator for both the video processor and the television controller, the picture quality can be improved. Prior systems had a dot clock generator with its own phase locked loop (PLL) circuit on both the video processor IC and the television controller IC. It is impractical to send the clock signal between integrated circuits so each IC would reconstruct a dot clock from the horizontal and vertical sync. Since the television controller and the video processor are synchronized by a single dot clock in the present system, this facilitates features such as picture-in-picture (PIP) and on-screen display (OSD). [0005] Additionally, by using an internal interface between the television controller and the video processor that uses a bank of registers, the communication between the television controller and the video processor can be improved. The control data in the registers can be written into and read from by either the television controller and the video processor. This data can include the parameter controls. Examples of such data would be the contrast or sharpness parameters input by the user into the television controller and stored in the register banks of the internal interface where the data can be easily accessed by the video processor. The transfer of data in

registers is facilitated since the television controller and video processor are on the same integrated circuit, and data need not be transferred in a bus between ICs.

## Briefs Description of the Drawings

**[0006]** The above and other features and aspects of the present invention will become more apparent upon reading the following detailed description in conjunction with the accompanying drawings.

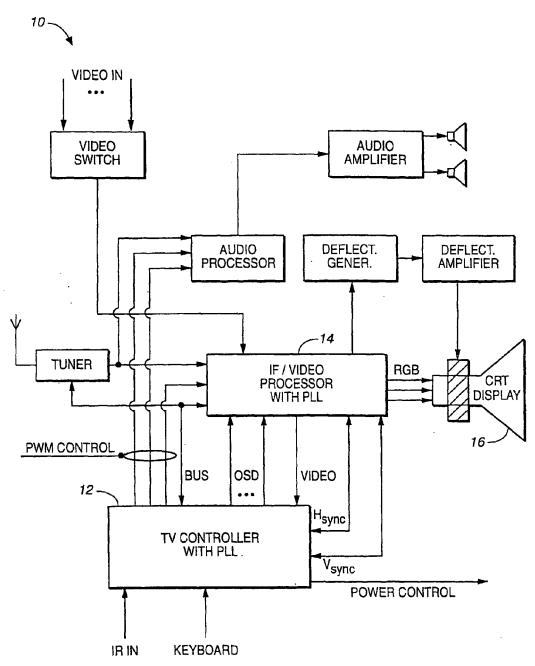

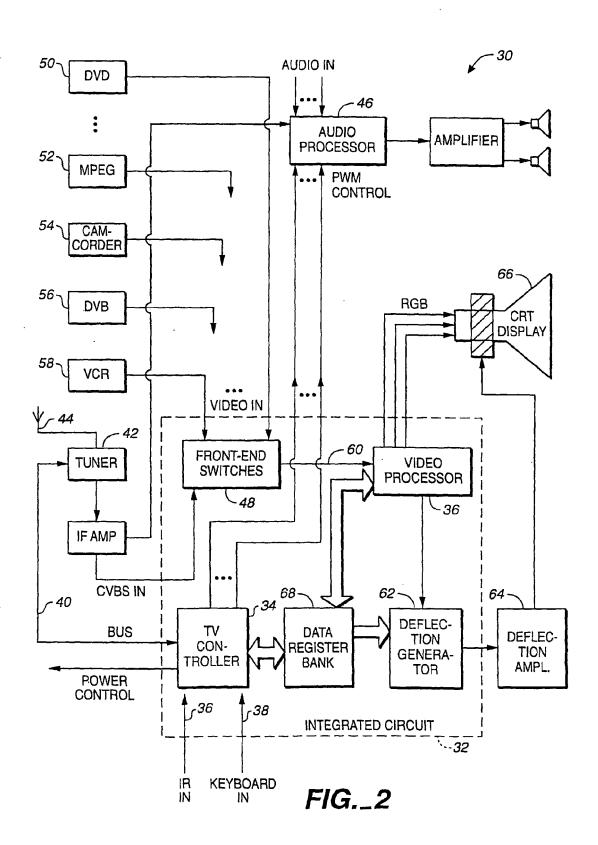

Figure 1 is a diagram of a prior art television system. Figure 2 is a diagram of the television system of the present invention with the integrated circuit including the television controller and video processor shown in phantom.

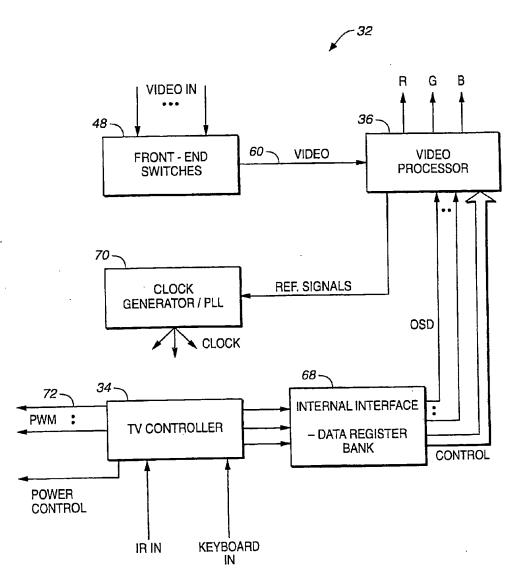

Figure 3 is a diagram of functional units of the integrated circuit including the television controller and video processor of the present invention.

## <u>Detailed Description</u> of the Preferred Embodiment

[0007] Figure 2 is a diagram of the television system 30 of the present invention showing the integrated circuit 32 with the television controller 34 and the video processor 36. Forming the television controller and video processor within the single integrated circuit 32 has the advantage that the connections between the units are shorter, and thus produce less electromagnetic interference. [0008] The television controller unit 34 receives user input over lines 36 and 38. An infrared (IR) input such as that from a remote control can be received over line 36, and a keyboard input could be received over, for example, line 38. The television controller can be used to produce a power control on/off signal for the television set, as well as placing information on the bus 40 to control the television tuner 42. The bus 40 can be, for example, an I<sup>2</sup>C bus available from the Philips Corporation. The television controller 34 can instruct the tuner 42 to tune the signal from the antenna 44. The audio portion of the tuned signal is sent to the audio processor 46 and the video portion is sent to the front-end switch 48. The frontend switch 48 is preferably a portion of the integrated circuit, and can receive additional video input such as that from a digital videodisc (DVD) 50, a source of data encoded in the MPEG (moving pictures expert group) standard 52, a camcorder 54, a digital video broadcast (DVB) 56, or a videocassette recorder (VCR) 58. The front-end switch is controlled by the television controller 34 and sends a video signal on line 60 to the video processor 36. The video processor converts the video data on line 60 to a red/green/blue (RGB) signal for the CRT display, as well as controls the deflection generator 62 to send a signal to the circuitry 64, which produces the deflection amplitude. The CRT display 66 uses the RGB signal and the deflection signal to produce the video display. Also shown in this circuitry is the data register bank 68 of the internal interface. The data register bank stores

10

15

20

40

45

50

55

the control information, such as the saturation and brightness controls, from the television controller 34 and holds it to be accessed by the video processor 36 as desired. As discussed above, storing the information in a data register accessible by both the television controller and the video processor has advantages over having separate ICs with the television controller and the video processor, and transferring data over a bus.

[0009] The use of a single dot clock generator with a phase locked loop circuit can be best seen in the functional diagram of Figure 3. Figure 3 is a diagram of the functional units of the integrated circuit of the present invention. The video processor 36 can send reference signals, such as the horizontal sync, to the clock generator phase lock loop system 70. The clock generator produces a dot clock which can be sent to the different elements, including the television controller 34 and the video processor 36. The television controller 34 is shown with the outgoing control line 72 sent to the audio processor (not shown). These control lines are sent as pulse-widthmodulated information. Pulse-width-modulated data does not need to be sent to the video processor 36 because the data registers in the bank 68 can store the control data. The transfer data can include on-screen display (OSD) data, such as menu selection information or closed captioning.

**[0010]** Having a single clock generator 70 has a number of advantages. The clock signals will be synchronized, since they come from a single circuit. This means that the video signals from a first source, such as the OSD data from the television controller, can be accurately combined with the signals from another source, such as the video line 60. In a similar manner, picture-in-picture functions can be improved.

**[0011]** Various details of the implementation and method are merely illustrative of the invention. It will be understood that various changes in such details may be within the scope of the invention, which is to be limited only by the appended claims.

**[0012]** Further preferred embodiments of the present invention are set out in the following clauses:

- 1. An integrated circuit including:

- a digital video processor for decoding a video signal and producing a pixel output;

- a digital television controller for receiving the user input and controlling the television channel selection; and

- an internal interface including registers for exchanging data between the digital video processor and the digital TV controller.

- 2. The integrated circuit of clause 1, wherein the television controller produces a power on/off signal.

- 3. The integrated circuit of clause 1, wherein the television controller produces an on-screen display.

- 4. The integrated circuit of clause 3, wherein the onscreen display information is sent through the internal interface to the video processor.

- 5. The integrated circuit of clause 1, wherein the television controller produces audio control signals.

- 6. The integrated circuit of clause 1, further comprising a single dot clock generator receiving reference information from the video processor and producing a dot clock for both the video processor and the TV controller.

- 7. The integrated circuit of clause 6, wherein the dot clock generator includes a phase locked loop circuit.

- 8. The integrated circuit of clause 6, wherein the dot clock generator includes horizontal sync pulses from the video processor as an input.

- 9. The integrated circuit of clause 1, further comprising a deflection signal generator connected to the registers.

- 10. The integrated circuit of clause 1, further comprising video input switches.

- 11. An integrated circuit including:

- a digital video processor for decoding a video signal and producing a pixel output;

- a digital TV controller for receiving the user input and controlling the television channel selection; and

- a single dot clock generator receiving reference information from the video processor and producing a dot clock for both the video processor and the television controller.

- 12. The integrated circuit of clause 11, wherein the dot clock generator includes a phase locked loop circuit.

- 13. The integrated circuit of clause 11, wherein the dot clock generator includes horizontal sync pulses from the video processor as an input.

- 14. The integrated circuit of clause 11, further comprising an internal interface including registers for exchanging data between the digital video processor and the digital television controller.

- 15. The integrated circuit of clause 11, wherein the television controller produces a power on/off signal.

- 16. The integrated circuit of clause 11, wherein the television controller produces an on-screen display.

10

15

17. The integrated circuit of clause 16, wherein the on-screen display information is sent through an internal interface to the video processor.

18. The integrated circuit of clause 1, wherein the television controller produces audio control signals.

#### Claims

1. A method comprising:

providing a television controller and a video processor together on one integrated circuit chip; and

providing an internal interface between the television controller and the video processor on the integrated circuit chip, the internal interface comprising a bank of registers;

wherein the television controller is arranged to provide saturation and brightness controls to the bank of registers for access in the bank of registers by the video processor.

- The method of Claim 1, wherein the television controller is operable to produce an on-screen display information and to send the on-screen display information through the internal interface to the video processor.

- 3. The method of Claim 1 or 2, further comprising providing a single dot clock generator on the integrated circuit.

- **4.** The method of Claim 3, wherein the dot clock generator uses a phase locked loop circuit to produce the dot clock.

- **5.** The method of claim 3 or 4, wherein the dot clock generator uses horizontal sync pulses from the video processor as an input to produce the dot clock.

45

30

50

55

FIG.\_1 (PRIOR ART)

FIG.\_3